## Ultra-capacitor based regenerative energy storage and power factor correction device for controlled electric drives

Petar Grbovic

#### ▶ To cite this version:

Petar Grbovic. Ultra-capacitor based regenerative energy storage and power factor correction device for controlled electric drives. Other. Ecole Centrale de Lille, 2010. English. NNT: 2010ECLI0009. tel-00585405

#### HAL Id: tel-00585405 https://theses.hal.science/tel-00585405

Submitted on 12 Apr 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N°d'ordre: 125 ECOLE CENTRALE DE LILLE

#### **THESE**

présentée en vue d'obtenir le grade de

#### **DOCTEUR**

en

Spécialité : Génie Electrique

Par

Petar J. GRBOVIĆ

#### DOCTORAT DELIVRE PAR L'ECOLE CENTRALE DE LILLE

### Dispositif correcteur de facteur de puissance à base de super-condensateur pour variateur de vitesse

Soutenue le 09 Juillet 2010 devant le jury d'examen:

| Rapporteur            | Johann Walter KOLAR     | Professeur                     | Swiss Federal Institute of<br>Technology (ETH), Zurich |  |  |

|-----------------------|-------------------------|--------------------------------|--------------------------------------------------------|--|--|

| Rapporteur            | Jean-Paul FERRIEUX      | Professeur                     | G2ELAB, Grenoble                                       |  |  |

| Membre                | Thierry MEYNARD         | Directeur de<br>Recherche CNRS | LAPLACE, Université de<br>Toulouse III, Toulouse       |  |  |

| Membre                | Philippe DELARUE        | Maître de Conférences          | L2EP, Polytech'Lille, Lille                            |  |  |

| Membre                | Patrick<br>BARTHOLOMEUS | Maître de Conférences          | L2EP, Ecole Centrale de<br>Lille, Lille                |  |  |

| Directeur de<br>thèse | Philippe LE MOIGNE      | Professeur                     | L2EP, Ecole Centrale de<br>Lille, Lille                |  |  |

| Membre invité         | Michel ARPILLIERE       |                                | Schenider Toshiba Inverter                             |  |  |

Thèse préparée au Laboratoire d'Electrotechnique et d'Electronique de Puissance (L2EP)

Ecole Doctorale SPI 072

## Ultra-capacitor based regenerative energy storage and power factor correction device for controlled electric drives

Petar J. Grbović

#### PhD Dissertation

Laboratoire d'Electrotechnique et d'Electronique de Puissance (L2EP)

Ecole Doctorale SPI 072,

ECOLE CENTRALE DE LILLE, LILLE

July 9<sup>th</sup> 2010

#### **ACKNOWLEDGEMENTS**

I wish to express my gratitude to the dissertation supervisor, Professor Philippe Le Moigne for giving me an opportunity to start my dissertation with L2EP. I appreciate his patience and time he spent to read my fifteen-pages long IEEE Transaction "essays".

I would like to thank to Professor Johann Walter Kolar from Swiss Federal Institute of Technology (ETH), Zurich, Professor Jean-Paul Ferrieux from The University of Grenoble and Thierry Menyard from The University Toulouse III for accepting to review the dissertation report and be members of the dissertation committee.

Especially, I would like to express my deep gratitude to associat Professor Philippe Delarue for all creative and fruitful discussions we had together during those two and half years. He was an excellent co-authors and reviewer of all journal papers we wrote together.

Also I wish to thank to associat Professor Patrick Bartholomeus, co-supervisor of my dissertation.

This project and dissertation would not be possible without support of Dr. Philippe Baudesson and R&D depertment of Schneider Toshiba Inverter, Pacy sur Eure.

I offer my deepest gratitude to my family and particularly to my wife Jelana and mother Stojka for their love and support and for their confidence in me.

Finally, let me express my deepest gratitude to God for His blessing.

### TABLE OF CONTENTS

| Acknowledgements                                                                                                                                                              | i        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Table of Contents                                                                                                                                                             | ii       |

| PART ONE: Introduction and General Considerations of the Dissertation                                                                                                         | 1        |

| 1. General Introduction                                                                                                                                                       | 2        |

| 1.1. Background                                                                                                                                                               | 2        |

| 1.1.1. Short History of Electric Drives                                                                                                                                       |          |

| 1.1.2. Present                                                                                                                                                                | 2<br>3   |

| 1.1.3. Typical Applications of Controlled Electric Drives                                                                                                                     | 4        |

| 1.1.4. Remaining Technical Issues in Application of Controlled Electric Drives                                                                                                | 5        |

| 1.2. Literature Overview                                                                                                                                                      | 7<br>7   |

| 1.2.1. Regenerative Drives Based on Back to Back and Matrix Converter 1.2.2. Regenerative Drives Based on the Energy Storage Concept                                          | 8        |

| 1.2.3. The Mains Current Harmonics and Related Issues                                                                                                                         | 10       |

| 1.2.4. Smoothing of the Input Peak Power                                                                                                                                      | 12       |

| 1.3. The Dissertation Objective                                                                                                                                               | 12       |

| 1.3.1. Parallel Connection of Energy Storage Device and Controlled Electric Drive                                                                                             | 12       |

| 1.3.2. The Mains Current Harmonics, DC Bus Voltage Control and Single Phase Supply                                                                                            | 12       |

| 1.3.3. Energy Storage and Power Factor Correction Device for Electric Drive Applications                                                                                      | 13       |

| 1.4. The Dissertation Organization                                                                                                                                            | 13       |

| 1.4.1. Part One: General Introduction                                                                                                                                         | 13       |

| 1.4.2. Part Two: Parallel Connected Energy Storage Device for Controlled Electric Drives 1.4.3. Part Three: Three-terminal Power Factor Correction and Voltage Control Device | 13<br>14 |

| 1.4.4. Part Four: Three-terminal Energy Storage and PFC Device for Controlled Electric Dri                                                                                    |          |

| 1.4.5. Part Five: Concluding Remarks and Conclusions                                                                                                                          | 15       |

| PART TWO: Parallel Connected Energy Storage Device for Controlled Electric                                                                                                    |          |

| Drives                                                                                                                                                                        | 16       |

| 2. An Ultra-Capacitor as Energy Storage Device for Power Conversion                                                                                                           |          |

| Applications                                                                                                                                                                  | 17       |

| 2.1. The Ultra-Capacitors                                                                                                                                                     | 17       |

| 2.1.1. Short History of the Ultra-capacitors                                                                                                                                  | 17       |

| 2.1.2. Overview of Different Technologies                                                                                                                                     | 18       |

| 2.1.3. Electric Double Layer Capacitors -EDLC                                                                                                                                 | 18       |

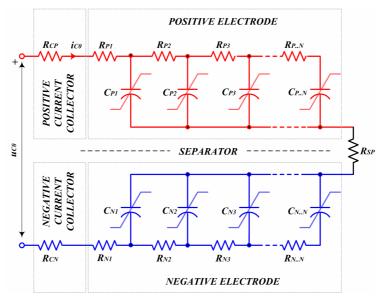

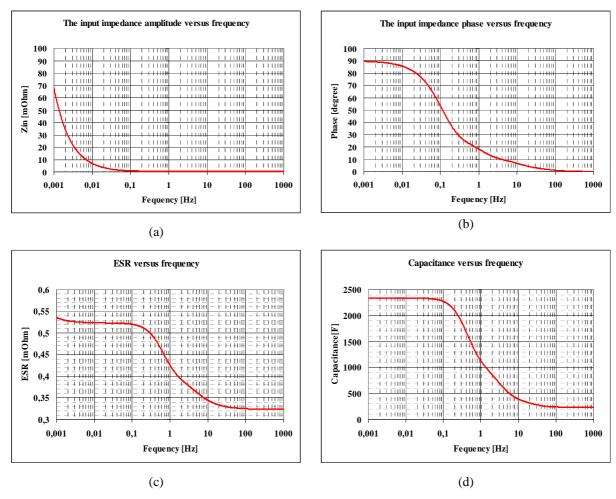

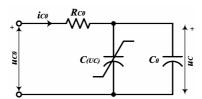

| 2.2. The Ultra-capacitors Macro (Electric Circuit) Model                                                                                                                      | 20       |

| 2.2.1. Full Theoretical Model                                                                                                                                                 | 20       |

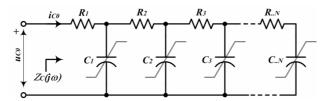

| 2.2.2. Simplified Model                                                                                                                                                       | 25       |

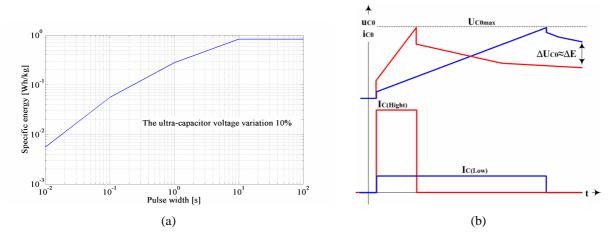

| 2.2.3. The Ultra-capacitor Energy Capacity 2.3. The Ultra-capacitor Charge/Discharge Methods                                                                                  | 26<br>27 |

| 2.3.1. Constant Resistive Load                                                                                                                                                | 27       |

| 2.3.2. Constant Current                                                                                                                                                       | 27       |

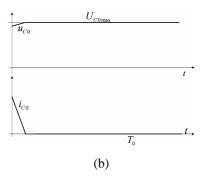

| 2.3.3. Charging                                                                                                                                                               | 28       |

| 2.3.4. Constant Power                                                                                                                                                         | 29       |

| 2.4. Frequency Related Losses                                                                                                                                                 | 30       |

| 2.4.1. How to Calculate Total Losses in Case that the ESR is a Function of Frequency?                                                                                         | 31       |

| 2.4.2. The Current is Periodic Function                                                                                                                                       | 31       |

| 2.4.3. The Current is Non-periodic Function                                                                                                                                   | 34<br>35 |

| 2.5. Trends in the Ultra-capacitors Development                                                                                                                               | 33       |

| 2.6. Short Conclusion                                                                    | 36       |

|------------------------------------------------------------------------------------------|----------|

| 3. Ultra-Capacitor Based Regenerative Electric Drives                                    | 38       |

| 3.1. Background                                                                          | 38       |

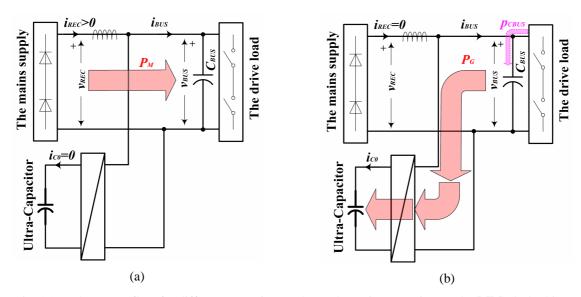

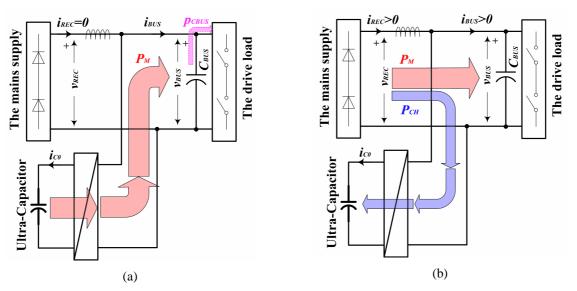

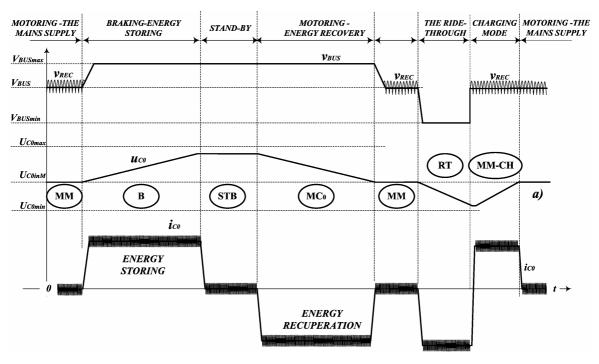

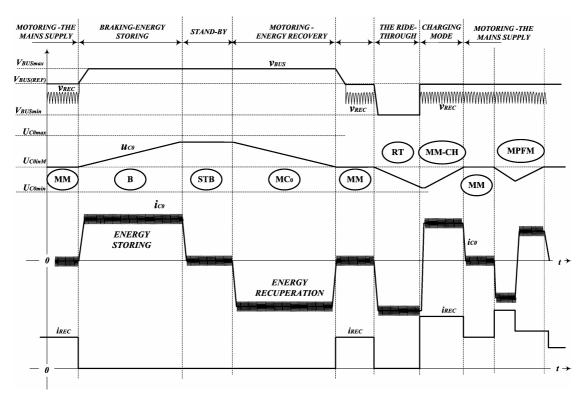

| 3.2. Operational Modes                                                                   | 39       |

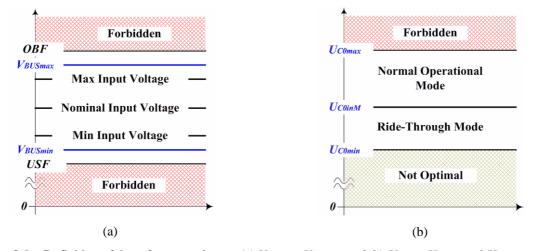

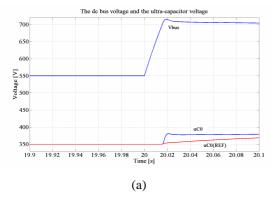

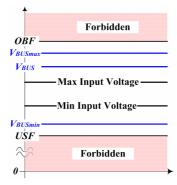

| 3.2.1. Definition of the Reference Voltages                                              | 41       |

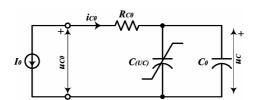

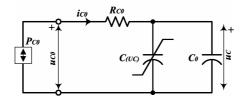

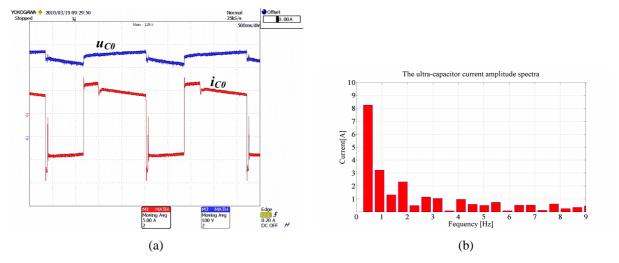

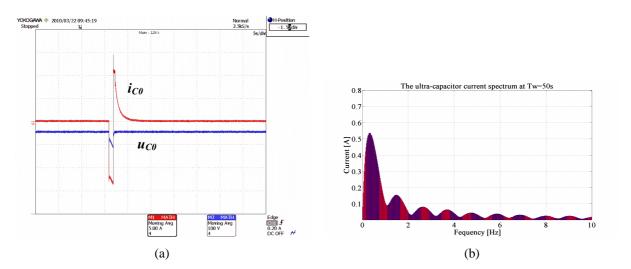

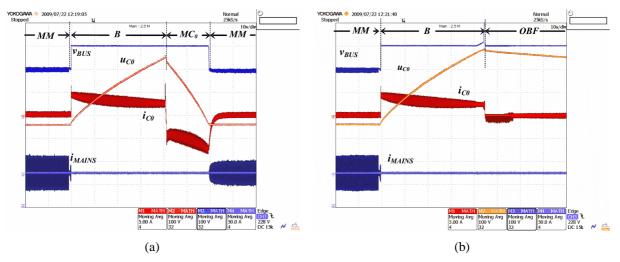

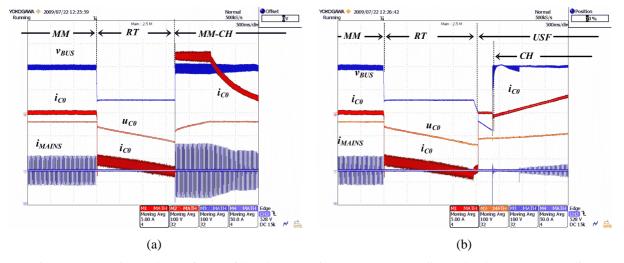

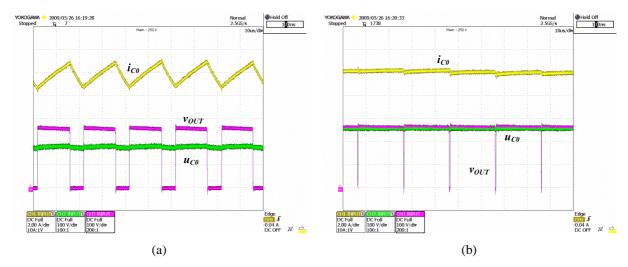

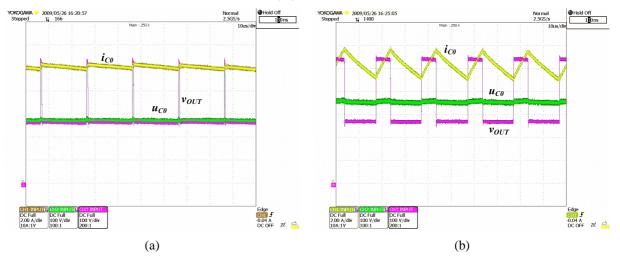

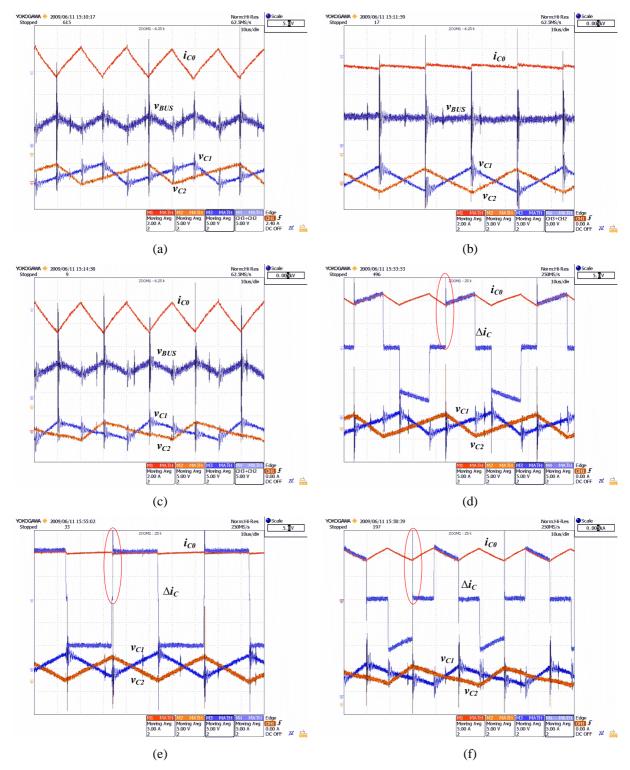

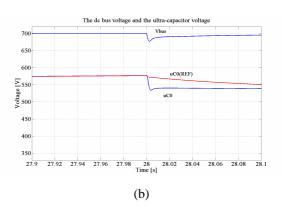

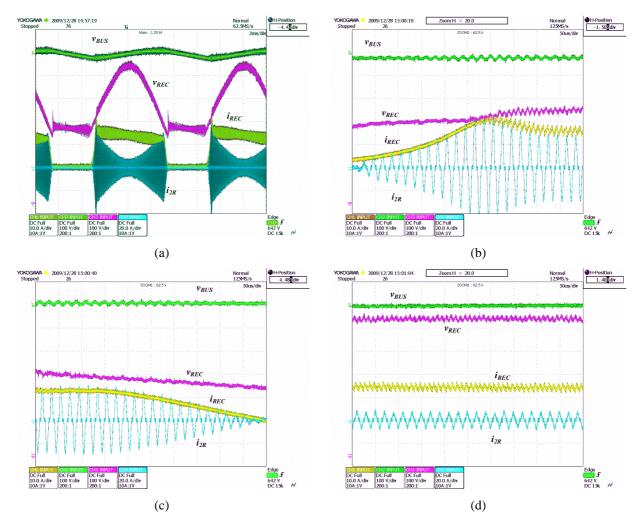

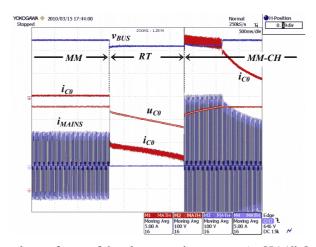

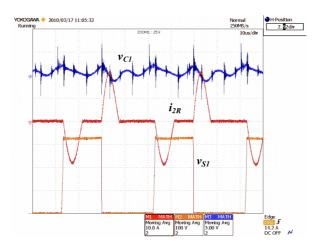

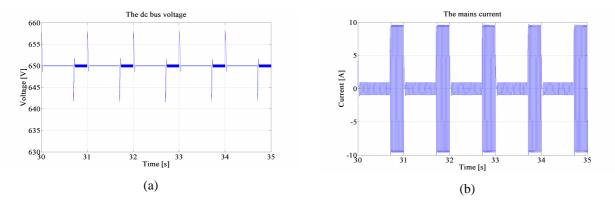

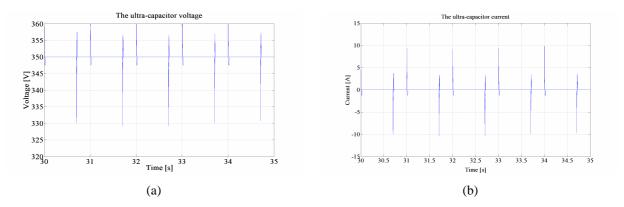

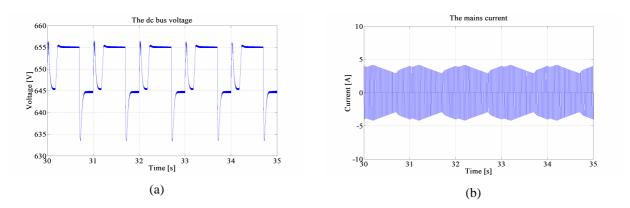

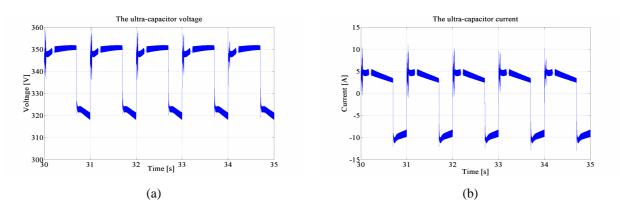

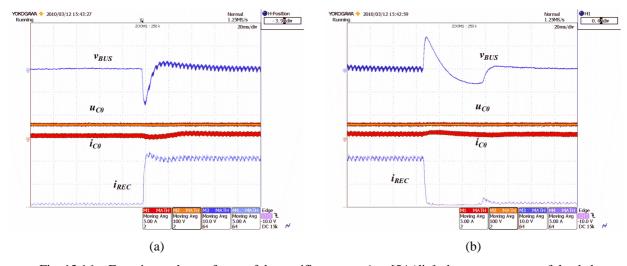

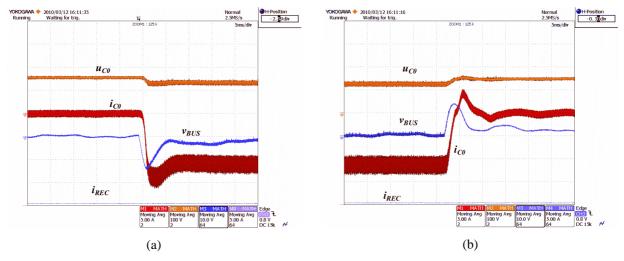

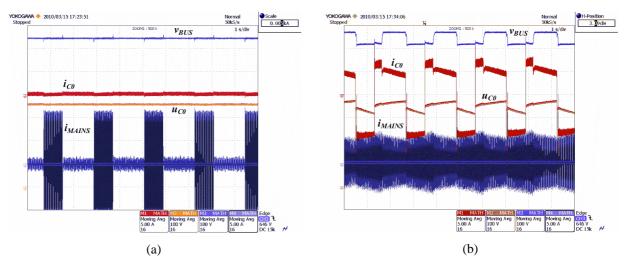

| 3.2.2. Some Experimental Waveforms                                                       | 42       |

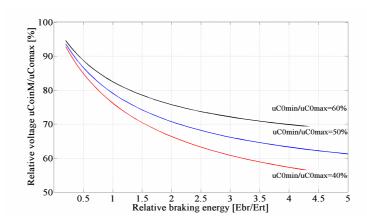

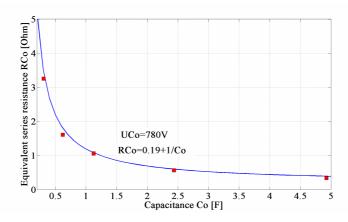

| 3.3. Ultra-capacitor Selection and Design                                                | 44       |

| 3.3.1. Voltage Rating                                                                    | 45       |

| 3.3.2. The Capacitance                                                                   | 45       |

| 3.3.3. Current Stress and Losses                                                         | 46       |

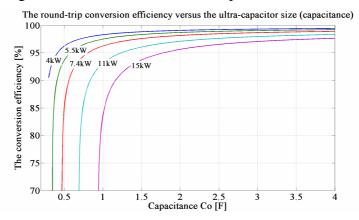

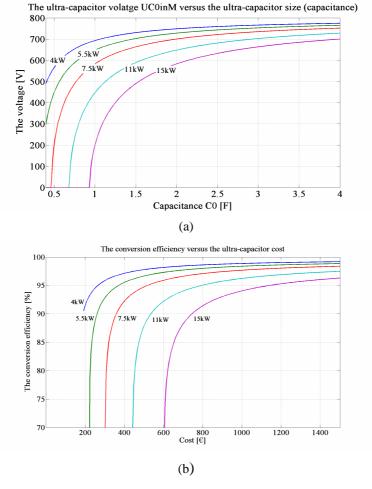

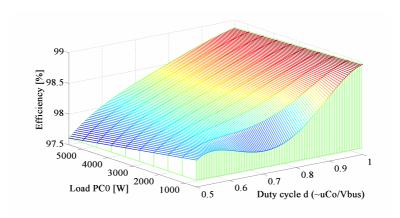

| 3.3.4. Conversion Efficiency                                                             | 48       |

| 4. Three-Level Interface DC-DC Converter                                                 | 51       |

| 4.1. Background and State of the Art                                                     | 51       |

| 4.2. Three-Level DC-DC Converter                                                         | 51       |

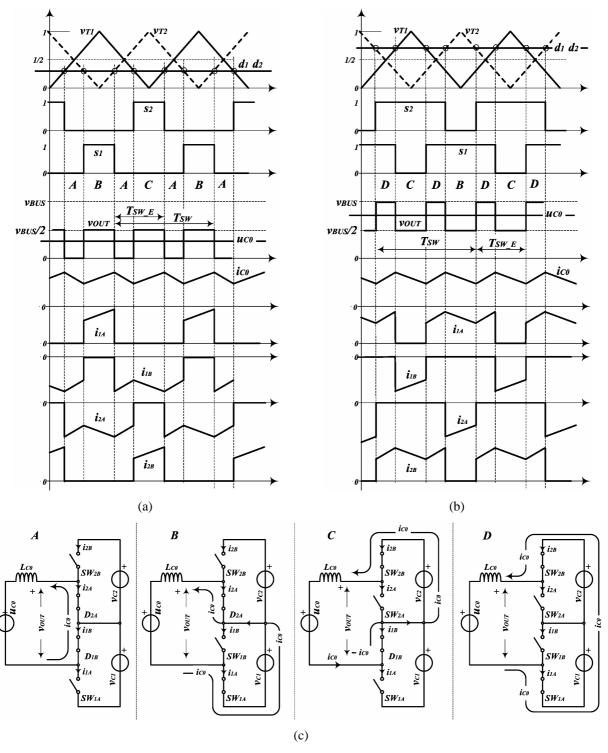

| 4.2.1. Analysis                                                                          | 53       |

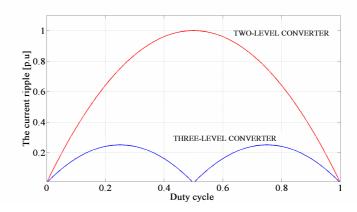

| 4.2.2. Filter Inductor $L_{C0}$                                                          | 55       |

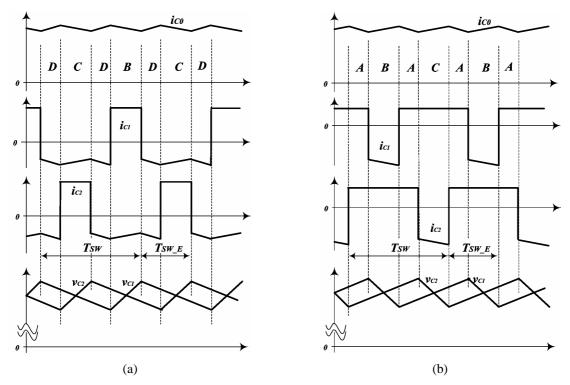

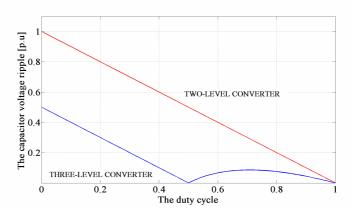

| 4.2.3. Filter Capacitors $C_{B1}$ , $C_{B2}$                                             | 57       |

| 4.3. Design and Selection of the Active Components                                       | 60       |

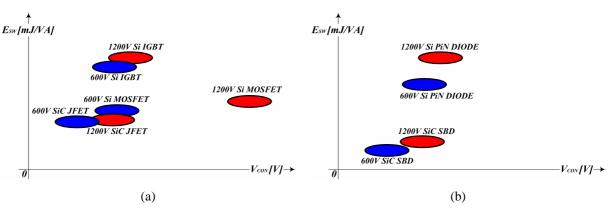

| 4.3.1. Advanced Semiconductor Switches                                                   | 60       |

| 4.3.2. Voltage Rating                                                                    | 60       |

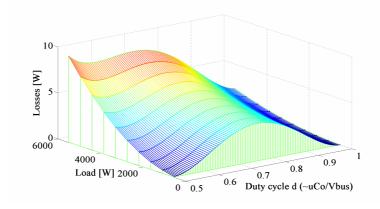

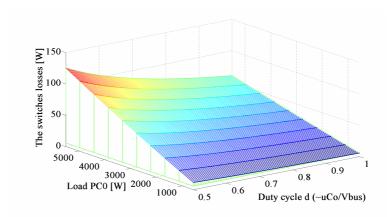

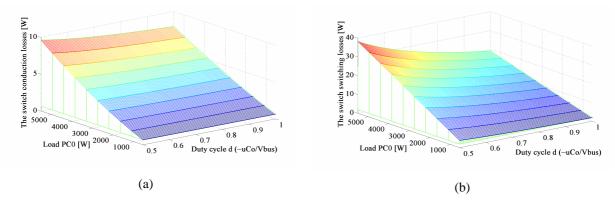

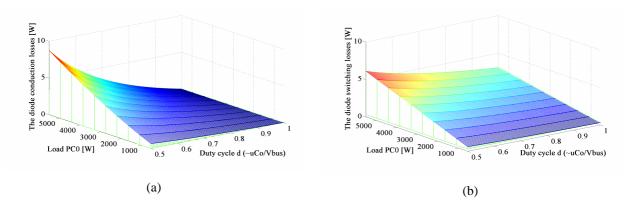

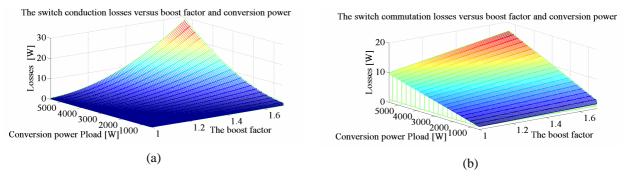

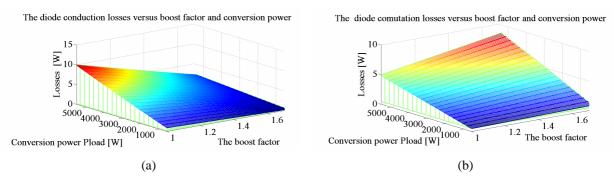

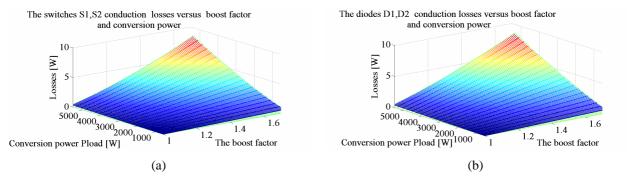

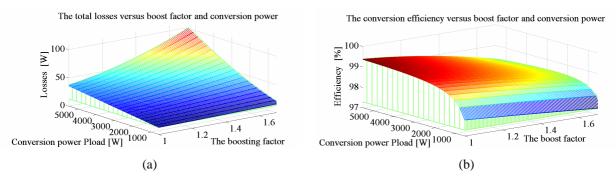

| 4.3.3. Conduction and Switching Losses                                                   | 61       |

| 4.4. The DC-DC Converter Design Example                                                  | 62       |

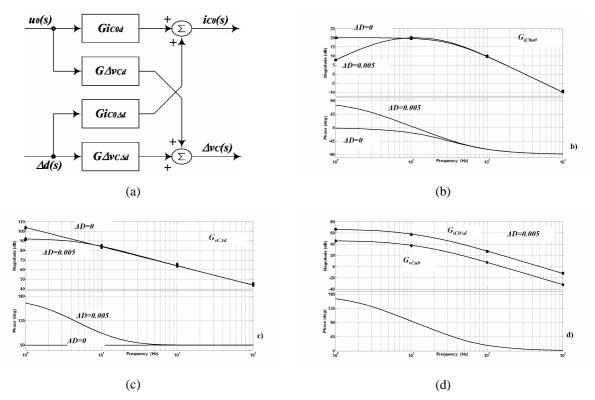

| 5. Modeling Aspects and Control Scheme                                                   | 68       |

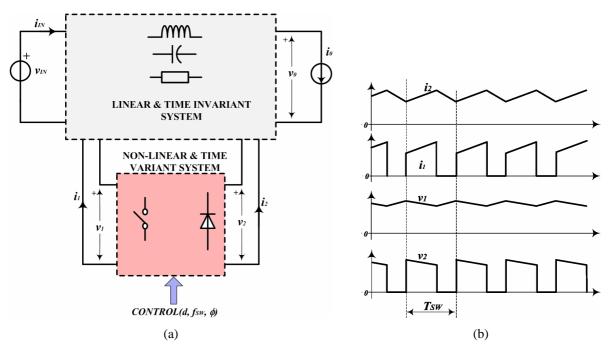

| 5.1. Modelling Techniques                                                                | 68       |

| 5.2. The DC-DC Converter Model                                                           | 71       |

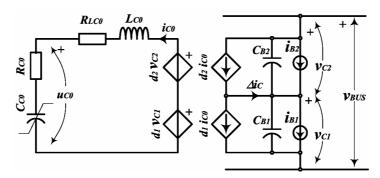

| 5.2.1. Large Signal Model                                                                | 71       |

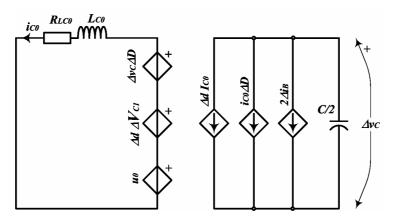

| 5.2.2. Linearization and Small Signal Model                                              | 72       |

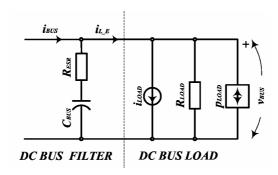

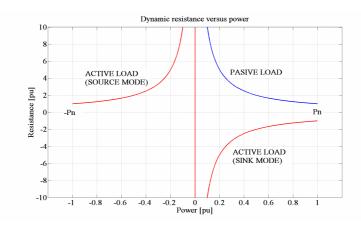

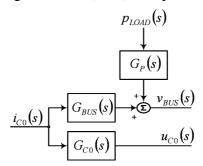

| 5.3. The DC Bus Circuit Model                                                            | 74       |

| 5.3.1. A General Case                                                                    | 74       |

| 5.3.2. PWM Inverter fed Variable Speed Drives as DC bus load                             | 75       |

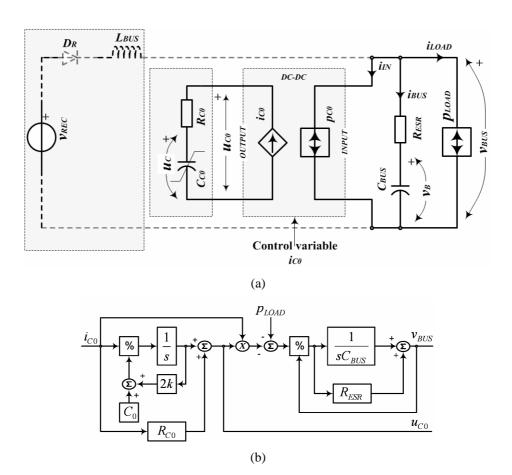

| 5.4. The Entire Conversion System Model                                                  | 76       |

| 5.4.1. Large Signal Model 5.4.2. Linearization and Small Signal Model                    | 76<br>77 |

| 5.4.3. Discussion on the Model                                                           | 79       |

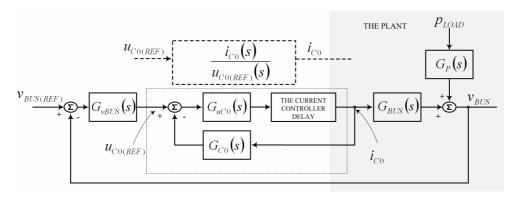

| 5.5. Control Scheme                                                                      | 79       |

| 5.5.1. The Control Objectives                                                            | 79       |

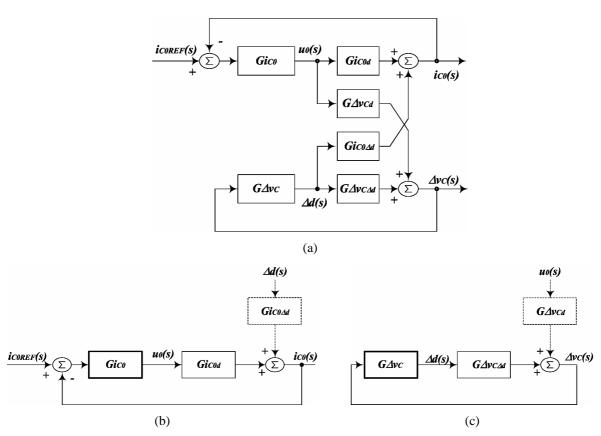

| 5.5.2. Control of the Ultra-capacitor Current and Voltage Balancing Error                | 80       |

| 5.5.3. The Ultra-capacitor and the DC Bus Voltage Control                                | 81       |

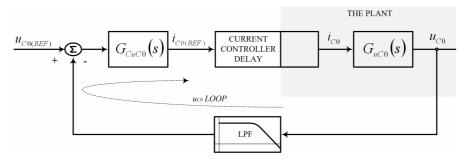

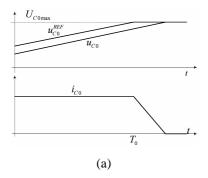

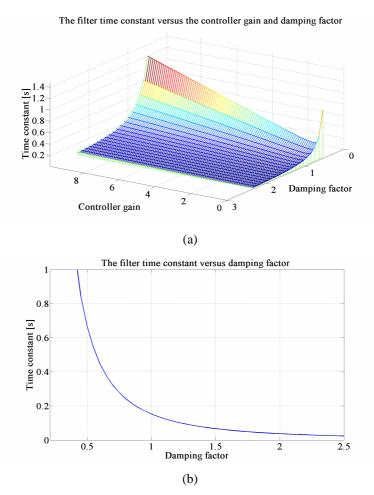

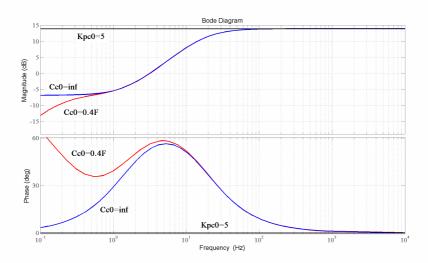

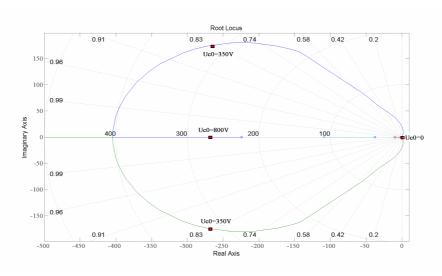

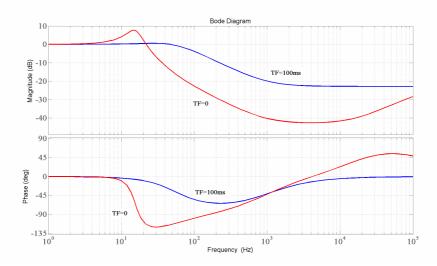

| 5.5.4. The Controller(s) Synthesis                                                       | 84       |

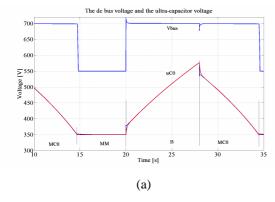

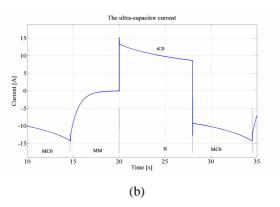

| 5.5.5. Simulation and Experimental Results                                               | 90       |

| 5.5.6. Discussion on the Current Controller Response Time and the DC Bus Voltage Control | 92       |

| 6. Discussion and Conclusions                                                            | 94       |

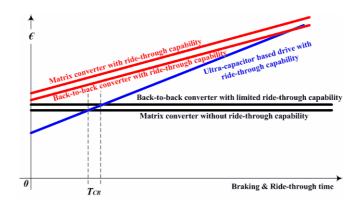

| 6.1. Concept of the Ultra-capacitor Based Controlled Electric Drive                      | 94       |

| 6.1.1. The Drive Immunity on the Mains Power Interruption                                | 94       |

| 6.1.2. The Drive Cost Comparison                                                         | 94       |

| 6.2. Interface DC-DC Converter                                                           | 95       |

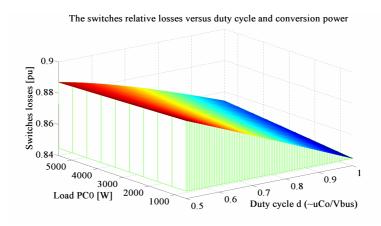

| 6.2.1. Semiconductors Switches                                                           | 95       |

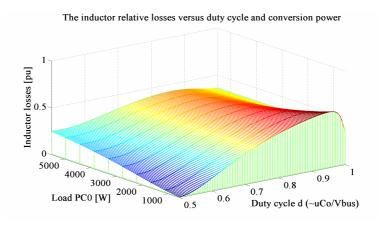

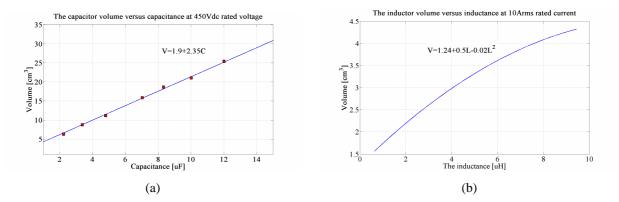

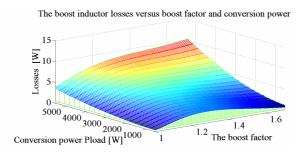

| 6.2.2. Passive Components                                                                | 96       |

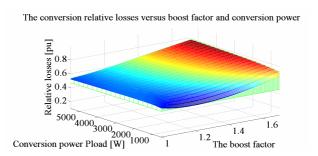

| 6.2.3. Conversion Losses                                                                 | 98       |

| 6.2.4. Model and Control Scheme                                                          | 99       |

| 6.3. Conclusions                                                                         | 100      |

| PART THREE: Three-Terminal Power Factor Correction Device                                | 102      |

| 7. Background and State of the Art                                                        | 103        |

|-------------------------------------------------------------------------------------------|------------|

| 7.1. Background                                                                           | 103        |

| 7.2. State of the Art                                                                     | 103        |

| 7.3. A Novel Half-DC-Bus-Voltage Rated Boost Rectifier                                    | 104        |

| 8. Hybrid Half-DC-Bus-Voltage Rated Boost Rectifier                                       | 106        |

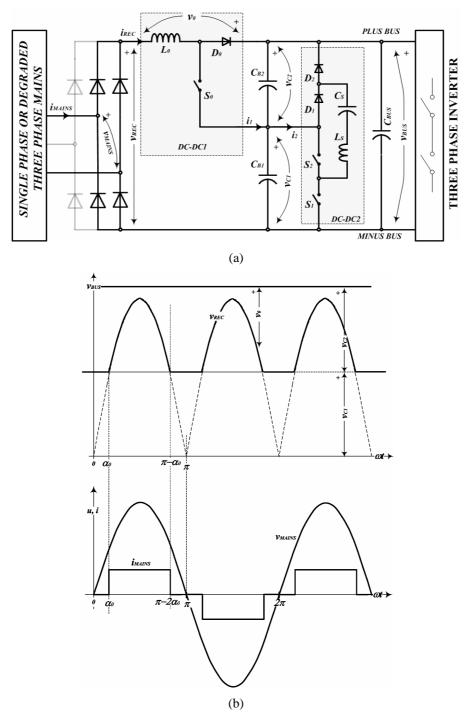

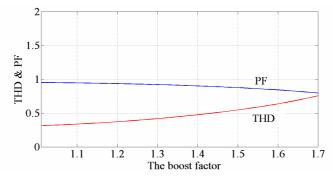

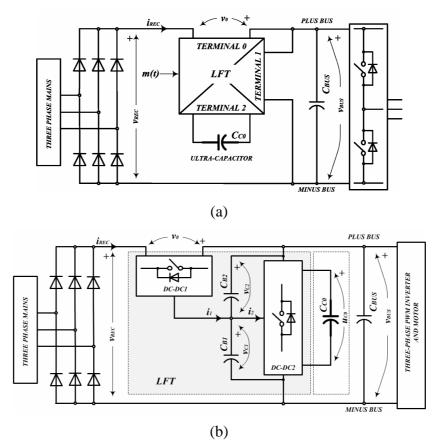

| 8.1. The Basic Principle                                                                  | 106        |

| 8.1.1. The LFT Realization                                                                | 107        |

| 8.1.2. The Mains Current Quality                                                          | 111        |

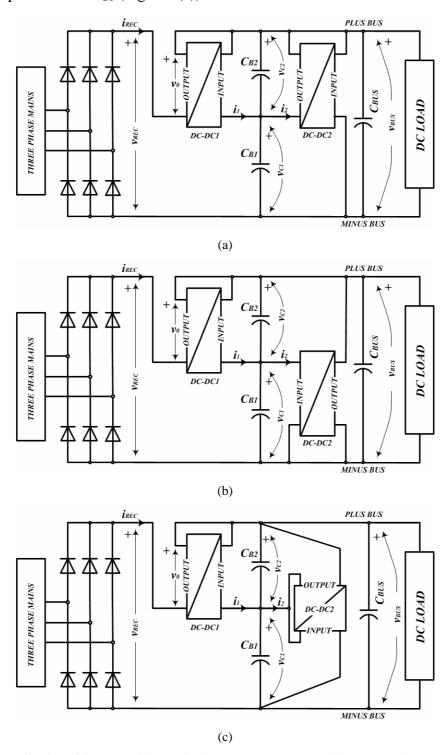

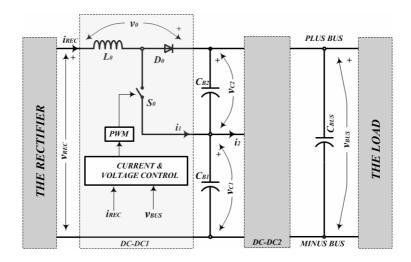

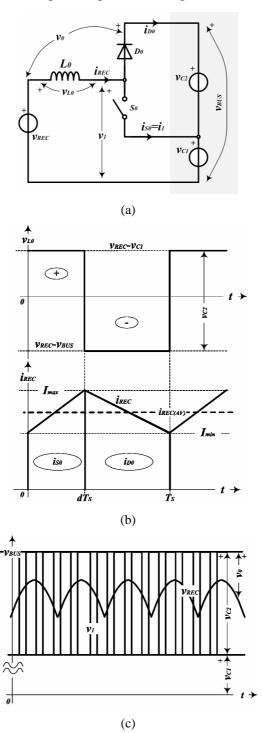

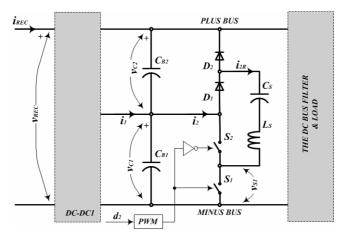

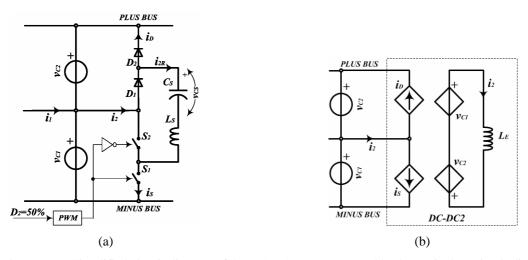

| 8.2. The DC-DC1 Converter                                                                 | 113        |

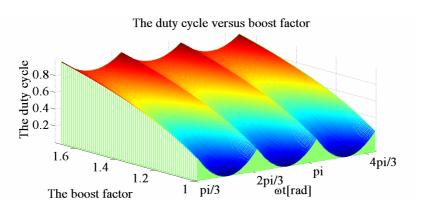

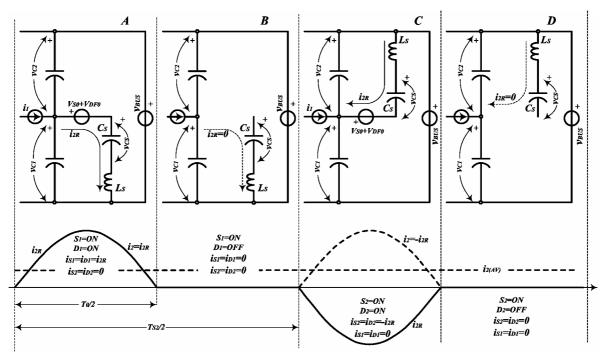

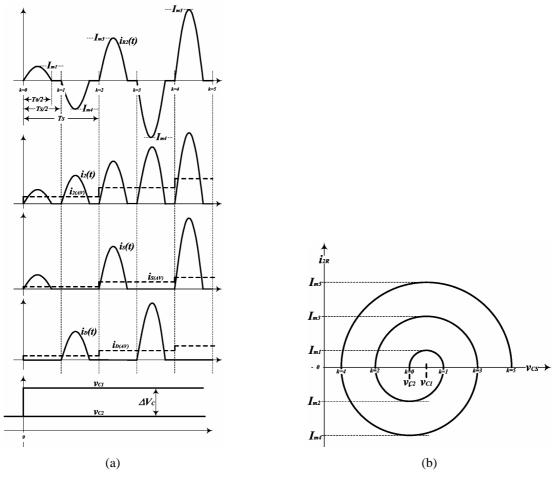

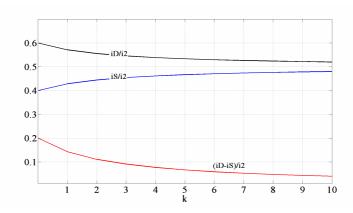

| 8.2.1. Analysis                                                                           | 114        |

| 8.2.2. Design Aspects                                                                     | 116        |

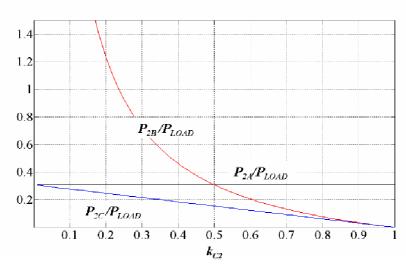

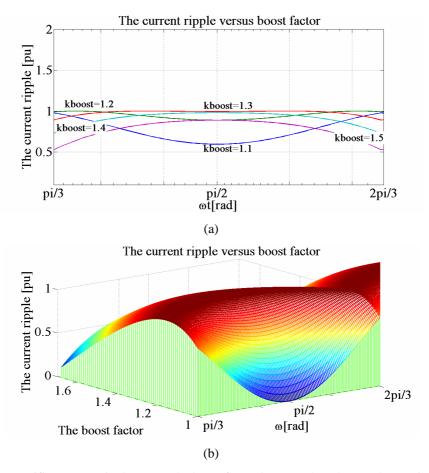

| 8.3. The DC-DC2 Converter                                                                 | 120        |

| 8.3.1. Analysis                                                                           | 120        |

| 8.3.2. Design Aspects                                                                     | 124        |

| 8.4. A Design Example                                                                     | 126        |

| 9. Modeling Aspects and Control Scheme                                                    | 129        |

| 9.1. Model of Series Resonant Converter                                                   | 129        |

| 9.2. The Entire Rectifier Model                                                           | 133        |

| 9.2.1. Large Signal Model                                                                 | 133        |

| 9.2.2. Linearization and Small Signal Model                                               | 135        |

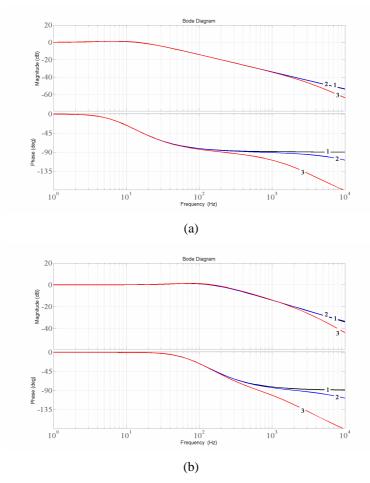

| 9.2.3. Matlab/Simulink Model Verification                                                 | 136        |

| 9.3. Control Scheme                                                                       | 137        |

| 9.3.1. The Control Objective                                                              | 137        |

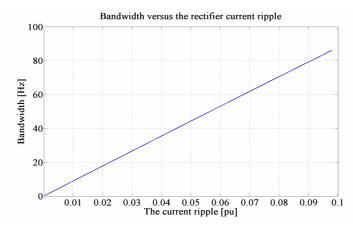

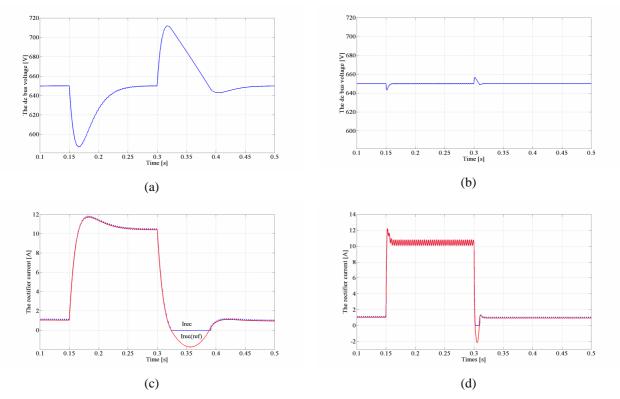

| 9.3.2. The DC Bus Voltage Controller 9.3.3. Matlab/Simulink Simulation Results            | 137<br>140 |

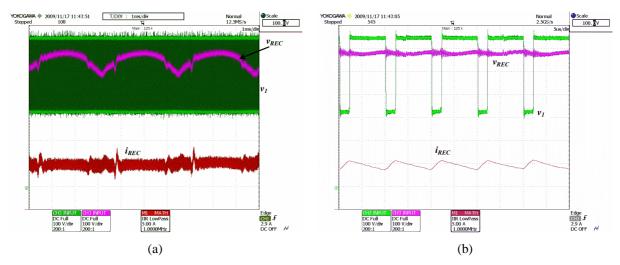

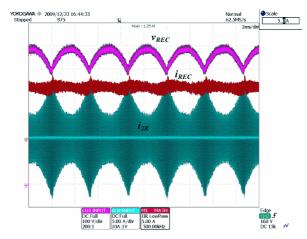

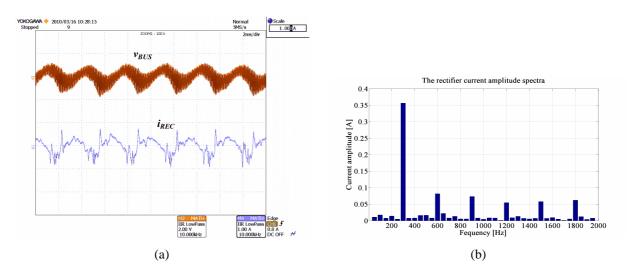

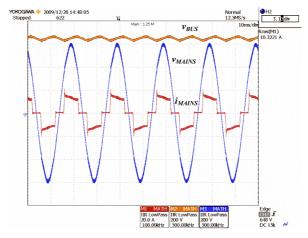

| 9.3.4. Experimental Results                                                               | 141        |

| 10. Single Phase Operation                                                                | 144        |

| 10.1. Short Introduction                                                                  | 144        |

| 10.2. Single Phase Operation of the Half-DC-Bus-Voltage Rated Boost Rectifier             | 145        |

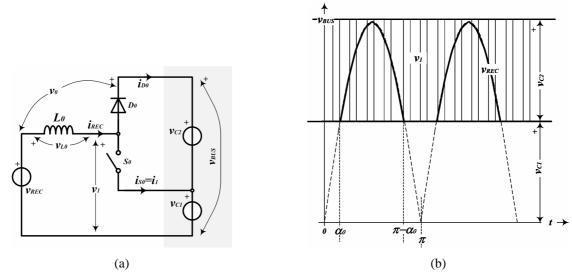

| 10.2.1. The Principle                                                                     | 145        |

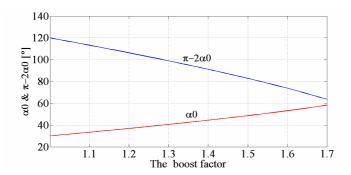

| 10.2.2. A Short Analysis                                                                  | 147        |

| 10.3. The DC-DC1 Converter under Single Phase Supply                                      | 150        |

| 10.3.1. An Ideal Circuit Analysis                                                         | 150        |

| 10.3.2. The Mains Diode Commutation Effect                                                | 151        |

| 10.3.3. The Switch and Boost Diode Stress Analysis                                        | 152        |

| 10.3.4. Boost Inductor                                                                    | 153        |

| 10.4. The DC-DC2 Converter Operation under Single Phase Supply                            | 153        |

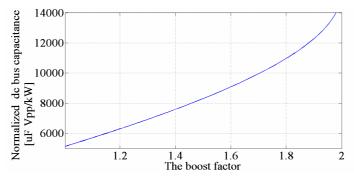

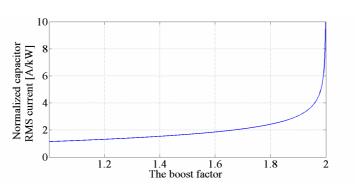

| 10.5. The DC Bus Capacitor Design                                                         | 154        |

| <ul><li>10.5.1. The Voltage Ripple</li><li>10.5.2. The Capacitor Current Stress</li></ul> | 156<br>156 |

| 11. Discussion and Conclusions                                                            | 158        |

|                                                                                           |            |

| 11.1. Comparison with State of the Art Solutions 11.1.1. Three Phase Operation            | 158<br>158 |

| 11.1.1. Three Phase Operation 11.1.2. Single Phase Operation                              | 158        |

| 11.1.2. Shigle Phase Operation 11.2. Three Phase versus Single Phase Supply               | 164        |

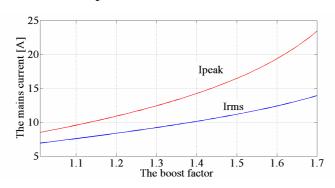

| 11.2. The Mains Current                                                                   | 164        |

| 11.2.2. The Switches Losses                                                               | 165        |

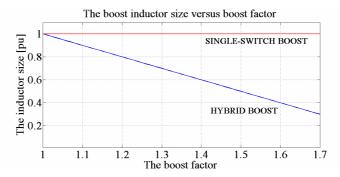

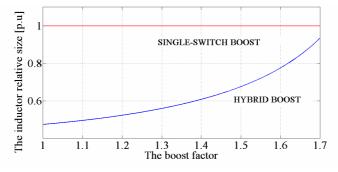

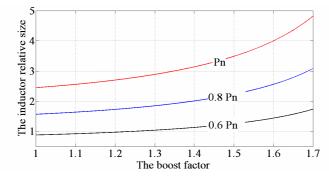

| 11.2.3. The Inductor Size                                                                 | 165        |

| 11.3. Conclusions                                                                         | 166        |

| PART FOUR: Three-Terminal Energy Storage and PFC Device                                   | 167        |

| 12. The Principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 168 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

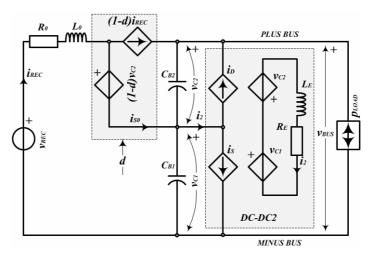

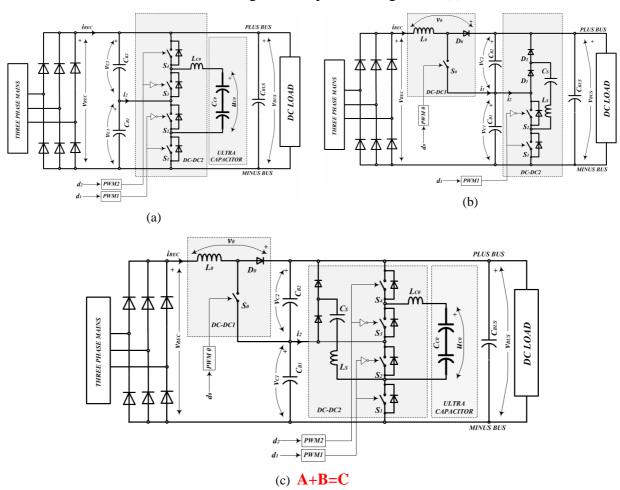

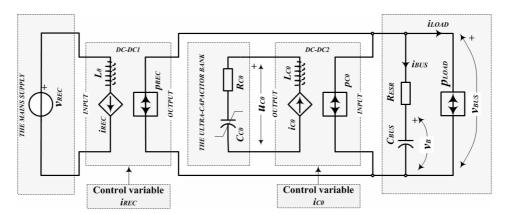

| 12.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 168 |

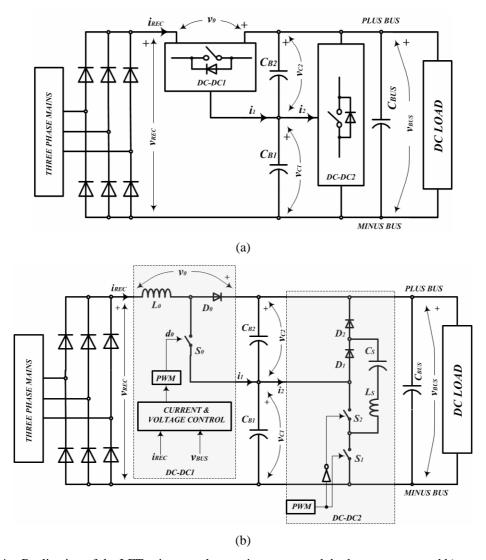

| 12.2. The Principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 168 |

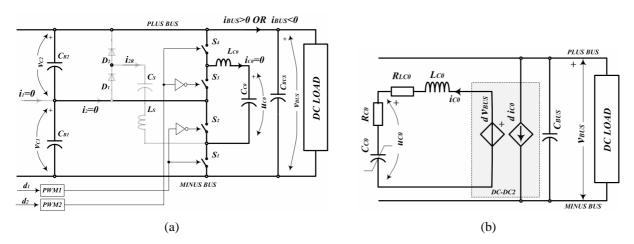

| 12.2.1. The System Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 170 |

| 12.2.2. The DC Bus Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 172 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 175 |

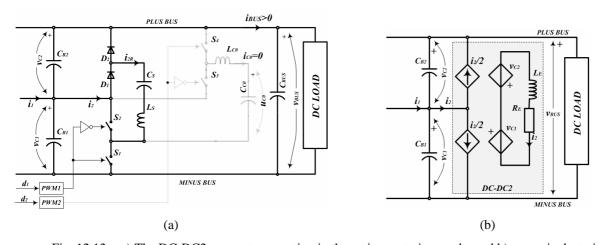

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 175 |

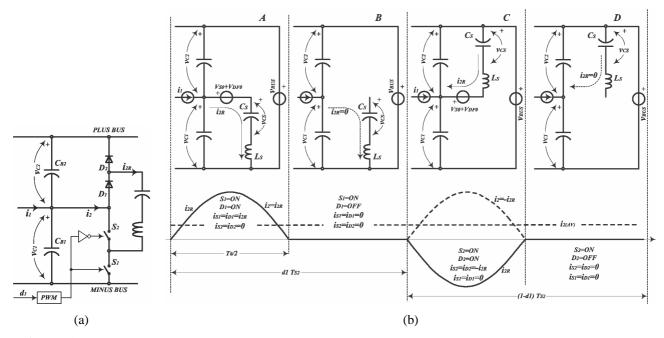

| 12.3.2. The DC-DC2 Converter Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 176 |

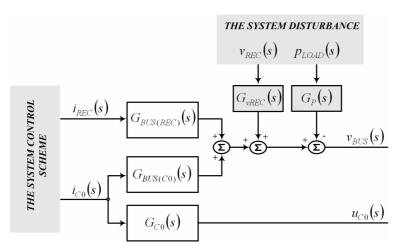

| 13. Modeling and Control Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 182 |

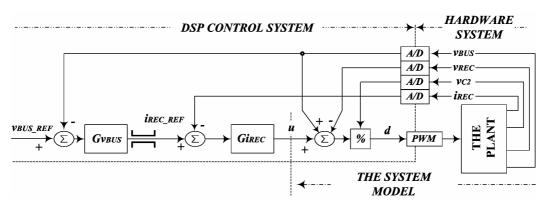

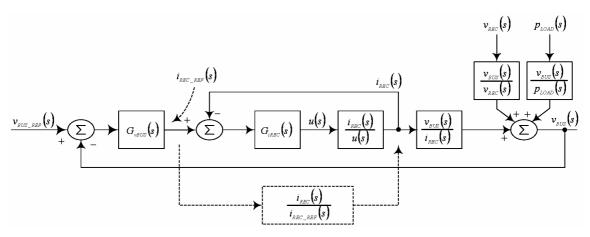

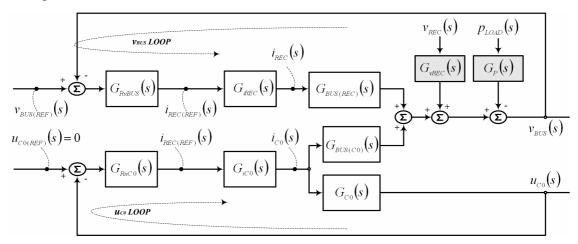

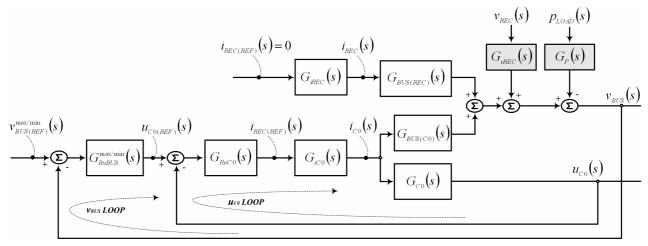

| 13.1. The System Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 182 |

| 13.1.1. Large Signal Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 182 |

| 13.1.2. Small Signal Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 183 |

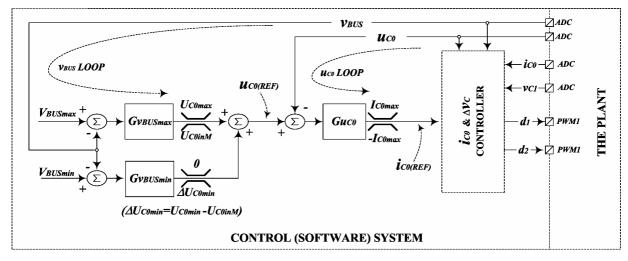

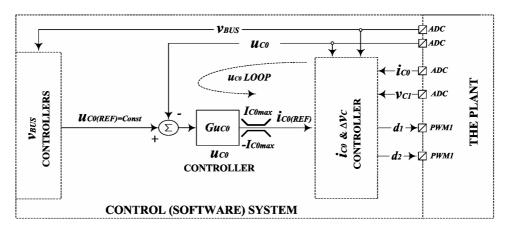

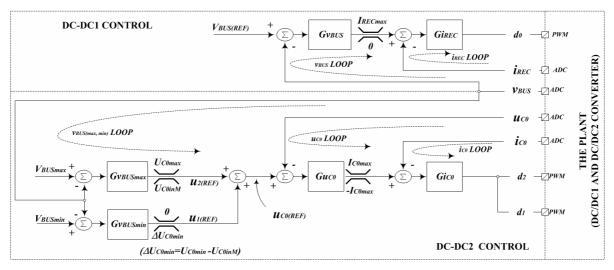

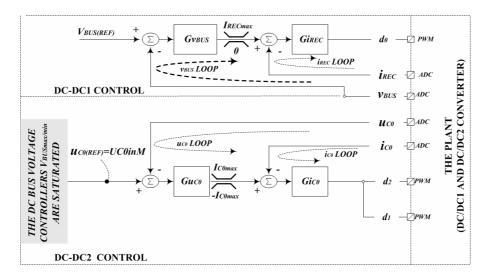

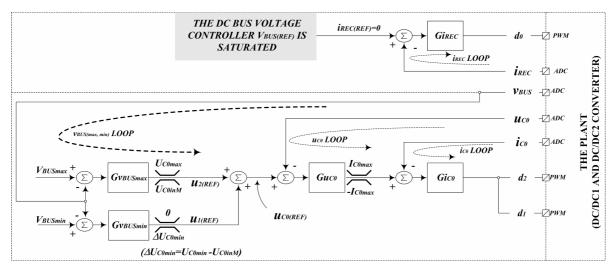

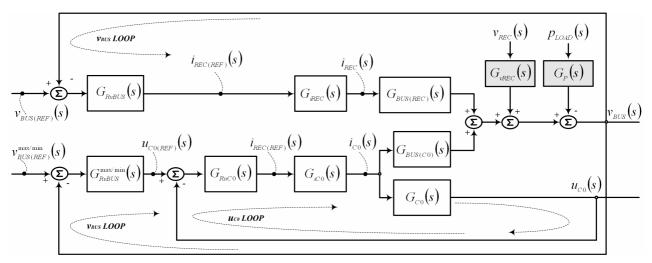

| 13.2. Control Aspects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 184 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 184 |

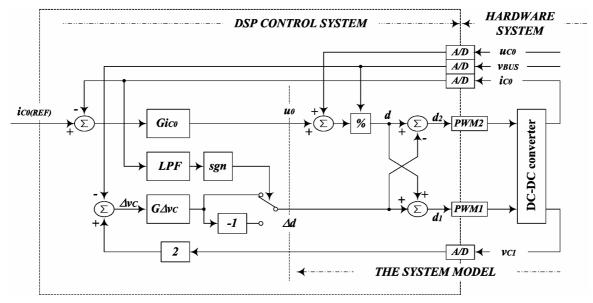

| 13.2.2. Control Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 184 |

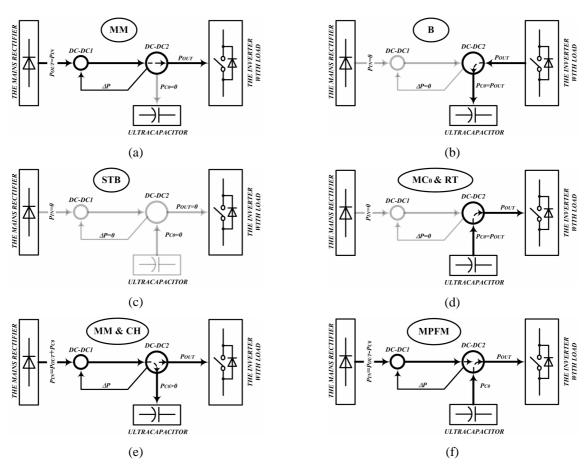

| 13.2.3. Operational Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 184 |

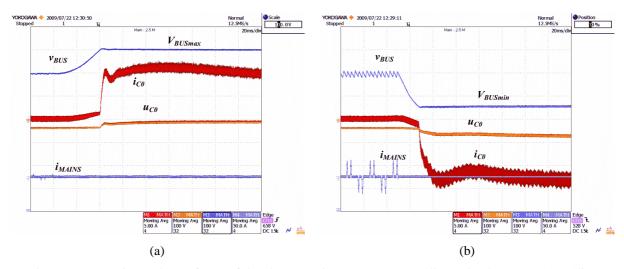

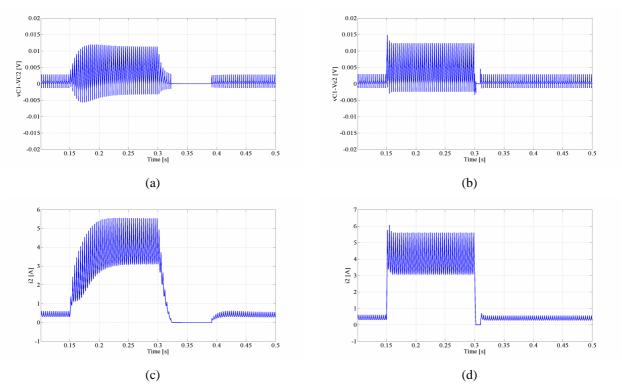

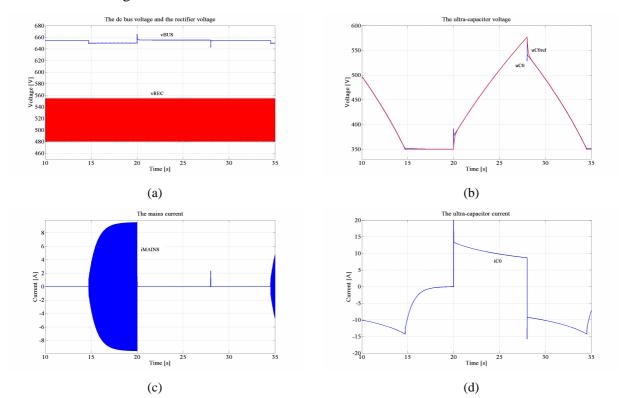

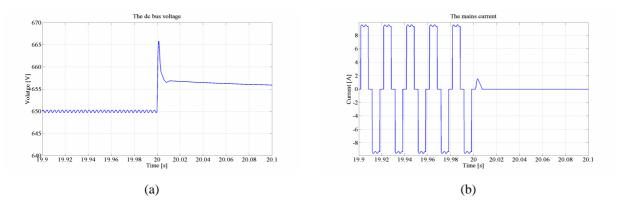

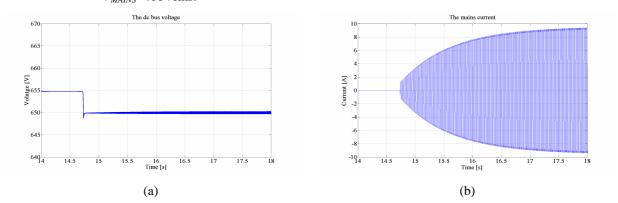

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 189 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 190 |

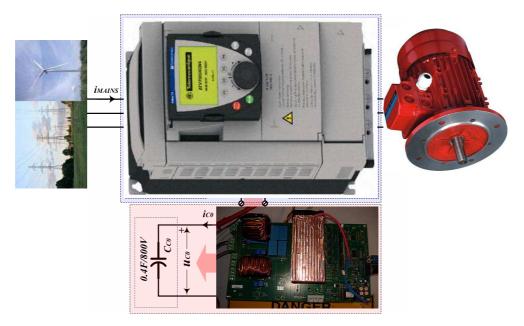

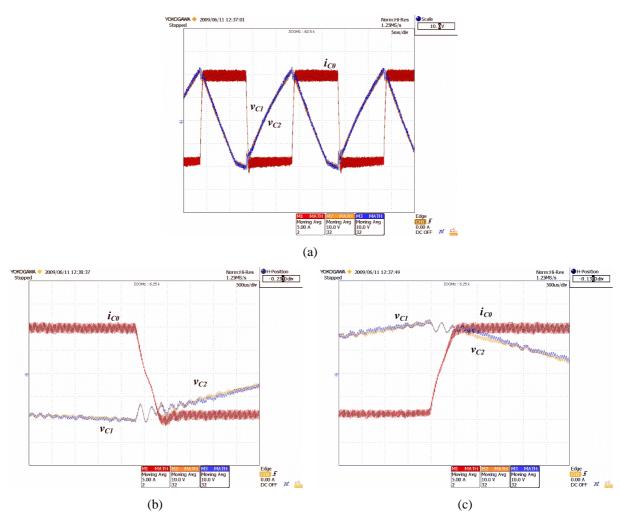

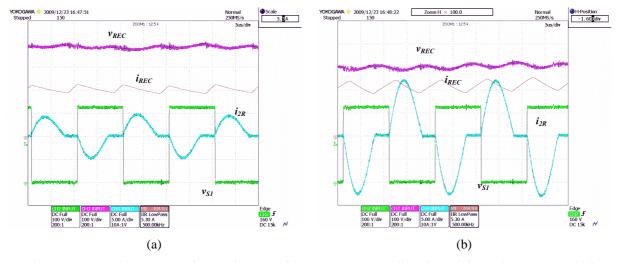

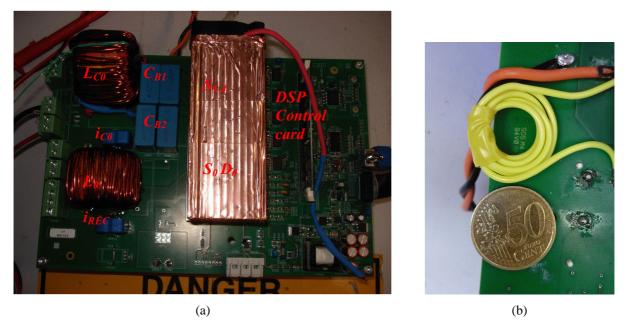

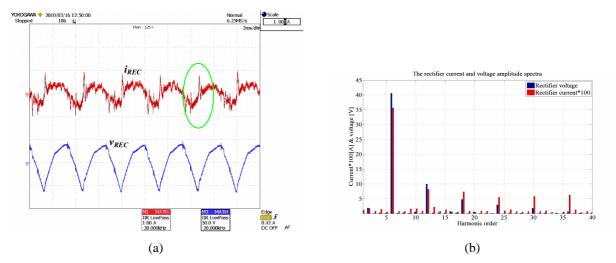

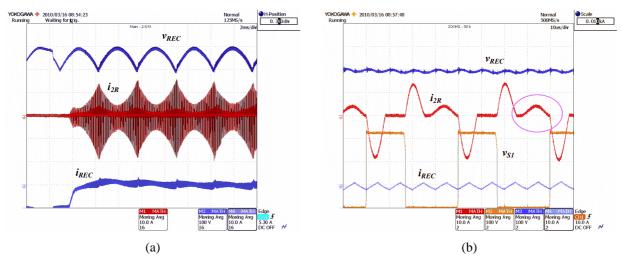

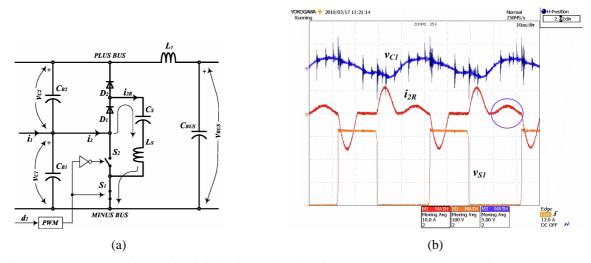

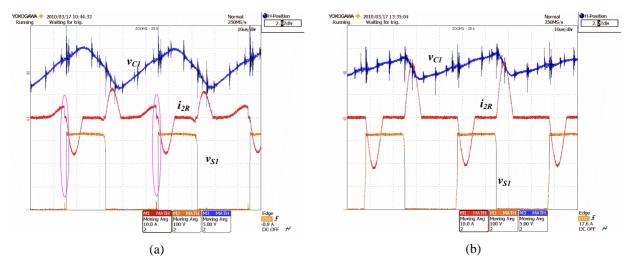

| 13.3.2. Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 193 |

| 14. Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 196 |

| PART FIVE: Concluding Remarks and Perspectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 197 |

| 15. The Dissertation Contribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 198 |

| 16. Conclusions and Perspectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 200 |

| 16.1 General conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 200 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 200 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 201 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 202 |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 202 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 203 |

| 16.2.2. On-line Monitoring and the Ultra-capacitor Life Time Estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 203 |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 204 |

| 12.2. The Principle 12.2.1. The System Operating Modes 12.2.2. The DC Bus Voltage Reference 12.3. Three-terminal Energy Storage and Power Factor Correction Device 12.3. I. Basic Principle 12.3.2. The DC-DC2 Converter Operating Modes  3. Modeling and Control Scheme  13.1. The System Model 13.1.1. Large Signal Model 13.1.2. Small Signal Model 13.2. Control Aspects 13.2.1. The Control Objectives 13.2.2. Control Scheme 13.2.3. Operational Modes 13.3. Simulation and Experiments 13.3.1. Simulation Results 13.3.2. Experimental Results  4. Conclusion  1ART FIVE: Concluding Remarks and Perspectives 15. The Dissertation Contribution 16.1.1. The Ultra-capacitor in Electric Drives and Other Power Conversion Applications 16.1.2. Novel Diode Boost Rectifier 16.1.3. All Together 16.2. Perspectives for Future Work 16.2.1. Commissioning and Self—tuning of the System Controllers 16.2.2. On-line Monitoring and the Ultra-capacitor Life Time Estimation |     |

# PART ONE: INTRODUCTION AND GENERAL CONSIDERATIONS OF THE DISSERTATION

#### 1. GENERAL INTRODUCTION

#### 1.1. Background

#### 1.1.1. Short History of Electric Drives

Through the centuries, "the production power" was the power of animals and slaves, hydro power and wind power. In the 1800s, after the invention of James Watt, it was the power of the steam machine. With the invention of electricity, electrical energy gradually came into focus. The first motors were direct current (DC) motors. At the end of 1800s, Nikola Tesla invented the three-phasevoltage system and the most famous motor; the induction motor was born. Because of many advantages over DC motors, the induction motors became dominant in most constant speed electric drive applications. However, difficulty with speed regulation was the basic disadvantage of the induction motor, and the main limiting factor for application in variable speed applications.

At the beginning of 20<sup>th</sup> century, a few configurations of variable speed drives were used.

- 1) Ward-Leonard motor-generator group. Since power conversion in such a system is done three times and a dc machine is included in the loop, this concept had not been broadly accepted in high power applications.

- 2) Wound rotor induction motor. The motor speed were adjusted and "regulated" by a circuit connected to the rotor via set of brushes, while the stator is connected to the fixed frequency supply. 1) The rotor resistor control and 2) "constant power" Kramer or "constant torque" Scherbious configurations [1].

All these drive configuration were fairly inefficient and faced a problem of reliability.

#### 1.1.1.1. The Early "Power Electronics" Driven ac Drives

The first period in development of "power electronics" controlled electric drives was the period between 1910 and 1940. Early "power electronics" drives were based on triggeredarc power switches, such as controlled mercury-arc rectifiers, thyratrons and ignitrons. The drive configurations were the electronic Kramer configuration using uncontrolled rectifier bridge, electronic Scherbius using rectifier-inverter configuration, Brown Boveri commutatorless drive, thyratron motor configuration and early version of load commuted synchronous motor drive [1]. In 1930s, the first cycloconvertor was used. All those topologies did not have broad success in industrial applications, simply because of complexity and reliability issues of the "power electronics" switches.

In early 1960s, the first silicon controlled rectifier (SCR) was invented. This invention brought a large step in development of power electronics controlled electric drives. Kramer and Scherbius drive configuration, load commuted synchronous motor drives and cycloconvertor drives become dominant in most of high power applications. Later on, current sourced inverter with variable output frequency became a very competitive scheme for induction motor applications. Voltage source drive topologies became competitive with the

invention of the gate turn-off thyristors (GTO) in 1970s and insulated gate bipolar transistors (IGBT) in the 1980s.

#### **1.1.2. Present**

Today, 70 % of the world electricity production is consumed by some kind of controlled electric drives; traction and transportation drives, industrial drives, home appliance drives and so on. This indicates the importance of controlled electric drives in everyday life.

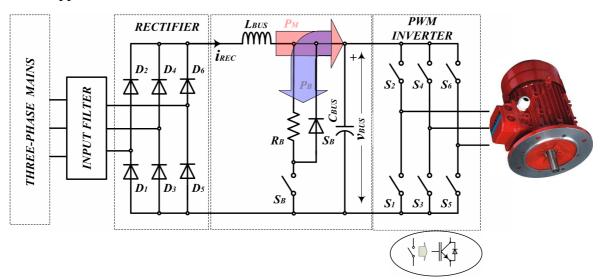

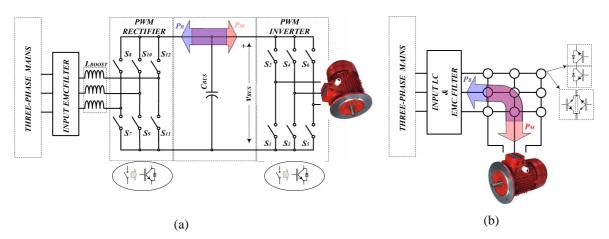

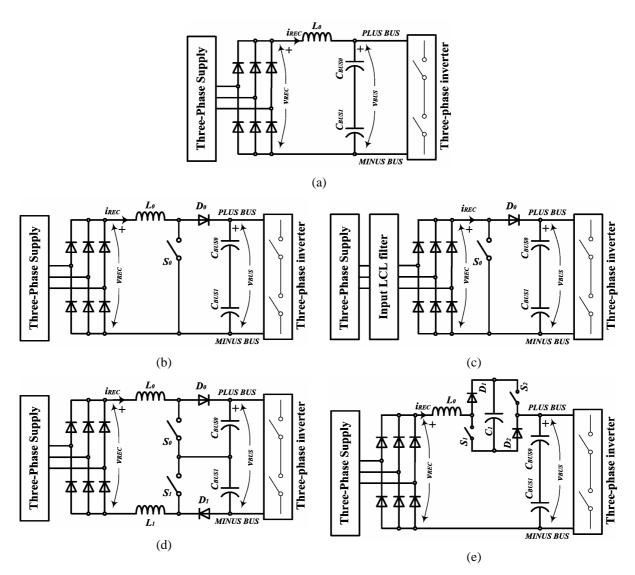

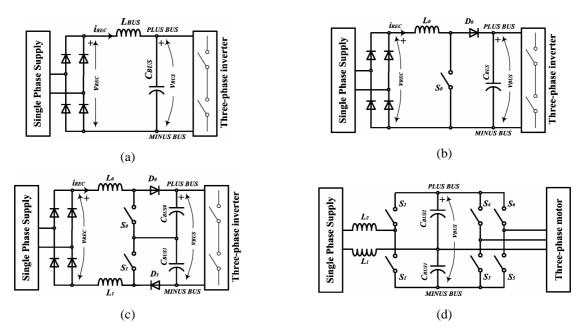

Modern low voltage controlled electric drives are exclusively based on three-phase motors, either induction or permanent magnet synchronous motors [2]-[3]. The motor is powered from a power converter, so-called the drive converter, having variable output voltage and frequency. The drive converter is supplied from low voltage industrial or distributive three-phase mains 230 V to 690V, 50 Hz to 60Hz. The most common converter topology is a cascade-connected diode front-end rectifier and voltage source pulse width modulated (PWM) inverter. A simplified circuit diagram is depicted in Fig. 1.1. The drive converter consists of an input three-phase diode rectifier ( $D_I$ - $D_6$ ), dc bus link with passive filter ( $L_{BUS}C_{BUS}$ ) and pulse width modulated (PWM) output inverter ( $S_I$ - $S_6$ ). The rectifier generates dc bus voltage  $v_{BUS}$ , which is further inverted in the output variable ac voltage via PWM inverter. The input rectifier is based on Si diodes, while the output inverter is exclusively based on IGBT devices [4]. Switching frequency falls in range of few kHz up to 20kHz. The PWM inverter is controlled from the upper level controller using some of advanced digital control techniques. The control objective is the control of the motor torque and speed in closed or open loop control mode [3].

An additional switch  $S_B$ , diode  $D_B$  and resistors  $R_B$ , so-called brake chopper and resistor are used in applications with a demand for braking of the drive load (hoisting and large inertia applications). The braking energy is dissipated in the brake resistor  $R_B$  via the brake chopper  $S_B$   $D_B$ . This is, in fact, one of the most limiting factors for advanced high efficient drive applications.

Fig. 1.1 State of the art low voltage drive converter based on voltage source indirect AC-DC-AC conversion. The output voltage is pulse width modulated (PWM) having fundamental voltage that is adjustable in amplitude, frequency and phase.

#### 1.1.3. Typical Applications of Controlled Electric Drives

#### 1.1.3.1. Hoisting and Lift Applications

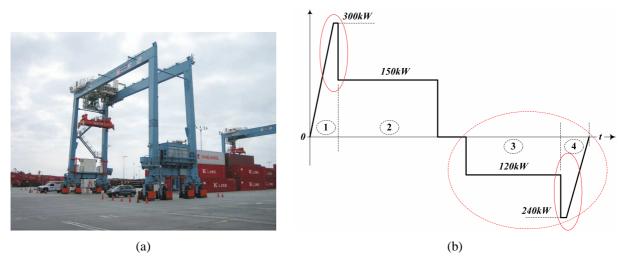

The first type of applications that are in the scope of this project are hoisting type applications. Fig. 1.2 (a) shows photography of one typical on-port rubber tyred gantry (RTG) crane [5]. The hoisting drive time-power profile is sketched in Fig. 1.2 (b). When lifting the load, the hosting drive takes energy from the primary supply, in this case a diesel engine generator. When lowering the load, the drive operates in braking mode. As a diesel engine generator is not reversible, the braking energy cannot be pumped back into the primary power source. Instead, it is dissipated as heat in the brake resistor.

Fig. 1.2 a) Rubber tyred gantry crane. b) Typical power profile of a hoisting application: lifting the load and acceleration (1), lifting the load at constant speed (2), lowering the load at constant speed (3) and lowering the load and deceleration (4).

Lift applications are similar to the RTG crane applications, except for two differences. The mains as the primary power supply source in lift applications is reversible. This means that the drive braking energy can be pumped back to the mains. The lift load (cabin) is balanced with a counterweight. Thus, the drive operating mode depends on the load direction (up or down) and ratio of the load to the counterweight.

#### 1.1.3.2. Machines with Intermittent Load

The second type of application to consider is industrial machines with intermittent load. Such applications are characterised by low ratio of average to peak power. The input power is highly positive when the drive accelerates, and the power is highly negative when the drive decelerates. During constant speed operation, the input power is normally low. Fig. 1.3 illustrates the time-power profile of such a drive application. Typical application is tools carriers in automatic milling machines [3].

Fig. 1.3 Typical power profile of a controlled electric drive applied in a machine with cycling load: acceleration (1), constant speed (2), and deceleration (3).

#### 1.1.3.3. Blowers and Pumps Applications

These applications are normally the simplest controlled electric drive applications. Blowers and pumps do not require specific control scheme and do not require braking (at lest do not require fast braking). In some cases, those applications can be sensitive to the mains power interruptions if applied in critical process industry.

Low power irrigation pump systems are specific application because the mains supply is often single-phase network. The motor is a three-phase induction motor powered from a three-phase PWM inverter.

#### 1.1.4. Remaining Technical Issues in Application of Controlled Electric Drives

Six technical issues in application and design of modern variable speed drives can be identified. Those issues are still a great challenge for power electronics researchers and drive designers [6].

#### 1.1.4.1. Saving and Recovery of the Drive Braking Energy

A lot of industrial and other applications, such as lifts, cranes and tooling machines are characterized by low balance between the input average power and peak power. Moreover, such applications have a demand for braking at full power. In ordinary variable speed drives, the mechanical energy stored in rotating mass of the motor load and the motor shaft is usually realized and wasted in a braking resistor. The energy losses in such applications go up 20 to 50% of the consumed energy. In today's energy crisis, energy efficiency has become the issue that needs an urgent solution [6].

#### 1.1.4.2. The Drive Ride-Through Capability

Modern controlled electric drives are sensitive to the mains supply disturbances. The most frequent disturbances are voltage dips/sags. A voltage sag is defined as instantaneous decrease in the RMS voltage, where the decrease is in range of 10 to 90% of the nominal voltage, while the sag duration is in order of a half cycle up to a minute [7]-[11]. Such a power interruption causes the dc bus voltage to drop below its lower limit, and then the entire drive system trips. The system interruptions are very costly and unacceptable when the drive is applied in critical process industry, oil pump systems, semiconductor and glass industry.

Such kind of industries have reported losses ranging from 10k\$ to 1M\$ per disrupting event [10].

#### 1.1.4.3. Quality of the Drive Input Current

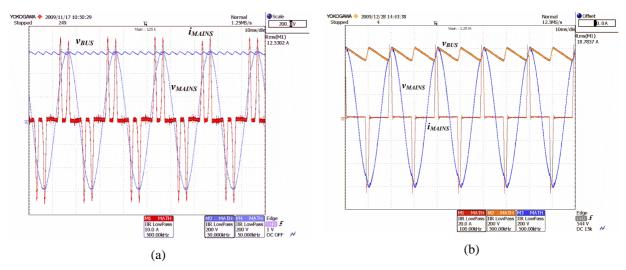

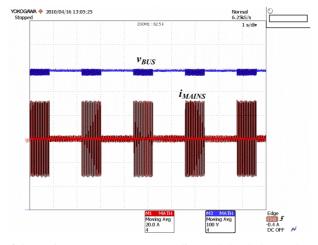

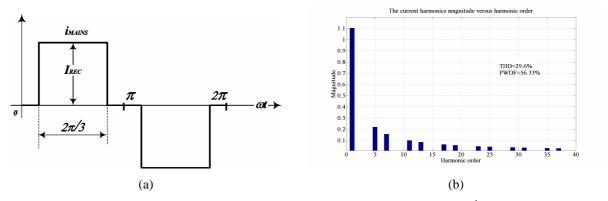

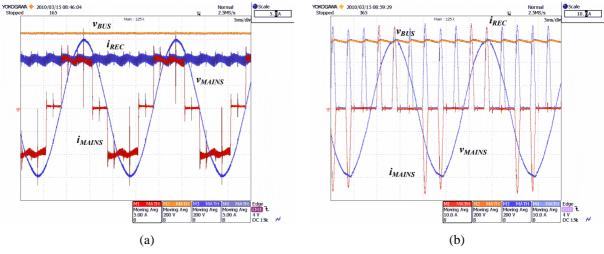

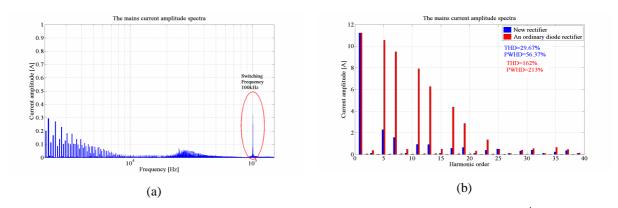

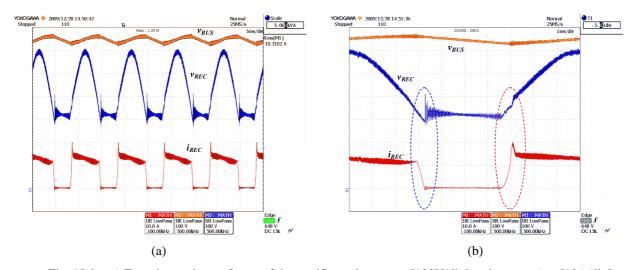

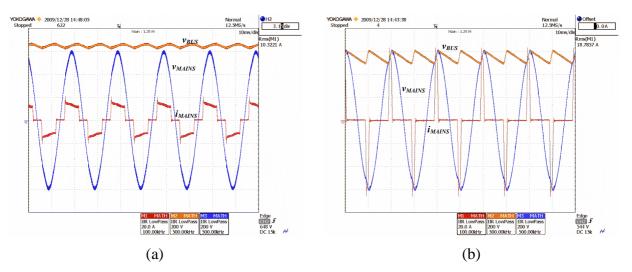

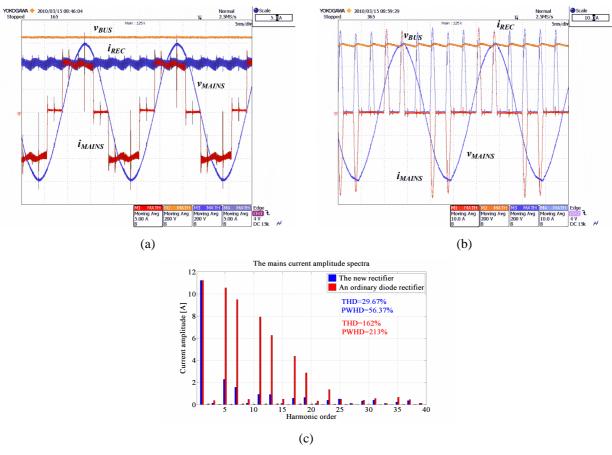

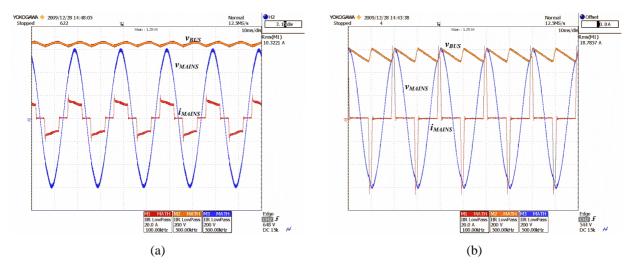

Another power quality issue, which is introduced by the drive itself, is quality of the drive input current. Harmonic spectra of the drive input current depends on the drive rectifier topology. Ordinary diode front-end rectifiers equipped with passive LC filter draws the input current that is distorted and rich with higher harmonics. An example set of waveforms is depicted in Fig. 1.4 (a). Total harmonic distortion (THD) factor can be as high as 150%, or even higher [12].

The mains current harmonics cause additional heating and stress of the distribution transformers, power factor correction capacitors and neutral line in low voltage distribution network. Electromagnetic interference (EMI) with communication network and sensitive equipment is a critical issue too. To avoid or at least minimize those problems, advanced controlled electric drive converters have to comply with the input current harmonics limitations defined by international standards [13].

#### 1.1.4.4. Quality of the Drive Converter DC Bus Voltage

The dc bus voltage is the intermediate voltage in the conversion path from the mains supply to the motor terminal. To achieve full motor voltage without distortion, it is important to provide sufficient dc bus voltage without significant fluctuation and ripple. Moreover, the higher dc bus voltage the better performance of the motor current and torque control [3].

The ordinary diode rectifier provides the dc bus voltage that is lower than the mains phase-to-phase peak voltage. The voltage ripple at 6<sup>th</sup> harmonic of the mains frequency is significant too. An example set of waveforms is depicted in Fig. 1.4 (a). The motor voltage, therefore, is not well controlled in case that the drive operates in full speed mode. This causes distortion of the motor flux and ripple in the motor torque. Negative effects of that are well known: oscillations and mechanical stress of the load machine, noise and vibrations.

#### 1.1.4.5. Single Phase Supply with or without the Drive De-rating

Operation of three-phase variable speed drives on single-phase supply is an application issue to be considered too. Single-phase supply could be due to the mains degradation when one of three phases is disconnected. In that case the drive rectifier is supplied with one phase-to-phase voltage. From the rectifier side it is nothing other than a single-phase supply. Another application example is rural single-phase supply network or specific drive applications, such as irrigation and small water supply systems.

Ordinary single-phase supplied diode front-end rectifiers draw an input current that is distorted and rich with higher harmonics. An example set of waveforms is depicted in Fig. 1.4 (b). The current peak is 5 to 10 times greater than the first harmonic current. This causes significant losses in the dc bus capacitor and input rectifier bridge. To be able to continuously operate under such conditions, the drive power has to be reduced to less than 40% of the drive rated power.

#### 1.1.4.6. Smoothing of the Drive Peak Power

Some controlled drive applications are characterized by low ratio of the average to peak power. Typical examples are lifts and hosting applications, and industrial tolling

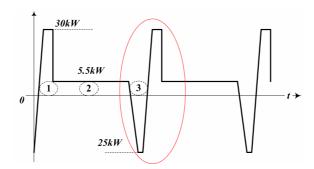

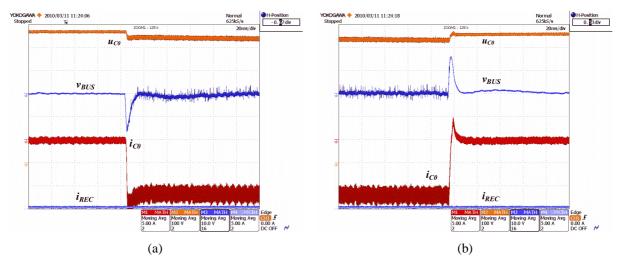

machines having intermittent load. Fig. 1.5 shows waveforms of the mains current  $i_{MAINS}$  and dc bus voltage  $v_{BUS}$  of an example controlled electric drive application. Peak power is 5500W for 0.8s, while minimum power is 500W for 1.6 s. It gives the ratio of average to peak power of 0.31. Thus, the drive cabling, fuses and contactors have to be over-sized by factor of 3. This type of load may also cause fluctuation and flicker in weak supply networks [14]. In lift applications the peak to average power ratio could be greater than 10, as reported in [15].

Fig. 1.4 Waveforms of the mains current, voltage and the dc bus voltage. a) Three-phase supply,  $P_{LOAD}$ =5500W, the current scale [10A/div]. b) Single phase supply,  $P_{LOAD}$ =4000W, the current scale [20A/div].

Fig. 1.5 Waveforms of the mains current  $i_{MAINS}$  [20A/div] and the dc bus voltage  $v_{BUS}$  [100V/div]. The drive load is cycling between 500W and 5500W at period of 2.2s with duty cycle of 30%. The average power is approximately 31% of the peak power.

#### 1.2. Literature Overview

#### 1.2.1. Regenerative Drives Based on Back to Back and Matrix Converter

Most of the existing regenerative controlled electric drive solutions belong to two groups; back to back PWM rectifiers [16], and so-called direct (matrix) converters, [17], [18].

Fig. 1.6 shows simplified circuit diagram of voltage source back-to-back and matrix drive converters. The drive takes energy from the mains whenever operates in motoring mode, and pumps the energy back to the mains whenever operates in breaking mode. The main disadvantage of such solutions is the fact that functionality and reliability of the drive is strongly linked to the mains reliability. Simple speaking, any power interruption of the mains is reflected on the drive. The drive is disabled whenever the mains is interrupted for longer than the mains cycle (20ms). Moreover, these drives have a high power demand during acceleration and deceleration (low ratio of average to peak power). This modulated input power produces additional losses and disturbances (flicker) in the weak supply mains.

Fig. 1.6 a) Voltage source back to back regenerative controlled electric drive. b) Voltage source matrix drive converter.

#### 1.2.2. Regenerative Drives Based on the Energy Storage Concept

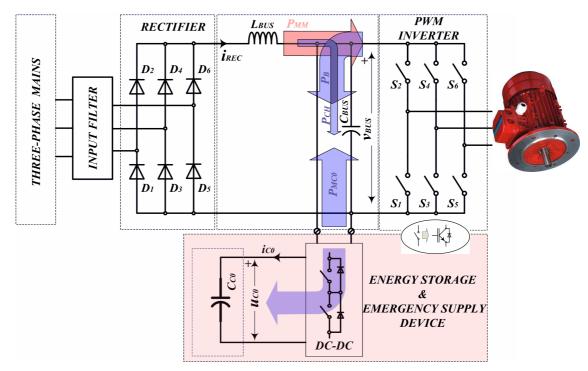

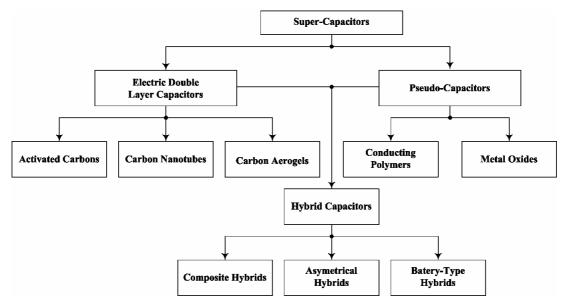

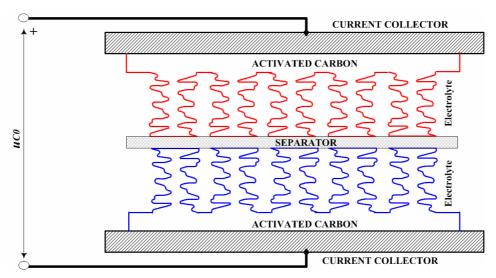

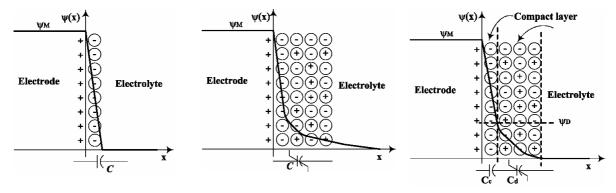

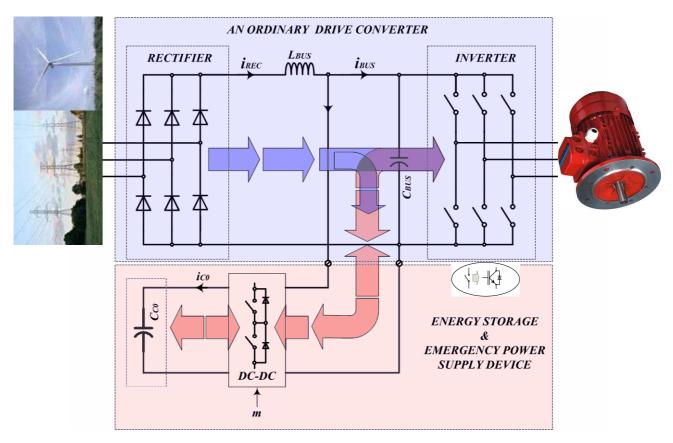

A block diagram of a regenerative drive based on energy storage concept is given in Fig. 1.7. The drive system consists on an ordinary diode front-end converter equipped with an energy storage device [19]-[24]. This concept has come into focus recently with broad application of new electro-chemical double layer capacitors (EDLC), so-called ultra-capacitors [26]. An ultra-capacitor is electro-chemical capacitor having two porous electrodes made of activated carbon that are separated by a separator and impregnated with electrolyte [26]. Thanks to large specific surface (2000m²/g) of activated carbon electrodes, the specific capacitance and energy are much higher than for standard electrolytic capacitors. In addition, the specific peak power of the ultra-capacitors is much higher than peak power of the existing electro-chemical batteries. Flywheel energy storage is usefully used in such a drive concept too [24].

The kinetic energy of the drive rotating masse, so-called braking energy is stored into the ultra-capacitor during the drive braking sequence. During the next motoring sequence, the energy is restored from the ultra-capacitor and realized on the drive. The first commercial applications of the ultra-capacitor based regenerative drives were traction and hybrid car drives [27]-[29]. General purpose variable speed drive with such an energy saving concept could be used in lift and hoisting applications, tooling machines having high demand for frequent and fast start/stop sequence, and many other application having a demand for braking. In [5], such a drive concept is analyzed and successfully applied on the rubber tyred gantry (RTG) crane. As reported in [5], the fuel saving is 30% to 40%. Moreover, the diesel

gen-set can be re-sized and smaller unit could be used. The same drive concept has been proposed for building lift applications [20], [15]. The ultra-capacitor as the energy storage for short term UPS function or extension of the drive ride-through capability is applied in critical industrial applications [21], [22].

Fig. 1.7 Controlled electric drive based on an ordinary drive converter with parallel connected energy storage and emergency power supply device.

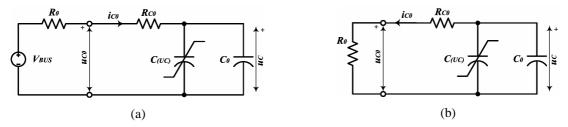

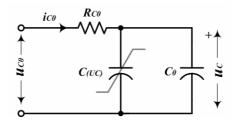

Unlike electrochemical battery, the ultra-capacitor state of charge strongly depends on the capacitor terminal voltage. The capacitor voltage varies a lot when the capacitor is charged/discharged. That means the ultra-capacitor cannot be connected directly to the drive dc bus, because the voltage adaptation and matching between the ultra-capacitor and dc bus. To achieve flexibility and high efficiency, a dc-dc power converter is used as a link between the ultra-capacitor and the drive [30]-[42].

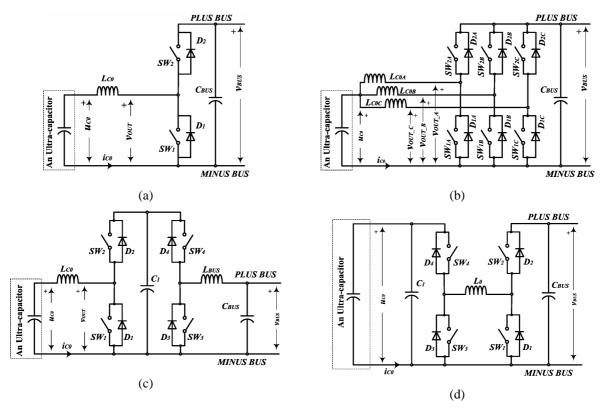

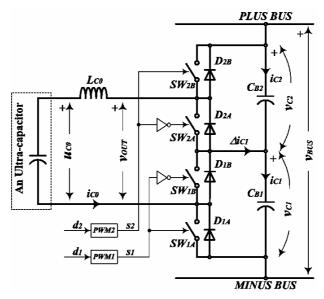

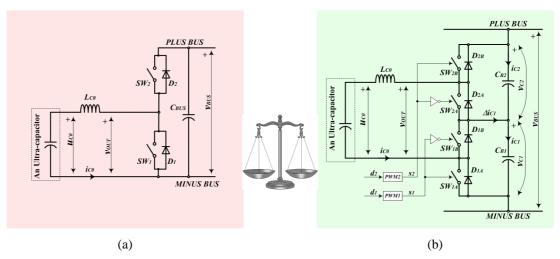

Most of dc-dc converter topologies are based on the ordinary two-level single-phase or multiphase interleaved topologies [5], [30]-[35]. The main drawback of these topologies is the switches voltage rating. The switches are rated on the full dc bus voltage. As the dc bus voltage may go up to 800V, even more, the switches are rated on 1200V. This becomes an issue if the converter switching frequency is quite high; let us say above 20kHz. Switching losses become quite significant. It causes degradation in the conversion efficiency and additional difficulties in the converter thermal design. Two-level dc-dc converter with soft switching has been presented in [36]. This solution offers lower switching losses. However, since the converter operates in discontinuous conduction mode (DCM), the peak current and ripple current are significantly greater than one that operates in continuous conduction mode (CCM). This causes a problem of the inductor losses, particularly the core losses. Moreover, additional losses on the ultra-capacitor internal resistance cannot be neglected if the output current is not well filtered. Isolated dc-dc converter topologies with soft switching have been analyzed in [37], [38]. These topologies are attractive solutions when ratio of the dc bus voltage to the ultra-capacitor voltage is high, greater than 2. If the ratio is lower than 2, the

efficiency is lower than that of a non-isolated ordinary topology. Three-level converters are well adopted solution in applications with high input voltage and relatively high switching frequency [39]- [40]. The switches are stressed on half of the total dc bus voltage. This allow us to use lower voltage rated switches having better switching and conduction performance compared to the switches rated on the full blocking voltage. Therefore, the converter overall performances, including cost and efficiency, can be significantly improved compared to two-level converters, especially when the switching frequency is above 20kHz or MOSFETs are used [41].

Most of the control methods presented in the literature are focused on hybrid electric vehicle and power sources [14], [27]-[29], [32]-[35], [43]-[47]. Only a few publications are focused on control of the ultra-capacitor based electric drives [5], [21]-[22].

#### 1.2.3. The Mains Current Harmonics and Related Issues

The energy storage based electric drives provide a more efficient way to save braking energy and improve global efficiency and reliability of the controlled electric drive systems [48]. The input current quality, however, remains an unsolved challenging issue. In the last decade, numerous different solutions for this problem have been proposed and discussed in literature.

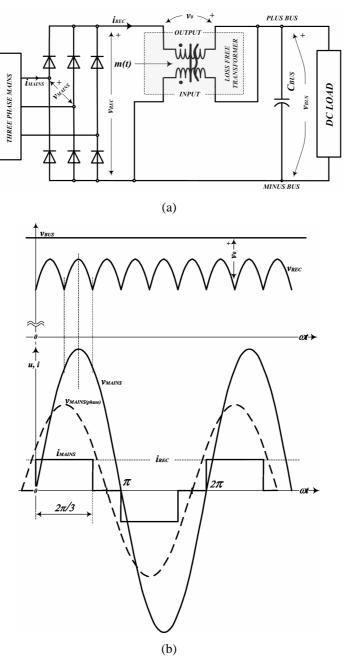

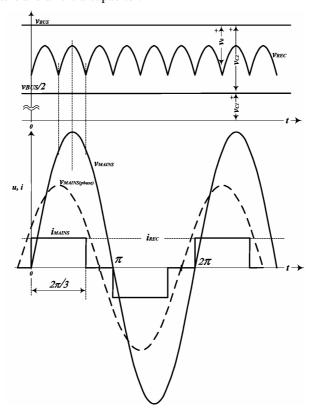

Single-switch three-phase continuous conduction mode (CCM) boost rectifier is a solution that offers numerous advantages compared to the ordinary diode front-end rectifier [49]-[51]. The rectifier output current is constant and therefore the mains current is  $2\pi/3$  square waveform with THD of approximately 30%. The dc bus voltage is actively controlled and boosted above the mains phase to phase peak voltage. The low frequency voltage ripple is small and it could be neglected compared to that of the diode rectifier. A variant of the CCM boost rectifier is discontinuous conduction mode (DCM) boost rectifier [52]-[55]. This topology offers lower THD of the input current than CCM boost rectifier (10-15% in comparison to 30%).

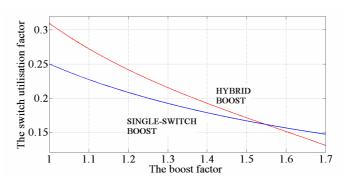

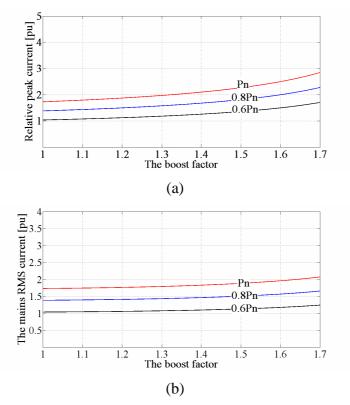

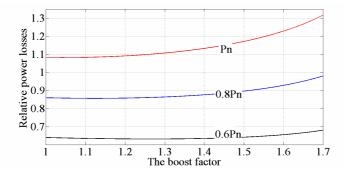

A common disadvantage of the single-switch boost topologies is power rating of the semiconductor switches. The switches are rated for the full dc bus voltage and full rectifier current. Generally speaking, a semiconductor switches' performance; conduction and switching strongly depend on the switch voltage rating and the switch technology. Lower voltage rating means lower conduction losses, better switching performance, higher efficiency and lower cost. For example, let us consider a 400V three-phase rectifier. The dc bus voltage is 700 to 800V. For the ordinary single-switch boost converter, the switch and boost diode voltage rating is 1000V to 1200V. For this voltage rating, 1200V IGBT and 1200V fast diode are used. In this case, maximum switching frequency is limited by the switching performance of the IGBT and the diode. To reduce switching losses, soft switching techniques can be used [56]-[58]. However, the soft switching techniques require additional active switches, diodes and passive resonant circuits, which make the circuit more complex and expensive.

Double-boost rectifiers employ two interleaved active switches and boost diodes. The switches and diodes are rated for half dc bus voltage and full rectifier current. As a result, the conversion losses are slightly lower in comparison to the single-switch boost rectifier [59]. The boost inductor is approximately 25% that of the single-switch topology.

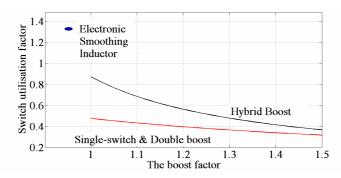

A dc side shunt active filter, applied on a single-phase diode rectifier has been analysed in [60]. The filter circuit is connected on the rectifier dc side, and as such it is simple and cost effective in comparison to the state of the art ac side connected active filters. This approach could be extended to three-phase rectifiers, wherein the input current THD can be