# Méthodes et outils de génération de code pour les plateformes multi-cœurs fondés sur la représentation de haut niveau des applications et des architectures

A. Elmrabti

### ▶ To cite this version:

A. Elmrabti. Méthodes et outils de génération de code pour les plateformes multi-cœurs fondés sur la représentation de haut niveau des applications et des architectures. Micro et nanotechnologies/Microélectronique. Université de Grenoble, 2010. Français. NNT: . tel-00568999

## HAL Id: tel-00568999 https://theses.hal.science/tel-00568999

Submitted on 24 Feb 2011

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITE DE GRENOBLE

N° attribué par la bibliothèque 978-2-84813-162-7

## <u>THÈSE</u>

Pour obtenir le grade de

## DOCTEUR de L'UNIVERSITÉ DE GRENOBLE

Délivré par l'Institut Polytechnique de Grenoble

Spécialité : Informatique

préparée au laboratoire TIMA

dans le cadre de l'école doctorale «Mathématiques, Sciences et Technologies de l'Information, Informatique »

Présentée et soutenue publiquement par

## **Amin EL MRABTI**

Le 08 Décembre 2010

#### **Titre**

Méthode et outils de génération de code pour les plateformes multi-cœurs fondés sur la représentation de haut niveau des applications et des architectures

## Jury

| Mr. Ahmed JERRAYA,     | Président,            |

|------------------------|-----------------------|

| Mr. Fabrice KORDON,    | Rapporteur,           |

| Mr. François TERRIER,  | Rapporteur,           |

| Mr. Emmanuel VAUMORIN, | Examinateur,          |

| Mr. Frédéric PÉTROT,   | Directeur de thèse,   |

| Mr. Frédéric ROUSSEAU, | Co-directeur de thèse |

### Remerciements

Au terme de ce travail, je tiens à exprimer mes remerciements envers toutes les personnes qui ont contribué, à des degrés divers, au bon déroulement de ce travail.

Je remercie vivement mon directeur de thèse Mr Frédéric Pétrot, responsable du groupe SLS au laboratoire TIMA, pour sa disponibilité et ses conseils pertinents.

Je témoigne ma profonde reconnaissance à mon codirecteur de thèse Mr Frédéric Rousseau pour m'avoir guidé, suivi et aidé tout au long de l'élaboration de ce travail.

J'exprime également mes remerciements aux membres de jury : Monsieur Fabrice Kordon, Professeur à l'université de Pierre et Marie Curie, et Monsieur François Terrier, Professeur et responsable du laboratoire LISE au CEA LIST pour avoir accepté d'être rapporteurs de ce travail.

Je tiens à remercier Mr Ahmed Jerraya, directeur de recherche au CEA LETI, et Mr Emmanuel Vaumorin, Manager de projets stratégiques dans la société MDS, pour avoir accepté d'être examinateurs de ce travail.

Je tiens à saluer tous mes collègues doctorants, post doctorants et permanents du groupe SLS avec qui j'ai partagé cette expérience.

#### Résumé

La complexité des systèmes sur puce augmente pour supporter les nouvelles applications dans le domaine des télécommunications et du multimédia. La tendance actuelle des nouvelles architectures matérielles converge vers des plateformes multi-cœurs où les unités de calcul (processeurs, DSP, IP) sont interconnectées par un réseau sur puce, dont les interfaces réseau sont configurables. Pour ces nouvelles architectures, les environnements de génération de code binaire classiques ne sont plus adaptés.

Cette thèse propose un flot de génération de code de configuration pour le déploiement des applications de type flots de données sur les architectures à base d'IPs interconnectés à travers un réseau sur puce configurable. Ce flot est basé sur des modèles de haut niveau de l'application et de l'architecture et propose une méthodologie générique de partitionnement des ressources. Le processus de génération de code de configuration passe par plusieurs étapes modélisées par diverses représentations intermédiaires du système. La première est déduite depuis les modèles de haut niveau de l'application, de l'architecture et du partitionnement des ressources. Elle ne contient pas d'informations spécifique à la plateforme cible. La deuxième est générée par raffinement du premier modèle intermédiaire. Elle est spécifique à la plateforme cible et elle est exploitée par les outils de génération de code développés pour produire le code de configuration.

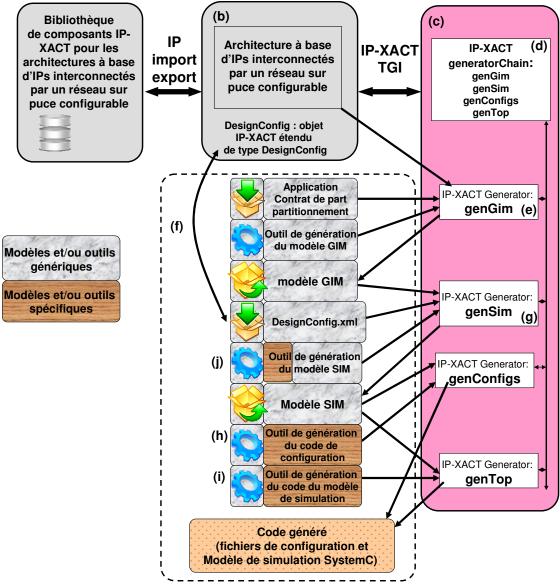

Le flot a été développé par la suite dans un environnement basé sur le standard IEEE 1685 (IP-XACT). Le flot proposé a été appliqué pour la génération et la validation du code de configuration en vue de déployer une application 3GPP-LTE de télécommunication sur la plateforme Magali du CEA LETI. Enfin, une généralisation pour intégrer ce flot dans un environnement classique de génération de code binaire exécutable par des processeurs, est proposée.

#### Abstract

The complexity of SoC is increasing to support new applications in the telecommunication and multimedia domains. The current trend of the new hardware architectures converges to multi-core platforms which gather several execution units (processors, DSP, IP) interconnected via a network on chip in which the network interfaces can be configured. For such architectures, the classical code generation tools and environments are no longer usable and suitable.

This thesis proposes a configuration code generation flow to deploy dataflow applications on IP-based architectures with configurable network on-chip. This flow starts with high level modeling of the application, the architecture and the resources partitioning methodology. The code generation flow goes through several phases which are modeled using various intermediate representations of the system.

The first intermediate representation is deducted from the high level models of the application, the architecture and the partitioning of the resources. This model does not contain any specific information related to the target platform. The second intermediate representation is generated through the refinement of the first intermediate model. It is specific to the target platform and is used by the code generation tools to produce the configuration code.

The code generation flow was developed in an environment based on IEEE 1685 (IP-XACT) standard. The proposed flow has been applied to generate and validate the configuration code to deploy the 3GPP-LTE application on the Magali telecommunication platform. Finally, a generalization of the proposed flow is proposed to integrate it in a classical generation flow of binary and executable code for processors.

# Table des matières

| Chapitre 1. Introduction                                                                                                 | 6  |

|--------------------------------------------------------------------------------------------------------------------------|----|

| 1.1. Contexte                                                                                                            | 6  |

| 1.2. Objectifs                                                                                                           | 6  |

| 1.3. Structure du document                                                                                               | 8  |

| Chapitre 2. Problématique                                                                                                | 10 |

| 2.1. Contexte : Programmation des systèmes sur puce                                                                      | 11 |

| 2.2. Problème : Insuffisance des méthodes et outils classiques de génération de code logiciel                            | 16 |

| 2.3. Problèmes liés à la modélisation des SoC pour la génération de code de configuration                                | 20 |

| 2.4. Conclusion                                                                                                          | 22 |

| Chapitre 3. Etat de l'art                                                                                                | 23 |

| 3.1. Outils de génération de code de configuration                                                                       | 24 |

| 3.2. Inadéquation des méthodes et outils de génération de code logiciel exécutable par les                               |    |

| processeurs                                                                                                              | 35 |

| 3.3. Conclusion                                                                                                          | 39 |

| Chapitre 4. Définition d'un flot de génération de code configuration supportant les interfac                             |    |

| réseau configurables                                                                                                     |    |

| 4.1. Rappel de la problématique                                                                                          |    |

| 4.2. Proposition d'une structure en couches du code de configuration                                                     |    |

| 4.3. Définition d'un flot de génération de code de configuration                                                         | 48 |

| 4.4. Modèle de représentation des plateformes à base d'IPs autour d'un réseau sur puce à interfaces réseau configurables | 51 |

| 4.5. Modèle de représentation des applications orientées flot de données                                                 | 54 |

| 4.6. Technique de partitionnement des ressources                                                                         | 57 |

| 4.7. Modèles intermédiaires et génération de code de configuration                                                       |    |

| 4.8. Conclusion                                                                                                          |    |

| Chapitre 5. Spécification du flot de génération de code de configuration dans un                                         |    |

| environnement IEEE 1685 (IP-XACT)                                                                                        | 63 |

| 5.1. Rappel de la problématique                                                                                          | 64 |

| 5.2. Présentation générale du standard IEEE 1685 (IP-XACT)                                                               |    |

| 5.3. Spécification du flot de génération de code de configuration basé sur le flot IP-XACT                               | 68 |

| 5.4. Extension du standard IP-XACT pour le modèle de représentation ARDL                                                 | 71 |

| 5.5. Spécification du modèle de représentation de l'application APDL et des modèles de partitionnement                   | 75 |

| 5.6. Automatisation du flot de génération de code de configuration                                                       |    |

| 5.7. Intégration du flot de génération de code de configuration dans l'environnement Magiller                            |    |

| 5.8. Conclusion                                                                                                          |    |

| Chapitre 6. Génération de code de configuration pour le déploiement d'une applic                      | ation de |

|-------------------------------------------------------------------------------------------------------|----------|

| télécommunication sur la plateforme Magali                                                            | 86       |

| 6.1. Modélisation de la plateforme Magali                                                             | 87       |

| 6.2. Présentation de l'application de télécommunication 3GPP-LTE                                      | 95       |

| 6.3. Partitionnement de l'application 3GPP-LTE sur la plateforme Magali                               | 98       |

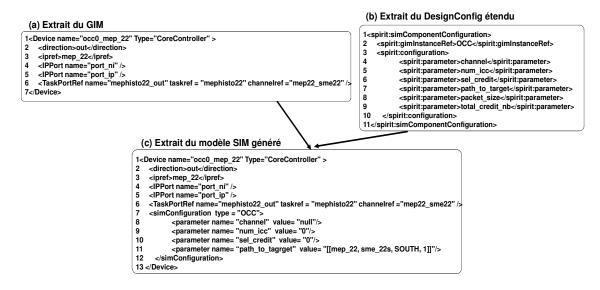

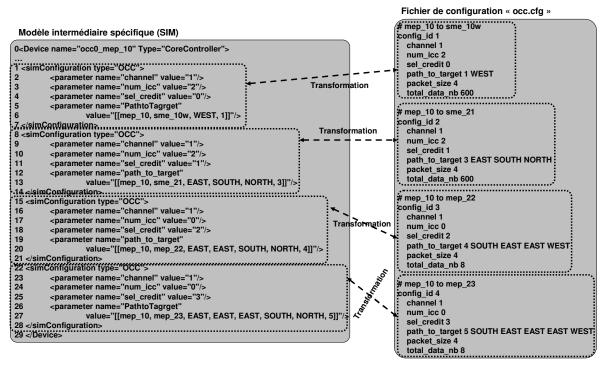

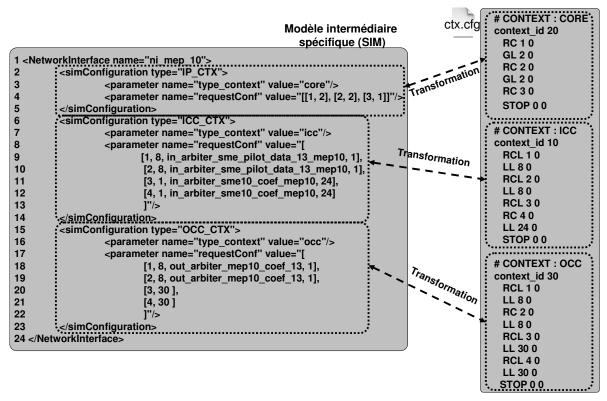

| 6.4. Génération des modèles intermédiaires                                                            | 101      |

| 6.5. Génération du code de configuration pour le déploiement de l'application 3GPI plateforme Magali  |          |

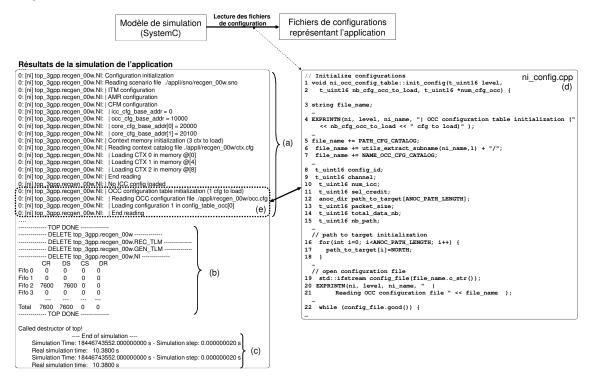

| 6.6. Simulation des fichiers de configuration                                                         | 111      |

| 6.7. Conclusion                                                                                       | 112      |

| Chapitre 7. Vers un flot commun de génération de code                                                 | 114      |

| 7.1. Rappel de la problématique                                                                       | 115      |

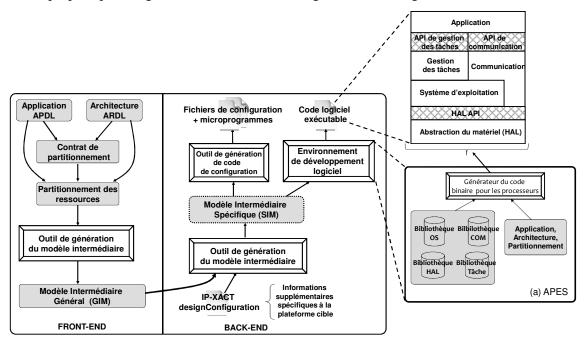

| 7.2. Présentation de l'environnement « APES » pour le développement du code logic par des processeurs |          |

| 7.3. Définition d'un flot commun de génération de code                                                |          |

| 7.4. Modèle de représentation ARDL pour les architectures multiprocesseurs                            |          |

| 7.5. Description des flots de données KPN avec la représentation APDL                                 |          |

| 7.6. Partitionnement des ressources                                                                   |          |

| 7.7. Modèles intermédiaires                                                                           | 121      |

| 7.8. Application du flot commun pour programmer les architectures multiprocesseu                      | ırs 122  |

| 7.9. Conclusion                                                                                       | 125      |

| Chapitre 8. Conclusion et Perspectives                                                                | 126      |

| 8.1. Conclusion.                                                                                      |          |

| 8.2. Perspectives                                                                                     |          |

| Références bibliographiques                                                                           |          |

| Annavas                                                                                               | 126      |

# **Chapitre 1. Introduction**

### 1.1. Contexte

Les systèmes intégrés sont de plus en plus présents dans notre vie quotidienne à travers les multiples fonctionnalités qu'ils fournissent (téléphonie, accès réseaux, appareils photo, GPS, musique MP3, vidéo, etc.). La conception de ces systèmes repose sur des plateformes matérielles, dont la complexité et les performances ne cessent de croître. La tendance actuelle converge vers des architectures matérielles multi-cœurs, c'est à dire contenant plusieurs unités de calcul (processeurs, accélérateurs matériels spécifiques, etc.) interconnectées par un réseau sur puce. Ces unités de calcul peuvent être de la même famille, on parle alors d'architecture homogène, ou de familles différentes, identifiées comme architecture hétérogène. De telles plateformes offrent des mécanismes assurant le parallélisme de calcul et de communication et sont conçues pour supporter des applications diverses. Un changement d'application implique de reprogrammer les unités de calcul et les supports de communications.

Ces nouvelles architectures multi-cœurs contribuent à supporter l'évolution rapide des normes applicatives liées aux marchés du multimédia et des télécommunications et à atteindre les performances de calcul et de communication requises. Mais la complexité de ces architectures rend très difficile le portage et le déploiement de telles applications. Des environnements logiciels d'aide au déploiement sont donc nécessaires pour aider les concepteurs systèmes.

Il existe des environnements de génération de code pour des architectures multiprocesseurs, ce qui facilite beaucoup le déploiement d'applications. Malheureusement, ces environnements se limitent à la production de code pour processeurs, et ne supportent pas à ce jour les récentes évolutions en termes de configuration (ou programmation) des supports de communication dans les réseaux intégrés sur puce (NoC : Network on Chip).

Au vu de ce contexte, cette thèse cherche à fournir de nouvelles méthodes et de nouveaux outils d'aide au déploiement d'applications sur des architectures matérielles multi-coeurs dont les supports de communication sont configurables.

## 1.2. Objectifs

Les techniques de développement d'une manière conjointe du logiciel embarqué et de la plateforme matérielle (co-développement ou co-design) ont pour but de produire un déploiement optimisé de l'application sur une architecture conçue sur mesure. Cela n'est plus viable pour des architectures matérielles complexes. Le coût élevé de telles solutions oblige les concepteurs à produire des plateformes matérielles adaptables à des familles d'applications.

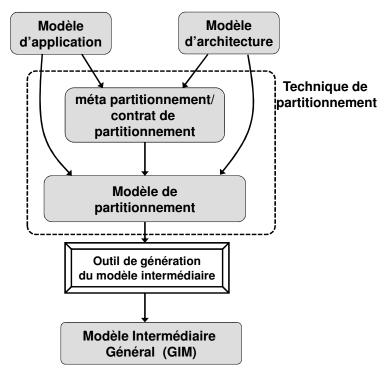

Pour répondre à cette contrainte, le développement d'environnements (ou de flots) de génération de code devient une priorité. Les architectures matérielles, tout comme les applications, n'étant jamais vraiment figées, il faut que ces environnements prennent en entrée une représentation de l'application à déployer et une représentation de l'architecture matérielle incluant les informations nécessaires à sa programmation ou à sa configuration. Ces flots de génération sont généralement basés sur des modèles de haut niveau décrivant les applications, les plateformes cibles ainsi que le partitionnement des ressources. Une représentation de haut niveau réduit la complexité de la description d'entrée. Elle ne conserve que les informations utiles, et s'affranchit de détails inutiles à cette étape de conception du système.

Nous avons constaté depuis quelques années que les architectures sur lesquelles nous voulons déployer des applications complexes ne sont pas uniquement des architectures multiprocesseurs. En effet, certaines sont basées sur un ensemble de composants spécifiques (IP : Intellectual Property) connectés par un réseau sur puce (NoC). Une telle plateforme offre la possibilité de configurer les IPs et les composants de communication responsables de l'exécution et de l'ordonnancement du calcul au sein de l'IP. La génération de code pour ce type d'architecture devient alors une génération de fichiers de configuration pour la partie de calcul et la partie de communication. En effet, le code de configuration pour la partie de calcul est constitué d'un ensemble de paramètres qui initialisent les registres des IPs en vue de réaliser une tâche bien définie. Le code de configuration pour la partie communication correspond à la programmation d'une partie des réseaux sur puce (NI : Network Interface ou interface réseau) qui relient les IPs avec les routeurs du réseau sur puce. Pour orchestrer le tout à un niveau local à chaque IP, mais aussi au niveau global de l'application, d'autres fichiers de configuration et microprogrammes sont aussi à générer.

La production de ce type de code n'est pas encore supportée par les flots classiques de développement et de génération de logiciel embarqué. En effet, il s'agit là d'une problématique nouvelle. Un réseau sur puce est généralement construit et optimisé en fonction d'une application donnée. La famille de réseau sur puce, visée dans cette thèse, est générique et offre de nombreux services (ordonnancement des communications et du calcul), à travers la configuration de ses composants.

Dans un futur proche, nous prévoyons l'émergence d'architectures intégrant, d'un coté, des processeurs pour lesquels il faudra générer le code binaire exécutable, et d'un autre coté, des IPs reliés par un réseau sur puce configurable, pour lesquels il faudra générer également le code de configuration. Il nous faut donc réfléchir à un environnement commun pour la génération de ces deux types de code à partir d'une description de haut niveau de l'architecture, de l'application et du partitionnement des ressources.

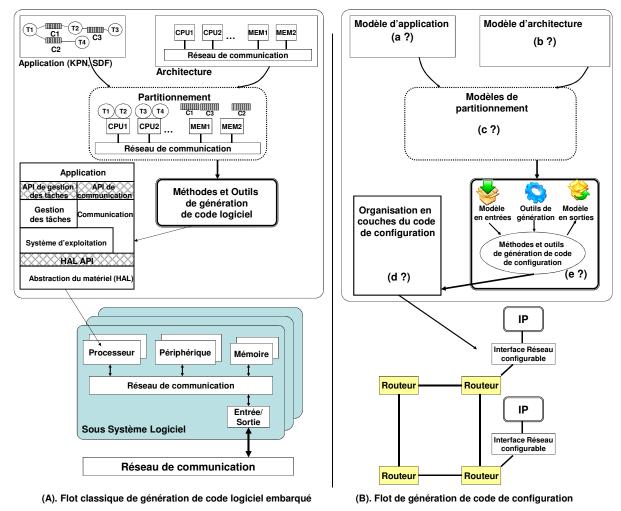

L'objectif de cette thèse est de fournir des méthodes et des outils pour la génération du code de configuration afin de déployer des applications orientées flots de données sur les plateformes à base d'IPs interconnectés à travers un réseau sur puce configurable. Nous

souhaitons également généraliser ces méthodes et outils pour supporter à la fois la génération du code de configuration et du code logiciel binaire exécutable par les processeurs.

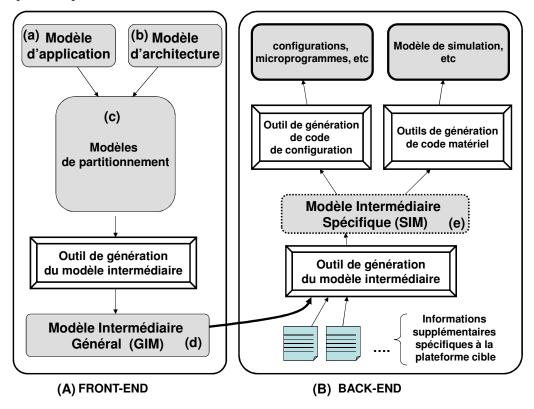

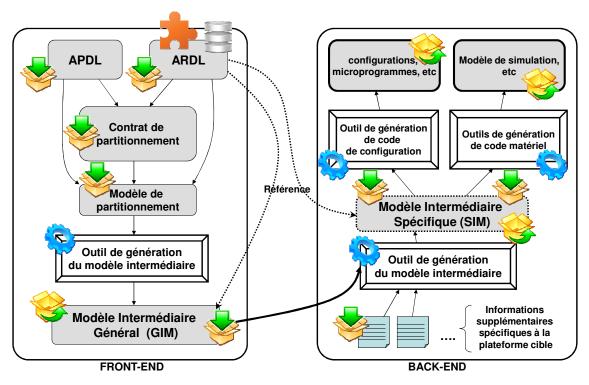

Le flot de génération de code de configuration proposé dans cette thèse est constitué de deux parties principales. La partie « avant » repose sur un modèle intermédiaire dit général représentant l'application déployée sur l'architecture. Ce modèle intègre toute l'information nécessaire à la suite du processus de génération, mais il n'est pas spécifique à la plateforme visée, ni au type de code à générer. Il contient en effet des informations structurelles de l'architecture et de l'application, mais ne comprend pas d'information sur le jeu d'instructions des processeurs ou sur la syntaxe des fichiers de configuration.

La partie « arrière » de ce flot s'appuie sur un modèle intermédiaire dit spécifique. Ce modèle est obtenu à partir du modèle intermédiaire général auquel viennent s'ajouter toutes les informations spécifiques à la plateforme visée et au type de génération souhaité. On précisera par exemple la syntaxe des fichiers de configuration, mais aussi le type des composants à configurer (entrée, sortie, ...).

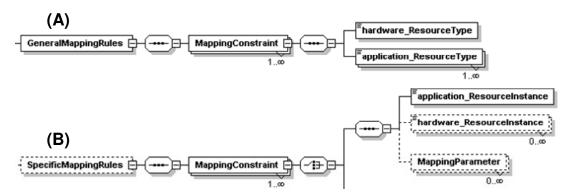

Ce flot de génération de code prend en entrée une description de la plateforme matérielle, une description de l'application et une solution de déploiement de l'application sur l'architecture. La description de l'architecture est basée sur le standard IEEE 1685 (IP-XACT) étendu pour répondre à nos besoins. Pour les applications, nous avons choisi une représentation qui intègre les formalismes classiques (KPN (Khan Process Network), SDF (Synchronous Data Flow)), mais qui permet aussi la description de fonctions particulières au domaine des télécommunications. Il ne s'agit donc pas d'un nouveau formalisme, mais juste d'une représentation textuelle sans sémantique associée. Les propriétés des modèles initiaux restent vraies, et l'utilisation des fonctions particulières modifie bien évidemment ces mêmes propriétés. On propose aussi dans cette thèse une représentation pour le déploiement de l'application sur les ressources de l'architecture qui se fait en deux étapes : une pour indiquer les contraintes et les règles d'association des ressources applicatives et matérielles, l'autre pour donner le déploiement final.

Enfin, cette thèse essaie de faire le lien entre un flot de génération de code binaire pour les processeurs et celui de génération de code de configuration. Il faut pour cela faire apparaître clairement les similitudes et les différences entre ces deux types de flots, et montrer qu'ils peuvent partager des étapes communes ou manipuler des modèles communs. L'objectif ici est d'anticiper sur les architectures matérielles du futur intégrant à la fois des processeurs et des IPs autour d'un réseau sur puce configurable.

#### 1.3. Structure du document

Outre cette introduction générale, ce mémoire comporte sept chapitres. Le chapitre suivant détaille le contexte de ce travail et expose la problématique liée à la génération automatique du code de configuration, qui constitue le thème central de ce travail.

Le chapitre 3 présente et discute des travaux qui ont abordé cette problématique. Nous citons principalement des outils de configuration de réseaux sur puce pendant la phase de

conception, ainsi que certaines méthodes et outils de génération de code pour les architectures multiprocesseurs.

Le chapitre 4 présente l'approche que nous avons mise en œuvre pour la génération du code de configuration. Une proposition est également établie pour structurer en couches ce type de code.

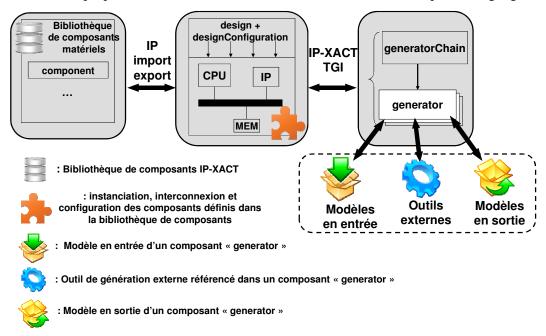

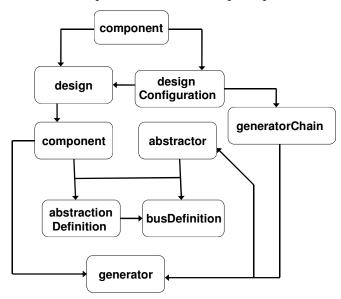

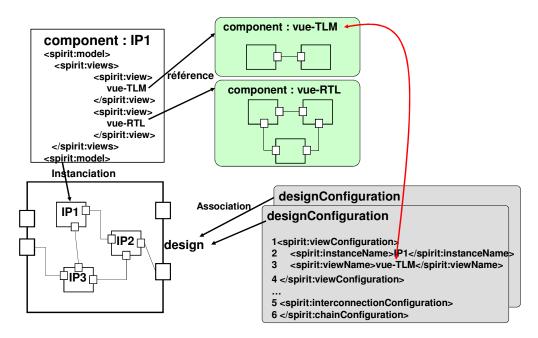

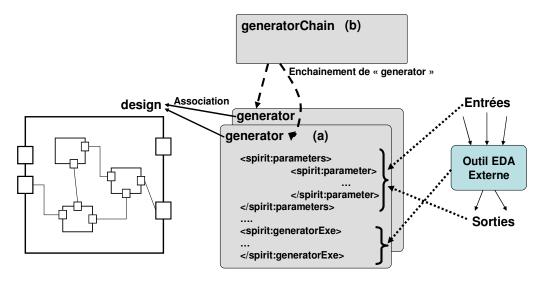

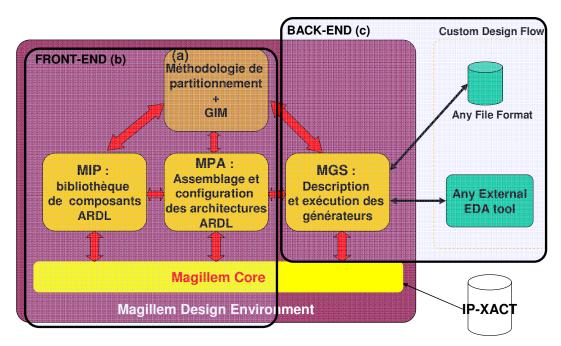

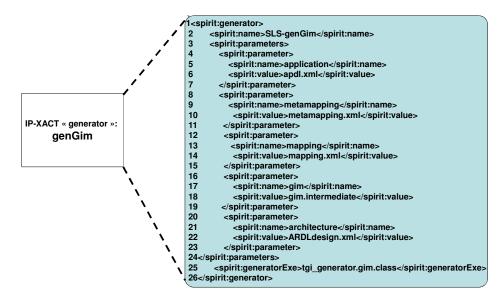

Le chapitre 5 détaille comment nous avons spécifié et implanté cette approche dans un environnement basé sur le standard IEEE 1685 (IP-XACT).

L'application de cette solution est abordée au chapitre 6 à travers une étude de cas dans laquelle nous générons le code de configuration, qui permet de déployer une application de télécommunication 3GPP-LTE sur la plateforme configurable et largement paramétrable « Magali » [Lat08]. Dans ce chapitre d'expérimentation, nous mettons en évidence l'efficacité et les limitations des méthodes et outils que nous avons mis en œuvre.

En résumé, les chapitres 4 et 5 abordent les principales contributions de cette thèse et le chapitre 6 détaille l'expérimentation réalisée et les résultats obtenus.

Dans le chapitre 7, nous présentons notre dernière contribution. Elle consiste à généraliser le flot de génération de code pour viser à la fois le code de configuration et le code binaire exécutable par les processeurs. Nous étudions la possibilité d'utiliser les mêmes représentations de haut niveau pour la description de l'application, de l'architecture et du partitionnement des ressources.

Enfin, Le chapitre 8 expose les conclusions de ce travail et propose quelques perspectives potentielles.

# Chapitre 2. Problématique

| 2.1. Contexte : Programmation des systèmes sur pucepuce                                                                         | 11      |

|---------------------------------------------------------------------------------------------------------------------------------|---------|

| 2.1.1. Architecture des systèmes sur puce                                                                                       | 11      |

| 2.1.2. Programmation des plateformes à base d'IPs interconnectés à travers un NoC                                               | 14      |

| 2.1.3. Exemple : Déploiement d'applications sur la plateforme Magali                                                            | 14      |

| 2.2. Problème : Insuffisance des méthodes et outils classiques de génération de code logic                                      | iel. 16 |

| 2.2.1. Programmation des sous systèmes logiciels                                                                                | 16      |

| 2.2.2. Flot de génération de code pour les sous systèmes logiciels : possibilités et limites                                    | 18      |

| 2.2.3. Conclusion : Besoin de nouvelles solutions pour la génération de code de configuration pointerfaces réseau configurables |         |

| 2.3. Problèmes liés à la modélisation des SoC pour la génération de code de configuration                                       | ı 20    |

| 2.3.1. Inadaptation des modèles de calcul classiques à certaines applications orientées flots de données                        | 20      |

| 2.3.2. Inadéquation des modèles intermédiaires                                                                                  | 21      |

| 2.3.3. Difficultés de raffinement des modèles de haut niveau vers le code final à déployer                                      | 21      |

| 2.3.4. Difficultés d'automatisation des flots de génération de code de configuration                                            | 22      |

| 2.4. Conclusion                                                                                                                 | 22      |

### 2.1. Contexte : Programmation des systèmes sur puce

Le progrès constant dans les technologies de l'électronique a favorisé l'apparition de systèmes sur puce (SoC pour System on Chip) de plus en plus performants qui embarquent de nombreuses fonctionnalités sur un unique substrat de silicium. Des appareils tels que les téléphones portables qui fournissent plusieurs fonctions (téléphone, accès réseaux, appareil photo, GPS, musique MP3, vidéo, etc.) témoignent de l'évolution croissante des systèmes sur puce. Ils sont également présents dans l'automobile (réglage des phares, contrôle du moteur, etc.), les téléviseurs HD, les « set-up box», etc. A la différence des ordinateurs, ils possèdent généralement des interfaces avec le monde extérieur (radio) et ont des contraintes de coût et de performance importantes.

Dans cette section, nous introduisons, dans une première étape, l'architecture d'un système sur puce. Nous décrivons, par la suite, comment déployer des applications sur ces systèmes, en particulier ceux à base de NoC à interfaces réseau configurables. Nous présentons, enfin, un exemple de ces architectures qui est la plateforme Magali [Lat08] du CEA/LETI. Nous nous intéressons à cette plateforme puisque le CEA/LETI nous a fourni son environnement de simulation dans le cadre d'un projet de recherche ANR [Hospi].

### 2.1.1. Architecture des systèmes sur puce

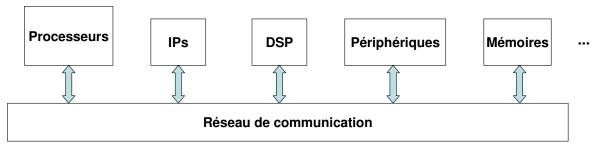

L'architecture générale d'un système sur puce est présentée dans la figure 2.1. Elle est constituée de composants de calcul (processeurs, IPs, DSPs (Digital Signal Processor)), d'un ensemble de périphériques et de composants de mémorisation, le tout interconnecté par un réseau de communication. On peut distinguer des composants de calcul programmables et non programmables. Les premiers sont généralement les processeurs. Ils exécutent des tâches applicatives diverses. Les seconds font référence aux composants IPs. Ils fournissent des fonctionnalités très spécifiques telles que la transformée de Fourier (FFT) ou la transformée de Fourier inverse (iFFT). Ils ont généralement des performances supérieures à celles d'un processeur. Certains composants non programmables proposent plusieurs fonctions spécifiques pouvant être sélectionnées durant une phase de configuration ; et ce, en écrivant certaines valeurs dans des registres de configuration.

Les composants périphériques étendent les possibilités du système en apportant des fonctionnalités d'accès à la mémoire (accès direct ou via le processeur), de gestion d'interruptions, de gestion de synchronisation, etc.

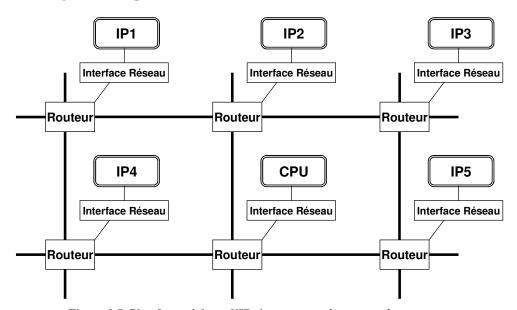

Figure 2.1. Architecture des systèmes sur puce

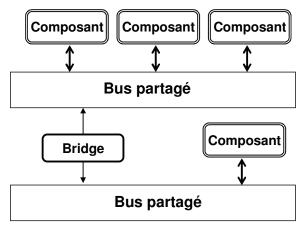

Tous ces composants communiquent par l'intermédiaire d'un support de communication qui peut être un bus ou un réseau sur puce. Le bus partage les communications entre tous les composants [Mur05]. Un bus hiérarchique, comme illustré dans la figure 2.2, est composé de plusieurs bus partagés, interconnectés par l'intermédiaire de ponts (« bridge »). Les infrastructures de communication classiques se basent sur les bus partagés. Or, ceux-ci ont montré leurs limites face à l'augmentation croissante des transferts de données entre les composants matériels de l'architecture, exigée par les applications. En effet, les bus partagés ne supportent pas des débits élevés et offrent peu de flexibilité quant au nombre de composants de calcul à interconnecter.

Face aux limitations des bus dans les systèmes sur puce, l'orientation actuelle des infrastructures de communication converge vers les réseaux sur puce, qui sont inspirés des réseaux informatiques classiques. Les NoCs supportent l'augmentation croissante de la complexité des applications en termes d'échanges de données. Ils permettent ainsi d'interconnecter plusieurs composants de calcul. Grâce aux multiples chemins de communication entre les ressources du SoC, les NoCs garantissent des critères de performance comme la latence, le débit et la bande passante.

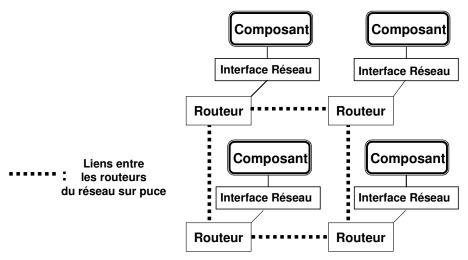

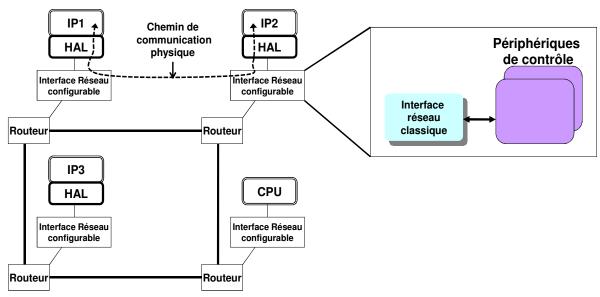

Figure 2.2. Bus hiérarchique

Les NoCs (Figure.2.3) sont constitués d'un ensemble de routeurs, auxquels s'interconnectent les composants via des interfaces réseau. Les routeurs fournissent des fonctions d'aiguillage et de routage des paquets de données échangés à travers la plateforme. Les interfaces réseau représentent les points d'entrée au NoC. Elles assurent l'acheminement des données de bout en bout. Ainsi, la communication entre deux composants distants connectés au NoC passe par deux interfaces réseau et plusieurs routeurs. Les interfaces réseau et les routeurs peuvent être configurables pour optimiser les chemins de communications des flux de données échangés à travers le NoC. Il existe plusieurs exemples de réseau sur puce : STNoc [Cop08], SPIN [Adr03] [Gue00], Xpipes [Ber04], Hermes [Fer04], FAUST [Cle05,Dur05], Æthereal [Goo05], etc.

Figure 2.3. Réseau sur puce

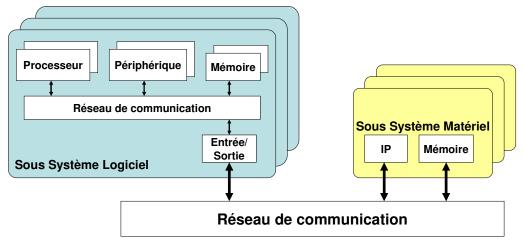

Un système sur puce peut être vu et représenté comme un ensemble de sous systèmes logiciels et de sous systèmes matériels interconnectés par un réseau de communication (Figure.2.4).

Un sous système logiciel fait référence à l'exécution d'un programme par un ensemble de composants matériels. Il dispose lui même d'une partie matérielle et d'une partie logicielle. La partie matérielle comporte un ou plusieurs processeurs, des composants de mémorisation et des périphériques (TIMER, DMA (Direct Memory Access), périphériques d'entrée/sortie, etc.). La partie logicielle comporte tous les composants logiciels nécessaires à l'exécution de tâches à savoir le système d'exploitation, les pilotes des périphériques, le programme applicatif, les bibliothèques de communication, etc.

Un sous-système matériel fait référence à l'exécution d'une fonctionnalité spécifique par un composant de calcul dédié (IP). Les composants IPs sont des blocs matériels physiquement implantés sur la puce. En les configurant, nous pouvons choisir la fonctionnalité qu'ils doivent réaliser, et ce, en initialisant certains de leurs registres. A noter que chaque configuration identifie un comportement du sous système matériel.

Figure 2.4. Sous système logiciel et sous système matériel

Nous focalisons les travaux de cette thèse sur le déploiement d'applications sur les sous systèmes matériels composés d'IPs et interconnectés à travers un réseau sur puce. Les plateformes que nous ciblons sont figées, c'est-à-dire que l'emplacement des IPs par rapport aux routeurs du réseau sur puce est fixe. Il s'agit de plateformes conçues pour cibler des familles d'applications précises connues à la conception. Nous présentons dans la section suivante la manière dont ces plateformes peuvent être programmées pour le déploiement d'applications.

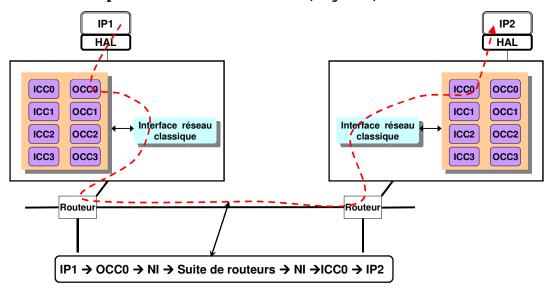

# 2.1.2. Programmation des plateformes à base d'IPs interconnectés à travers un NoC

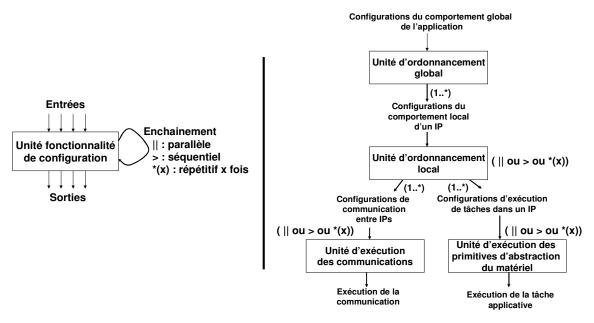

Le déploiement d'applications sur une plateforme figée commence par associer les tâches applicatives aux différents IPs. Un composant IP fournit une fonctionnalité à travers une configuration bien précise de ses registres. Plusieurs configurations peuvent être affectées à un seul IP s'il fournit plusieurs fonctionnalités. Les communications applicatives, représentant les échanges de données entre les blocs IP, sont assurées par le NoC, en particulier par les routeurs et les interfaces réseau.

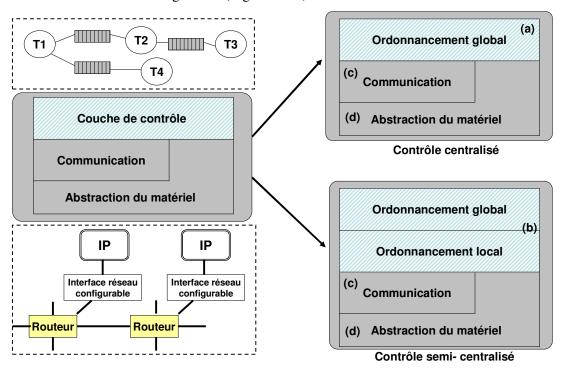

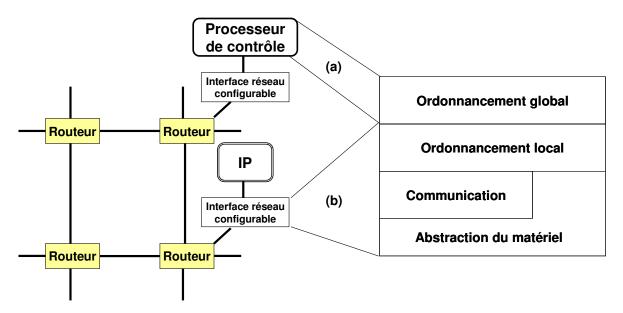

Un mécanisme de contrôle et de synchronisation de l'exécution des tâches réparties sur les IPs doit être mis en place. Un processeur central peut jouer ce rôle et ordonnancer toutes les tâches et les communications. Cependant, un tel système centralisé a des limites vu le grand nombre d'interruptions à gérer, ce qui affecte les performances globales de la plateforme. Ainsi, le processeur central peut déléguer la gestion des communications et du comportement des IPs aux interfaces réseau réparties. Il se contente, quant à lui, de gérer les contrôles effectués par les interfaces réseau.

Ces interfaces réseau avancées qui fournissent des fonctionnalités de contrôle et de synchronisation des communications et des tâches sont configurables. En effet, elles ont besoin d'informations relatives aux échanges de données en entrée et en sortie de l'IP qui leur est connecté. Elles doivent disposer également des paramètres à associer aux registres de l'IP pour qu'il exécute la fonctionnalité demandée. Ces interfaces exécutent un jeu d'instructions simple qui permet d'exprimer le séquencement des tâches applicatives et des échanges de données, et définir ainsi le comportement de l'IP.

Magali est un exemple concret de plateforme qui dispose de ce genre d'interfaces réseau avancées. Nous présentons dans la section suivante les mécanismes de déploiement d'applications sur cette plateforme.

## 2.1.3. Exemple : Déploiement d'applications sur la plateforme Magali

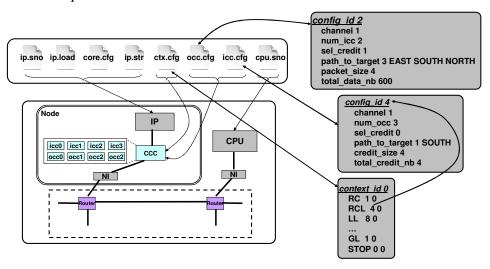

La plateforme Magali est une plateforme dédiée à la réalisation des fonctionnalités des couches physique et MAC (Medium Access Control) pour des applications de télécommunication haut débit, de type 3G et suivantes (3GPP-LTE, WiMax, etc). Cette plateforme inclut un processeur unique ainsi qu'un ensemble d'IPs répartis sur le NoC. Le réseau sur puce est asynchrone. Il est constitué de routeurs à cinq ports reliés entre eux par des liens bidirectionnels, selon une grille à deux dimensions (2D-Mesh NoC). Cette plateforme, illustrée dans la figure 2.5, peut être représentée comme tout réseau sur puce qui interconnecte plusieurs IPs.

Pour chaque IP, plusieurs configurations élémentaires de calcul et de communication sont définies. Le code de configuration pour la partie de calcul est constitué par un ensemble de paramètres qui initialisent les registres des IPs en vue de réaliser une tâche bien définie. Le code de configuration pour la partie communication définit le nombre de données à transférer, le chemin qu'elles doivent suivre à travers le réseau ainsi que des informations concernant le contrôle de flux.

L'ordonnancement de ces configurations permet de définir le comportement de l'IP, à savoir les tâches à exécuter ainsi que les échanges de données à réaliser. Ainsi, un IP peut avoir un comportement différent selon l'ordonnancement choisi des configurations élémentaires. On appelle « ordonnanceur local » l'unité qui s'occupe de l'ordonnancement de ces configurations. Il est associé à l'interface réseau qui est connectée à chaque IP. Celle-ci définit le comportement des blocs matériels à travers un scénario d'ordonnancement des différentes configurations, écrit sous la forme d'un microprogramme.

Un « séquenceur global » associé à l'unique processeur de la plateforme permet d'ordonnancer les différents scénarii locaux (microprogrammes) en vue de définir le comportement global de la plateforme.

Figure 2.5. Plateforme à base d'IPs interconnectés par un réseau sur puce

Le code de configuration est exécuté au niveau des interfaces réseau configurables de la plateforme. En effet, l'interface réseau dans la plateforme Magali réalise plusieurs fonctionnalités telles que la configuration des unités de calcul (les IPs et l'unique processeur), l'ordonnancement des configurations de calcul et de communications locales ainsi que le contrôle de flux. Une présentation détaillée de l'architecture de l'interface réseau dans Magali, ainsi que son modèle de programmation se trouve dans le chapitre 3 de l'état de l'art.

Le développement du code de configuration pour cette architecture est complexe. Il est écrit, à l'heure actuelle, par la personne effectuant l'intégration de l'application sur la plateforme. Le code est constitué d'un grand nombre de fichiers contenant chacun plusieurs paramètres (5 fichiers de configuration par IP contenant les configurations de communication et de calcul). La grande difficulté dans la production de ce genre de code est de garantir la

cohérence des différentes valeurs, liées aux dépendances entre les divers paramètres dans les fichiers de configuration.

Nous nous intéressons dans cette thèse aux difficultés de génération de code de configuration pour déployer des applications sur des plateformes comme « Magali ». Nous nous focalisons principalement sur les interfaces réseau qui fournissent des services avancés d'ordonnancement et de synchronisation des communications et des tâches applicatives.

Nous exposons dans la suite les raisons pour lesquelles les méthodes et les outils de génération de code existants, pour les processeurs, ne sont pas applicables aux plateformes que nous ciblons.

# 2.2. Problème : Insuffisance des méthodes et outils classiques de génération de code logiciel

Dans cette section, nous présentons la structure du code logiciel qui cible les processeurs et les caractéristiques des méthodes et des outils qui le génèrent. Ensuite, nous discutons les possibilités d'application de ces méthodes et outils pour programmer les interfaces réseau configurables.

### 2.2.1. Programmation des sous systèmes logiciels

La programmation d'un sous système logiciel nécessite le développement des tâches applicatives exécutées par les unités de calcul. Le code applicatif fait appel à des modèles de programmation pour la gestion des tâches et des transferts de données entre elles. Par exemple, dans le but de programmer des applications parallèles pour des plateformes multiprocesseurs à mémoire partagée, le programmeur a besoin d'utiliser des mécanismes de gestion et de synchronisation de tâches. La norme Posix [But97] est un standard proposant de tels mécanismes.

Des systèmes d'exploitation (multi tâches, temps réel, etc.) sont aussi indispensables pour la programmation des sous systèmes logiciels. Ils fournissent les mécanismes d'ordonnancement et de gestion de l'allocation du processeur entre les différentes tâches applicatives. Le développement des systèmes d'exploitation nécessite le développement de primitives d'accès et de gestion des composants matériels de la plateforme. Des pilotes sont ainsi indispensables pour effectuer cette gestion, en particulier pour les composants périphériques.

Certaines plateformes fournissent une API (Application Programming Interface) sous forme de SDK (Software Developement Kit) à partir de laquelle l'utilisateur peut développer des applications. Cette API représente une interface d'accès à une couche logicielle contenant un intergiciel (« middleware »). Cette couche « middleware » est dépendante de la plateforme cible et du système d'exploitation. Nous pouvons citer «Android », « SymbianOS » et « Windows Mobile » pour les terminaux mobiles, qui fournissent des SDK facilitant le développement d'applications. Un émulateur de la plateforme et du système d'exploitation est généralement fourni pour valider les applications développées. Cette couche « middleware » joue le rôle d'intermédiaire entre le code de l'application d'une part et le transfert des données et leurs traitements sur la plateforme d'autre part.

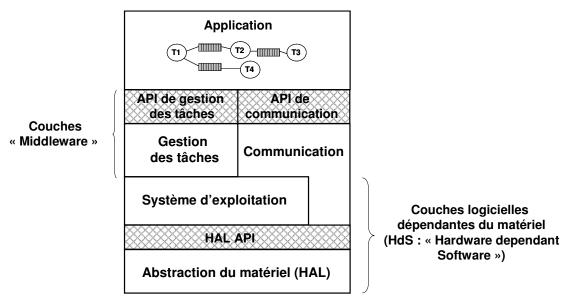

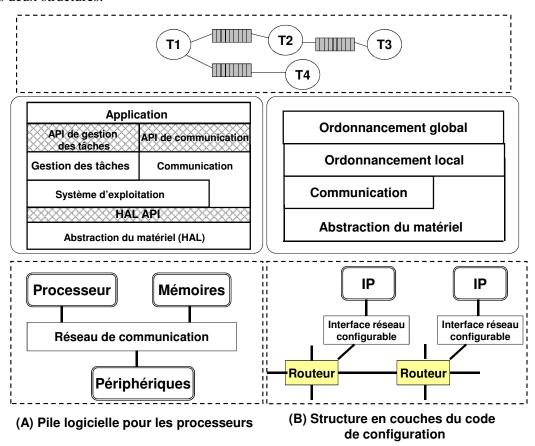

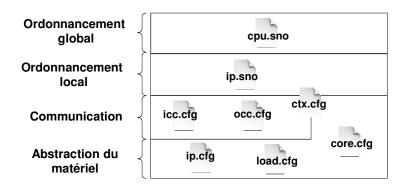

Formaliser la programmation des sous systèmes logiciels en un ensemble de couches simplifie son développement. Nous pouvons ainsi structurer tous les composants logiciels, nécessaires à la programmation des sous systèmes logiciels. Cette structure en couches est appelée « pile logicielle » [Jer06] (Figure.2.6). Elle est composée de :

- La couche applicative qui est la couche de niveau supérieur. Il s'agit de la partie fonctionnelle du logiciel embarqué. Elle comporte une ou plusieurs tâches exécutées par le(s) processeur(s) du sous système logiciel. Le mode d'interaction et d'échange de données entre les différentes tâches suit un modèle de calcul. Un exemple très utilisé pour le développement des applications parallèles est KPN (Khan Process Network) [Lee95].

- Les couches « API de gestion des tâches » et « Gestion des tâches » fournissent des primitives pour la gestion des tâches applicatives (création, suspension, synchronisation des tâches, etc.). La première représente l'interface à l'ensemble des primitives de gestion de tâches implantées au niveau de la seconde couche.

- Les couches « API de communication » et « Communication » fournissent des primitives pour la gestion des communications entre les tâches décrites au niveau applicatif. La première représente une interface à l'ensemble des primitives de communication qui sont implantées au niveau de la seconde. Elles font appel à des fonctionnalités du système d'exploitation et de la couche « HAL API ».

- ⇒ Les couches de gestion des tâches et de communication constituent la couche « middleware » pour développer des applications contenant des tâches communicantes. Cette couche est extensible si nous voulons développer d'autres applications respectant des modèles de calcul différents.

- La couche du système d'exploitation englobe le système d'exploitation lui-même ainsi que les pilotes de périphériques.

Figure 2.6. Modélisation du logiciel embarqué en pile logicielle

Les couches HAL (Hardware Abstraction Layer) sont les couches d'abstraction du matériel. Elles comportent une interface générique pour les accès élémentaires aux composants matériels ainsi que l'implantation de cette interface, qui est spécifique à l'architecture cible. La couche « HAL API » est générique alors que son implantation (couche « HAL ») est spécifique au sous système logiciel et en particulier au processeur cible.

**Exemple**: la fonction de changement de contexte « cxt\_switch », dont la signature est « void cxt\_switch (cxt\_type old\_context, cxt\_type new\_context) », représente un exemple de primitive générique de la couche «HAL API ». Cette fonction est développée de différentes manières, dans la couche « HAL » selon le type du processeur cible du sous système logiciel.

⇒ Les couches du système d'exploitation et HAL représentent le logiciel dépendant du matériel appelé HdS (Hardware dependant Software) dans [Dom09] et [Jer06]. La séparation du logiciel embarqué en deux parties -dépendante et indépendante du matériel- facilite son développement et améliore sa portabilité en favorisant sa réutilisation sur plusieurs plateformes.

Le paragraphe suivant présente les méthodes et les outils existants pour la génération du logiciel embarqué pour les sous systèmes logiciels. L'organisation de ces outils et la mise en œuvre des méthodes de déploiement introduisent le flot de génération de code logiciel.

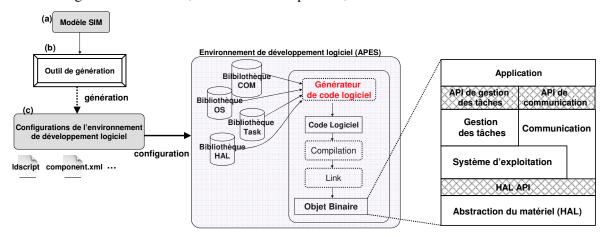

# 2.2.2. Flot de génération de code pour les sous systèmes logiciels : possibilités et limites

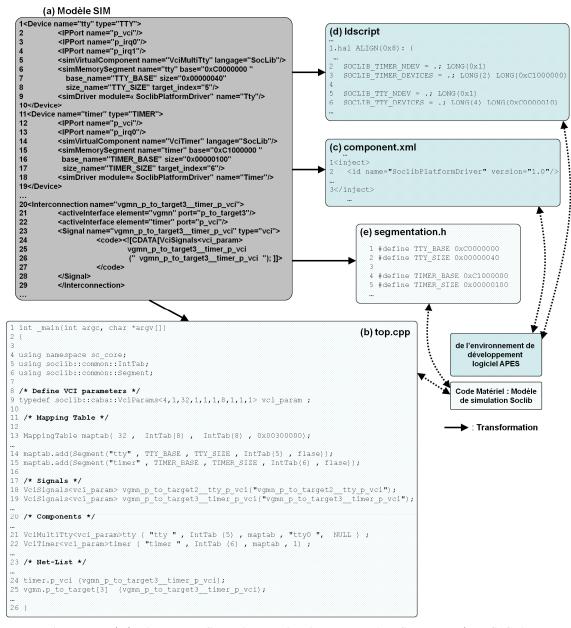

Nous présentons dans ce paragraphe le flot de génération de code pour les sous systèmes logiciels. Il s'agit d'un flot connu [Gue07] et spécifique aux architectures multiprocesseurs (Figure.2.7). Le flot commence par la modélisation à haut niveau de l'application et de l'architecture et par la proposition d'un modèle de partitionnement des ressources applicatives sur les ressources architecturales, tel que défini dans [Thi07] et [Dsx]. Les applications généralement déployées sur des plateformes multiprocesseurs sont des applications orientées « flot de données » provenant de plusieurs domaines (multimédia, télécommunication, etc.). Il s'agit d'applications décrites par des tâches parallèles qui échangent des données via des canaux logiciels. Ces flots de données respectent généralement des modèles de calcul comme KPN et SDF [Lee87].

Le modèle de partitionnement des ressources applicatives sur des architectures multiprocesseurs consiste à associer les tâches applicatives aux processeurs et les canaux de communication applicatifs aux composants de mémorisation de la plateforme.

Le flot de génération de code utilise plusieurs outils et bibliothèques (systèmes d'exploitation, bibliothèques de communication, etc.). Certains outils peuvent générer le fichier « Makefile » pour la compilation du logiciel. Après compilation et édition de liens, un objet binaire est généré et exécuté par un processeur de l'architecture. Dans une architecture multiprocesseur, ce flot est potentiellement (sauf système SMP (Symmetric Multi Processing)) exécuté pour chaque processeur. Ainsi, un objet binaire est produit pour chacun

Système d'exploitation

HAL API

Abstraction du matériel (HAL)

Modèle d'application Modèle d'architecture Т3 CPU1 CPU2 МЕМ1 MEM2 Réseau de communication Modèle de partitionnement CPU1 CPU2 МЕМ1 МЕМ2 Réseau de communication Bilbilothèque **Application** Génération du génération du Makefile. logiciel API de gestion API de Bibliothèque Ldscript des tâches communication OS Bibliothèque **Code Logiciel** Gestion Task Communication des tâches Bibliothèque Compilation HAL

et sauvegardé dans ses espaces d'adressage. L'ensemble des outils et des bibliothèques peuvent être regroupés dans un environnement de développement logiciel.

Figure 2.7. Flot classique de génération de code logiciel

Ce type de flot est spécifique au déploiement d'applications orientées flot de données, dont le modèle de calcul est KPN ou SDF, sur des architectures multiprocesseurs. Cette spécificité concerne la description de haut niveau des applications, des architectures et du partitionnement.

Link

Objet Binaire

Environnement de développement Logiciel

Ce flot ne peut pas être utilisé pour d'autres types d'architectures (architecture à base d'IPs interconnectés par un réseau sur puce) voulant exécuter d'autres types d'applications qui ne se représentent pas par les modèles de calcul KPN et SDF, i.e. comme le CSDF (Cyclo-Static DataFlow) [Bil95].

Il lui manque des modèles permettant de renprésenter l'aspect configurable de l'architecture. En plus, il n'existe pas d'outils capables de produire le code de déploimement sous la forme de configurations distribuées sur l'ensemble des interfaces réseau. Les plateformes, comme Magali, sont nouvelles et ne sont pas encore supportées par le flot classique de génération de code.

Il n'existe pas en notre connaissance, au moment où nous rédigeons cette thèse, de flots génériques de génération de code de configuration pour programmer les plateformes que nous ciblons.

# 2.2.3. Conclusion : Besoin de nouvelles solutions pour la génération de code de configuration pour les interfaces réseau configurables

A travers l'exemple de la plateforme Magali, nous avons montré que le code que nous voulons générer pour ce type d'architecture est un code de configuration. Le flot classique, présenté en figure 2.7, ne permet pas de le générer. En effet, le modèle de description de l'architecture ainsi que celui du partitionnement ne sont pas suffisants pour exprimer les aspects configurables des interfaces réseau et des IPs matériels dans une architecture telle que Magali.

L'évolution rapide de la technologie des réseaux sur puce, en particulier l'aspect configurable des interfaces réseau et leurs modes de programmation, fait ressentir le besoin d'améliorer les flots classiques de génération de code logiciel.

# 2.3. Problèmes liés à la modélisation des SoC pour la génération de code de configuration

La modélisation de haut niveau des SoC permet de fournir une vue qui facilite leur développement et réduit leur complexité. Cela nécessite la modélisation des applications, des architectures ainsi que leur partitionnement à un niveau d'abstraction approprié (TLM (Transaction Level Model [Systemc]) par exemple pour la modélisation des architectures). Plusieurs standards sont utilisés pour la modélisation de haut niveau comme UML (Unified Modeling Language), XML (eXtensible Markup Language), des bibliothèques C++ (SystemC [Systemc], SoCLib [Soclib]), etc. Cette modélisation représente une solution clé pour remédier au problème du retard que prend la production du code logiciel par rapport au saut technologique des architectures et des applications. Elle est généralement accompagnée par un ensemble de méthodes et d'outils de partitionnement et de génération de code. L'efficacité de la modélisation de haut niveau est conditionnée par l'efficacité des outils d'exploitation qui l'accompagnent (outils de transformation, de raffinement, de vérification, de génération, de simulation, etc.). Ces outils permettent le passage du niveau abstrait au niveau de réalisation en exploitant des informations additionnelles spécifiques à la plateforme cible. Ils sont généralement regroupés dans des environnements de développement logiciel.

Nous introduisons dans cette partie les problématiques liées à la modélisation de haut niveau des applications et des architectures ainsi qu'à la définition des représentations intermédiaires. Nous essayons, à travers la présentation de ces problèmes, de répondre aux besoins des flots de génération de code de configuration pour des plateformes ayant des interfaces configurables comme Magali.

# 2.3.1. Inadaptation des modèles de calcul classiques à certaines applications orientées flots de données

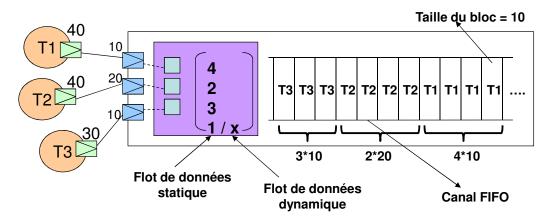

Les modèles de calcul connus pour la représentation des applications flots de donnés dans les domaines du multimédia et de la télécommunication sont principalement KPN et SDF. Les applications flots de données, dans ce cas, sont développées en utilisant des modèles de programmation parallèle connus (développement du modèle de processus de Khan à l'aide du standard *Posix* par exemple). Il se trouve que les applications ne cessent d'augmenter en

complexité au niveau de leurs algorithmes (algorithmes de traitement de signal et d'images par exemple). Un seul modèle de calcul devient insuffisant pour modéliser autant d'applications complexes et variées. Par exemple, le modèle de processus de Khan ne permet pas la représentation de l'arbitrage des transferts de données au niveau des canaux de communication. En effet, il ne représente pas la synchronisation des transferts de données entre les canaux de communication logiciels indépendants.

Or, l'arbitrage des communications est de plus en plus présent dans les applications récentes, en particulier dans le domaine des télécommunications. Le besoin se fait sentir de représenter ces informations d'arbitrage et de synchronisation dans les modèles applicatifs pour réaliser un partitionnement optimal des ressources.

### 2.3.2. Inadéquation des modèles intermédiaires

Dans les flots de génération de code, l'utilisation de modèles intermédiaires, qui regroupent les informations applicatives et architecturales, facilite l'extraction des données nécessaires aux outils de génération de code.

En effet, il existe plusieurs composants logiciels (tâches, primitives de système d'exploitation, primitives de communication, configurations, pilotes, etc.) qui sont exécutés par des composants matériels variés (DSP, ASIC, processeurs, infrastructure de communication, etc.). Le partitionnement ou le déploiement (mapping) de ces différents composants d'une manière optimale est un défit majeur dans la modélisation des systèmes sur puce. Il existe des modèles intermédiaires qui représentent l'affectation des tâches aux processeurs et l'association des canaux de communication logiciels aux composants de mémorisation [Chu08].

En revanche, lorsque l'on aborde des plateformes telles que Magali, ces modèles intermédiaires sont dans l'incapacité de représenter l'association des configurations ou des microprogrammes aux interfaces réseau configurables.

# 2.3.3. Difficultés de raffinement des modèles de haut niveau vers le code final à déployer

Dans les flots de génération de code, le passage depuis les modèles de haut niveau de l'application et de l'architecture vers le code final à exécuter nécessite généralement plusieurs étapes de raffinement. Les modèles de haut niveau ne contiennent pas assez d'informations pour la génération de code. Des détails concernant le partitionnement des espaces d'adressage, le système d'exploitation, les pilotes de périphériques, les adresses d'interruptions, etc., sont nécessaires à la génération de code final pour les processeurs. Ces informations supplémentaires peuvent être ajoutées par les développeurs à travers des environnements de développement logiciel.

Il s'avère que ces informations ne sont pas utiles pour des plateformes telles que Magali. En effet, le rôle classique du système d'exploitation et des bibliothèques de communication sont joués par des configurations dans la plateforme Magali.

Ainsi, nous cherchons dans cette thèse à identifier les informations adéquates à injecter aux outils de génération de code de configuration pour des plateformes à interfaces réseau

configurables. Le problème réside dans la définition de ces informations supplémentaires et dans leurs représentations dans des modèles intermédiaires.

# 2.3.4. Difficultés d'automatisation des flots de génération de code de configuration

Afin de garantir une génération de code rapide, les nouveaux flots de génération de code doivent être facilement automatisables. Il s'agit de définir un enchaînement d'exécutions de différents outils. Cet enchaînement est généralement le même pour une famille d'applications et de plateformes. Les principales difficultés dans l'automatisation des flots de génération de code dans ce contexte sont liés à :

- (1) L'interopérabilité des outils de transformation et de génération de code ainsi que les types d'échanges qui peuvent se produire entre eux.

- (2) L'expression d'un modèle d'automatisation du flot de génération de code avec les standards existants.

### 2.4. Conclusion

Nous avons présenté dans ce chapitre les architectures matérielles auxquelles nous nous intéressons dans cette thèse à savoir les systèmes à base de réseaux sur puce à interfaces réseau configurables comme la plateforme Magali. Nous avons mis l'accent sur l'importance des outils de modélisation et de génération de code pour supporter le saut technologique que connaissent les architecture multi-cœurs à base de réseau sur puce. Les flots de génération de code logiciel actuels sont spécifiques aux plateformes à base de processeurs et ne fournissent pas de fonctionnalités d'extension supportant de nouveaux types d'architectures.

Nous avons vu que le code à générer, pour une plateforme contenant des interfaces réseau configurables, comme Magali, est essentiellement un code de configuration.

Dans la première partie de cette thèse, nous essayons d'apporter des réponses aux questions suivantes :

- 1) Comment pouvons-nous formaliser le code de configuration, nécessaire à la programmation des interfaces réseau configurables, pour simplifier son développement ?

- 2) Comment pouvons-nous générer le code de configuration pour ces plateformes en se basant sur des modèles de haut niveau d'application, d'architecture et de partitionnement ?

- 3) Comment pouvons-nous automatiser le processus complet de génération de code de configuration ?

Nous souhaitons, dans la suite, aborder le problème de généricité des flots de génération de code. La principale question qui se pose à ce niveau est la suivante :

4) Pouvons-nous disposer d'un flot commun/général de génération de code qui pourra cibler plusieurs types de plateformes (plateformes à base de processeurs, plateformes à base d'IPs avec des interfaces réseau configurables, plateformes hétérogènes contenant à la fois les processeurs et les IPs, etc.) ?

# Chapitre 3. Etat de l'art

| 3.1. Outils de génération de code de configuration                                                     | 24 |

|--------------------------------------------------------------------------------------------------------|----|

| 3.1.1. Architecture des réseaux sur puce                                                               | 24 |

| 3.1.2. Les interfaces réseau classiques                                                                | 25 |

| 3.1.3. Méthodes et outils de génération de code des réseaux sur puce                                   | 26 |

| 3.1.4. Interface réseau configurable du réseau sur puce Æthereal                                       | 27 |

| 3.1.5. Interface réseau configurable dans la plateforme Magali                                         | 30 |

| 3.1.6. Synthèse                                                                                        | 35 |

| 3.2. Inadéquation des méthodes et outils de génération de code logiciel exécutable par les processeurs | 35 |

| 3.2.1. Méthodes et outils de génération de code pour les processeurs                                   |    |

| 3.2.2. Synthèse                                                                                        | 39 |

| 3.3. Conclusion                                                                                        | 39 |

Ce chapitre présente l'état de l'art des flots de génération de code de configuration. Ce type de code est généré pour des architectures figées. Il s'agit de plateformes à base d'IPs dont l'emplacement est déjà prédéfini sur un réseau sur puce. Le code de configuration est constitué d'un ensemble de fichiers qui définissent le comportement des IPs et des interfaces réseau configurables de la plateforme. Le principal problème dans le développement de ce type de code se situe au niveau de la gestion de sa complexité (gestion d'un grand nombre de configurations et de leurs cohérences). C'est pour cela que nous nous intéressons aux moyens de génération du code de configuration d'une manière automatique à partir de la formalisation de celle ci.

Ainsi, l'état de l'art se focalise sur les méthodes et outils de génération de ce type de code pour les plateformes basées sur les réseaux sur puce et ayant des interfaces réseau configurables. Cette thématique a été rarement abordée dans les travaux de recherche existants. Les thèmes les plus traités se rapportant à la génération de code pour les réseaux sur puce sont autour de la synthèse d'architecture, ce qui n'est pas notre objectif.

Dans ce chapitre, nous introduisons d'abord les réseaux sur puces et les interfaces réseau classiques. Nous présentons ensuite les deux uniques exemples, qui existent à notre connaissance, traitant de la programmation des plateformes à travers de multiples configurations des interfaces réseau. Nous présentons par la suite les principaux flots classiques de génération de code logiciel. Nous exposons enfin les obstacles qui nous empêchent de les utiliser pour déployer des applications sur les plateformes que nous étudions dans le cadre de cette thèse. Nous rappelons que l'objectif est de réutiliser une même plateforme dans le déploiement de plusieurs applications appartenant à la même classe.

## 3.1. Outils de génération de code de configuration

## 3.1.1. Architecture des réseaux sur puce

Les réseaux sur puce [Gue00] [Ben05] sont des infrastructures de communication qui ont connu un grand essor durant ces dernières années. Ils sont de plus en plus utilisés dans les plateformes avancées en raison de la flexibilité et de la capacité à passer à l'échelle (scalability) qu'ils apportent dans les communications, en comparaison avec les systèmes à base de bus.

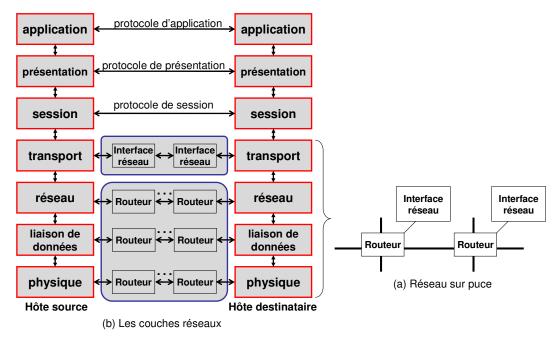

Le principe des réseaux sur puce s'inspire des réseaux entre ordinateurs classiques. La transmission de données entre diverses machines dans les réseaux classiques est définie selon le modèle en couches OSI (Open Systems Interconnection) [Zim80] de l' « *International Standard Organization* ». Il s'agit d'une architecture de référence en sept couches qui définit les étapes de traitement des informations entre le matériel et les applications. Pour concevoir et mettre en œuvre des réseaux sur puce, il a fallu adapter leurs caractéristiques au modèle OSI puisqu'il n'existe pas de modèle de référence pour la représentation des couches réseau propre aux réseaux sur puce. Ainsi, un réseau sur puce peut être représenté par les quatre couches basses du modèle OSI (Figure.3.1.b) [Bje06] [Ben01].

Les fonctionnalités des trois premières couches basses (« Physique », « Liaison de données » et « Réseau ») sont assurées par le composant routeur. D'une manière générale, le routeur est constitué de tampons en entrée et en sortie. Il réalise des mécanismes de routage et

d'arbitrage des données entre les différents nœuds. L'interface réseau joue le rôle d'adaptateur réseau. Elle fournit les fonctionnalités de la couche « Transport » du modèle OSI, à savoir la gestion des communications de bout en bout entre les nœuds connectés au réseau. L'interface réseau peut être configurable. Dans ce cas, elle fournit des fonctionnalités de contrôle de flux optimal [Rad04] ou d'ordonnancement et de synchronisation des tâches [Cle09]. Cette dernière fonctionnalité est généralement fournie en logiciel, à travers un système d'exploitation par exemple, dans les réseaux comme SPIN [Cha06] et STNoC [Cop08].

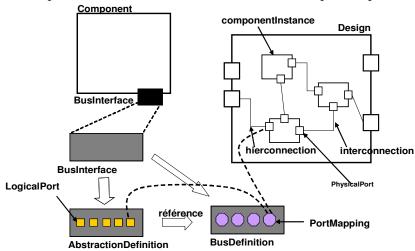

Figure 3.1. Les couches réseau pour un réseau sur puce

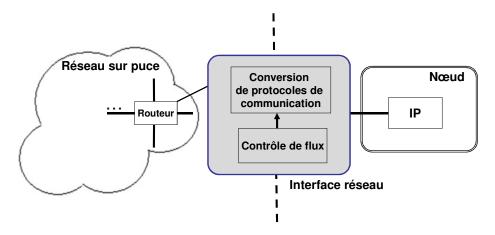

#### 3.1.2. Les interfaces réseau classiques

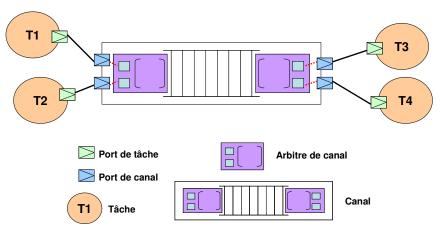

L'interface réseau (Figure.3.2) est un composant qui relie les nœuds de la plateforme au réseau sur puce. Un nœud peut être un sous système logiciel ou un sous système matériel. L'interface réseau est interconnectée à un routeur d'un coté et au nœud de la plateforme de l'autre. L'ensemble des interfaces réseau constitue les points d'accès au réseau. Elles fournissent un ensemble de services qui masquent les mécanismes internes de transfert de données (mécanisme de routage, topologie du réseau, mécanisme de détection et correction d'erreur de transmission, contrôle de flux, etc.). Les interfaces réseau permettent la conversion des protocoles de communication physiques de chaque nœud vers ceux du réseau et vice versa.

Les interfaces réseau découpent les messages provenant de l'émetteur en paquets et ajoutent des informations supplémentaires relatives à la destination de ces paquets lors de l'envoi des données. De manière similaire, les interfaces réseau rassemblent les paquets reçus du réseau avant de transmettre le message complet au récepteur lors de la réception des données. L'interface réseau assure également le contrôle de flux des communications de bout en bout. Ce mécanisme permet d'éviter l'envoi de données vers une destination n'ayant pas d'espace suffisant dans ses tampons pour les recevoir. Les services mentionnés ci-dessus sont

fournis par les interfaces réseau classiques et sont indépendants des applications à déployer sur la plateforme.

Figure 3.2. Fonctionnalités d'une interface réseau classique

#### 3.1.3. Méthodes et outils de génération de code des réseaux sur puce

Dans la littérature, la majorité des outils développés pour les réseaux sur puce ciblent la synthèse d'architecture. Il s'agit d'outils et de générateurs qui permettent de concevoir une architecture de réseau optimisée pour une application ou une famille d'applications. Nous présentons brièvement les principaux travaux allant dans ce sens. Dans [Ber05], un flot de conception intitulé « Netchip » est proposé pour le réseau sur puce « Xpipes » [Ber04]. Le flot contient un outil pour la sélection de la topologie [Mur04], un outil pour une synthèse personnalisée de la topologie [Ati08] et un outil pour la génération du code matériel du réseau sur puce en SystemC [Jal04]. Un outil de synthèse du réseau µSPIDER [Eva06] est également présenté dans [Daf07]. Cet outil prend en considération des contraintes de latence et de bande passante.

Nous rappelons que nous ne nous intéressons pas à la synthèse d'architecture. Dans cette thèse, nous cherchons à développer des méthodes et des outils de génération de configurations pour les interfaces réseau avancées, afin de déployer des applications sur des plateformes déjà conçues. Ces dernières offrent des mécanismes de configuration dynamique des IPs et du réseau pour obtenir le comportement souhaité selon l'application à déployer.

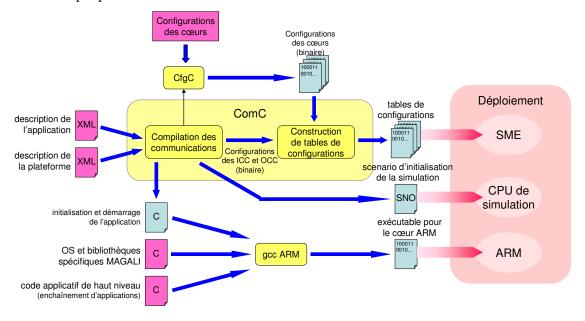

Nous présentons dans la suite les deux uniques outils, à notre connaissance, qui permettent la génération du code de configuration pour deux NoCs dédiés. Le premier est lié au réseau Æthereal [Goo05]. Il permet de générer les configurations en prenant en considération des contraintes de latence et de bande passante. Le second est intitulé « ComC » et permet la génération du code de configuration pour la plateforme Magali. Nous avons choisi ces deux exemples puisque le code de configuration à générer est dépendant du flot de données des applications à déployer. Nous nous intéressons particulièrement à la plateforme Magali puisque nous allons l'adopter comme cas d'étude.

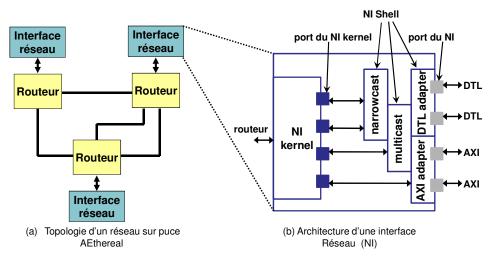

#### 3.1.4. Interface réseau configurable du réseau sur puce Æthereal

Dans cette section, nous présentons le réseau sur puce Æthereal et l'architecture de ses interfaces réseau. Ensuite, nous détaillons comment ces interfaces sont configurées et nous détaillons les outils qui génèrent le code de configuration.

#### 3.1.4.1. Présentation du réseau sur puce Æthereal

Æthereal est un réseau sur puce proposé par Philips. C'est une architecture qui assure une garantie de débit, de latence et de bande passante. Elle représente une infrastructure de communication sans topologie précise (Figure.3.3.a) pour les applications multimédia ou de télécommunication. La communication entre les ressources interconnectées au réseau est assurée par un mécanisme d'allocation de temps. Une unité de temps dans le réseau Æthereal est appelée « slot ». Une table d'attribution des « slot » aux différentes communications est configurée statiquement, au niveau des interfaces réseau, lors de la conception du NoC. Une configuration du réseau correspond à une application donnée. Une bande passante peut ainsi être garantie pour des communications en leur allouant un certain nombre de « slot ». La table d'attribution des « slot » peut être configurée d'une manière dynamique pendant l'exécution de l'application.

Le réseau Æthereal est configurable au niveau des interfaces réseau afin de réaliser les communications applicatives. Ces configurations permettent l'ordonnancement des communications mais n'interviennent pas au niveau de la partie de calcul de l'application.

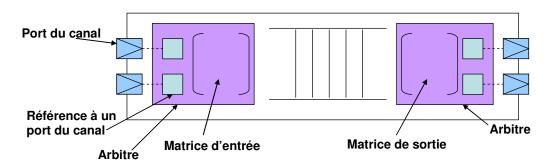

#### 3.1.4.2. Architecture des interfaces réseau dans Æthereal

L'interface réseau (Figure.3.3.b) dans le réseau Æthereal est le composant de base qui permet la configuration et la reconfiguration des communications à travers le réseau. Elle est composée d'une partie centrale nommée « NI Kernel » et d'une seconde partie nommée « NI Shell ». Le « NI Kernel » fournit les services de base d'une interface réseau classique, à savoir le contrôle de flux, l'assemblage et le désassemblage des messages reçus et émis. Les « NI Shell » sont des modules adaptateurs qui permettent la conversion des protocoles de communication entre le réseau et les IPs.

Figure 3.3. Réseau sur puce Æthereal [Rad04]

Ils supportent des services de diffusion de type « Norrwcast » et « Multicast ». Les protocoles de communication supportés par Æthereal sont DTL (Device Transaction Level), AXI (ARM) et OPC (Open Core Protocol). Le « NI Kernel » est relié aux adaptateurs « NI Shell » via des ports point à point.

Dans le « NI Kernel », il y a deux types de FIFO : les FIFO sources qui sont réservées aux messages à envoyer et les FIFO destinataires pour les messages à recevoir. La taille de ces zones mémoire est configurable pour l'optimisation des communications. Le mécanisme de contrôle de flux est assuré par un compteur de crédits associé à ces zones mémoires. Il est initialisé au moment du choix de la taille de la FIFO. Si une donnée est envoyée depuis une FIFO source, le compteur de crédits est décrémenté. Si une donnée est consommée par l'IP à partir des FIFO destinataires, le compteur de crédits associé à cette FIFO est alors incrémenté.

#### 3.1.4.3. Mécanisme de configuration des interfaces réseau dans Æthereal

Æthereal permet de définir des connexions configurables et paramétrables entre les IPs qui communiquent, en garantissant un certain débit et une certaine latence. Les configurations des connexions se font à travers les interfaces réseau émettrices reliant les IPs. Elles sont dépendantes du flot de données applicatives et peuvent être activées ou désactivées au cours de l'exécution de l'application.

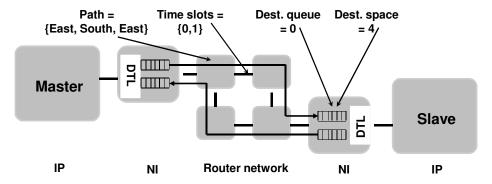

Figure 3.4. Configuration d'une communication entre deux IPs [Han07]

Comme illustré dans la figure 3.4, les informations indispensables pour configurer une interface réseau sont :

- Un chemin à travers le réseau pour le transfert des données (Elément « Path » dans la figure 3.4).

- Un identifiant de la FIFO destinataire pour la mise en correspondance entre la FIFO source de l'IP émetteur et la FIFO destinataire de l'IP récepteur.

- La taille de la FIFO destinataire qui reçoit les données. Cette information est indispensable pour fournir le service de contrôle de flux (« Dest.queue »/ « Dest.space » dans la figure 3.4).

- Un temps pour la communication spécifié par l'allocation d'un nombre de « slot ».

Cette information est importante pour identifier les instants où la communication entre les ressources utilise les liens du réseau (« Time slots » dans la figure 3.4).

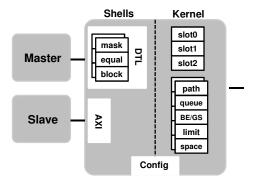

La définition des communications entre les IPs dans le réseau se fait par la configuration des registres des interfaces réseau. Cela est réalisé par un « mapping » mémoire appliqué aux ports de configuration des interfaces réseau. Ces ports offrent un accès aux registres des interfaces par le biais de transactions de lecture et d'écriture. Il existe des registres de configuration spécifiques au « NI kernel » et d'autres spécifiques aux « NI Shell ». L'ensemble de ces registres configurables au niveau des interfaces réseaux (Figure. 3.5), est classé en trois principales catégories:

- Les registres « path, queue, BE (Best Effort)/GS (Garanteeted Service), limit and space» : L'acheminement des données à travers le réseau est défini dans le registre « path » associé à l'IP émetteur. La FIFO de l'interface réseau destinataire vers laquelle les données sont transmises est définie dans le registre « queue ». Le registre « BE/GS » définit le choix des contraintes de qualité de service des communications. Enfin, le compteur de contrôle de flux, utilisé pour suivre l'occupation de la file d'attente de l'interface réseau destinataire, est défini dans le registre « space ».

- La table des « slot » : Ces registres participent à orchestrer d'une manière temporelle l'utilisation des chemins de communication et décident des moments d'envoi des données vers le réseau.

- Les registres du « NI Shell » : ces registres sont optionnels et permettent de configurer l'interface réseau pour supporter les protocoles de communication des composants IPs (DTL, AXI, etc.).

Figure 3.5. Liste des registres configurables dans une interface réseau [Han07]

#### 3.1.4.4. Flot de génération de code du réseau Æthereal

Le flot de génération de code pour le réseau Æthereal, illustré dans la figure 3.6, est présenté dans [GDGPRR05].

Il prend en entrée un modèle de flot de données décrivant l'application (communication.xml), l'ensemble des IPs à interconnecter au réseau (ip.xml) ainsi qu'un modèle de contraintes (contraintes sur la bande passante et la latence des communications (constraints.xml)) en vue de générer la topologie du NoC. Il s'agit d'associer les IPs à leurs emplacements sur le réseau. Ensuite, le flot génère les configurations de communication pour les interfaces réseau (configuration.xml). Il produit enfin le code VHDL de la plateforme.

Si on dispose d'une nouvelle application flot de données à déployer, le flot exige une nouvelle génération du NoC (disposition des IPs par rapport aux routeurs). La génération des configurations est réalisée après que la plateforme soit définie, c'est-à-dire , après que les IPs à utiliser soient identifiés et placés sur le réseau.

A ce stade, nous avons présenté un exemple d'une interface réseau configurable qui fournit des services de communication pour une plateforme Æthereal à base d'IPs. L'interface réseau est configuratble à travers ses registres. Ces derniers contiennent des informations de communication de bas niveau se rapportant aux chemins de données, aux FIFO des interfaces réseau, aux adaptateurs avec les IPs, etc. L'outil de génération de ces configurations est spécifique au réseau Æthereal. Nous cherchons dans cette thèse à fournir une approche générale qui pourrait s'interfacer avec différents types d'interfaces réseau avancées.

Figure 3.6. Flot de conception du réseau sur puce Æthereal [GDGPRR05]

Dans le prochain paragraphe, nous présentons un second exemple d'interface réseau configurable au sein de la plateforme Magali. Nous présentons également un outil de génération de code de configuration qui lui est spécifique.

#### 3.1.5. Interface réseau configurable dans la plateforme Magali

On s'intéresse dans ce paragraphe à la plateforme Magali et à ses interfaces réseau configurables. Celles-ci permettent, contrairement aux interfaces réseau dans Æthereal, la gestion et l'ordonnancement à la fois de la partie communication et calcul de l'application à déployer.

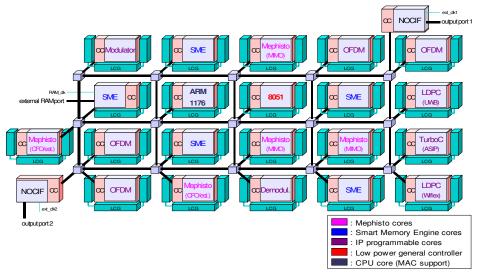

#### 3.1.5.1. Structure de la plateforme Magali

La plateforme Magali est une architecture parallèle semi hétérogène (Figure.3.7). Elle contient des IPs configurables fournissant des fonctionnalités spécifiques (IPs OFDM, les IPs de codage/décodage LDPC et Turbocodes, etc.).

Elle contient également des composants SME (Smart Memory Engine) qui sont des composants de mémorisation possédant les fonctionnalités d'un DMA programmable. La plateforme comporte des DSP basse consommation, appelés Mephisto, indispensables pour les applications de télécommunication. Ces DSP sont considérés comme des IPs car le code qu'ils exécutent est toujours fourni avec eux et figé. Enfin, la plateforme dispose d'un unique processeur central ARM11 pour le contrôle général de la plateforme. Les différents IPs sont interconnectés au NoC via les interfaces réseau, reliées elles mêmes aux routeurs.

Figure 3.7. Architecture de la plateforme MAGALI

Chacun de ces derniers dispose de cinq ports : quatre pour la liaison avec d'autres routeurs et un pour interconnecter un IP ou le processeur central. Cette structure offre une grande flexibilité de routage pour échanger les données entre les différents IPs de la plateforme.

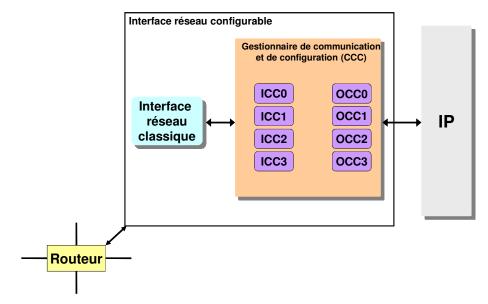

# 3.1.5.2. Interface réseau configurable : gestionnaire de configuration et de communication

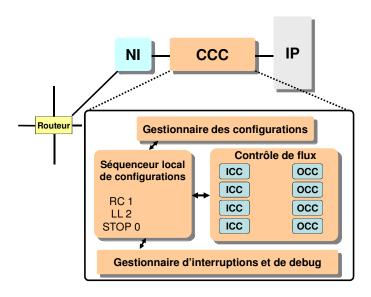

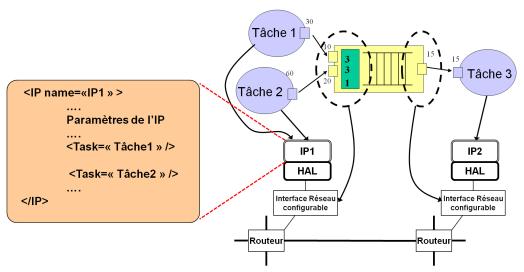

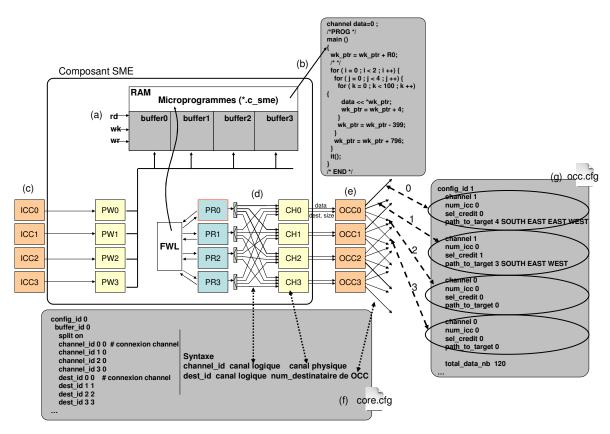

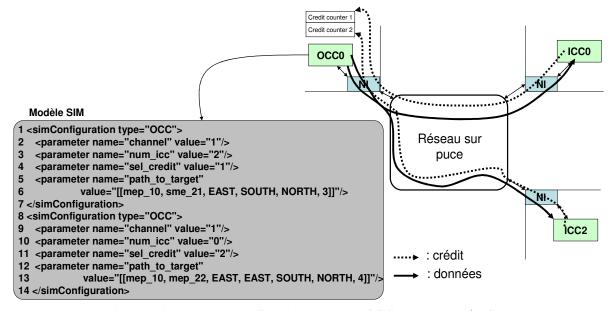

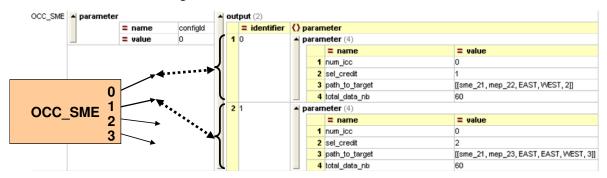

Dans la plateforme Magali, chaque IP est relié à un routeur par l'intermédiaire d'une interface réseau avancée qui contient un bloc appelé CCC (*Communication and Configuration Controller*) [CLTV09]. Il s'agit du gestionnaire de configuration et de communication (Figure.3.8).

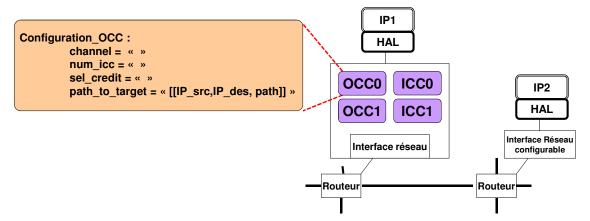

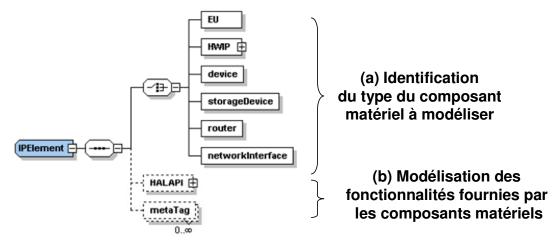

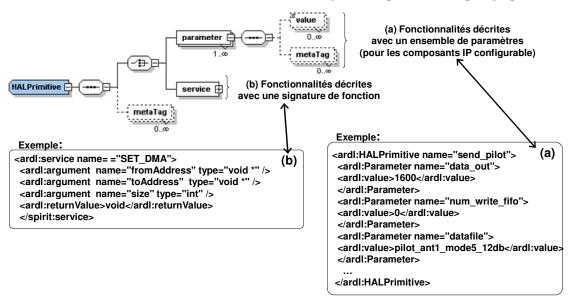

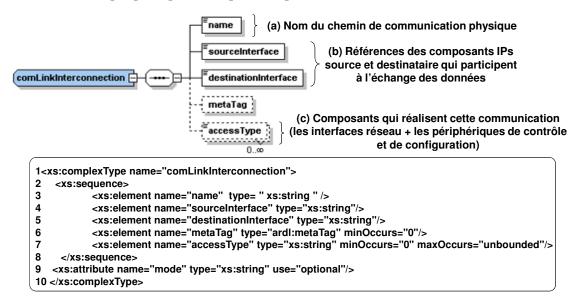

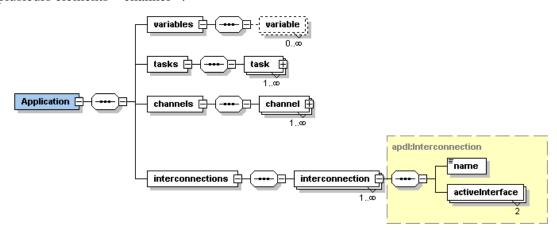

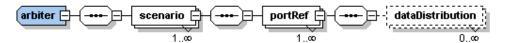

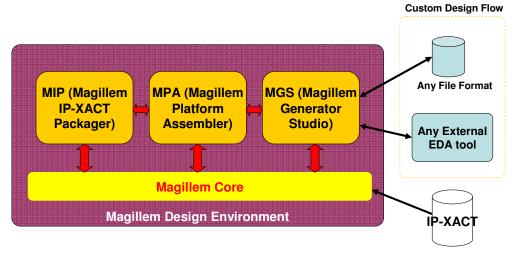

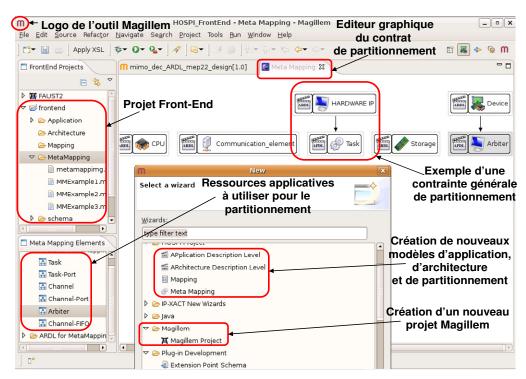

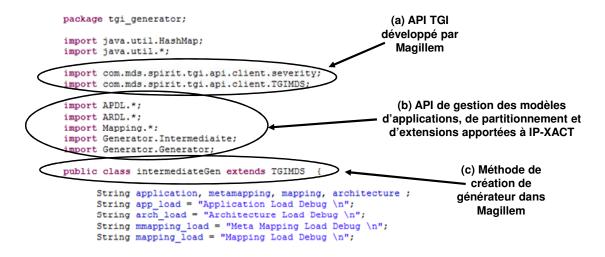

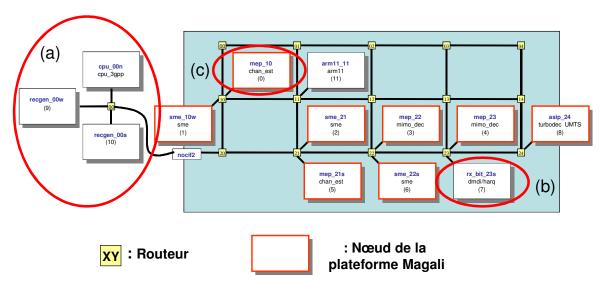

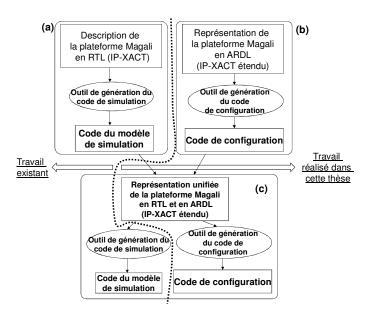

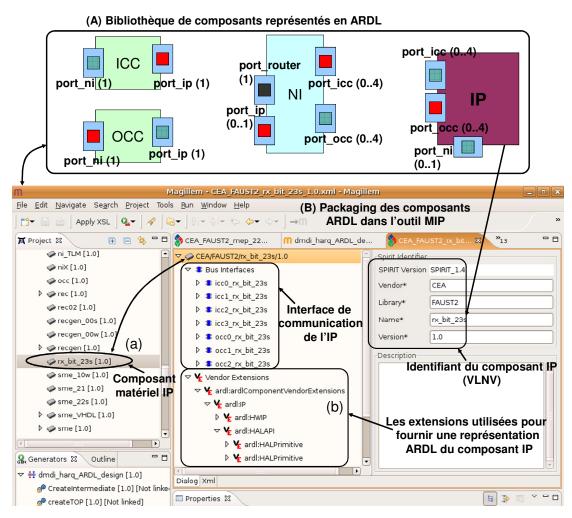

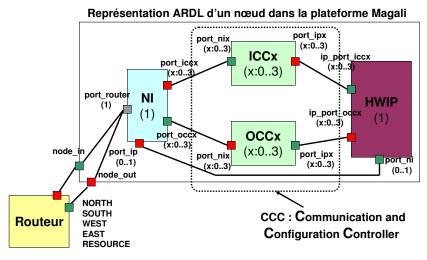

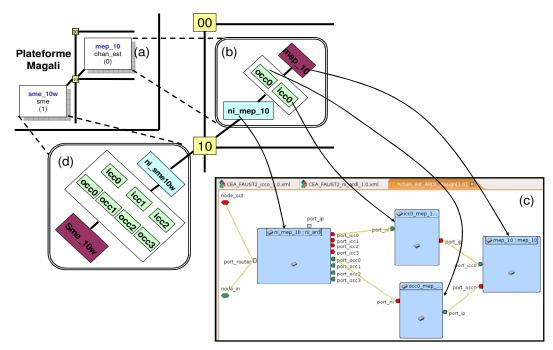

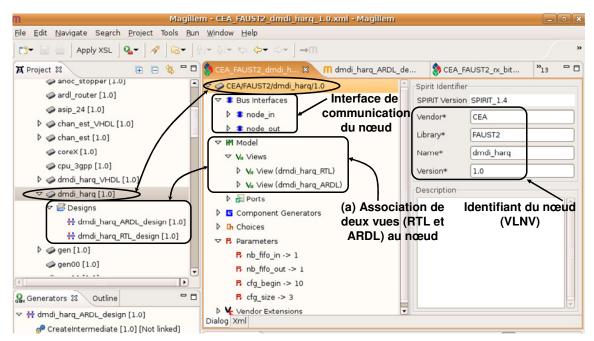

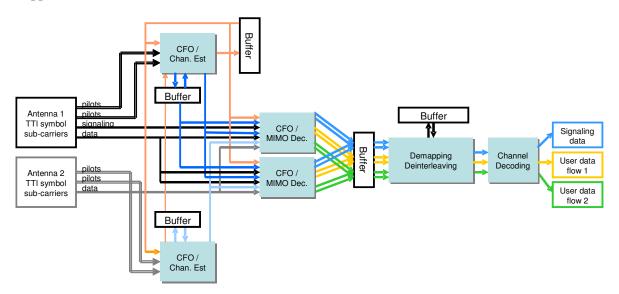

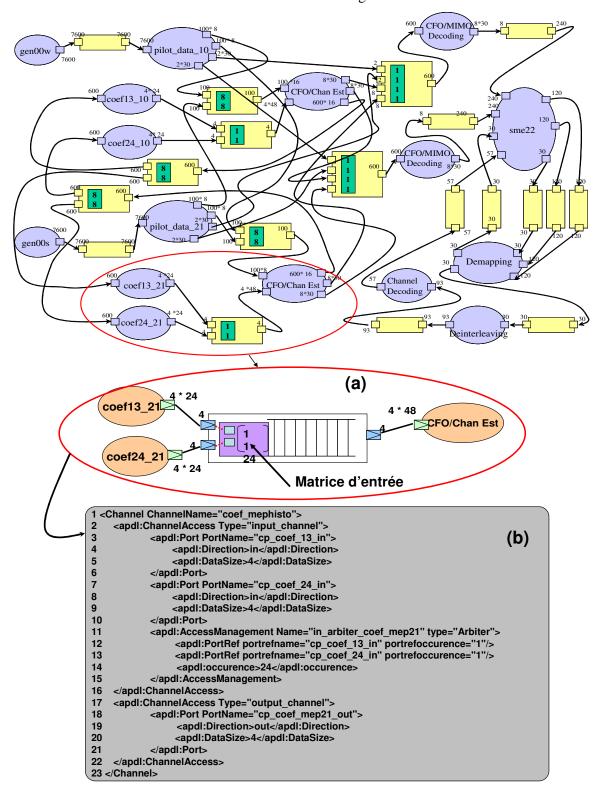

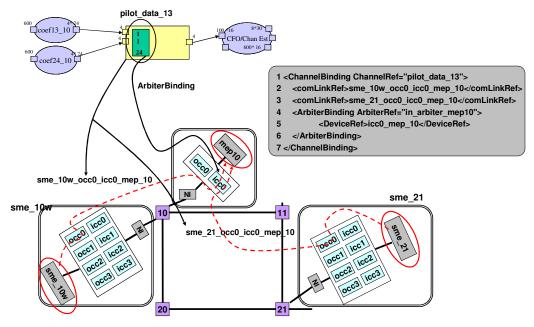

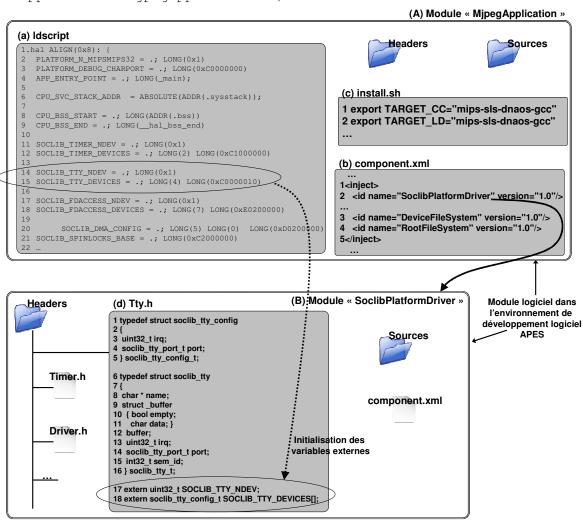

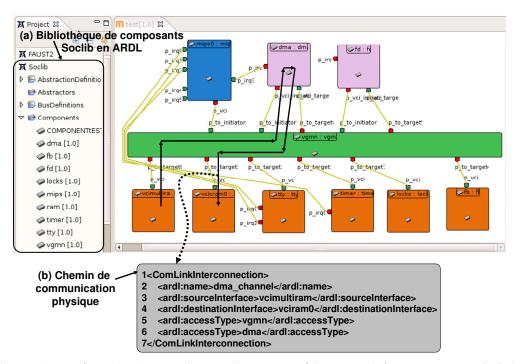

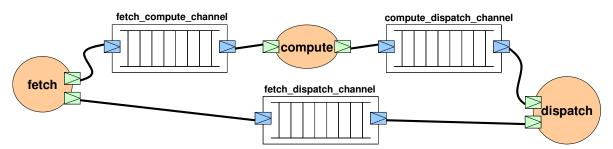

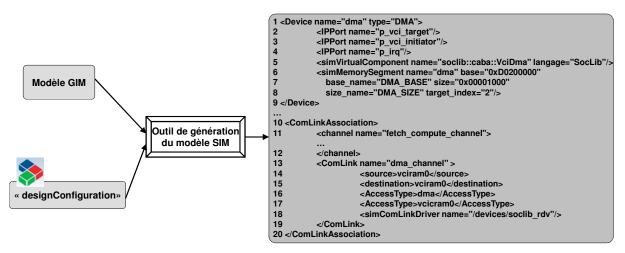

Ce bloc est le contrôleur global des communications et des traitements dans le réseau. C'est lui qui exécute l'ensemble des configurations. Chaque bloc CCC peut gérer jusqu'à quatre contrôleurs de communication en entrée (ICC: Input Configuration Controller) et quatre contrôleurs de communication en sortie (OCC: Output Configuration Controller). Le nombre de « ICC » et « OCC » à utiliser dépend du type de l'IP auquel le CCC est interconnecté. Il fournit différentes fonctionnalités, à savoir la configuration du processeur central et des différents IPs au niveau des communications et des traitements. Il fournit un séquenceur local des configurations (*local scheduling*) et un mécanisme de contrôle de flux des données.