### Design of 60GHz 65nm CMOS Power Amplifier.

Sofiane Aloui

#### ▶ To cite this version:

Sofiane Aloui. Design of 60GHz 65nm CMOS Power Amplifier.. Micro and nanotechnologies/Microelectronics. Université de Bordeaux, 2010. English. NNT: . tel-00544612

### HAL Id: tel-00544612 https://theses.hal.science/tel-00544612

Submitted on 8 Dec 2010

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$N^{\circ}$  d'ordre : —-

### THÈSE

présentée à

### L'Université Bordeaux 1

Ecole doctorale des Sciences Physiques et de l'Ingénieur

### par Sofiane ALOUI

Pour obtenir le grade de

### DOCTEUR

SPÉCIALITÉ : ÉLECTRONIQUE

Design of 60GHz 65nm CMOS Power Amplifier

Soutenance prévue le 6 Décembre 2010

Après avis de :

M. Georg BOECK Professeur Technischen Universität Berlin Rapporteur Patrice GAMAND HDR NXP Semiconductors Rapporteur

Devant la commission d'examen formée de :

| м.     | Didier Belot       | Expert     | ST Microelectronics            | Industriel            |

|--------|--------------------|------------|--------------------------------|-----------------------|

|        | Georg BOECK        | Professeur | Technischen Universität Berlin | Rapporteur            |

| Melle. | Nathalie Deltimple | MCF        | IPB Bordeaux                   | Examinateur           |

| M.     | Yann Deval         | Professeur | IPB Bordeaux                   | Examinateur           |

|        | Patrice GAMAND     | HDR        | NXP Semiconductors             | Rapporteur            |

|        | Eric Kerhervé      | Professeur | IPB Bordeaux                   | Directeur de thèse    |

|        | Robert Plana       | Professeur | LAAS Toulouse                  | Co-Directeur de thèse |

| Li | st of           | Abbre   | eviations                                 | 15 |

|----|-----------------|---------|-------------------------------------------|----|

| Li | st of           | Notat   | ions                                      | 19 |

| In | $\mathbf{trod}$ | uction  |                                           | 23 |

| 1  | Ove             | erview  | of PA design for 60GHz WPAN applications  | 27 |

|    | 1.1             | 60GHz   | z WPAN background                         | 28 |

|    |                 | 1.1.1   | Power devices: CMOS, a key for the future | 28 |

|    |                 | 1.1.2   | 60GHz band overview                       | 32 |

|    |                 | 1.1.3   | 60GHz transceivers                        | 41 |

|    | 1.2             | 60GHz   | z WPAN PA design issues                   | 47 |

|    |                 | 1.2.1   | PA fundamentals                           | 47 |

|    |                 | 1.2.2   | Modulation issues                         | 49 |

|    |                 | 1.2.3   | Scaling technology issues                 | 53 |

|    |                 | 1.2.4   | High frequency issues                     | 55 |

|    | 1.3             | 60GHz   | z CMOS technology PA                      | 56 |

|    |                 | 1.3.1   | State of the art                          | 57 |

|    |                 | 1.3.2   | Conclusion                                | 65 |

|    | 1.4             | Thesis  | s contribution                            | 66 |

| 2  | Pas             | sive de | evice optimization                        | 67 |

|    | 2.1             | Design  | n flow process                            | 68 |

|    |                 | 2.1.1   | High frequency considerations             | 69 |

|    |                 | 2.1.2   | Simulation approximations                 | 72 |

|    |                 | 2.1.3   | Measurement setup                         | 74 |

|    | 2.2             | Passiv  | re Device Characterization                | 79 |

|    |                 | 2.2.1   | Transmission lines                        | 79 |

|    |                 | 222     | Inductors                                 | 92 |

|              |        | 2.2.3 RF-pads                                            | 03        |

|--------------|--------|----------------------------------------------------------|-----------|

|              | 2.3    | Conclusion                                               | 10        |

| 3            | 60G    | Hz PA Design                                             | 13        |

|              | 3.1    | Introduction                                             | 14        |

|              | 3.2    | PA design methodology                                    | 16        |

|              |        | 3.2.1 PA architecture choice                             | 17        |

|              |        | 3.2.2 Power stage design                                 | 21        |

|              |        | 3.2.3 Driver stage design                                | 27        |

|              |        | 3.2.4 Matching network                                   | 29        |

|              |        | 3.2.5 Stability analysis                                 | 31        |

|              | 3.3    | Single-ended PA design                                   | 37        |

|              |        | 3.3.1 Passive device characterization                    | 37        |

|              |        | 3.3.2 Active device characterization                     | 42        |

|              |        | 3.3.3 PA description and results                         | 48        |

|              |        | 3.3.4 Conclusion                                         | 52        |

|              | 3.4    | Differential PA design                                   | 53        |

|              |        | 3.4.1 Balun design                                       | 53        |

|              |        | 3.4.2 PA design description                              | 57        |

|              |        | 3.4.3 PA measurement results                             | 59        |

|              |        | 3.4.4 Conclusion                                         | 63        |

|              | 3.5    | Comparison with the state of the art                     | 64        |

|              | 3.6    | Future works                                             | 69        |

|              |        | 3.6.1 Co-integration PA/emmiter in SoC configuration     | 69        |

|              |        | 3.6.2 Co-integration PA/transceiver in SiP configuration | 70        |

|              | 3.7    | Conclusion                                               | 72        |

| Co           | onclu  | usion 17                                                 | 73        |

| Pι           | ıblica | ations 17                                                | 77        |

| Bi           | bliog  | graphy 17                                                | 79        |

| $\mathbf{A}$ | Pre    | liminary PA design - Circuit 1                           | <b>91</b> |

|              | A.1    | Active device                                            | 92        |

|              | A.2    | Passive device                                           | 93        |

|              | A.3    | PA description                                           | 94        |

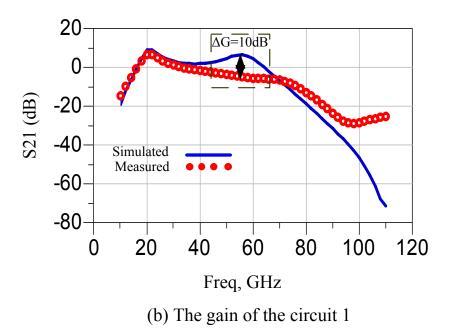

|              | A.4 | Simulation and measurement results                  | 195 |

|--------------|-----|-----------------------------------------------------|-----|

|              |     | A.4.1 Simulation results                            | 195 |

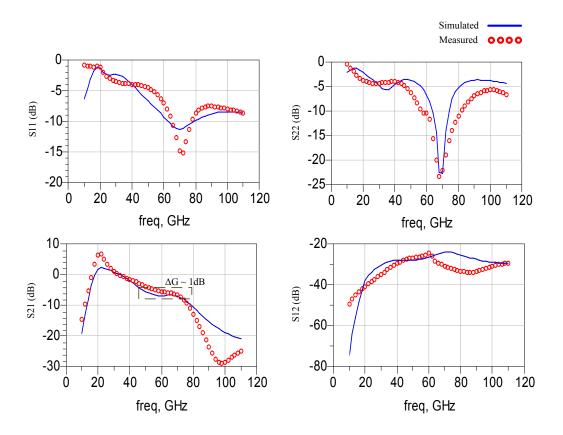

|              |     | A.4.2 Measurement results                           | 195 |

|              |     | A.4.3 Discussion                                    | 195 |

|              | A.5 | Conclusion                                          | 198 |

| В            | Pre | liminary PA design - Circuit 2                      | 199 |

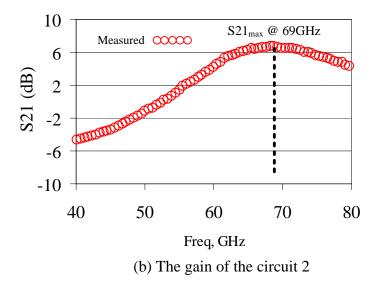

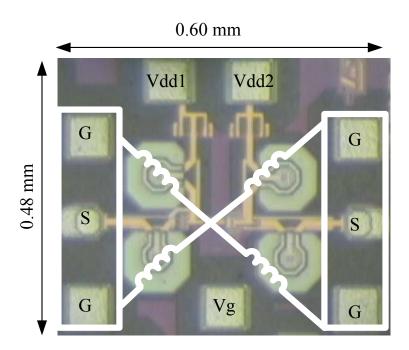

|              | B.1 | PA description and results                          | 200 |

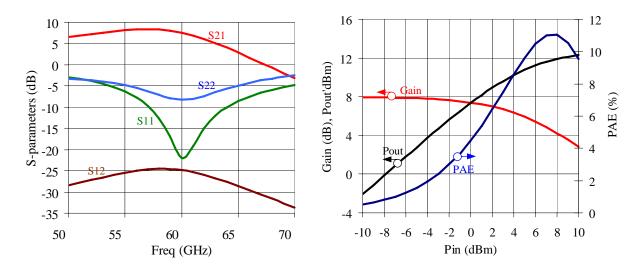

|              |     | B.1.1 Small signal performances                     | 200 |

|              |     | B.1.2 Large signal performances                     | 203 |

|              |     | B.1.3 Performance improvements with load pull setup | 203 |

|              | B.2 | Conclusion                                          | 204 |

| $\mathbf{C}$ | PA  | Characterization for OFDM modulated signal          | 205 |

|              | C.1 | Two-tone simulation                                 | 207 |

|              | C.2 | PA response to OFDM modulated signal                | 208 |

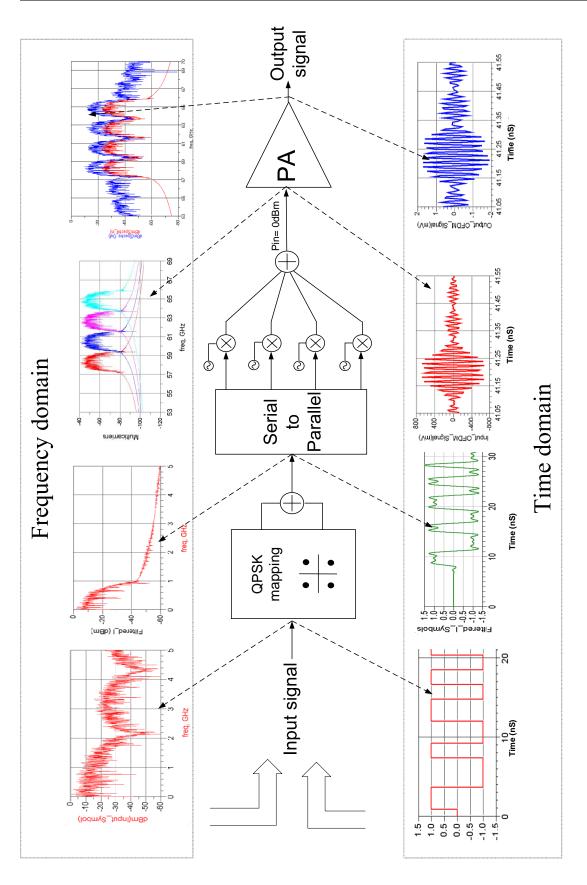

|              |     | C.2.1 Transmitter building blocks                   | 208 |

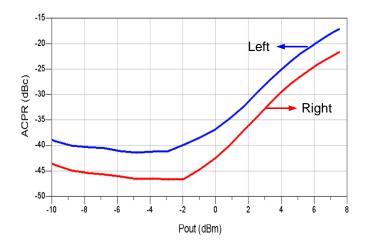

|              |     | C.2.2 ACPR                                          | 210 |

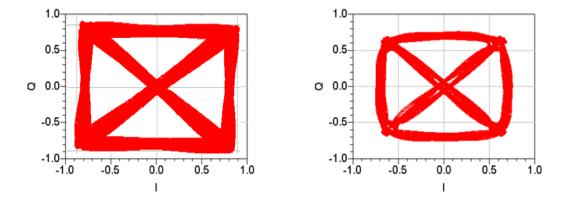

|              |     | C.2.3 EVM                                           |     |

|              | C.3 | Conclusion                                          | 211 |

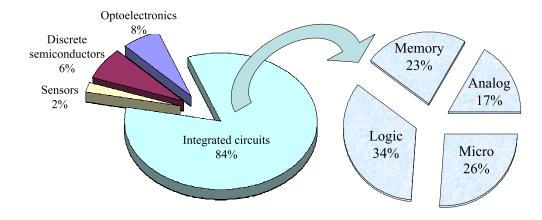

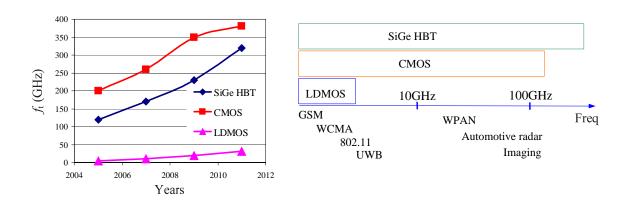

| 1.1  | Semiconductor market share                                                                | 31 |

|------|-------------------------------------------------------------------------------------------|----|

| 1.2  | Silicon ability to target millimeter Wave applications                                    | 31 |

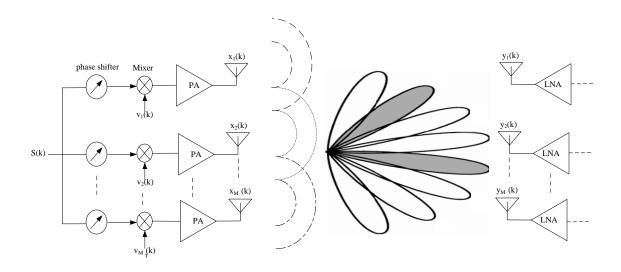

| 1.3  | System combining MIMO and beam-forming techniques                                         | 32 |

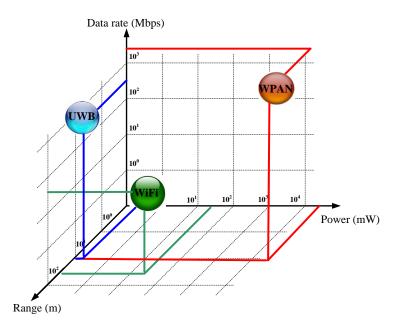

| 1.4  | Comparison of wireless standards-setting                                                  | 33 |

| 1.5  | Millimeter-wave applications                                                              | 34 |

| 1.6  | Oxygen absorption at 60GHz                                                                | 35 |

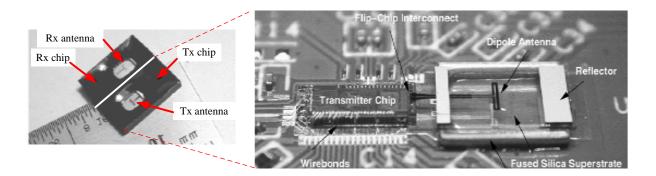

| 1.7  | NEC's AlGaAs/InGaAs transceiver module                                                    | 37 |

| 1.8  | IBM's SiGe single-chip 60GHz transceiver                                                  | 38 |

| 1.9  | IMEC's 45nm 60GHz front-end                                                               | 38 |

| 1.10 | WPAN spectrum overview                                                                    | 39 |

| 1.11 | 60GHz WLAN/WPAN applications                                                              | 39 |

| 1.12 | Heterogenous devices in the 60<br>GHz WPAN $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 40 |

| 1.13 | Building blocks of a SHT                                                                  | 41 |

| 1.14 | 60<br>GHz CMOS single chip radio block diagram based on SHT $\ \ldots \ \ldots \ \ldots$  | 42 |

| 1.15 | Building blocks of a DCT                                                                  | 43 |

| 1.16 | Block diagram and die micrograph of a 60<br>GHz DCT $\ \ldots \ \ldots \ \ldots \ \ldots$ | 43 |

| 1.17 | The SDRT principle                                                                        | 44 |

| 1.18 | Chip micrograph of the 60GHz six-port transceiver based on SDRT                           | 45 |

| 1.19 | Characteristic parameters of a PA                                                         | 47 |

| 1.20 | $P_{out}$ versus $P_{in}$ with a SW signal                                                | 49 |

| 1.21 | OFDM signal generation                                                                    | 51 |

| 1.22 | $P_{out}$ versus $P_{in}$ with a modulated signal                                         | 52 |

| 1.23 | System linearity FoM of a communication system                                            | 53 |

| 1.24 | BSIM3 model considerations                                                                | 54 |

| 1.25 | BEOL of different silicon technologies                                                    | 55 |

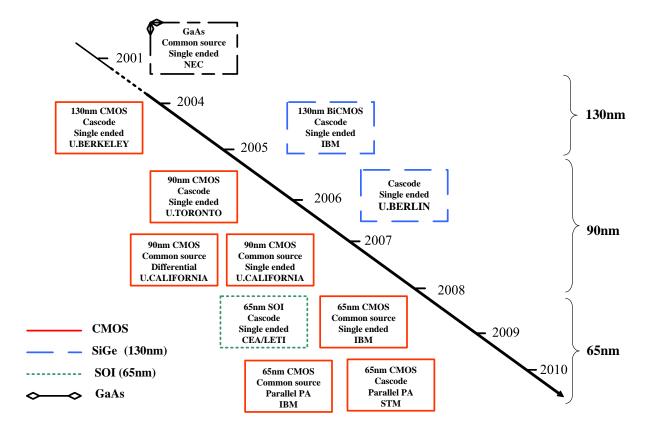

| 1.26 | 60GHz PA realizations in time                                                             | 56 |

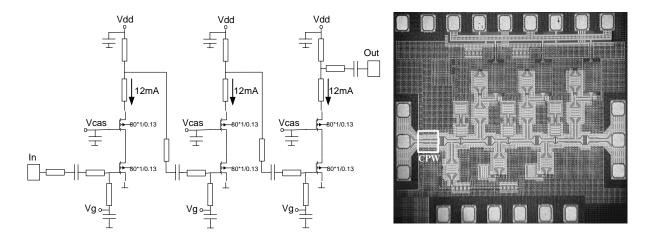

| 1.27 | 60GHz PA in 130nm based on T-lines                                                        | 57 |

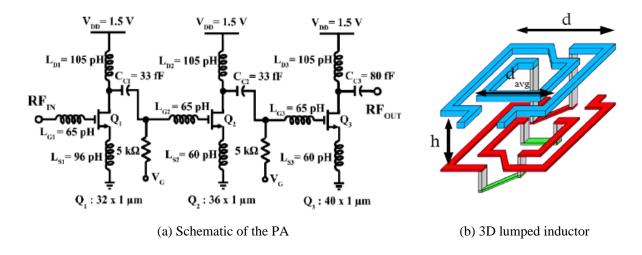

| 1.28 | 60GHz PA in 130nm based on 3D lumped inductors                                       | 58  |

|------|--------------------------------------------------------------------------------------|-----|

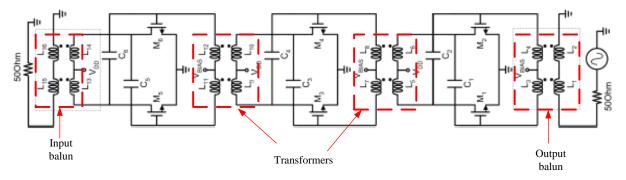

| 1.29 | $60 \mathrm{GHz}$ PA in $65 \mathrm{nm}$ based on baluns                             | 59  |

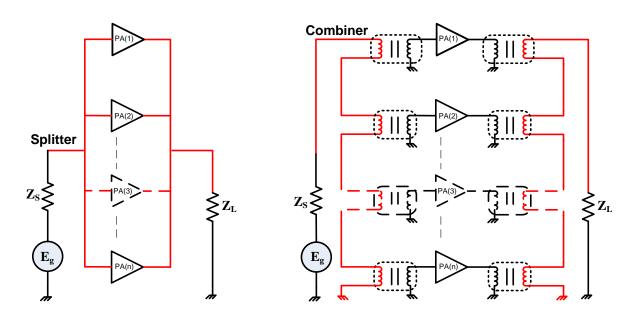

| 1.30 | PA in parallel topologies                                                            | 60  |

| 1.31 | Chip micrography of a current combining PA                                           | 61  |

| 1.32 | 60GHz PA measured large signal parameters                                            | 62  |

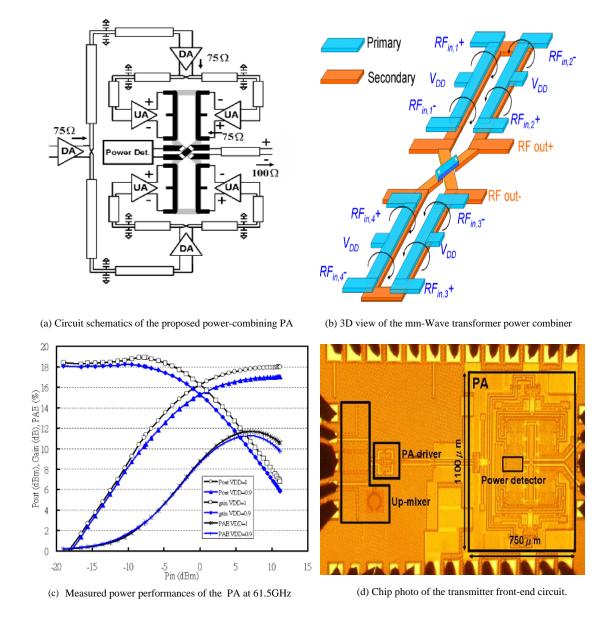

| 1.33 | Building bloc of a power-combining PA based on mmW transformer power combiner $$     | 63  |

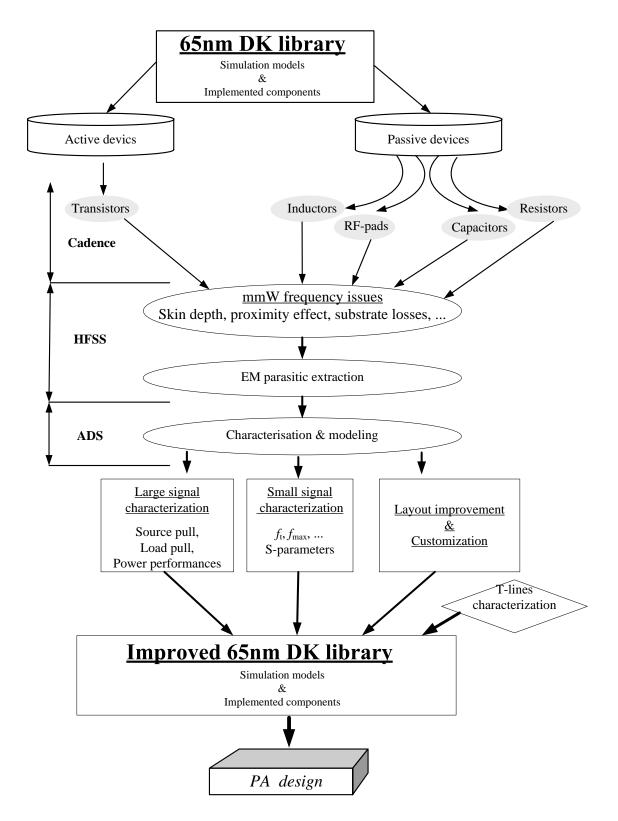

| 2.1  | Design flow process of passive device characterization                               | 70  |

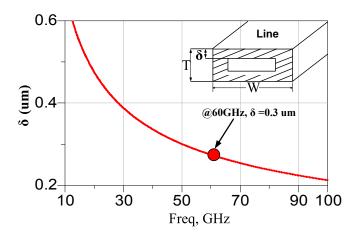

| 2.2  | Skin depth effect vs. frequency                                                      | 71  |

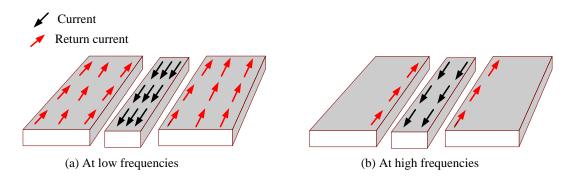

| 2.3  | Frequency-dependent return current path in a CPW line                                | 71  |

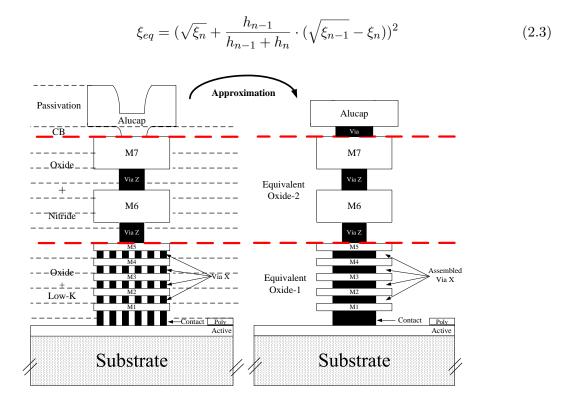

| 2.4  | A 65nm CMOS BEOL structure                                                           | 73  |

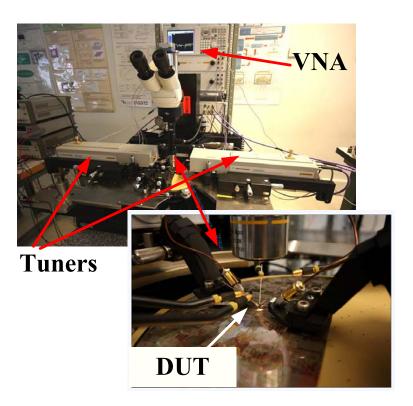

| 2.5  | Agilent mmW VNA (10MHz to 110GHz) photography                                        | 74  |

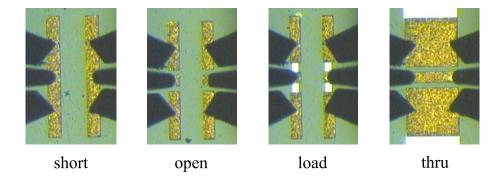

| 2.6  | SOLT method circuits photographies                                                   | 75  |

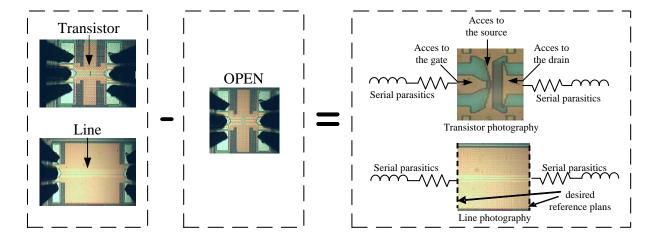

| 2.7  | Open method parasitic extraction                                                     | 76  |

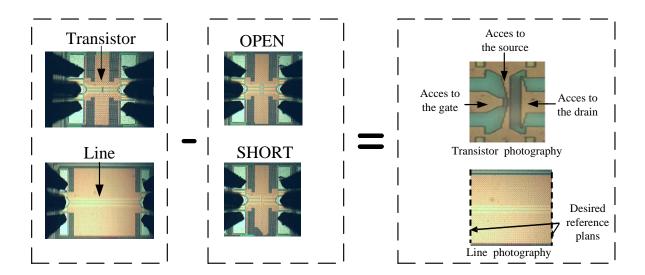

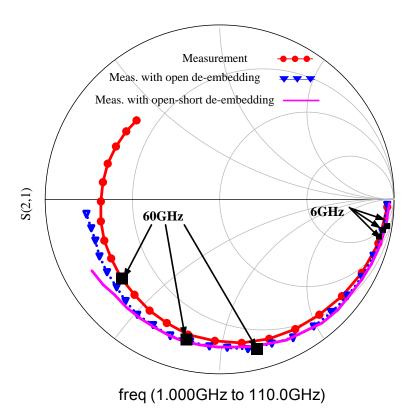

| 2.8  | Open short method parasitic extraction                                               | 77  |

| 2.9  | Impact of de-embedding methods on T-line measurement results                         | 78  |

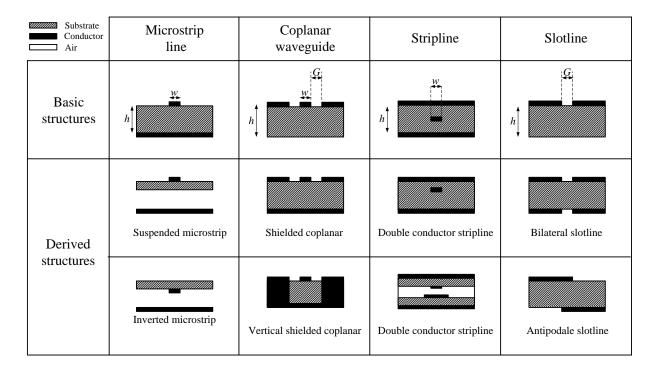

| 2.10 | Main T-lines structures                                                              | 80  |

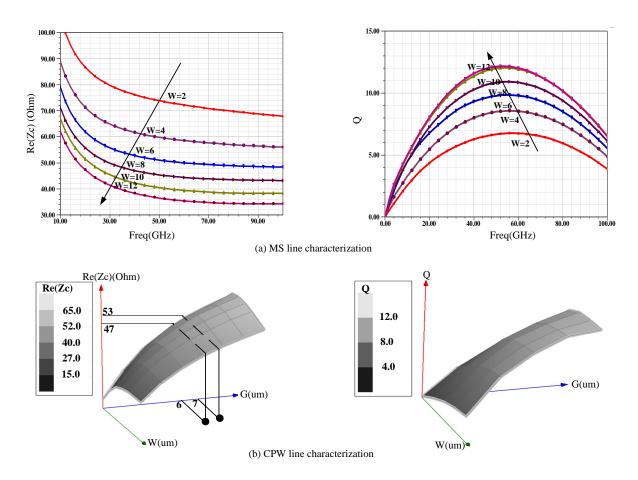

| 2.11 | Characterization of a MS line and a CPW line                                         | 82  |

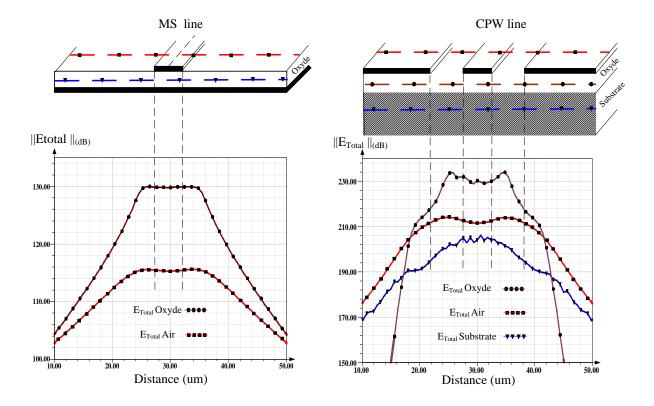

| 2.12 | Electric field distribution in a MS line and a CPW line                              | 83  |

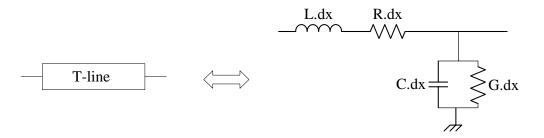

| 2.13 | A RLCG T-line model                                                                  | 87  |

| 2.14 | Simulated and measured RLCG parameters of a CPW line $(w,G)=(10\mu m,6.5\mu m)$      | 89  |

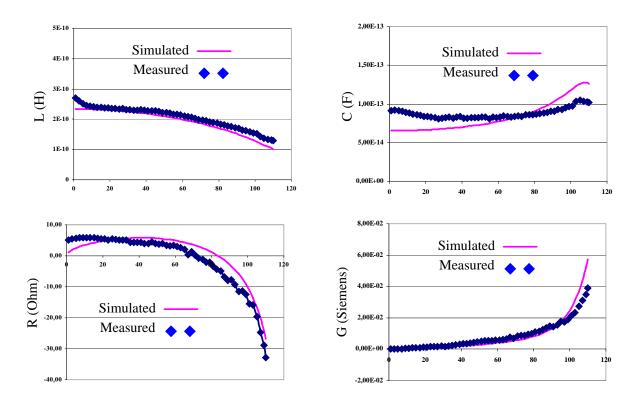

| 2.15 | A distributed RLCG T-line model                                                      | 89  |

| 2.16 | Determination of T-line $T_r$                                                        | 90  |

| 2.17 | $Z_c$ of different T-line structures                                                 | 90  |

| 2.18 | Attenuation in a CPW line $(w, G) = (10\mu m, 6.5\mu m)$                             | 91  |

| 2.19 | Octagonal inductor structure                                                         | 93  |

| 2.20 | Inductor lumped model                                                                | 93  |

| 2.21 | Performances of the octagonal inductor model                                         | 94  |

| 2.22 | Inductor lumped model                                                                | 95  |

| 2.23 | Inductor lumped model                                                                | 95  |

| 2.24 | Effect of shielding inductor on $L$ and $Q$ at $mmW$ frequencies                     | 97  |

| 2.25 | Effect of the RF strip design on $L$ and $Q$ at $mmW$ frequencies                    | 98  |

| 2.26 | Inductive mutuals in a square inductor                                               | 99  |

| 2.27 | Current distribution with illustration of the mutual effect                          | 99  |

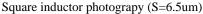

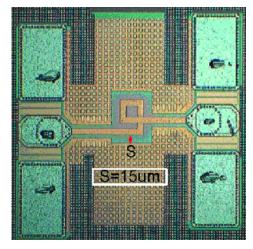

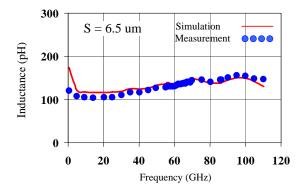

| 2.28 | Die photographies of the two square inductors, $S=6.5\mu m$ and $S=15\mu m$          | 101 |

| 2.29 | Simulated vs. Measured $L$ of the two inductors $\ldots \ldots \ldots \ldots \ldots$ | 101 |

| 2.30 | The effect of $S$ on $L$ and $Q$                                                               |

|------|------------------------------------------------------------------------------------------------|

| 2.31 | RF-Pad structure and layout                                                                    |

| 2.32 | ESD circuit schematic                                                                          |

| 2.33 | RF-pad behavior $(C_p \text{ and } Q)$ at $f \leq 20 \text{GHz}$ and at $f \geq 20 \text{GHz}$ |

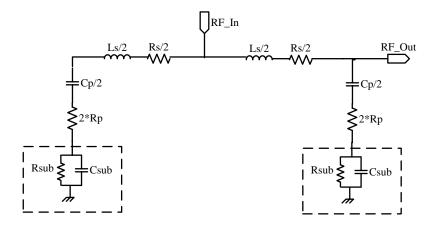

| 2.34 | An improved RF-pad lumped model                                                                |

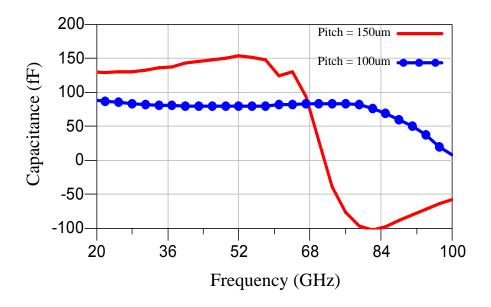

| 2.35 | The effect of the pitch on RF-pad resonance                                                    |

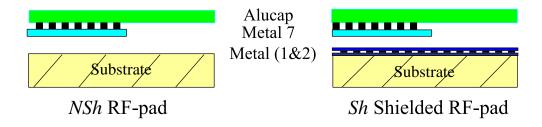

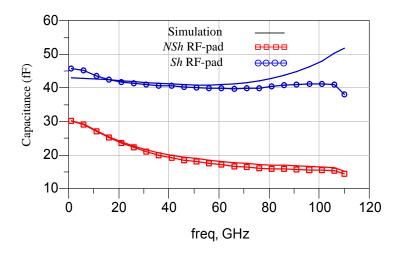

| 2.36 | The structures of a $Sh$ RF-pad and a $NSh$ RF-pad                                             |

| 2.37 | Measured and simulated capacitance of RF-pads                                                  |

| 2.38 | The impact of a RF-pad pattern shield on impedance matching and losses $10^{\circ}$            |

| 2.39 | The impact of a RF-pad pattern shield on circuit mismatch and losses 109                       |

| 3.1  | Generic PA structure                                                                           |

| 3.2  | A $mmW$ PA process flow diagram                                                                |

| 3.3  | Different PA architectures                                                                     |

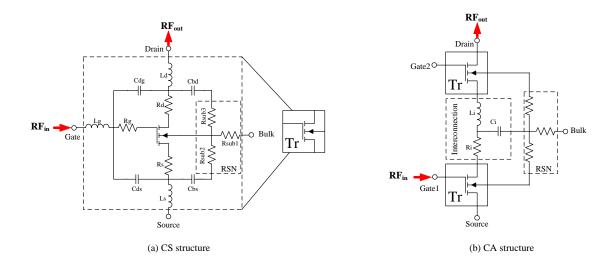

| 3.4  | Equivalent circuit of a CS and a CA structure                                                  |

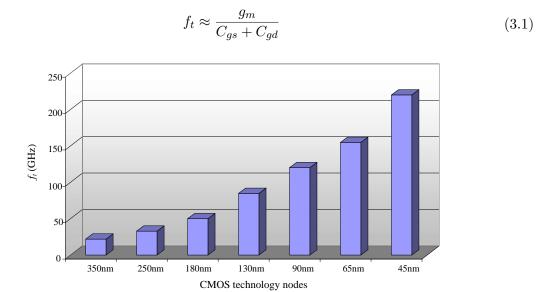

| 3.5  | $f_t$ enhancement with technology evolution                                                    |

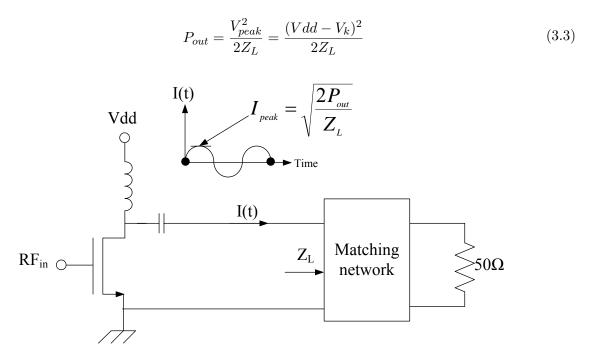

| 3.6  | Maximum power delivered to $Z_L$                                                               |

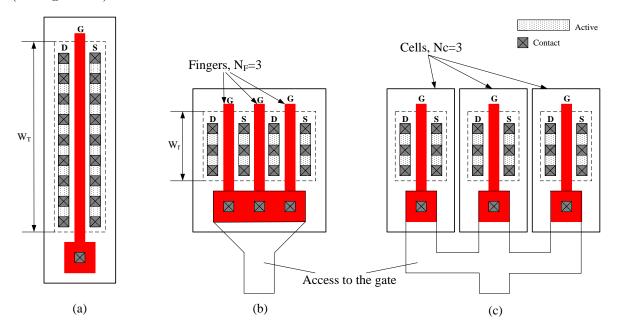

| 3.7  | Different configurations for the same $W_T$                                                    |

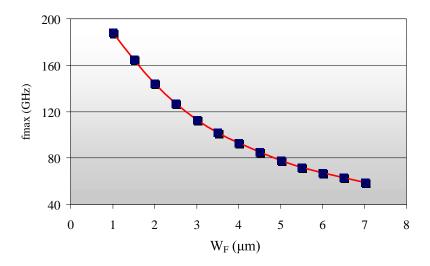

| 3.8  | $f_{max}$ as a function of $W_F$ for 1 finger of an NMOS transistor                            |

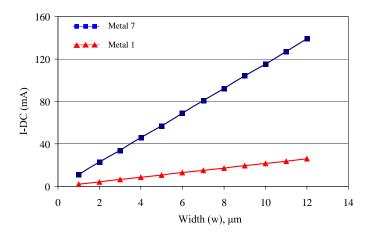

| 3.9  | Limits of DC current as a function of $w$                                                      |

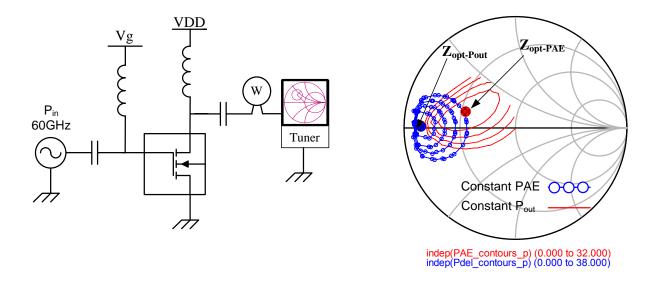

| 3.10 | Determination of $Z_{opt}$ with load pull simulation setup                                     |

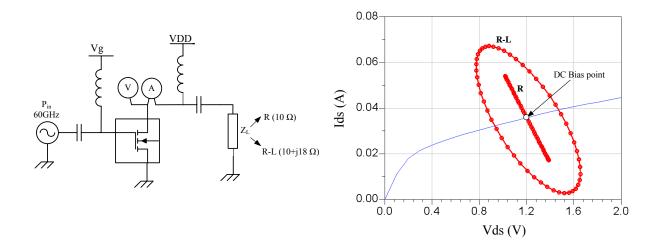

| 3.11 | Load line shapes for different $Z_L$                                                           |

| 3.12 | Illustration of linearity worsening because of the driver stage                                |

| 3.13 | Matching networks in a PA                                                                      |

| 3.14 | Causes of instability in a $mmW$ PA                                                            |

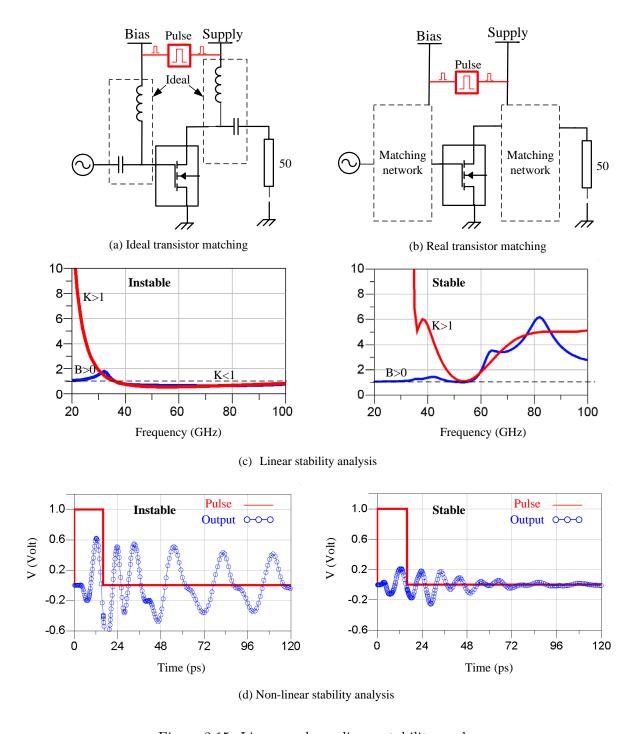

| 3.15 | Linear and non-linear stability analyzes                                                       |

| 3.16 | Background of the circuit 1                                                                    |

| 3.17 | Novel ground plan layout                                                                       |

| 3.18 | Novel ground plan layout                                                                       |

| 3.19 | Background of the circuit 2                                                                    |

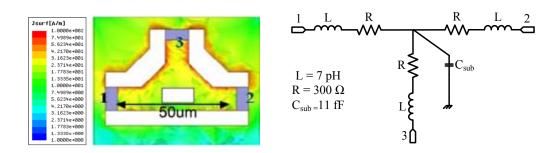

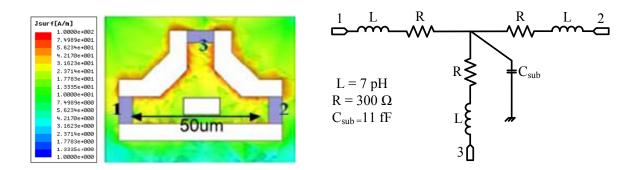

| 3.20 | T-junction current distribution and its lumped model                                           |

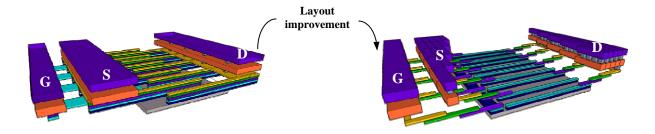

| 3.21 | Layout optimization of a 65nm NMOS transistor                                                  |

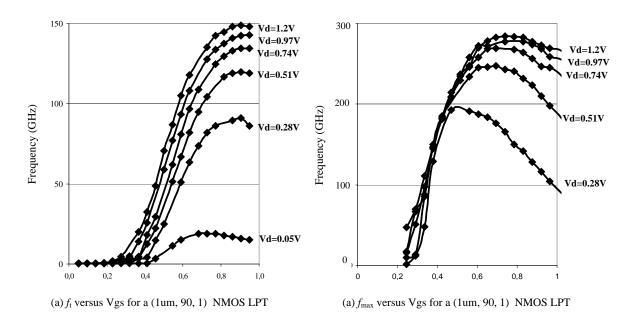

| 3.22 | $f_t$ and $f_{max}$ for a $(1\mu m, 90, 1)$ 65nm NMOS LPT                                      |

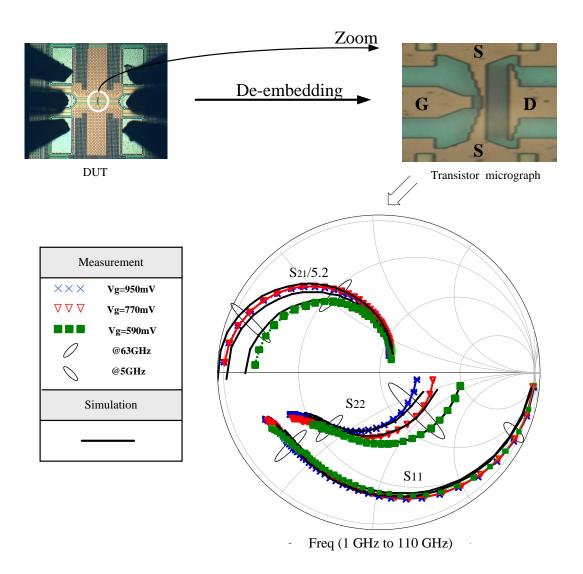

| 3.23 | Measured and modeled S-parameters for $V_{dd}=1.2V$                                            |

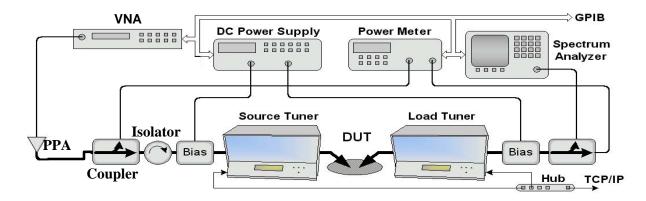

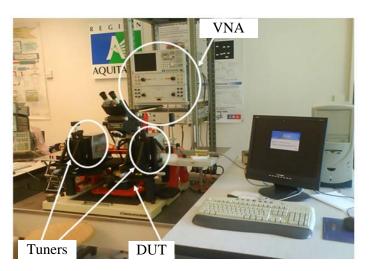

| 3.24 | Load pull measurement setup                                                                    |

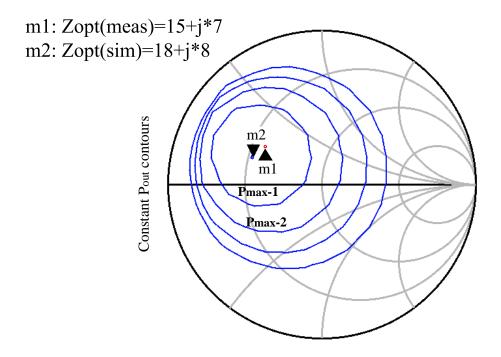

| 3.25 | Measured and simulated optimum impedance to deliver a maximum $P_{out}$ 140                    |

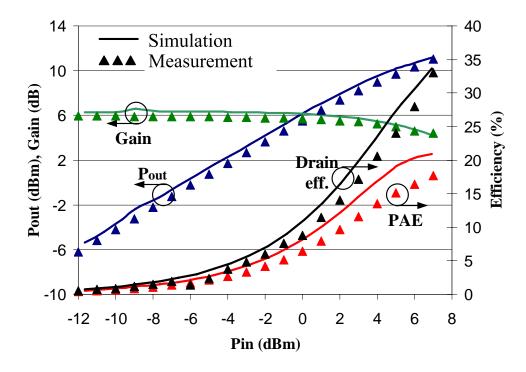

| 3.26 | Power performances of the power transistor at $Z_{opt}$ for a maximum $P_{out}$ 1             | 47 |

|------|-----------------------------------------------------------------------------------------------|----|

| 3.27 | I-V characteristics for a $(W_f, N_f, N_c) = (1\mu m, 90, 1)$ NMOS LPT                        | 47 |

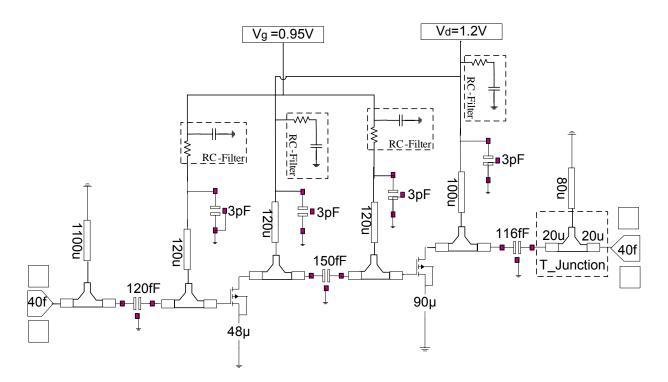

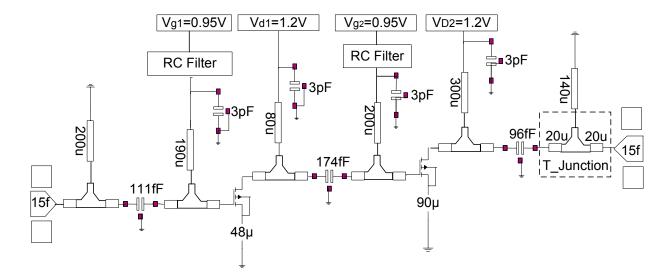

| 3.28 | Schematic of the 60GHz single-ended PA in 65nm CMOS technology 14                             | 48 |

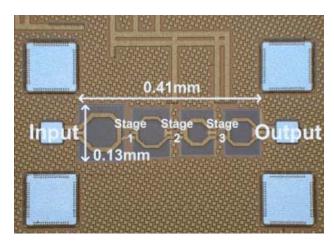

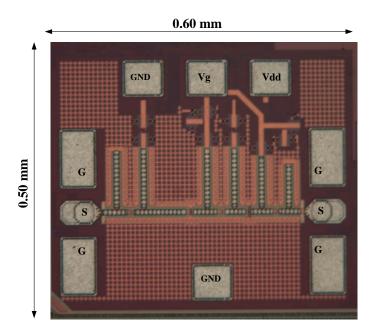

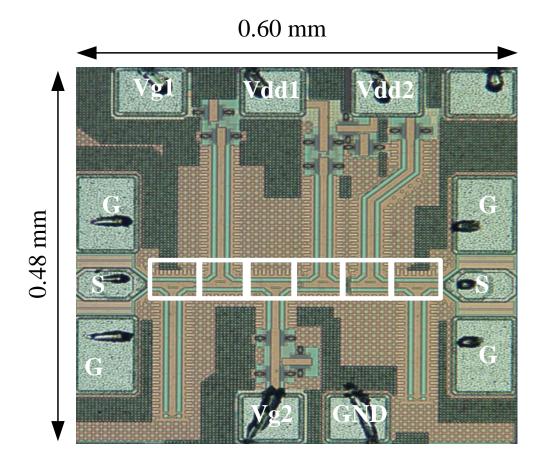

| 3.29 | Die photography of the $60\mathrm{GHz}$ single-ended PA in $65\mathrm{nm}$ CMOS technology 14 | 49 |

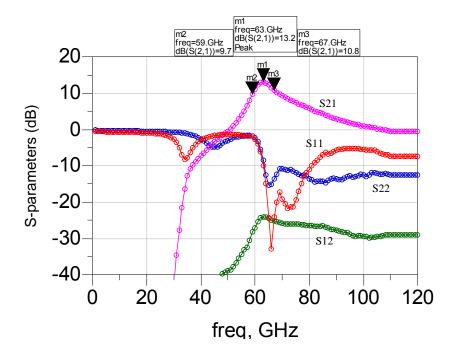

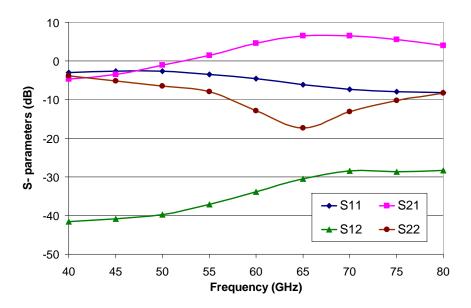

| 3.30 | Measured S-parameters at the bias point $(V_{gs}, V_{ds}) = (0.95V, 1.2V)$                    | 49 |

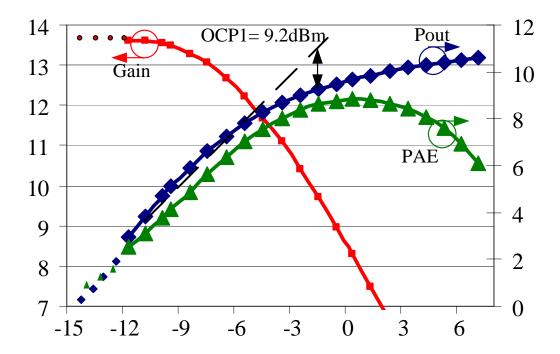

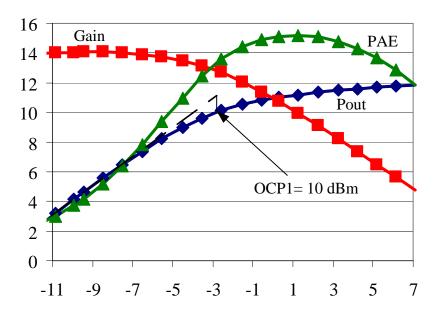

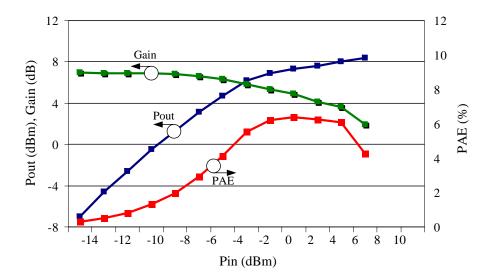

| 3.31 | Measured $P_{out}$ , gain and $\eta_d$ at 63GHz $(V_{gs}, V_{ds}) = (0.95V, 1.2V) \dots 1.00$ | 50 |

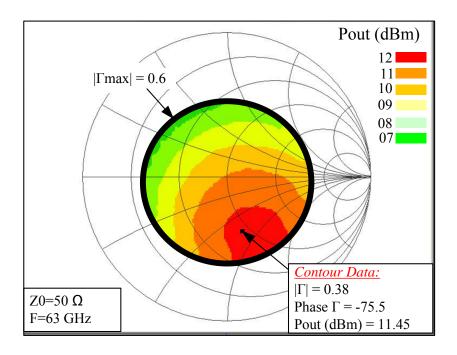

| 3.32 | $Z_{opt}$ determination to deliver a maximum of $P_{out}$ at 63GHz                            | 51 |

| 3.33 | Measured $P_{out}$ , gain and PAE at 63GHz                                                    | 51 |

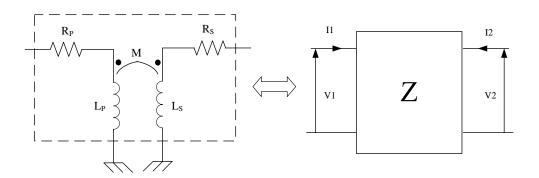

| 3.34 | Simplified model of a generic transformer                                                     | 53 |

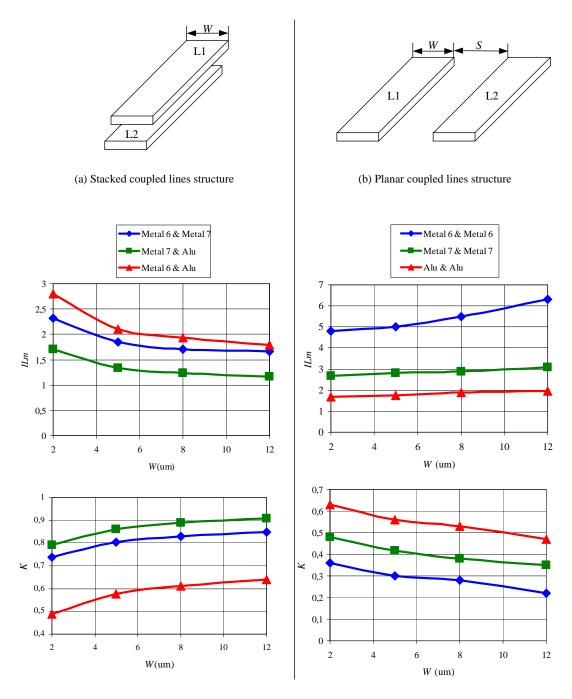

| 3.35 | Coupled lines characterization with EM simulation                                             | 55 |

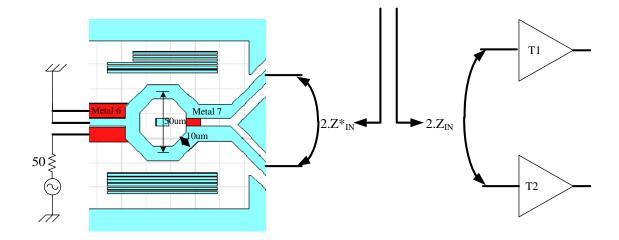

| 3.36 | Balun integration in a 60GHz PA (only input is plotted)                                       | 57 |

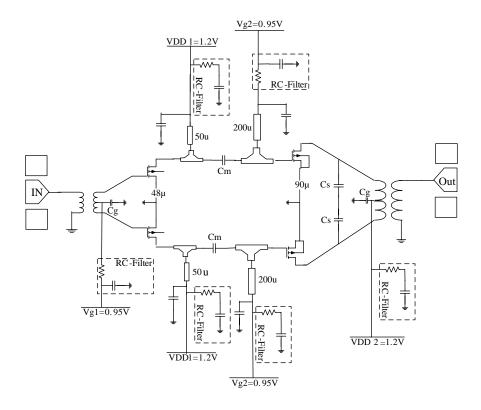

| 3.37 | Schematic of the 65nm 60GHz differential PA                                                   | 58 |

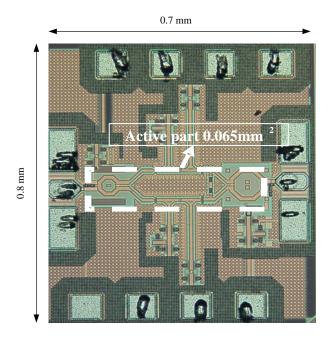

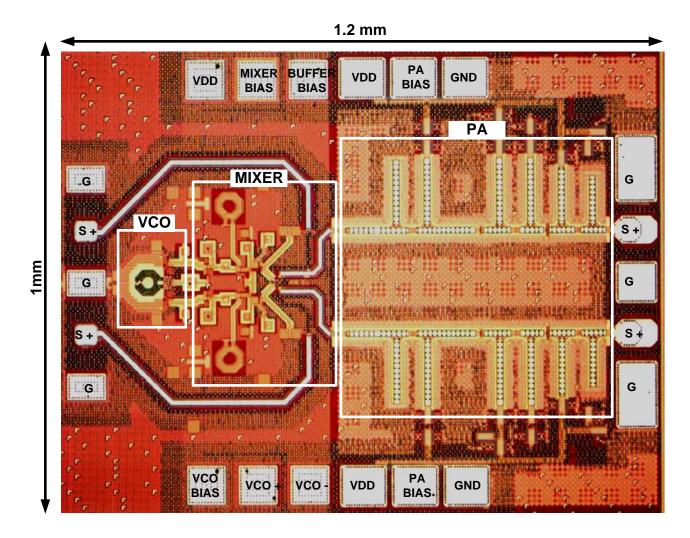

| 3.38 | Die photography of the 60GHz differential PA                                                  | 58 |

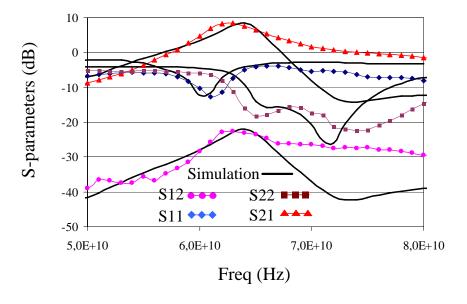

| 3.39 | Measured S-parameters at $(V_{gs}, V_{ds}) = (0.95V, 1.2V)$                                   | 59 |

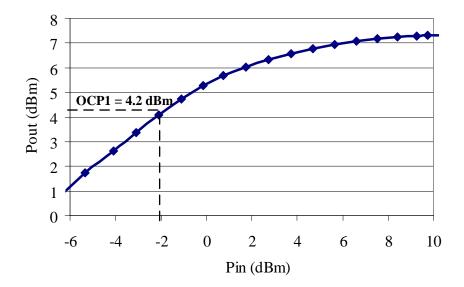

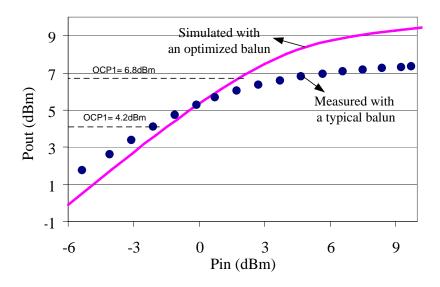

| 3.40 | Measured power transfer at $(V_{gs}, V_{ds}) = (0.95V, 1.2V)$                                 | 60 |

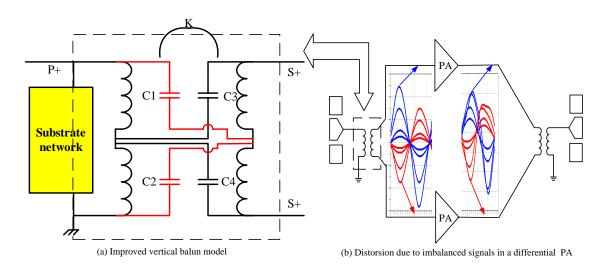

| 3.41 | Balun assymetries and their consequence on the PA operation                                   | 60 |

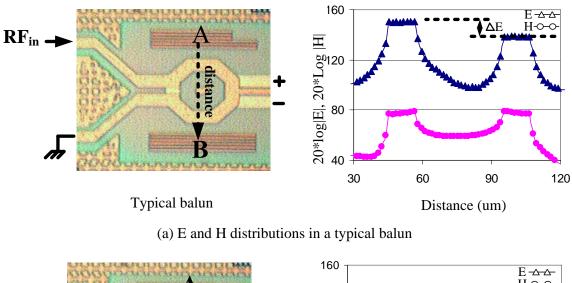

| 3.42 | Comparison between a typical and an optimized baluns                                          | 61 |

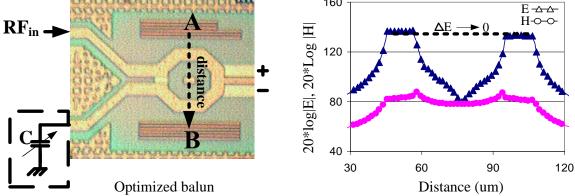

| 3.43 | Influence of the capacitor on CCMR                                                            | 62 |

| 3.44 | Simulated power transfer with the improved balun                                              | 63 |

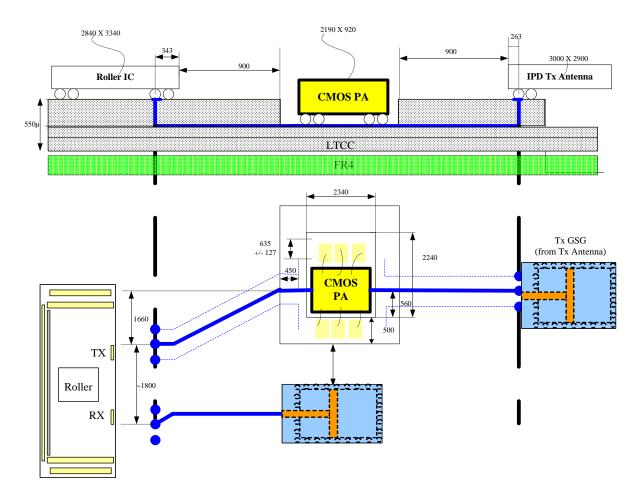

| 3.45 | PA integration in the NANOCOM emitter                                                         | 69 |

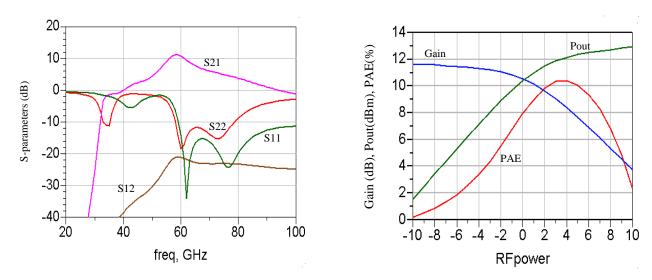

| 3.46 | Simulated S-parameters and power performances of the pseudo-differential $60\mathrm{GHz}$     |    |

|      | PA                                                                                            | 70 |

| 3.47 | PA integration in the QSTREAM transceiver                                                     | 71 |

| A 1  |                                                                                               | 00 |

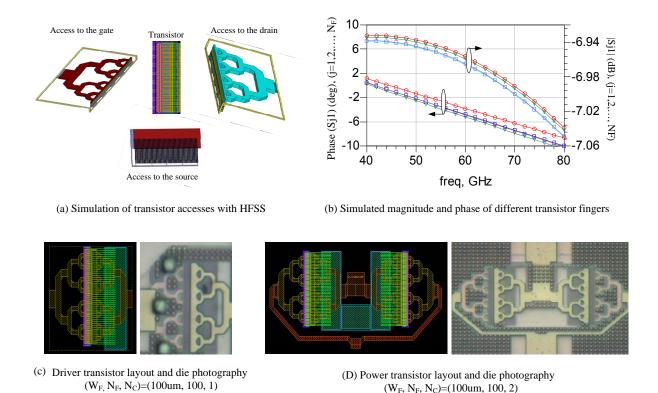

| A.1  | Design of the power and driver transistors                                                    |    |

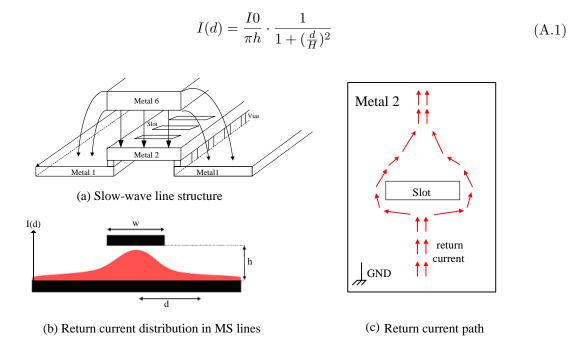

|      | Customized T-line structure                                                                   |    |

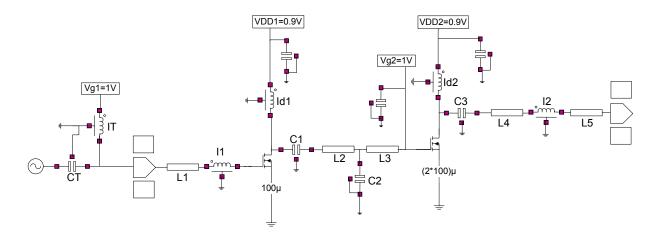

| A.3  | Schematic of the 60GHz PA in 65nm CMOS technology                                             |    |

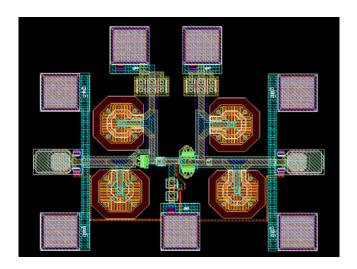

| A.4  | Die photography of the fabricated 60GHz PA in 65nm CMOS technology 19                         |    |

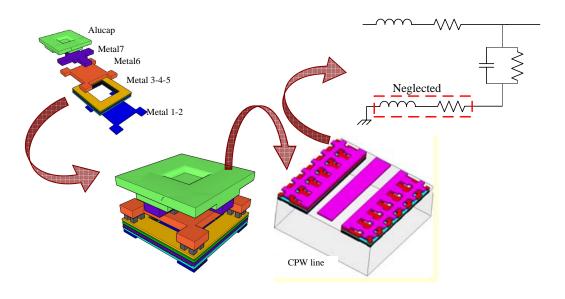

| A.5  | Small and large signal simulation results of circuit 1                                        |    |

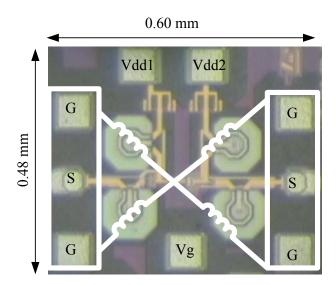

| A.6  | Die photography and comparison between simulated and measured PA gain 19                      |    |

| A.7  | Validation of redo simulation results with measurement results                                | 97 |

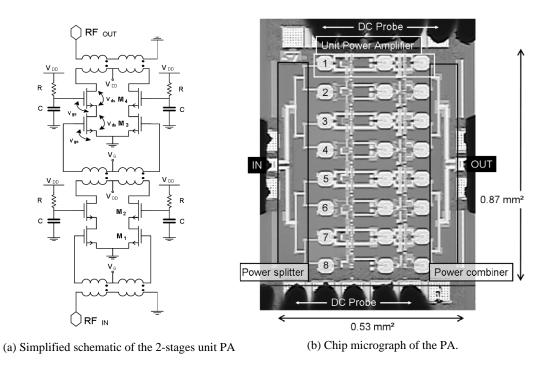

| B.1  | Schematic of the fabricated 60GHz circuit 2                                                   |    |

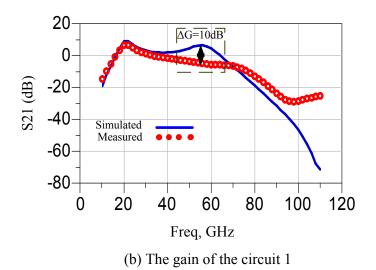

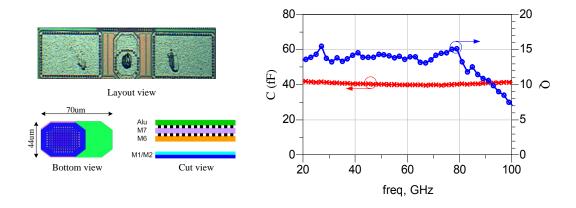

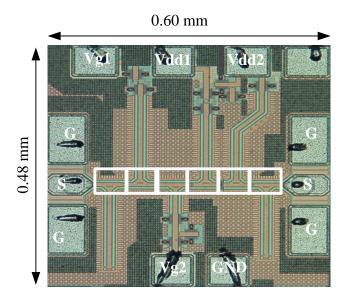

| B.2  | Die photography of the circuit 2 highlighting neglected areas                                 | 01 |

| B.3  | Measured S-parameters at the bias point $(V_{gs}, V_{ds}) = (0.95V, 1.2V)$                    | 02 |

| B.4  | Tee junction current distribution and its lumped model                                        | 02 |

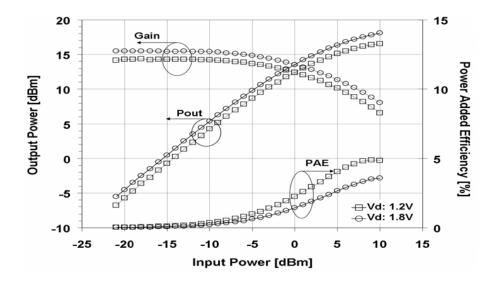

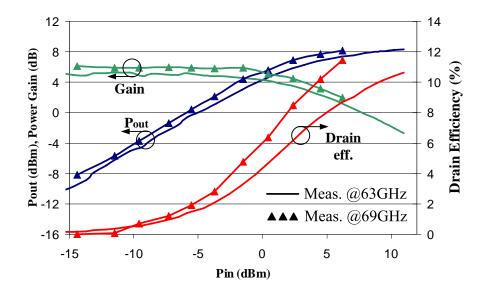

| B.5 | Measured $P_{out}$ , gain and $\eta_d$ at 63GHz and 69GHz at $(V_{gs},V_{ds})=(0.95V,1.2V)$ . | 203 |

|-----|-----------------------------------------------------------------------------------------------|-----|

| B.6 | Measured $P_{out}$ , gain and $PAE$ at 63GHz and 69GHz at $(V_{gs}, V_{ds}) = (0.95V, 1.2V)$  | 204 |

| - · |                                                                                               |     |

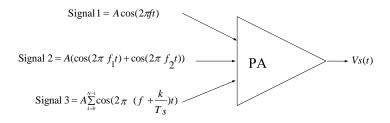

| C.1 | Different input signals applied to the PA                                                     | 206 |

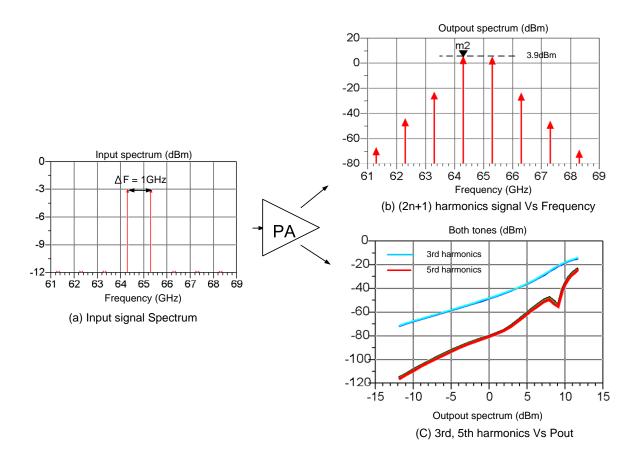

| C.2 | Two-tone simulation                                                                           | 207 |

| C.3 | WPAN spectrum overview                                                                        | 208 |

| C.4 | Transmitter path1                                                                             | 209 |

| C.5 | ACPR (left and right) vs. Pout                                                                | 210 |

| C 6 | OPSK Constellation in linear and saturated regime                                             | 210 |

| 1.1  | Physical parameters for Si, GaAs and $\alpha$ -SiC substrates    |

|------|------------------------------------------------------------------|

| 1.2  | Comparison of the principal materials properties                 |

| 1.3  | 60GHz channel insertion loss                                     |

| 1.4  | Measured performances summary of SHT, DCT and SDRT               |

| 1.5  | PAPR for different modulated signals                             |

| 1.6  | Comparison of PAs dedicated to 60GHz WPAN standard 64            |

| 2.1  | MS lines Versus CPW lines                                        |

| 2.2  | Sh RF-pad vs. $NSh$ RF-pad                                       |

| 3.1  | Comparison between PA architectures                              |

| 3.2  | Comparison between CS and CA structures                          |

| 3.3  | Comparison between LPT and GPT                                   |

| 3.4  | Extrinsic parasitic capacitances                                 |

| 3.5  | Large signal PA performances                                     |

| 3.6  | Comparison between planar and stacked coupled lines              |

| 3.7  | Comparison of single-ended CMOS 60GHz PAs                        |

| 3.8  | Comparison of parallel CMOS 60GHz PAs                            |

| 3.9  | Comparison of 60GHz PAs designed with different technologies 167 |

| 3.10 | Large signal pseudo-differential PA performances                 |

| B.1  | Large signal PA performances                                     |

### List of Abbreviations

AC Alternative Current

ADC Analog-to-Digital Converter

**ASK** Amplitude Shift Keying

BEOL Back End Of LineBiCMOS Bipolar-CMOS

**BPSK** Binary Phase Shift Keying

BWRC Berkeley Wireless Research Center

CB2 Copper Bondpad

**CCDF** Complementary Cumulative Distribution Function

**CDMA** Code Division Multiple Access

CMOS Complementary Metal Oxide Semiconductor

CMRR Common Mode Rejection Ratio

**CPW** Co-Planar Waveguide

CA Cascode

**CS** Common Source

DAC Digital-to-Analog ConverterDAT Distributed Active Transformer

**DC** Direct Current

**DCT** Direct Conversion Transceiver

**DDRT** Software Defined Radio Transceiver

**DK** Design Kit

DS-UWB Direct Sequence UWBDUT Device Under Test

**ECMA** European Computer Manufacturers Association

**EM** Electro-Magnetic

**ESD** Electro-Static Discharge

FCC Federal Commission Communication

**FDTD** Finite-Difference Time-Domain

FEM Finite Element Method

FET Field-Effect Transistor

FIR Finite Impulse Response

**FoM** Figure of Merit

FSK Frequency Shift Keying

GaAs Gallium ArsenideGaN Gallium Nitride

**GPT** General Purpose Transistor

HB Harmonic BalanceHD High DefinitionIC Integrated Circuit

**IEEE** Institution of Electrical and Electronics Engineers

IF Intermediate FrequencyIRF Image Radio Frequency

ISM Industrial, Scientific and Medical

**ISSCC** International Solid-State Circuits Conference

ITRS International Technology Roadmap for Semiconductors

**LDMOS** Laterally Diffused Metal Oxide Semiconductor

LRM Line-Reflect-Match

**LRRM** Line-Reflect1-Reflect2-Match

**LNA** Low Noise Amplifier

LOS Local Oscillator

LOS Line-Of-Sight

**LPT** Low Power Transformer

LTCC Low Temperature Co-fired Ceramic

MIMO Multiple-Input Multiple-Output

MMIC Monolithic Microwave Integrated Circuit

mmW millimeter Wave

MS MicroStrip

NDF Normalized Determinant Function

**NF** Noise Figure

**NLOS** Non-Line-Of-Sight

**OFDM** Orthogonal Frequency Division Multiplexing

OOK On-Off Keying

PA Power Amplifier

**PAPR** Power Average to Power Ratio

PCB Printed Circuit Board

PDF Probability Distribution Function

PGS Patterned Ground Shield

**PHEMT** Pseudomorphic High Electron Mobility Transistors

PLL Phase Locked Loop

**PPM** Pulse Position Modulation

**PSK** Phase Shift Keying

**QAM** Quadrature Amplitude Modulation

QoS Quality of Service

QPSK Quadrature PSK

RF Radio-Frequency

**RX** Receiver

SCBT Single Carrier Block Transmission SDRT Software-Defined Radio Transceiver

SGS Single-Ground-Signal SGS Single-Ground-Signal

**SHT** Super-Heterodyne Transceiver

SiGe Silicon Germanium

SiO2 Silicon Dioxide

SiP System in Package

SNR Signal-to-Noise Ratio

SoC System on Chip

**SOLT** Short-Open-Load-Through

SR Software Radio

**SRF** Self-Resonant Frequency

**SW** Sine Wave

**TEM** Transverse Electromagnetic

T-lines Transmission lines

TRL Through-Reflect-Line

TX Transmitter

UCLA University of California

**UWB** Ultra-Wideband

VCO Voltage-Controlled Oscillator

VNA Vector Network Analyzer

WCDMA Wide band CDMA

WLAN Wireless Local Area Network

WiFi Wireless Fidelity

WPAN Wireless Personal Area Network

### List of Notations

ACPRAdjacent Channel Power Ratio

BERBit Error Rate Ccapacitance

$C_{ds}$ Drain to Source Capacitance

Choke-LChoke Inductors

$C_{gs}$ Gate to Source Capacitance  $C_{gd}$ Gate to Drain Capacitance

$C_p$ Parasitic Capacitance

DDiameter

$E_c$ Critical electric field

$E_g$ Gap Energy

EIRPEquivalent Isotropically Radiated Power

EVMError Vector Magnitude

$f_{max}$ Maximum Frequency of Oscillation

Transition Frequency  $f_t$

GGap

$G_{av}$ Available gain

GBpsGigaByte per second  $G_c$ Compression Gain  $G_{op}$ Operating gain  $G_{tr}$ Transducer Gain Transconductance

hHeight

$g_m$

$IL_M$ Minimum Insertion Loss

$J_c$ Current Density

kThermal Conductivity

KCoupling Factor

LInductance

Drain Inductance  $L_d$  $L_g$ Gate Inductance  $L_s$ Source Inductance MBpsMegaByte per second  $N_C$ Number of Cells  $N_F$ Number of Fingers NShNon-Shielded OBOOutput Back-Off Output 1dB Compression Point OCP1PAEPower Added Efficiency  $P_{in}$ Input Power  $P_{DC}$ DC power consumption  $P_{out}$ Output Power Average Output Power  $P_{outAV}$  $P_{Peak}$ Peak Power Saturated Power  $P_{sat}$ PBOPeak Back Off QQuality Factor λ Wavelength Impedance Transformation Ratio RResistance  $R_d$ Drain Resistance Gate Resistance  $R_g$  $R_s$ Source Resistance SDistance ShShielded  $SiO_2$ Silicon Dioxide  $T_r$ Rise Time  $tg(\delta)$ Loss Factor Saturated Velocity  $V_{sat}$ knee Voltage  $V_k$

Width

Finger Width

Transistor Width

w  $W_F$

$W_T$

- $Z_c$  Characteristic Impedance

- $Z_{in}$  Input Impedance

- $Z_{opt}$  Optimum Impedance

- $Z_{out}$  Output Impedance

- $Z_L$  Load Impedance

- $Z_s$  Source Impedance

- $Z^*$  Conjugate Impedance

- $\eta_d$  Drain Efficiency

- $\epsilon_r$  Effective dielectric constant

- $\delta$  Skin Depth

- $\mu$  Mobility

- $\mu$  Mobility

- $\epsilon_r$  Relative Permittivity

- $\gamma$  Complex Propagation Constant

- $\gamma_{in}$  Input Reflection Coefficient

- $\gamma_{out}$  Output Reflection Coefficient

### Introduction

Telecommunication industry claims for increasing data rate in wireless communication systems. Nowadays, current data rates of radio communication systems are limited to some 100Mbps. This limitation is the result of the high saturation and the coexistence of wireless standards in frequency bands below 10GHz. Despite of the domination of Radio Frequency (RF) wireless devices, mature standards such as Wi-Fi, Bluetooth and UWB can not anymore support both high data rates and strong power specifications.

The major demand of high data rate applications concerns a large panel of home multimedia exchanging data especially for the uncompressed HD data transfer. A particular interest is to operate beyond RF domain to target that demand. Operating at millimeter-Wave frequencies (mmW) frequencies becomes attractive because of the availability of large free frequency band without any close neighbor standards. The 7GHz band around 60GHz is free of use and fulfills the short range gigabit communication requirements.

Semiconductor foundries are getting involved in wireless HD products to ensure a data rate superior to 1Gbps. Based Gallium Arsenide (GaAs) or Silicon Bipolar technologies are well suited to mmW applications and were adopted for first designed products. Those wireless HD products target a large number of consumers. They are subject to cost, size and performances constraints. Their use is costly which prevents from targeting a large scale market.

CMOS technology is known to be the best process for designing digital circuits. More than 80% of the total amount of integrated circuits are designed with that technology. This is the major reason why semiconductor foundries investigate in CMOS technologies even for the design of analog circuits. It drives a fast time to market with a low cost for high integration volume. Hence, a fast improvement in CMOS technology has been seen during the last decade. In this context, emerging CMOS technologies enable for operating at mmW frquencies promising to be competitive against III-V technologies. IBM, IMEC, STMicroelectronics and other companies are now developing complete CMOS technology transceiver operating above 60GHz.

This thesis work is in the frame of the NANOCOMM ANR project and the European QSTREAM project. A 65nm CMOS technology is provided by STMicroelectronics. Those projects aim at realizing low-cost, highly-integrated CMOS transmitter prototypes sending data up to 1 Gbps in a range up to 1 meter to target 60GHz WPAN applications.

The design of 65nm CMOS technology on bulk Power Amplifier (PA) dedicated to 60GHz WPAN standard is here investigated. The designed PA aims at being integrated in mobile device. The optimization of power consumption is one of the major requirement to be focused on because of the limited life time of the battery. Moreover, the PA linearity specification must be also optimized because the 60GHz WPAN standard uses OFDM modulation scheme. The use of the emerging 65nm CMOS technology makes the PA design challenging to meet a good linearity-power consumption trade-off. Indeed, the technology downsizing leads to a reduction of the breakdown voltage and thus sets a low voltage supply. Hence, a high current density is required to provide high output power causing an important dissipated power especially with technology on bulk.

Chapter 1 exposes an overview of PA dedicated to 60GHz WPAN standard. The main applications and the characteristics of the physical layer such as the frequency plan, the modulation and the data rate of the WPAN standard are reminded. As the PA structure also depends on the system architecture, different transceiver architectures are exhibited. The PA fundamentals are depicted to highlight the technological bottleneck and the modulation issues. A state of the art enlists 60GHz CMOS PA realizations detailing their respective novelties.

Chapter 2 presents the characterization and the optimization steps of passive devices before PA design. Working at  $60 \,\mathrm{GHz}$  requires a good knowledge of the  $65 \,\mathrm{nm}$  CMOS technology from STMicroelectronics before being adopted in the design. mmW physical phenomena are quoted and their consideration using HFSS simulator are detailed. As the  $65 \,\mathrm{nm}$  CMOS passive components have never been characterized above  $60 \,\mathrm{GHz}$ , their electrical behavior at RF and mmW frequencies is studied. The impact of layout geometry and substrate to construe simulations and to predict measurements are analyzed. The characterization of T-lines, inductors and RF pads is presented. Optimized structures are proposed.

Chapter 3 focuses on the PA design. It firstly discusses about the defined design flow to design a generic mmW PA. Secondly, additional considerations are studied according to issues met during the design of preliminary PAs. Then, two 65nm CMOS PAs realizations

designed with different topologies are described. The first PA is a single-ended topology while the second one is differential. Their respective simulation and measurement results are analyzed. To compare our works, our designed PAs are compared with the ones in a state of the art targeting the same application to highlight the CMOS PAs performances with other competitive technologies. Finally, promising future works are presented.

Chapter -

1

# Overview of PA design for 60GHz WPAN applications

| 1.1 600 | GHz WPAN background                       | 28        |

|---------|-------------------------------------------|-----------|

| 1.1.1   | Power devices: CMOS, a key for the future | 28        |

| 1.1.2   | 60GHz band overview                       | 32        |

| 1.1.3   | 60GHz transceivers                        | 41        |

| 1.2 600 | GHz WPAN PA design issues                 | 47        |

| 1.2.1   | PA fundamentals                           | 47        |

| 1.2.2   | Modulation issues                         | 49        |

| 1.2.3   | Scaling technology issues                 | 53        |

| 1.2.4   | High frequency issues                     | 55        |

| 1.3 600 | GHz CMOS technology PA                    | <b>56</b> |

| 1.3.1   | State of the art                          | 57        |

| 1.3.2   | Conclusion                                | 65        |

| 1.4 The | esis contribution                         | 66        |

Chapter 1 presents an overview of PA dedicated to 60GHz WPAN standard. A low cost fabrication with CMOS technology is adopted to fulfill a large scale market. The first part demonstrates how the 60GHz band is a promising way to reach gigabit data rate. Different transceiver architectures are exhibited. The second part presents the PA fundamentals with a focus on PA design constraints related to technology scaling, high operating frequency and modulation issues. Finally, a state of the art lists 60GHz CMOS PA realizations detailing their novelties.

Key words: 60GHz standard, CMOS, multimedia convergence.

### 1.1 60GHz WPAN background

#### 1.1.1 Power devices: CMOS, a key for the future

The choice of a technology is related to the constraints of the circuit to be designed. Those constraints are technical, strategical and economical. All these considerations must be analyzed. Designers and managers background is required to determine pro and cons for each process to focus on the most adapted one.

Devices are manufactured on different substrates. Besides acting as mechanical support structures, they directly affect the circuit performances. Two main reasons create the substrate coupling with the circuit. In one hand, the voltage supply to ground commutation in a mixed circuit presents a noise source for the substrate. In the other hand, a non-ideal dielectric leads to current propagation in the substrate. Each material is characterized by the relative permittivity  $(\epsilon_r)$ , the loss factor  $(tg(\delta))$  and must ensure process requirements such as a low roughness. For microwave power applications, high thermal conductivity (k) and high resistivity  $(\rho)$  (or low mobility  $(\mu)$ ) are highly demanded at high operating temperature. Moreover, the substrate height (h) is a geometric parameter that involves the thermal characteristics. Indeed, a thin wafer is necessary to improve thermal dissipation while keeping the support solid. The most used substrate in this context are GaAs, SiC and Si.

| Material | $k_{@300 \deg}$ $(W/(K.cm)$ | $\mu_{e@300K}$ $(cm^2/(V.s))$ | $\zeta_r$ | $tg(\delta)_{@10GHz}$ |

|----------|-----------------------------|-------------------------------|-----------|-----------------------|

| Si       | 1.5                         | < 1450                        | 12.7      | $10^{-3}$             |

| GaAs     | 0.45                        | < 8500                        | 12.8      | $4*10^{-4}$           |

| α-SiC    | 4.2                         | $420 < \mu_e < 950$           | 10        | _                     |

Table 1.1: Physical parameters for Si, GaAs and  $\alpha$ -SiC substrates

Table 1.1 reports their electric and thermal characteristic parameters. Globally, the III-V technologies present higher  $\rho$  and support higher breakdown voltage compared to the silicon ones. They have been widely used for microwave power applications in the past. They are still more suited to power devices such as base stations and military radars. Nevertheless, silicon technologies benefit from a high K and takes advantages to GaAs in terms of technology maturity with large possibilities for post process such as growing oxides, flip chip bumping and bonding technologies. III-V technologies are expensive and are not adapted to large scale market. SiC enjoys inherent advantages over Si and GaAs for high-temperature sustaining and high thermal conductivity. It includes LEDs and high-power switching devices. However, the disadvantages of this substrate are still the high cost and the process difficulty to growth Gallium Nitride(GaN). SiC substrate is available in several forms such as 4H-SiC and 6H-SiC.

When the substrate is chosen, in most cases, an hetero-junction is integrated to improve power and gain capabilities and thus, the efficiency of a transistor to operate at high temperature and at high frequency. The most relevant physical indicators are:

- The band gap energy  $(E_g)$ : a high band gap value lowers the intrinsic carrier density even at high temperature limiting the leakage currents in the transistor. The gap sets the critical electric field  $(E_c)$  which determines the breakdown voltage and thus the maximum power supported by the device.

- The mobility  $(\mu)$ : electrons and holes are driven when an electric field is applied to a semiconductor. They reach the saturation velocity  $(V_{sat})$  under a significant electric field setting the maximal current density.  $V_{sat}$  depends on the interactions in the crystalline structure. Consequently, hetero-junctions are added to reach higher current densities since it confines carriers in a quantum well. Hence, the mobility is greatly increased.

Specific semiconductor technologies are used to answer to PA requirements. Their parameters are reported in Table 1.2 [1]. They impact on Power Amplifier (PA) performances.

| Transistor       | $E_g(eV)$                 | $E_c(V/cm)$  | $\mu_e(cm^2/(V.s))$        | $V_{sat}(cm/s)$ |

|------------------|---------------------------|--------------|----------------------------|-----------------|

| Si               | 1.12                      | $3*10^{5}$   | < 1450                     | $10^{7}$        |

| $Si_{1-x}Ge_x$   | $1.12 - 0.41x + 0.008x^2$ | $< 3 * 10^5$ | 1450 - 4325x               | _               |

| GaAs             | 1.43                      | $4*10^{5}$   | < 8500                     | $10^{7}$        |

| GaN              | 3.43                      | $5*10^{6}$   | < 1000                     | $2*10^{7}$      |

| $Al_xGa_{1-x}As$ | 1.424 + 1.247x            | $5*10^{5}$   | $8000 - 22000x + 10000x^2$ | _               |

| $Al_xGa_{1-x}N$  | 6.026x + 3.39(1-x)        | $1.4 * 10^6$ | 300x + 1000(1-x)           | _               |

Table 1.2: Comparison of the principal materials properties

- Gallium Arsenide (GaAs) based Pseudomorphic High Electron Mobility Transistors (PHEMT) and Hetero-junction Bipolar Transistor (HBT): their use is widespread for cellphones since they offer promising capabilities for high linearity applications. For X band (10GHz) applications, the measured power density in a PA reaches  $3W/mm^2$  and only  $0.5W/mm^2$  for the HBT GaAs and PHEMT GaAs respectively [2]. Their major drawback is the high thermal resistance that limits the maximum dissipated power in a defined area.

- AlGaN/GaN HEMT on SiC: most of the promising results for GaN are achieved. They demonstrate very high power densities achieving (6-9 W/mm<sup>2</sup>) at 10GHz. The relative technology immaturity of GaN with respect to Si and GaAs leaves unanswered issues like longterm reliability. According to the International Technology Roadmap for Semiconductors (ITRS), the GaN HEMTs are said to become the reference technology for power applications at operating frequencies until 40GHz [3].

- Laterally Diffused Metal Oxide Semiconductor (LDMOS) transistor: it is derived from low cost MOSFET device. It benefits of good electrical and thermal characteristic ensuring high power level. This technology is used for cellular systems from 400MHz to 3.5GHz. It supports up to 32V voltage supply. It presents a serious competitor for GaAs PA device. This technology is not yet suited for frequencies beyond 10GHz and not alone for a high integration level since their large area comparing with bipolar transistors.

In parallel, the fast improvement in Complementary Metal Oxide Semiconductor (CMOS) scaling enables designing high speed circuits with small die size to reduce significantly the cost. Indeed, CMOS process is the best process to design digital circuits (processor, memory) which presents more than 80% of the total amount of Integrated Circuits (IC)(Figure 1.1) [4]. This is the major reason that influences semiconductor foundries to fabricate chips only with CMOS

technology. It drives a fast time to market. In addition, digital and analog designers communicate more often avoiding big conflicts when assembling analog and digital part in transceiver.

Figure 1.1: Semiconductor market share

Consequently, several research axes have been initiated to design PAs with CMOS technologies. In [5] a 65nm CMOS PA dedicated to Wireless Local Area Network (WLAN) applications reaches 31.5dBm  $P_{sat}$  with a maximum PAE (PAE<sub>max</sub>) of 25% under 3.3V of supply voltage. Other works presented in [6] [7] and [8] exhibit PAs operating at 17GHz, 24GHz and up to 140GHz respectively. The use of hetero-junction Si/SiGe is a good alternative when the system design does not require high density logic and high-performance analog. It allows having a higher Transition Frequency ( $f_t > 200$ GHz) and a higher gain while remaining on Si (Figure 1.2) [9].

Figure 1.2: Silicon ability to target millimeter Wave applications

The ultimate goal is to find the CMOS technology limits for analog part, disregarding their less performances compared to the common power technologies, previously described.

#### 1.1.2 60GHz band overview

The low power system standards based on Bluetooth IEEE 802.15.1 and Zigbee IEEE 802.15.4 standards have reached the maturity in terms of performances and marketplace. However, they are expected to ensure low throughput communications [10]. Designers adopt some techniques to improve the data rate, as following.

The first mean to increase the data rate is the use of the attractive Multiple-Input Multiple-Output (MIMO) technique. It allows a spatial diversity and multiplexing to increase the channel capacity within a limited frequency band [11]. It uses different antenna patterns for multiple users. It supports higher throughput to ensure classical Wireless Local Area Network (WLAN) applications by transmitting independent data streams with the same bandwidth. In addition, many algorithms are proposed to realize a beam-forming system which performs adaptive spatial signal processing with an array of antennas (Figure 1.3) [12][13]. This technique is limited due to the lower operating frequency that sets the antenna size. In this context, integrating up to two antennas in the transceiver is reasonable. The evolutionary IEEE 802.11.n standard improves the previous IEEE 802.11.a/b/g/n standards known as WiFi. The data rate is increased from 20MBps to 100MBps achieving an operating range of 100 meters.

Figure 1.3: System combining MIMO and beam-forming techniques

The second mean to obtain higher data rate is to increase the channel bandwidth. This is not possible due to the standard regulations and cluttering in the Industrial, Scientific and Medical (ISM) band in 2.4GHz or 5GHz band. The available bandwidth are 70MHz and 500MHz for the 2.4GHz and the 5GHz bands respectively. This is the major limiting factor for this standard.

The other competitive standard to narrow band systems is the Ultra Wide Band (UWB). It was most often used before in confidential research in military radars development. The Federal Commission Communication (FCC) has authorized the unlicensed [3.1-10.6]GHz band to answer to the large demand for short range rapid communication standard in 2002 [14]. A fundamental difference between UWB and the traditional systems exists. Instead of transmitting a modulated Sine Wave (SW) signal, a time pulse is generated. Thanks to time-frequency domain duality, the pulse width offers a large bandwidth. The pulse encodes data with a conventional modulation like On-Off Keying (OOK), Pulse Position Modulation (PPM), Phase Shift Keying (PSK), etc. Those modulation schemes are based on Direct Sequence-UWB (DS-UWB) coding approach. This approach is attractive for its easy implementation that can be designed with low cost process. The second approach is the Pulsed-OFDM-UWB. It improves data rate communication in Non-Line-Of-Sight (NLOS) channel conditions. The [3.1-10.6]GHz band is divided into 14 sub-bands of 528MHz wide. Each sub-band contains 128 sub-carriers [15]. With this modulation scheme, data rate achieved 1.92GBps. This approach leads to expensive and complex systems. Additionally, a drastic power limitation (less than -41.3dBm/MHz) is imposed by the FCC to avoid interference issues with standards occupying the same frequency band like WiFi standard.

Figure 1.4 shows a comparison of wireless competitive standards considering the data rate, the range and the Equivalent Isotropically Radiated Power (EIRP).

Figure 1.4: Comparison of wireless standards-setting

Somehow or other, a gigabit link is hardly feasible, even with complex modulations or with MIMO techniques. It is due to the presence of various standards operating at frequencies below 10GHz. Indeed, the ISM band hosts a multitude of standards dedicated to data and multimedia transmission. The budget link of each standard is not efficient to ensure gigabit data transmission. This is why new researches are investigating for available large bands even if they are at very high frequencies. Consequently, the unlicensed 7GHz band around 60GHz is targeted to fulfill the demand of high data rate short range communications. The emerging 60GHz standard is a very promising way to reach gigabit links.

Working at 60GHz requires new considerations especially related to technology scaling and high propagation losses in channels. The next section introduces the motivations and the context of this frequency range.

#### Available broadband

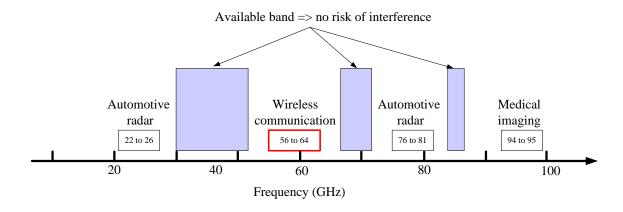

As discussed before, the IEEE 802.11a/b/g/n and UWB standards do not answer to gigabit data rate specifications. Those standards can be improved only by adopting complex modulations schemes requesting high cost which prevents from targeting a large scale market. A solution consists in operating in an empty wide-band without close neighbor standards to avoid coexistence issues and power constraints. The 7GHz band around 60GHz is a matter of concern and free of use and well suited to high data rate for indoor Wireless Personal Area Network (WPAN) applications. The FCC sets aside this band in 2001 [16]. The neighbor millimeter Wave (mmW) applications occupy the 24GHz and 77GHz bands, dedicated to radar applications (Figure 1.5). Consequently, there is no interference issues between these mmW applications. Moreover, they operate in different environments namely the indoor environment for WPAN communications and the car environment for radar applications.

Figure 1.5: Millimeter-wave applications

#### Scaling components

The requirements for microelectronics industry is striving to reduce die size. The main motivation to operate towards high frequency is the technology down-scaling. Reaching higher frequency is one of the best way to integrate all components at least in a small die area and why not, in a single chip. Thus, System in Package (SiP) and System on Chip (SoC) integrations are a promising trend. Indeed, lumped passive devices are more compact. The size of passive devices as Transmission lines (T-lines) and antennas are set in function of the wavelength. At 60GHz, the wavelength is only 2.5mm in the Silicon Dioxide ( $SiO_2$ ). Hence, the integration of network containing 4 or 8 antennas becomes realistic to improve the antenna's directivity. Likewise, MIMO systems are more suitable at high frequency since two adjacent antennas are separated by a low distance. Finally, the die area gain exists due to the transistor scaling.

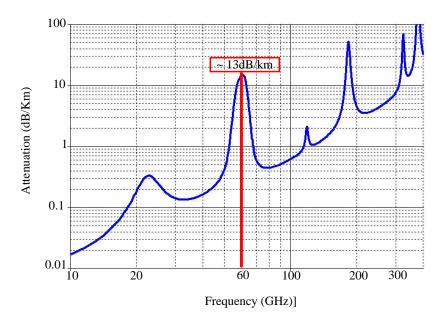

#### Oxygen absorption

A particular interest of the band around 60GHz is due to a natural phenomenon. The oxygen molecule absorbs the electromagnetic energy at this specific frequencies. This absorption is the cause of a 13dB/km attenuation (Figure 1.6) [17]. That is why this band is targeted also for satellite-to-satellite communication data link. In WPAN context, this attenuation enables a high secure communication for short range distance. The 60GHz data link operates within a small geographic area without any interference with other standards or with other users working at the same frequency.

Figure 1.6: Oxygen absorption at 60GHz

#### 60GHz channel

Dimensions of wireless link are determined by channel properties. According to the Friis propagation loss formula given by Eq. 1.1, the free-space losses are proportional to the frequency square. For instance, an additional 20dB loss is expected for a system operating at 60GHz compared to another one operating at 6GHz. These losses can be compensated by the design of a high gain and directive miniaturized antenna array to limit the number of multi-paths propagation.

$$P_r = \frac{P_t \cdot D_r \cdot D_t \cdot \lambda^2}{4 \cdot \pi \cdot R^2} \tag{1.1}$$

Where,

- $P_r$  and  $P_t$  present the received and the transmitted power.

- $D_r$ ,  $D_t$  present the directivity of the received and the transmitted antennas.

- R presents the distance between the receiver and the transmitter.

- $\lambda$  presents the wavelength.

In addition, the transitivity of the electromagnetic wave decreases at higher frequency. Consequently, walls and human body are the most common obstacle and present sources of reflection in indoor environments. Hence, the link budget study depends on the communication scenario: LOS or NLOS. The high free-space losses and low wave penetration at 60GHz confine the communication data link in one room. Table. 1.3 lists the amount of insertion losses caused by obstacles in indoor environment. A concrete wall attenuates the signal more than 40dB.

Table 1.3: 60GHz channel insertion loss

| Material type | Insertion loss (dB) |

|---------------|---------------------|

| Human body    | 20                  |

| Concrete wall | > 40                |

| Plywood       | 6                   |

| Dry wall      | 11                  |

| Full wall     | 26                  |

#### 1.1.2.1 Standardization of the 60GHz WPAN standard

# **Brief history**

The standardization of the 60GHz WPAN standard is the result of several works demonstrated all over the world. Academic and industrial researchers have initiated their investigations in the 60GHz band 20 years ago. The goal was to reach the maximum data rate for asynchronous transfer mode networks [18]. The most important actors who had driven ambitious projects to develop this standard are presented as follows:

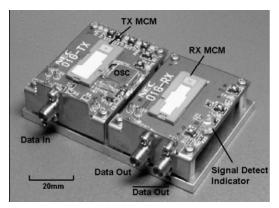

In Japan, the government was probably the first to investigate in 1984 to use the mmW frequencies for WLAN applications. The main researches began in the communication research laboratory in 1992 [19]. The first 60GHz demonstrator has hardly ensured a 51MBps data rate [20]. This work has participated to regulate the 60GHz WLAN in 2001 [21]. A licensed [54-59]GHz band and an unlicensed [59-66]GHz band are authorized for high-speed data communication. NEC company was one of the most active partner publishing in 2002 a 1.25GBps 60GHz transceiver device using a Amplitude Shift Keying (ASK) modulation [22] with a  $0.25\mu m$  AlGaAs/InGaAs hetero-junction FET technology (Figure 1.7).

(b) Photo of encapsulated transceiver module

Figure 1.7: NEC's AlGaAs/InGaAs transceiver module

In USA, the FCC assigned [57-64]GHz frequency band as unlicensed band for short-range high-speed communication in 2001 [23]. In 2005, an alternative group 802.15.TG3C was formed to develop a mmW based alternative standard to the 802.15.3-2003 standard to WPAN applications. Berkeley Wireless Research Center (BWRC), University of California (UCLA) and IBM were the relevant actors that investigate in this domain. IBM has presented a 60GHz chip set in 2006 [24] [25]. The TX/RX are packaged together in a chip on board assembly as depicted

Figure 1.8: IBM's SiGe single-chip 60GHz transceiver

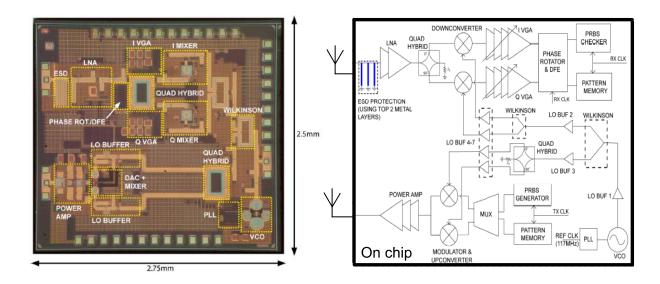

in Figure 1.8. The process adopted was  $0.13\mu m$  SiGe technology. The transceiver achieved a 630MBps data rate over 10 meters. BWRC has brought interest to this application and designed all the transceiver. The challenge consisted in the chosen technology. Indeed, their first works were based on  $0.13\mu m$  CMOS technology [26]. Recently, a 90nm CMOS transceiver was demonstrated [27].

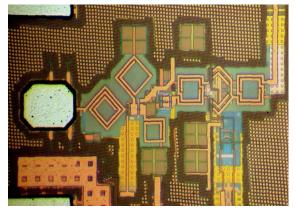

In Europe, The MEDIAN European project (1994-1997) investigated in WLAN standard providing 150MBps data rate with a Orthogonal Frequency Division Multiplexing (OFDM) modulation. Several projects like BROADWAY, COMMINDOR, MAGNET, WINNER developed physical layer. IMEC is developing single chip 60GHz radios using advanced 45nm CMOS technology. In the International Solid-State Circuits Conference (ISSCC 2009) [28] [29], IMEC reports also a world-first mmW PA and a digitally controlled [57-66]GHz receiver with multiple antenna front-end as shown in (Figure 1.9). STMicroelectronics also brought interest in developing this application.

(b) Photo of RF front-end IC with antenna interface

Figure 1.9: IMEC's 45nm 60GHz front-end

## 1.1.2.2 Frequency plan

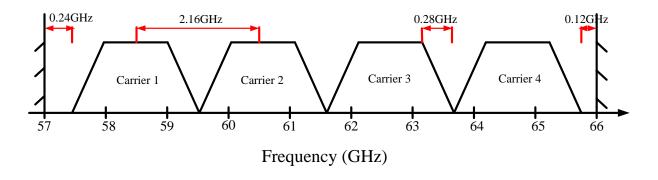

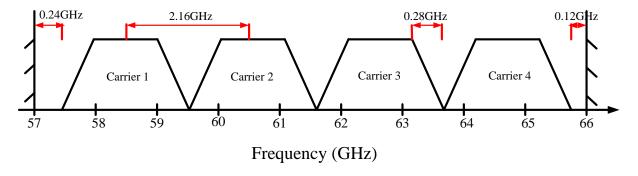

To set the 60GHz standard, Institution of Electrical and Electronics Engineers (IEEE) and European Computer Manufacturers Association (ECMA) have presented the final draft in 2008 [30] and 2009 [31] respectively. A summary of ECMA frequency plan is presented in Figure 1.10. The physical layer uses the unlicensed 7GHz frequency band around 60GHz. The channel width is set to 2.16GHz with a symbol rate of 1.72GBps for each channel. The mask depends on the targeted device type in the network.

Figure 1.10: WPAN spectrum overview

# 1.1.2.3 Architecture network and 60GHz features

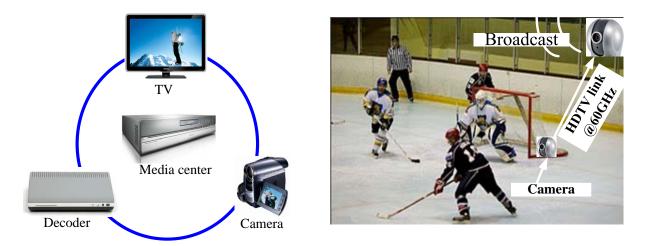

Main applications of WPAN standard are the HD video streaming and wireless docking station applications (Figure 1.11). The links can be set by point-to-point and by point-to-multi-points communication type. Otherwise, three types of devices can operate independently, cohabit and inter operate in the same area. Figure 1.12 illustrates the possible links between the 3 types of

Figure 1.11: 60GHz WLAN/WPAN applications

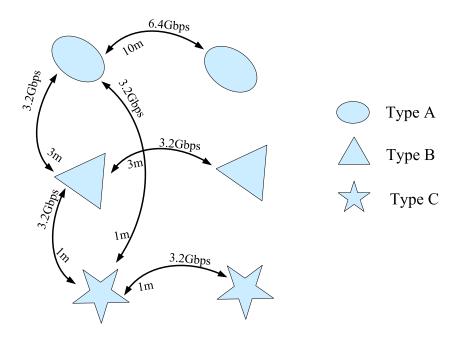

devices. The data rate and the range of every link are also presented. It is an heterogeneous network composed by:

- Device type A: it ensures principally the uncompressed or lightly compressed video streaming over a range of 10 meters. Both LOS and NLOS scenarii are envisaged. This type of device has the highest performances. It operates following two modes:

- with a Single Carrier Block Transmission (SCBT) mode employing BPSK, QPSK and 16QAM modulation schemes. The data link must support a data rate from 0.794GBps to 6.35GBps.

- with an OFDM mode, data are splitted into several sub-carriers with QPSK and 16QAM modulation schemes. The data rate varies according to the adopted scheme from 1GBps to 1.588GBps.

- Device type B: it aims at transferring data, pictures and video over a shorter range from 1 to 3 meters. The communication is a point-to-point-link (LOS). It enables a lower cost implementation and a lower power consumption than type A device. Device type B uses a simplified SCBT with a 3.175GBps data rate.

- Device type C: it offers only a transmission data for LOS link. The distance between TX/RX does not exceed 1 meter without Quality of Service (QoS) guarantee. This device is considered as the less constrained and ruled device. This type uses OOK mode with a data rate up to 1.6GBps.

Figure 1.12: Heterogenous devices in the 60GHz WPAN

# 1.1.3 60GHz transceivers

Systems are built as a function of the requirements of the targeted standards. Mainly, the adopted technology node sets the cost and the performances of the transceiver. FoM must be studied before each realization (linearity of the PA, Signal to Noise Ratio (SNR), Noise Figure (NF) of the Low Noise Amplifier (LNA), selectivity of different filters or reconfigurability ...).

The classification of transceivers differs by their mean of down-conversion. Operations in the receiver are the dual of the ones with the transmitter. Three families of transceivers are reported in a realization example dedicated to the 60GHz WPAN standard.

- Super-Heterodyne Transceiver (SHT).

- Direct Conversion Transceiver (DCT).

- Software Defined Radio Transceiver (SDRT).

# 1.1.3.1 Super-Heterodyne Transceiver (SHT)

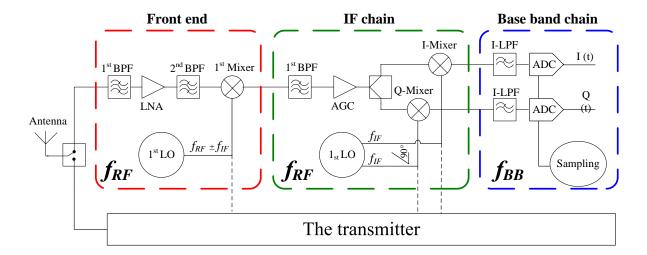

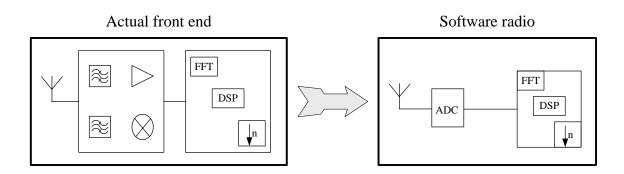

The SHT is the most common one. It is identified by the use of several down-converters to operate at Intermediate Frequencies (IF) before translating signal to base-band. High performances are achieved at the expense of highly selective required filters. Figure 1.13 depicts the building blocks of a SHT. The two filters located at the front end chain reject the Image Radio Frequency (IRF) and the one located at the IF chain selects the IF. The main issue consists in the necessity of several encumber components. Hence, a high integration level on chip is difficult with this traditional topology. In spite of that, this approach is useful for high-tier communications.

Figure 1.13: Building blocks of a SHT

For instance, [32] presents a 60GHz SHT. The TX and the RX are designed separately in 90nm CMOS technology (Figure 1.14). The digital part is integrated in the same chip. It includes an Analog to Digital Converter (ADC), a DC-offset canceler and a Finite Impulse Response (FIR) to support the heavy constraints imposed by the OFDM modulation schemes. It achieves a data rate of a 7GBps with a QPSK and a 15GBps with a 16QAM modulation scheme. The antenna is co-integrated in a low cost FR4 substrate. To avoid aliasing matters, IF must be as high as possible, from 7GHz to 13GHz. A push-push Voltage Controlled Oscillator (VCO) and a double-balanced quadrature Gilbert-cell mixer are implemented to down-convert the modulated signal to IF. The PA provides a gain of 17dB with a  $P_{out}$  of 5.1dBm.

Figure 1.14: 60GHz CMOS single chip radio block diagram based on SHT

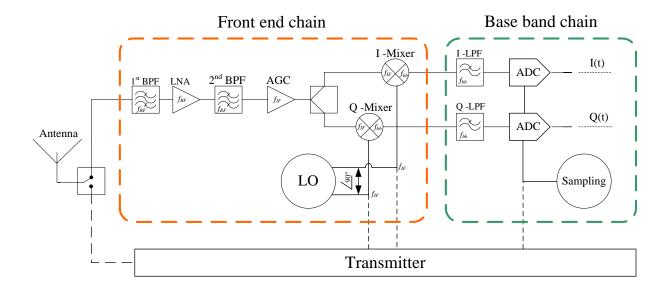

# 1.1.3.2 Direct Conversion Transceiver (DCT)

Figure 1.15 depicts the building block of a DCT. The front-end is simplified in this configuration. Only one Local Oscillator (LO) is used to down-convert the modulated signal to base band. In this frequency range, 1/f noise and DC-offset are present. The mixer must have a large dynamic range. The low pass filter located before the ADC must be designed to select the useful channel. Contrary to SHT, I/Q splitting is mandatory to not have aliasing issues. This kind of transceiver is suited for mid-tier communications.

Figure 1.15: Building blocks of a DCT

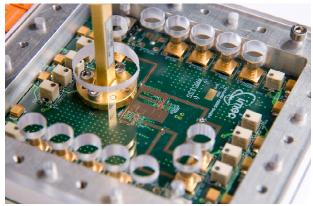

For instance, [27] presents the design of a 90nm CMOS low power 60GHz DCT with its base band circuitry (Figure 1.16). The wireless link achieves a 10GBps data rate with a QPSK modulation scheme. A fully differential combined Digital to Analog Converter (DAC)-mixer structure is used for the modulator. The difficulty in this transceiver is to ensure good matching between the input of the PA and the low output impedance of the modulator. In the receiver, the LNA amplifies the received signal before being down-converted to base band. A digitally-programmable analog phase rotator is used to synchronize in phase the TX and the RX. The

Figure 1.16: Block diagram and die micrograph of a 60GHz DCT

Phase Locked Loop (PLL) is designed at 30GHz with push-push topology to operate at 60GHz without any frequency divider. One power splitter in phase and another one in quadrature share the VCO between the TX and the RX to generate I and Q paths with a difference phase of 90deg.

A mix of the SHT and the DCT is the Low IF transceiver. It is the less common topology. It uses an IF equals to the spacing channel to release the implementation constraints. However, the transceiver requires a complex poly-phase filter. This approach is well suited for low cost communications [33].

## 1.1.3.3 Software Defined Radio Transceiver (SDRT)

SDRT aims at being a flexible transceiver to integrate various standards on a single chip. The concept of Software Defined Radio (SDR) paves the way to challenge this idea. Joseph Mitola exposed for the very first time the concept of Software Radio (SR) in 1995 [34], replacing the major part of dedicated analog front-end in a transceiver by a fully digital implementation monitored by software (Figure 1.17). The digital part is getting as close as possible to the antenna. Until now, this approach must support a large dynamic range of a wide diversity of standards and leads to a dramatic high power consumption. Those issues prevent from designing a full Software Radio system (SR) and constraint researchers to explore new RF architecture to fulfill SDR specifications.

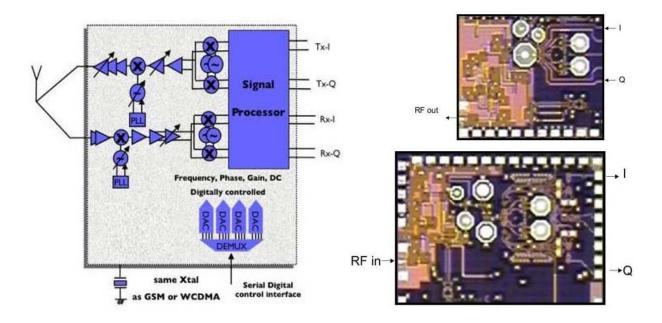

Figure 1.17: The SDRT principle

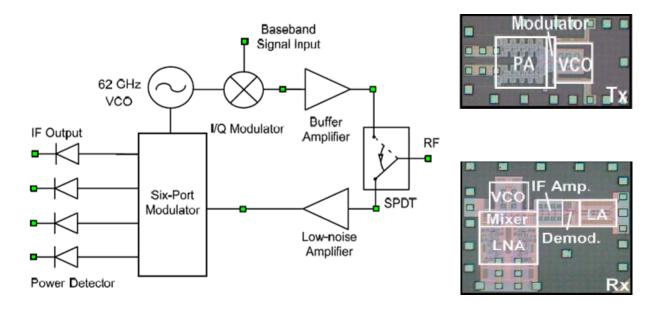

For instance, Figure 1.18 presents a 60GHz SDRT. It is fabricated with 130nm CMOS technology from TSMC [35]. The innovation in this transceiver is that a six-port receiver replaces the analog part. Implementing the six-ports in the receiver requires a low LO power compared to the required one for a typical mixer. Each amplifier used in the receiver and in the transmitter provides a high gain of 20dB to improve the link budget. The transceiver has been tested with a BPSK modulation scheme achieving a data rate of 4GBps.

Figure 1.18: Chip micrograph of the 60GHz six-port transceiver based on SDRT

Table. 1.4 shows the FoM of the main elementary circuits of the presented transceiver examples. The SHT exhibits good link budget achieving a high data rate. However, it suffers from high power consumption and a large die area due to the separated design of the TX/RX parts.

DCT consumes the same power as the SHT. It is justified by the high output power generated by the PA. Despite of that, it does not achieve a better data rate than the SHT.

SDRT presents an innovative architecture. It benefits from a small area because of the use of the six-port receiver. But its power performances are lower than the previous transmitters ones even with the use of a simple BPSK modulation scheme.

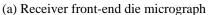

In every cases, the antenna is not implemented in the same chip. It uses other low loss substrate such as FR4. Indeed, antenna on silicon suffers from very loss efficiency (lower than 15%). In this context, most of transceivers adopts SiP packaging with Printed Circuit Board-Monolithic Microwave Integrated Circuit (PCB-MMIC) chip interface [36] [37] or with Low Temperature Co-fired Ceramic-MMIC (LTCC-MMIC) chip interface [38] [39].

Table 1.4: Measured performances summary of SHT, DCT and SDRT  $\,$

| Topology                             | SHT         | DCT        | SDRT     |

|--------------------------------------|-------------|------------|----------|

| Frequency(GHz)                       | 57 to 65    | 59.6 to 64 | 60 to 64 |

| ${f Technology(nm)}$                 | 90          | 90         | 130      |

| Amplification                        |             |            |          |

| PA                                   |             |            |          |

| Psat (dBm)                           | 8.4         | 10.6       | -        |

| $P1dB \ (dBm)$                       | 5.1         | 9          | -2       |

| Gain (dB)                            | 17          | 14         | 20       |

| LNA                                  |             |            |          |

| Gain (dB)                            | 32          | -          | 20       |

| Sensitivity                          |             |            |          |

| Noise figure (dB)                    | 8           | _          | 8        |

| Phase Noise (1MHz)(dBc/Hz)           | -95         | -95        | -92      |

| Power consumption (mW)               |             |            |          |

| PA PA                                | 54          | -          | 36.9     |

| LNA/Mixer/IF Amplifier               | 70          | -          | 31       |

| VCO+PLL                              | 30+30       | 12+18      | 30       |

| $IQ\ Modulator/Demodulator/QVCO/PLL$ | 36+42+40    | -          |          |

| Base band                            | -           | 12         | -        |

| $Total\ power\ consumption\ (mW)$    | 362         | 369        | -        |

| Link Budget                          |             |            |          |

| Modulation schemes                   | QPSK        | QPSK       | BPSK     |

| Data rate (Gbps)                     | 7           | 4          | 4        |

| Die area (TX+RX) (mm²)               | 2.62 + 3.82 | 6.87       | 2.47     |

# 1.2 60GHz WPAN PA design issues

#### 1.2.1 PA fundamentals

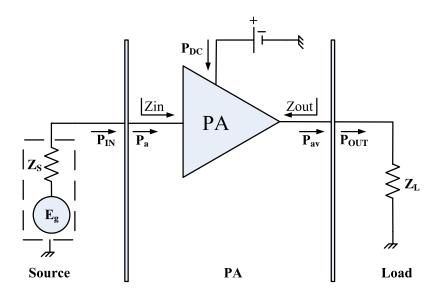

The PA design is said to be complex because of the simultaneous consideration of criteria that characterize the PA performances. PA FoM is given by saturated power  $(P_{sat})$ , linearity, efficiency, frequency response, gain, stability and die area. All those parameters govern the design during every steps. Indeed, the PA is one of the most critical element in a RF front-end design. In one hand, it is the most current hungry component in the chip. In the other hand, it can be considered as a non-linearity source. Typical parameters used in this work are given by Figure 1.19:

- $P_{in}$  and  $P_{out}$  are the input and the output power.

- $Z_{in}$  and  $Z_{out}$  are the input and the output impedances of the PA.

- $Z_s$  is the source impedance of the generator (typically  $50\Omega$ ).

- $Z_L$  is the load impedance of the PA.

Figure 1.19: Characteristic parameters of a PA

Gain: Several reflections are present due to mismatching problems while the signal passes through the PA from the generator to the load. This phenomenon has power gain penalties and leads to different gain definitions: the operating gain  $(G_{op})$ , the available gain  $(G_{av})$  and the transducer gain  $(G_{tr})$ . Their respective expressions are given in Eq. 1.2, Eq. 1.3 and Eq. 1.4.

$$G_{op} = P_{out}/P_a \tag{1.2}$$

$$G_{av} = P_{av}/P_{in} \tag{1.3}$$

$$G_{tr} = P_{out}/P_{in} \tag{1.4}$$

Where  $P_a$  is the accepted input power and  $P_{av}$  is the available output power.

The transducer gain is the most realistic one since it is the one measured considering every mismatching effects. Others gain definitions based on S-parameters are used in small signal domain to analyze gain and stability issues. Those aspects will be detailed in the transistor characterization.

Efficiency: The power consumption of the PA must be optimized as much as possible to guarantee a long battery life. This is why the efficiency is one of the most important FoM in a PA design. The efficiency considers directly the DC power consumption  $(P_{DC})$  and the portion of the alternative signal when the current is flowing through the transistor. Two definitions are set: the drain efficiency  $(\eta_d)$  (Eq. 1.5) and the Power Added Efficiency (PAE) (Eq. 1.6).

$$\eta_d = P_{out}/P_{DC} \tag{1.5}$$

$$PAE = (P_{out} - P_{in})/P_{DC} \tag{1.6}$$

$\eta_d$  is frequently used for high-gain GaAs and Bi-CMOS PAs and is also used for a single PA stage. In the context of 60GHz CMOS PA, the gain is expected to be low and  $P_{in}$  can not be neglected. Thus, the PAE will be the FoM of efficiency since it considers all input powers and the gain.

The principles of transistor matching, stability and modeling for PAs applications will be detailed in chapter 3. The next part highlights the issues in PA design related to the 60GHz WPAN standard with a 65nm CMOS technology.

# 1.2.2 Modulation issues

The PA characterization differs from and depends on the nature of the signal applied to the input of the PA. A complete PA design takes into account the impact of the modulated signal. Two cases are distinguished:

- Constant envelope signal.

- Non-constant envelope signal.

## Constant envelope signal

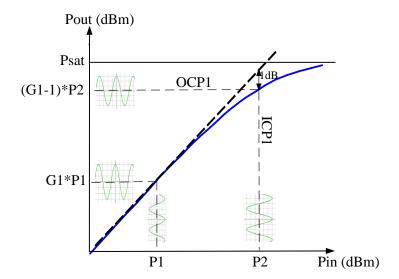

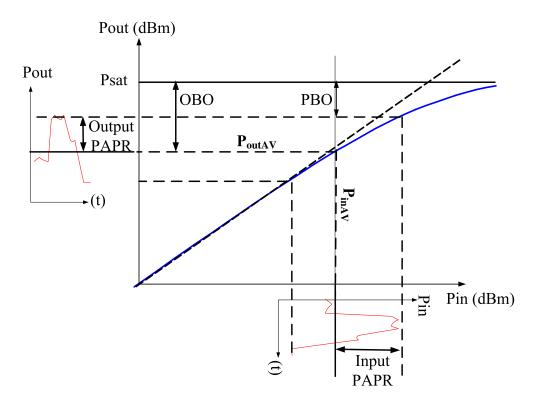

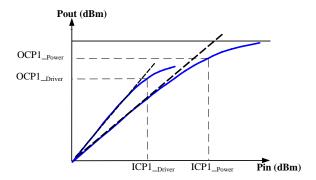

The first step in the PA design consists in applying a source swept in power.  $P_{out}$  versus  $P_{in}$  is the most frequent power characteristic. Two operating modes are distinguished (Figure 1.20):

Figure 1.20:  $P_{out}$  versus  $P_{in}$  with a SW signal

- A linear regime is defined when the output signal is intended to be the same than the input signal and amplified to the desired level.

- A non linear regime is defined when the gain decreases. The Output 1dB Compression Point  $(OCP_1)$  is defined when the gain falls by 1dB. The PA operates in a non linear regime from this point.

Only magnitude and phase distortions due to multiple harmonics are analyzed with a sine wave analysis. That characterization does not bring enough information concerning linearity to be as accurate as required for broadband signal.

# Non-constant envelope signal

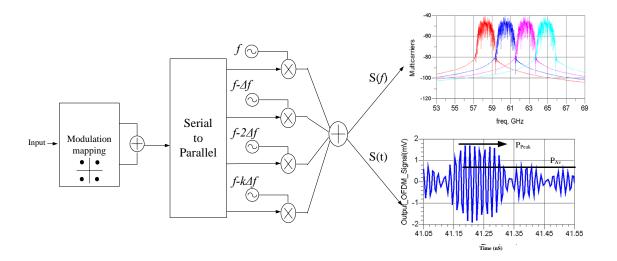

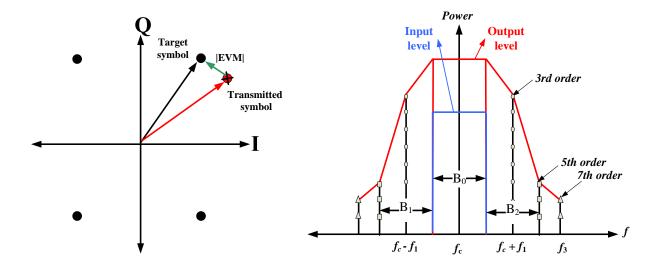

Advanced standards use non constant envelope signal by choosing a multi-carrier approach to improve data rate. In this context the instantaneous  $P_{in}$  applied to the PA varies in time. Two parameters are defined from the modulated signal to set the linearity constraints: Power Average To Power Ratio (PAPR) and Output Back-Off (OBO).

#### PAPR:

Contrary to a SW signal, the OFDM signal is a result of the coherent sum of several carriers varying in time (Eq. 1.7). Hence, the OFDM signal has a non constant envelope. In order to quantify the envelope fluctuations, the PAPR is defined as the ratio between the peak power  $(P_{Peak})$  and the average power  $(P_{Av})$  of the signal during an interval of time (Eq. 1.8) (Figure 1.21). It differs from a standard to an other.

$$S(t) = A \sum_{k=-\infty}^{\infty} \sum_{i=0}^{N-1} x_{i,k} \cdot w(t - kT) \cdot e^{j2i\pi\Delta f(t - kT)}$$

(1.7)

Where:

- w(t kT) is the window function,

- $\bullet$  N is the number of channels,

- x is the symbol of sub-carrier i at time k,

- $\Delta f$  is the distance separating two carriers,

- A is the magnitude of a digit.

Table. 2.1 shows the most common signals used for wireless communication with their respective PAPR. OFDM signals have the highest PAPR.

Table 1.5: PAPR for different modulated signals

| Signal | PAPR (dB) |

|--------|-----------|

| GSM    | 0         |

| CDMA   | 5 - 9     |

| WCDMA  | 3.5 - 6   |

| OFDM   | 10 - 17   |

Figure 1.21: OFDM signal generation

The OFDM signal is described statistically by a Complementary Cumulative Distribution Function (CCDF) that determines the probability that the magnitude crosses a certain threshold [40]. Typically, the peak power is reached infrequently (Figure 1.21). The probability that the magnitude crosses 90% of the peak of the signal is around 5%. In spite of the few presence of high power level in time, the PA must be at least linear when the highest level of power is applied to keep the PA linear.

$$PAPR = \frac{P_{max}}{P_{av}} = \frac{max_{[0,T]}|S(t)|^2}{\frac{1}{T}\int_0^T \cdot |S(t)|^2 dt}$$

(1.8)

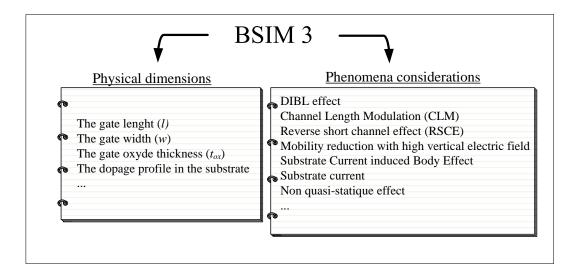

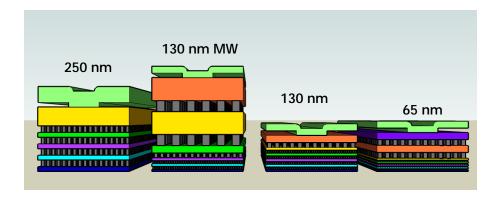

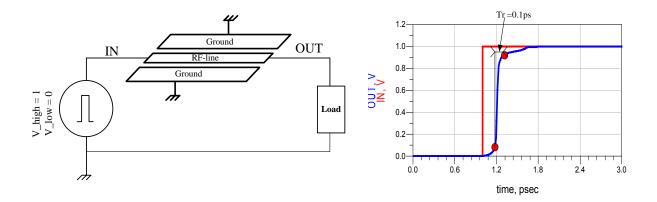

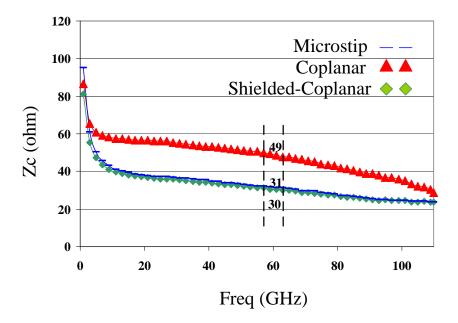

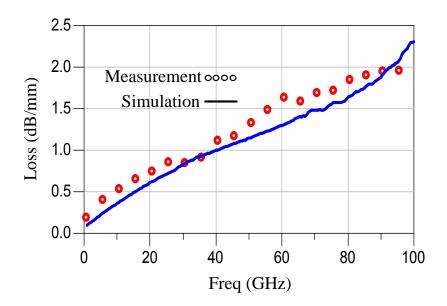

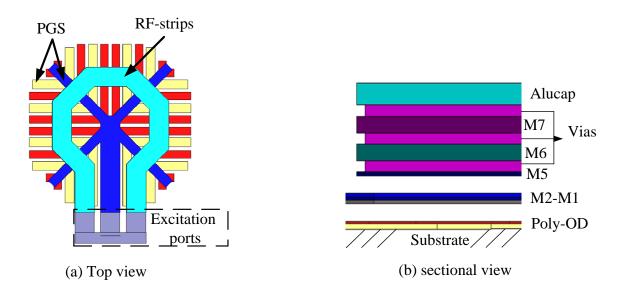

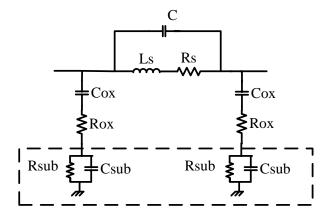

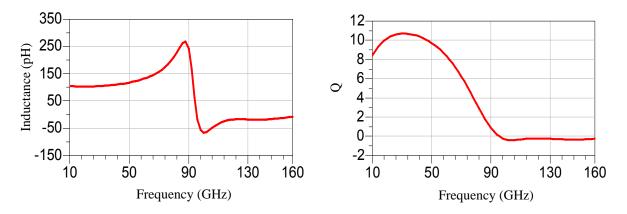

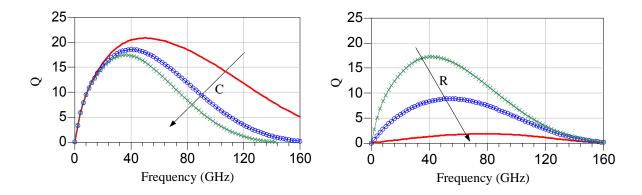

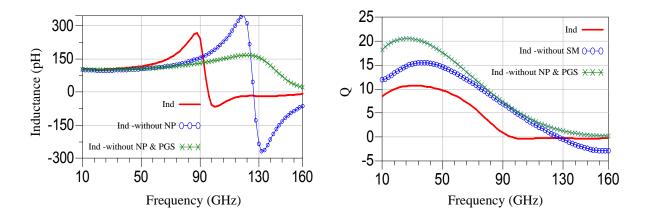

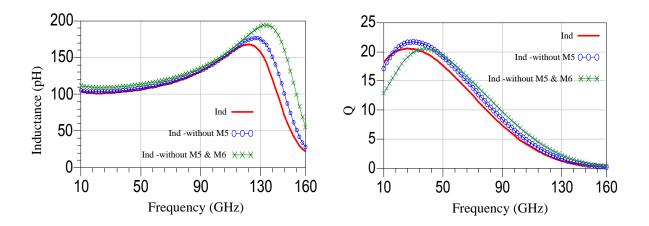

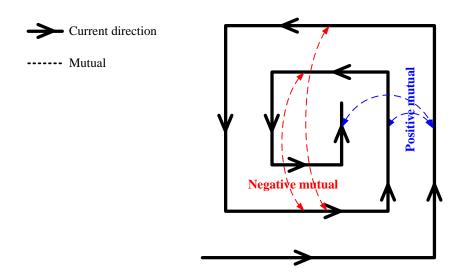

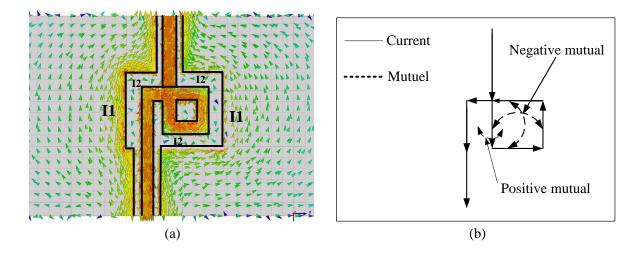

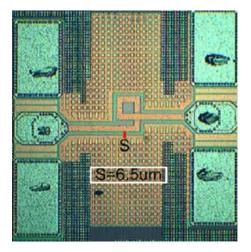

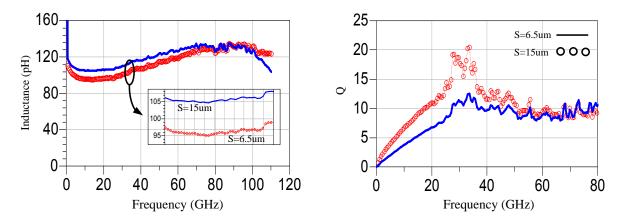

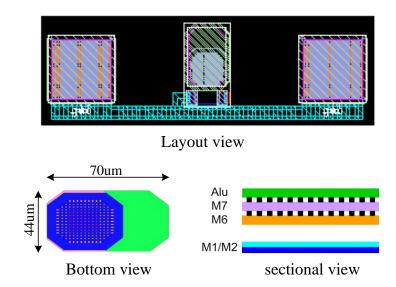

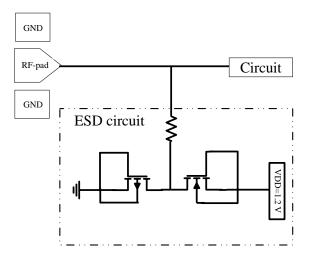

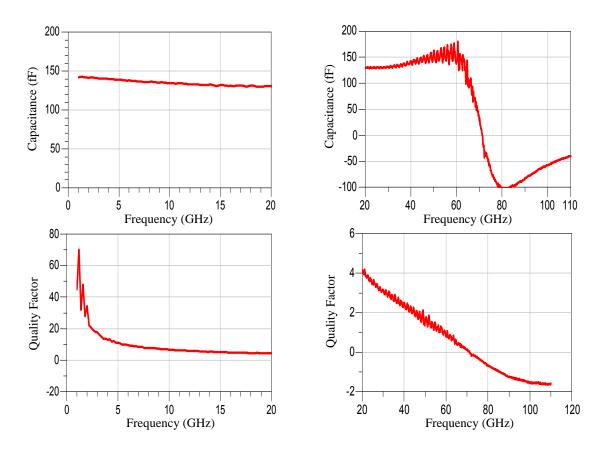

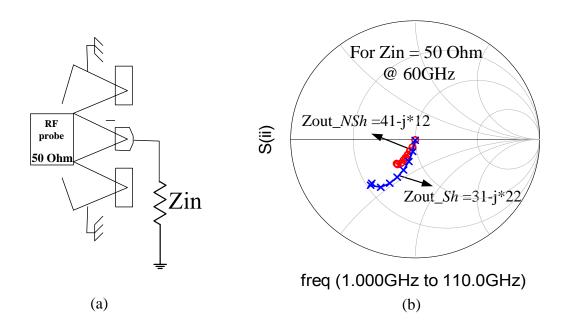

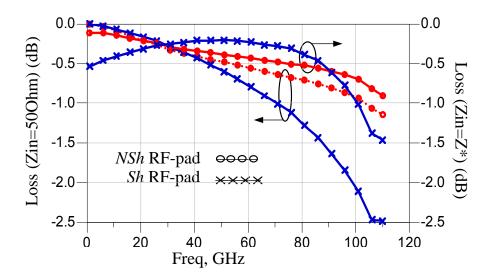

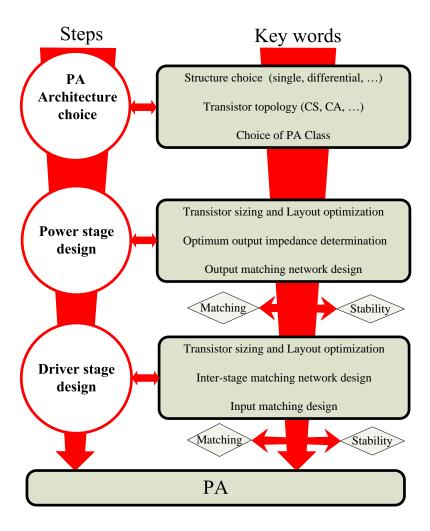

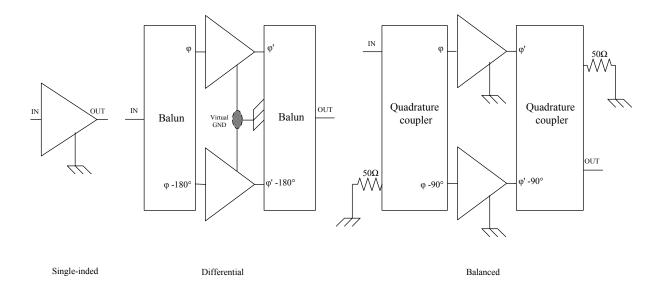

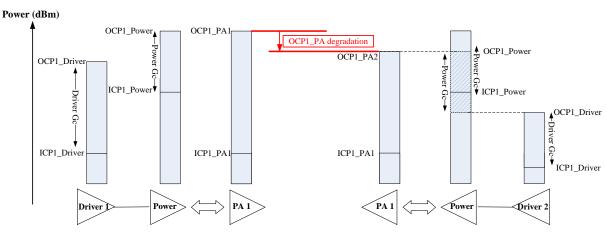

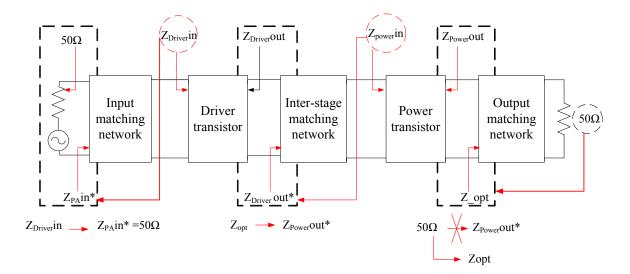

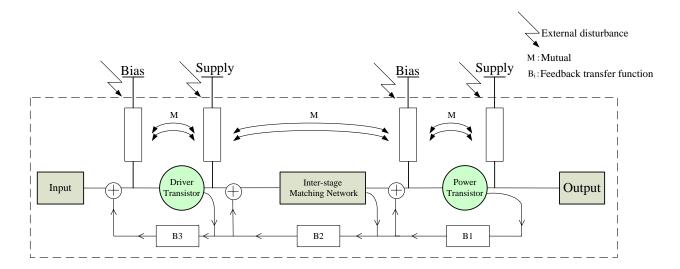

#### OBO: