# Conception des modulateurs sigma-delta d'ordre élévé pour des convertisseurs analogique-numérique en parallèle

Mohammad Javidan

#### ▶ To cite this version:

Mohammad Javidan. Conception des modulateurs sigma-delta d'ordre élévé pour des convertisseurs analogique-numérique en parallèle. Micro and nanotechnologies/Microelectronics. Université Paris Sud - Paris XI, 2009. English. NNT: . tel-00469483

## HAL Id: tel-00469483 https://theses.hal.science/tel-00469483

Submitted on 1 Apr 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

**ORSAY** N° d'ordre :

Université de Paris XI Centre d'Orsay École Supérieure d'Électricité SUPÉLEC

# **THÈSE**

présentée pour obtenir le grade de

#### DOCTEUR EN SCIENCES DE L'UNIVERSITÉ DE PARIX XI ORSAY

Par

### Mohammad JAVIDAN

#### CONCEPTION DES MODULATEURS SIGMA-DELTA D'ORDRE ÉLEVÉ POUR DES CONVERTISSEURS ANALOGIQUE-NUMÉRIQUE EN PARALLELE

Thèse soutenue le 18 décembre 2009

## Commission d'examen :

MM.

Souhil MEGHERBI Président

Dominique DALLET Rapporteur

Maurits ORTMANNS Rapporteur

Jean GODIN Examinateur

Raymond QUERE Examinateur

Philippe BENABES Examinateur

Matthieu CHATRAS Invité

Thèse préparée au Service des Mesures École Supérieure d'Électricité

# Design of high-order sigma-delta modulators for parallel analog-to-digital converters

#### Mohammad JAVIDAN

Department of Signals processing and Electronic Systems (SSE)

University of Paris XI, Centre d'Orsay

A thesis submitted for the degree of  $PhilosophiæDoctor\ (PhD)$

2009 December

1. President: Souhil MEGHERBI, professor (Dr.-Ing), Head of IUT Cachan-Paris XI university, Cachan, France. Email: souhil.meghrebi@u-psud.fr

2. Supervisor: Philippe Benabes, professor (Dr.-Ing), SSE department-Supelec,

GIF SUR YVETTE, FRANCE. Email: philippe.benabes@supelec.fr

3. Reviewer: Maurits Ortmanns, professor (Dr.-Ing), Institute Fur Mikroelektronik-

Ulm university, Ulm, Germany. Email: maurits.ortmanns@uni-ulm.de

4. Reviewer: Dominique Dallet, professor (Dr.-Ing), IMS laboratory-Bordeaux

university, BORDEAUX, FRANCE. Email: dominique.dallet@ims-bordeaux.fr

5. Examiner: Jean Godin, Head of GCBH (Dr.-Ing), Alcatel-Thales III-V Labora-

tory, ROUTE DE NOZAY, FRANCE. Email: jean.godin@3-5lab.fr

6. Examiner: Raymond Quere, professor (Dr.-Ing), C2S2 Laboratory-XLIM,

LIMOGES, FRANCE. Email: raymond.quere@xlim.fr

7. Invited: Matthieu Chatras, professor, C2S2 Laboratory-XLIM, Limoges,

FRANCE. Email: matthieu.chatras@xlim.fr

Day of the defense: 18 December 2009

ii

#### Abstract

The present work is about design of convenient high-order continuous-time band-pass sigma-delta modulators for parallel A/D converters. First of all, an overview on the basic concepts of analog to digital conversion is presented.

The extended frequency band decomposition technique is chosen as a good solution for parallelism. The requirements of this technique are studied, including high resolution performance of the used converters at high frequencies.

A  $6^{th}$ -order continuous-time band-pass single-stage sigma-delta modulator with a quantizer number of bits equal to 3 and an oversampling ratio equal to 64 is theoretically able to meet the objectives. However, a proper methodology of design is required in order to make a reliable design in practice since continuous-time modulators are sensitive to analog imperfections. This methodology must be able to overcome the practical issues such as the dependence of the modulator performance to the modulator central frequency as well as the issue of a robust stability margin.

For this aim, a new structure based on Weighted feedforward techniques providing an adequate control on the position of the poles of the noise-transfer-function by simple means is proposed. Moreover, the proposed structure provides a filtering-signal-transfer-function close to the modulator central frequency in order to increase the input dynamic range of the modulator.

An optimization method on the modifiable parameters of the proposed topology is developed in order to recover the performance of the modulator accounting analog imperfections. The system-level model of analog components extracted from a transistor-level simulation must be used to guarantee the modulator performance in practice.

The methodology must be associated with a proper resonator capable of providing a large quality-factor at the required band of frequency. Of all the studied sorts of the resonators, Lamb-wave-resonators are chosen. Also solutions are considered in order to overcome the issues of this kind of resonators including the anti-resonance and low impedance connections.

Finally, a second-order sigma-delta modulator is chosen to benchmark the proposed solutions. AMS Bi-CMOS 0.35  $\mu m$  technology kit is used and the modulator is designed and simulated in layout-level. The results approve the efficiency of the proposed solutions.

#### Acknowledgements

I would like to take this opportunity to acknowledge all those who gave me the possibility to complete this thesis and who have made the last three years of my life a memorable and unforgettable experience.

I am deeply indebted to my supervisor Prof. Philippe Benabes. Thanks for your support, for your intelligent guidance, for your valuable comments when I needed them must. A few words can not certainly express the extent to which I am indebted to your positive influence.

I have furthermore to thank the head of the department Prof. Gill Fleury, who supports me kindly during my thesis and encouraged me to go ahead with my thesis.

I have to thanks Prof. Jerome Juillard, for his stimulating support interest and valuable hints.

I have to thanks Prof. Matthieu Chatras, from XLIM laboratory, for his Collaboration and constructive comments during the analysis of the lamb-wave-resonators

I have to thanks Mr. Francis Trelin, for assistance during the process of laying out my chips.

I have to thanks Prof. Richard Kielbasa and Prof. Morgan Roger for all their help.

I have to thanks my colleagues supported me in my research work. I want to thank them for all their help, support, interest and motivation. Especially I am obliged to Mr. Luc Batalie, Ms. Karine Bernard, Mr. Bahman Soheilian and Mr. Zhiguo Song.

Finally, my most grateful thanks are reserved for my parents for their encouragement, patient, support and love, and for believing in me and having made all of this possible.

## Glossary

ADC Analog to Digital Converter

BAW Bulk Acoustic Wave Bi-CMOS Bipolar and CMO

CMOS Complementary Metal Oxide Semiconductor

CT Continuous Time

CTOC Current TO Current converter

CTOV Current TO Current converter

DAC Digital to Analog Converter

DR Dynamic Range

DSP Digital Signal Processors

**DT** Discrete Time

**EFBD** Extended Frequency Band Decomposition

**ENOB** Effective number of bits

ERWB Effective Resolution BandWidth

FBD Frequency Band Decomposition

Gm-C Classical resonator based on trans-inductance amplifier

and integrated capacitance

Gm-LC Classical resonator based on integrated capacitance and

inductance

HZ Half delay Zero

$\mathbf{IF}$ Intermediate Frequency LNA Low Noise Amplifier LSB Least Significant Bit **MASH** Multi Stage noise SHaping MSCL Multi Stage Closed Loop NRZ Non Return to Zero NTFNoise Transfer Function OSR Over Sampling Ratio  $\mathbf{RF}$ Radio Frequency

${f RZ}$  Return to Zero

SAW Surface Acoustic Wave

SMASHSturdy Multi Stage noise SHapingSNDRSignal to Noise and Distortion Ratio

$\begin{array}{lll} \mathbf{SNR} & & \text{Signal to Noise Ratio} \\ \mathbf{STF} & & \text{Signal Transfer Function} \\ \mathbf{TI}\Sigma\Delta & & \text{Time Interleaved Sigma-Delta} \\ \mathbf{VTOC} & & \text{Voltage TO Current converter} \end{array}$

$\prod \Sigma \Delta$  Parallel Sigma-Delta

# Contents

| Li            | st of | Figur | es           |                                   | xiii |

|---------------|-------|-------|--------------|-----------------------------------|------|

| $\mathbf{Li}$ | st of | Table | $\mathbf{S}$ |                                   | xxi  |

| 1             | Out   | line  |              |                                   | 1    |

|               | 1.1   | Motiv | ations       |                                   | . 1  |

|               | 1.2   | Objec | tives and    | completed work                    | . 3  |

|               | 1.3   |       |              | f the statement                   |      |

| 2             | Intr  | oduct | ion          |                                   | 5    |

|               | 2.1   | Basic | concepts     |                                   | . 5  |

|               |       | 2.1.1 | Analog-      | to-digital conversion             | . 5  |

|               |       | 2.1.2 | Quantiz      | ation error                       | . 6  |

|               |       |       | 2.1.2.1      | Model of Bennet                   | . 7  |

|               |       |       | 2.1.2.2      | Low-order quantizer               | . 8  |

|               |       | 2.1.3 | Oversan      | apling and decimation             | . 9  |

|               |       | 2.1.4 | Noise sh     | aping                             | . 11 |

|               |       |       | 2.1.4.1      | Delta conversion                  | . 11 |

|               |       |       | 2.1.4.2      | Sigma-delta conversion            | . 12 |

|               |       | 2.1.5 | From lo      | w-pass to band-pass conversion    | . 14 |

|               | 2.2   | Band- | pass cont    | inuous-time sigma-delta modulator | . 15 |

|               |       | 2.2.1 | Discrete     | -time or continuous time          | . 15 |

|               |       | 2.2.2 | From di      | screte-time to continuous-time    | . 17 |

|               | 2.3   | Globa | l loop filt  | er structures                     | . 19 |

|               |       | 2.3.1 | _            | age modulators                    |      |

|               |       |       | 2.3.1.1      | MASH structures                   |      |

|   |      |         | 2.3.1.2 MSCL structures                        | 21 |

|---|------|---------|------------------------------------------------|----|

|   |      | 2.3.2   | Single-stage modulators                        | 22 |

|   |      |         | 2.3.2.1 Multi-feedback structures              | 22 |

|   |      |         | 2.3.2.2 Mono-feedback structures               | 23 |

|   |      |         | 2.3.2.3 Weighted feedforward structures        | 23 |

|   | 2.4  | Perfor  | mance criteria                                 | 24 |

|   |      | 2.4.1   | Resolution criteria                            | 24 |

|   |      |         | 2.4.1.1 Signal to noise ratio                  | 24 |

|   |      |         | 2.4.1.2 Bit resolution                         | 25 |

|   |      |         | 2.4.1.3 Signal to noise and distortion ratio   | 25 |

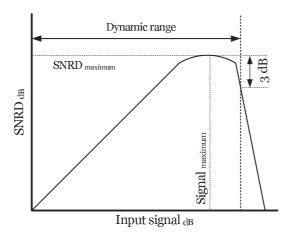

|   |      |         | 2.4.1.4 Input dynamic range                    | 25 |

|   |      | 2.4.2   | Stability criteria                             | 25 |

|   |      |         | 2.4.2.1 Bounded input-bounded output criterion | 27 |

|   |      |         | 2.4.2.2 Lee criterion                          | 27 |

|   |      |         | 2.4.2.3 Classical stability margins            | 27 |

|   | 2.5  | Sigma   | -delta modulators history and trends           | 30 |

|   | 2.6  | Conclu  | asion                                          | 32 |

| 3 | Scor | pe of F | Problem 3                                      | 33 |

|   | 3.1  | •       |                                                | 33 |

|   |      | 3.1.1   | •                                              | 33 |

|   |      | 3.1.2   |                                                | 36 |

|   | 3.2  | Specifi | ı                                              | 38 |

|   |      | 3.2.1   | •                                              | 38 |

|   |      | 3.2.2   |                                                | 39 |

|   |      | 3.2.3   | <i>Q</i> -factor                               | 41 |

|   | 3.3  | Specifi |                                                | 43 |

|   | 3.4  | -       |                                                | 45 |

|   |      | 3.4.1   |                                                | 45 |

|   |      | 3.4.2   | •                                              | 49 |

|   | 3.5  |         |                                                | 50 |

|   | 3.6  | Concli  |                                                | 52 |

| 4 | Lan | nb Wa  | ve Resonators                              | <b>55</b>  |

|---|-----|--------|--------------------------------------------|------------|

|   | 4.1 | Choice | e of resonator                             | 56         |

|   |     | 4.1.1  | Classical resonators                       | 56         |

|   |     | 4.1.2  | Gm-LC resonators                           | 56         |

|   |     | 4.1.3  | Gm-C resonators                            | 56         |

|   |     | 4.1.4  | Micro-mechanical resonators                | 57         |

|   |     | 4.1.5  | Piezo-electric resonators                  | 58         |

|   |     |        | 4.1.5.1 Surface acoustic wave resonators   | 59         |

|   |     |        | 4.1.5.2 Bulk acoustic wave resonators      | 60         |

|   |     |        | 4.1.5.3 Lamb wave resonators               | 61         |

|   | 4.2 | Chara  | acteristics of LWRs                        | 62         |

|   |     | 4.2.1  | Electrical model                           | 62         |

|   |     | 4.2.2  | Anti-resonance                             | 64         |

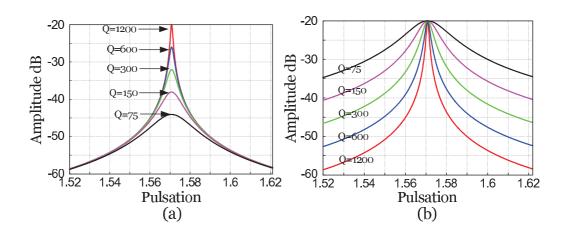

|   |     | 4.2.3  | Quality factor                             | 66         |

|   |     | 4.2.4  | Harmonic content                           | 68         |

|   | 4.3 | Reson  | ator circuit                               | 69         |

|   | 4.4 | Concl  | usion                                      | 71         |

| 5 | Hig | h-Ord  | er Single-Stage Delta-Sigma Modulators     | <b>7</b> 3 |

|   | 5.1 | Modu   | lator global filter synthesis              | 76         |

|   |     | 5.1.1  | Global filter topology                     | 76         |

|   |     | 5.1.2  | DAC delay management                       | 78         |

|   |     | 5.1.3  | Synthesis method                           | 79         |

|   | 5.2 | Analo  | g imperfections                            | 82         |

|   |     | 5.2.1  | Compensation capacitance                   | 83         |

|   |     | 5.2.2  | Buffers cut-off frequency                  | 84         |

|   |     | 5.2.3  | Input and output impedances of the buffers | 85         |

|   |     | 5.2.4  | Harmonics of LWR                           | 86         |

|   |     | 5.2.5  | Trans-impedance gains                      | 87         |

|   |     | 5.2.6  | Feedforward coefficients                   | 88         |

|   |     | 5.2.7  | Loop delay                                 | 89         |

|   |     | 5.2.8  | All imperfections simulation               | 90         |

|   | 5.3 | Optim  | nization method                            | 91         |

|   | 5.4  | STF sl    | haping                                                          | 99  |

|---|------|-----------|-----------------------------------------------------------------|-----|

|   | 5.5  | Conclu    | nsion                                                           | 105 |

| 3 | Elec | etronic   | design 1                                                        | .07 |

|   | 6.1  |           | e of technology                                                 | 109 |

|   | 6.2  |           | t rules                                                         |     |

|   | 6.3  | Compo     | onent design                                                    | 114 |

|   |      | 6.3.1     | Voltage to current converter                                    | 114 |

|   |      | 6.3.2     | Current to voltage converter                                    | 115 |

|   |      | 6.3.3     | Current to current converter                                    | 116 |

|   |      | 6.3.4     | Amplifier                                                       | 118 |

|   |      | 6.3.5     | Analog to digital converter                                     | 119 |

|   |      |           | 6.3.5.1 Comparator circuit                                      | 121 |

|   |      |           | 6.3.5.2 Rectifier system                                        | 122 |

|   |      |           | 6.3.5.3 Delay                                                   | 123 |

|   |      |           | 6.3.5.4 Clock                                                   | 124 |

|   |      | 6.3.6     | Digital to analog converter                                     | 124 |

|   |      | 6.3.7     | DC current sources                                              | 127 |

|   |      | 6.3.8     | DC voltage sources                                              | 127 |

|   | 6.4  | Design    | of a second-order single-stage sigma-delta modulator working at |     |

|   |      | $f_c = 0$ | $25f_s$                                                         | 128 |

|   |      | 6.4.1     | Voltage to current converter                                    | 129 |

|   |      | 6.4.2     | Current to voltage converter                                    | 132 |

|   |      | 6.4.3     | Current to current converter                                    | 134 |

|   |      | 6.4.4     | Amplifier                                                       | 137 |

|   |      | 6.4.5     | Analog to digital converter                                     | 137 |

|   |      |           | 6.4.5.1 comparator                                              | 137 |

|   |      |           | 6.4.5.2 Rectifier system                                        | 141 |

|   |      |           | 6.4.5.3 Delay                                                   | 142 |

|   |      | 6.4.6     |                                                                 | 145 |

|   |      | 6.4.7     | Clock generator                                                 | L47 |

|   |      | 6.4.8     | The performance of the second-order $\Sigma\Delta$ modulator    | 149 |

|   | 6.5  | Model     | Extraction                                                      | 154 |

|              | 6.6   | Conclusion                                                           | 158 |

|--------------|-------|----------------------------------------------------------------------|-----|

| 7            | Con   | aclusions and perspectives                                           | 161 |

|              | 7.1   | Conclusions                                                          | 161 |

|              | 7.2   | Perspectives                                                         | 163 |

| $\mathbf{A}$ |       |                                                                      | 165 |

|              | A.1   | The modulus of the NTF of a $6^{th}$ -order MSCL employing band-pass |     |

|              |       | resonators with infinite $Q$ -factors                                | 166 |

|              | A.2   | The modulus of the NTF of a $6^{th}$ -order MSCL employing band-pass |     |

|              |       | resonators with finite $Q$ -factors                                  | 168 |

| Bi           | bliog | graphy                                                               | 171 |

# List of Figures

| 1.1  | The principle of software radio solution                                             | 1  |

|------|--------------------------------------------------------------------------------------|----|

| 2.1  | Analog-to-digital conversion                                                         | 5  |

| 2.2  | Quantization principle                                                               | 6  |

| 2.3  | Quantizer linear model                                                               | 7  |

| 2.4  | Noise spectrum of the quantization error                                             | 8  |

| 2.5  | The linear model of a low-order quantizer                                            | 9  |

| 2.6  | Comparison the Nyquist-rate anti-aliasing filter with two-times oversam-             |    |

|      | pling anti-aliasing filter (a), the quantization process of a 2x oversam-            |    |

|      | pling ADC(b)                                                                         | 10 |

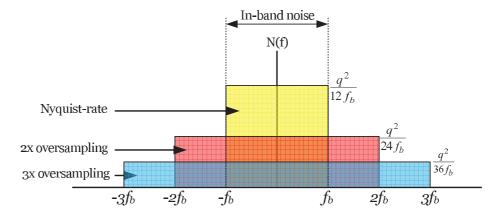

| 2.7  | Comparison the in-band noise of Nyquist-rate ADCs and that of over-                  |    |

|      | sampling ADCs.                                                                       | 11 |

| 2.8  | Delta modulation principle                                                           | 12 |

| 2.9  | $\Sigma\Delta$ modulation                                                            | 12 |

| 2.10 | Linear model of a first-order low-pass DT $\Sigma\Delta$ modulator                   | 13 |

| 2.11 | Comparison the noise spectrum of a Nyquist-rate ADC, an oversampling                 |    |

|      | ADC and a first-order low-pass $\Sigma\Delta$ modulator                              | 14 |

| 2.12 | Low-pass modulator (a) and band-pass modulator (b) in DT domain. $\;\;$ .            | 14 |

| 2.13 | DT $\Sigma\Delta$ modulator structure (a), CT $\Sigma\Delta$ modulator structure (b) | 15 |

| 2.14 | Influence of clock jitter on charge loss in DT (a) and CT (b) modulators.            | 17 |

| 2.15 | Model of the response of the ADC+DAC                                                 | 18 |

| 2.16 | A possible implementation of equation 2.13                                           | 18 |

| 2.17 | Proposed topology in [54] for implementing $D(z)$                                    | 19 |

| 2.18 | Fourth-order MASH topology                                                           | 20 |

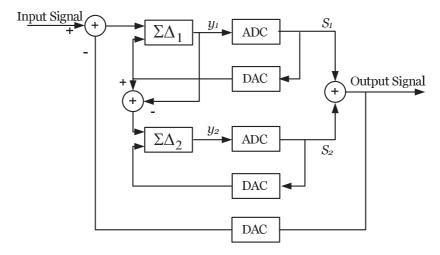

| 2.19 | Second-order MSCL topology                                                           | 22 |

| 2.20 | $6^{th}$ -order multi-feedback structure                                           | 22 |

|------|------------------------------------------------------------------------------------|----|

| 2.21 | $6^{th}$ -order mono-feedback structure                                            | 23 |

| 2.22 | $6^{th}$ -order feedforward structure                                              | 24 |

| 2.23 | Concept of the input signal dynamic range                                          | 26 |

| 2.24 | Modulus, gain and phase margin for the open-loop frequency characteristic. $$      | 27 |

| 2.25 | Required DT linear model of CT modulators for calculating the stability            |    |

|      | margins                                                                            | 28 |

| 2.26 | Another representation of figure 2.16                                              | 29 |

| 2.27 | First step to find the linear DT mono-loop model                                   | 29 |

| 2.28 | DT linear model of CT modulators to calculate the modulus margin                   | 30 |

| 3.1  | Frequency band decomposition principle                                             | 34 |

| 3.2  | Comparison the work-band of a band-pass FBD system with that of a                  |    |

|      | FBD system for $N = 5$                                                             | 34 |

| 3.3  | Extended frequency band decomposition principle                                    | 35 |

| 3.4  | Variation of the modulator resolution versus the modulator order for               |    |

|      | several values of the quantizer number of bits when the OSR is equal to            |    |

|      | 64                                                                                 | 38 |

| 3.5  | Output noise spectrum density of a $6^{th}$ -order CT MSCL working at              |    |

|      | $f_c = 0.25 f_s.  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 40 |

| 3.6  | Modulator resolution (a) and required number of modulators (b) to cover            |    |

|      | the frequency band of interest $(0.2f_s < f < 0.3f_s)$ versus OSR. The             |    |

|      | dotted line indicates the resulting resolution and the required number of          |    |

|      | modulators when OSR= 64                                                            | 41 |

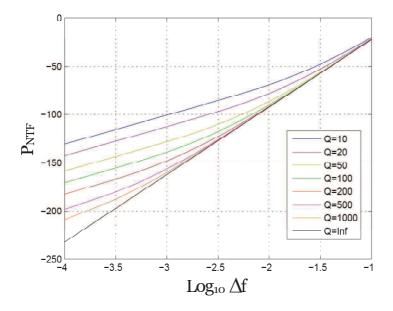

| 3.7  | Variation of $P_{NTF}$ versus the modulator bandwidth $(\Delta f)$ for several     |    |

|      | values of the $Q$ -factor                                                          | 42 |

| 3.8  | Variation of $P_{NTF}$ versus $Q$ -factors for an OSR equal to 64                  | 42 |

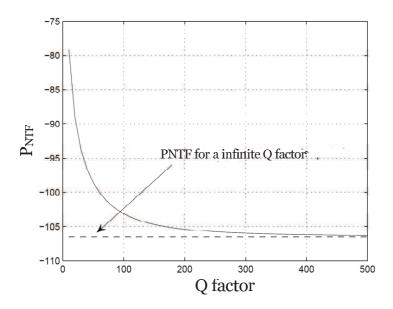

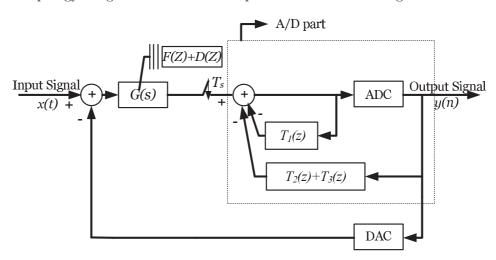

| 3.9  | Variation of $P_{NTF}$ versus $\lambda$                                            | 44 |

| 3.10 | Another representation of figure 2.17                                              | 45 |

| 3.11 | Linear model of the A/D part of figure 3.10                                        | 46 |

| 3.12 | DT equivalent model of figure 2.17                                                 | 47 |

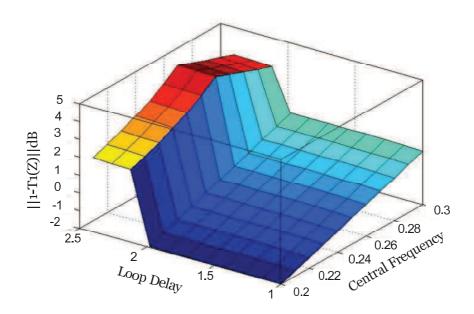

| 3.13 | Variation $  1 - T_1(z)  $ in dB versus $f_c$ (0.2 < $f_c$ < 0.3) and loop delay   |    |

|      | (1T. < delay < 2.5T.)                                                              | 48 |

| 3.14 | Topology obtained by removing $T_1(z)$ and $T_2(z)$                                       | 49 |

|------|-------------------------------------------------------------------------------------------|----|

| 3.15 | Variations of $a_1$ and $a_2$ (equation 3.21) versus the modulator central                |    |

|      | frequency                                                                                 | 49 |

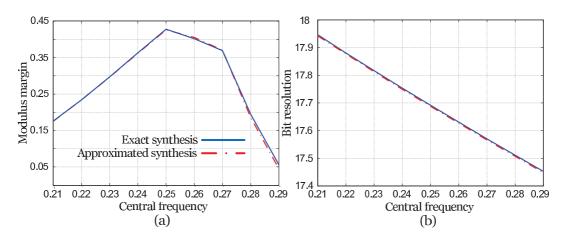

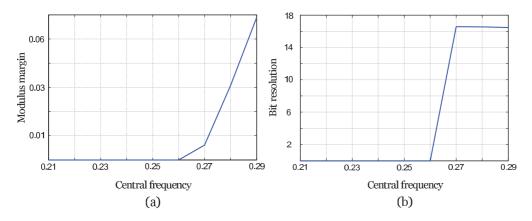

| 3.16 | Modulus margin (a) and bit resolution (b) of the proposed topology com-                   |    |

|      | pared with those of the original DT modulator, versus central frequency.                  | 50 |

| 3.17 | System modifications necessary to calculate the exact STF                                 | 51 |

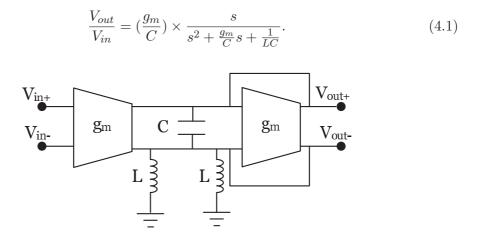

| 4.1  | Structure of a typical second-order Gm-LC resonator                                       | 56 |

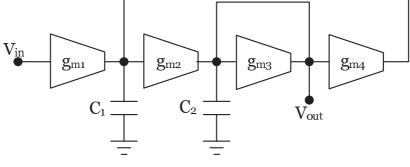

| 4.2  | Structure of a typical second-order Gm-C resonator                                        | 57 |

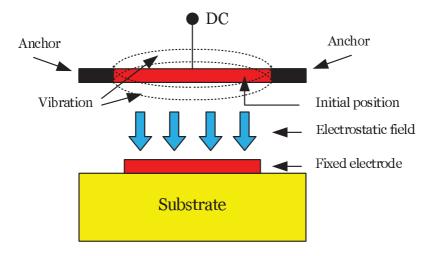

| 4.3  | Schematic view of a typical vibrating beam MEMS                                           | 58 |

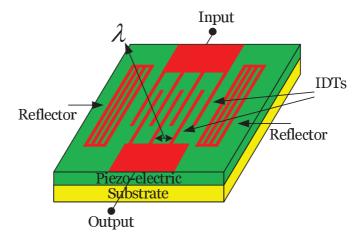

| 4.4  | Schematic view of a typical SAW resonator                                                 | 59 |

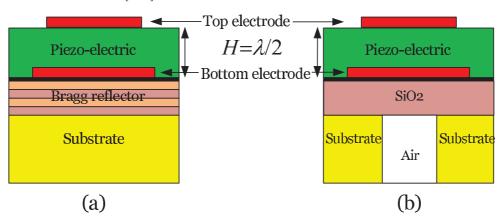

| 4.5  | Schematic views of a typical SMR resonator (a) and a typical FBAR                         |    |

|      | resonator (b)                                                                             | 60 |

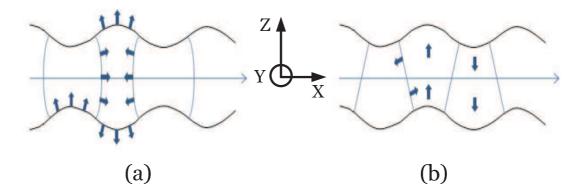

| 4.6  | Symmetric (a) and asymmetric (b) modes of lamb wave                                       | 61 |

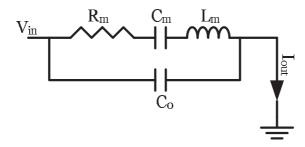

| 4.7  | Equivalent model of a one-port piezo-electric resonator                                   | 62 |

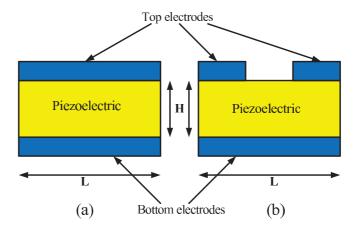

| 4.8  | Lamb wave resonator working on (a) fundamental (b) third harmonic                         | 63 |

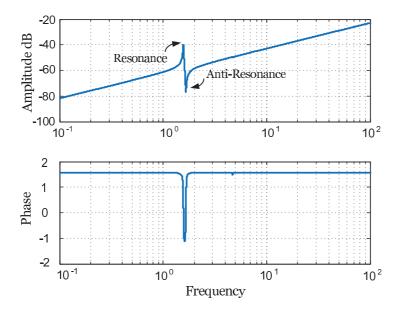

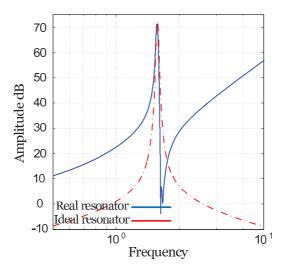

| 4.9  | Frequency response of the LWR corresponding to table 4.1                                  | 64 |

| 4.10 | Comparison the global filter transfer function of a $6^{th}$ -order $\Sigma\Delta$ modu-  |    |

|      | lator employing an ideal band-pass resonator and a practical LWR                          | 65 |

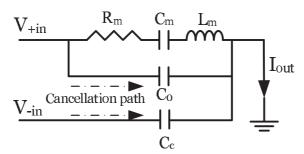

| 4.11 | Principle of anti-resonance cancellation                                                  | 65 |

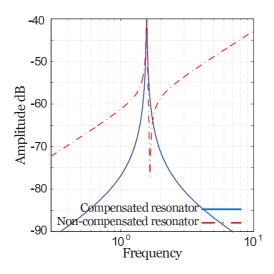

| 4.12 | Compensated resonator and non-compenated resonator transfer functions. $$                 | 66 |

| 4.13 | Influence of electrical (a) and acoustic (b) losses on the $Q$ -factor                    | 67 |

| 4.14 | Approximate electrical model of LWR considering the third and fifth                       |    |

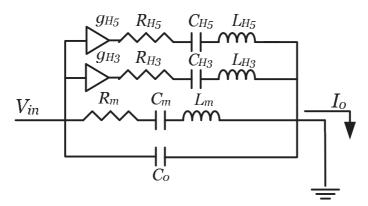

|      | harmonics                                                                                 | 68 |

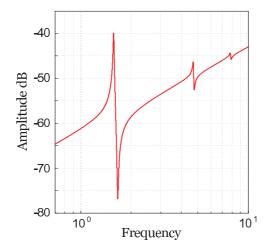

| 4.15 | Frequency response of the electrical model of figure $4.14$                               | 69 |

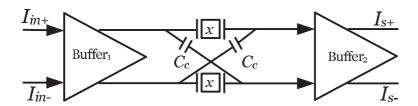

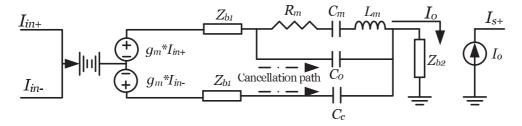

| 4.16 | Electronic control circuit of the LWR                                                     | 70 |

| 4.17 | Equivalent model of the positive path of the electronic control circuit                   | 70 |

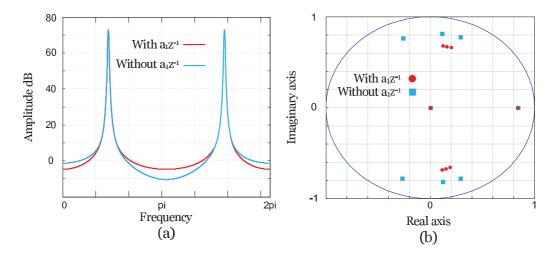

| 5.1  | Influence of $T_1(z) = a_1 z^{-1}$ on the modulus of the DT equivalent of the             |    |

|      | global filter (a) and the position of the NTF poles (b) for $f_c=0.22f_s$ .               | 73 |

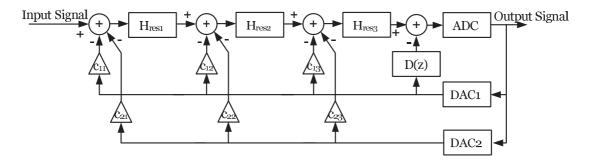

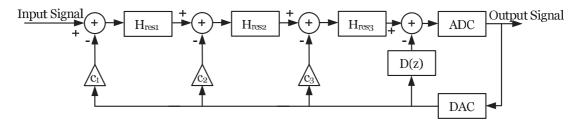

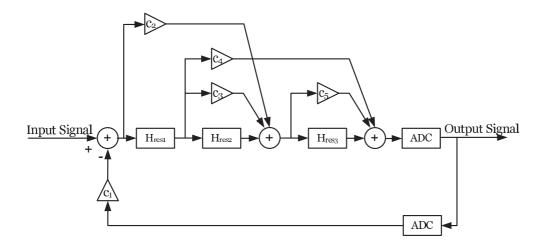

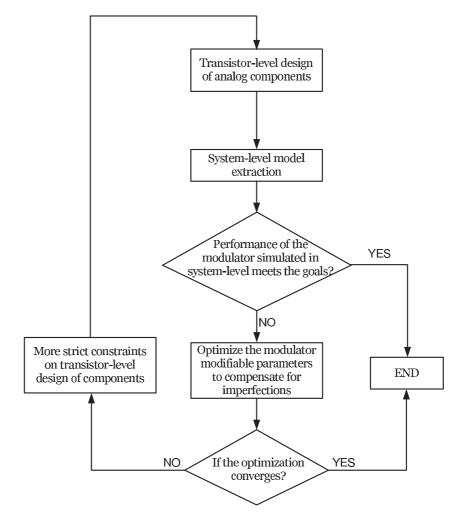

| 5.2  | Proposed optimization method                                                              | 75 |

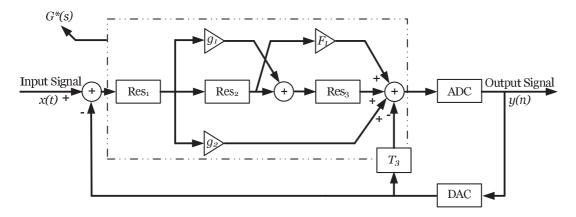

| 5.3  | The topology proposed to synthesize the global filter transfer function. $\boldsymbol{.}$ | 76 |

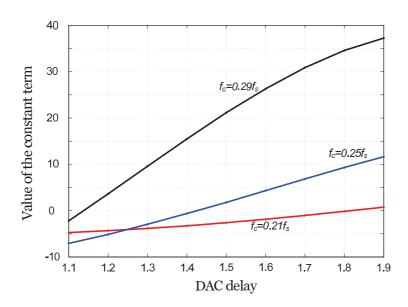

| 5.4  | Variation of the constant term versus DAC delay for several $f_c$                         | 78 |

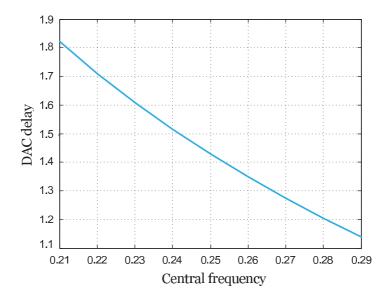

| 5.5  | DAC delay value canceling out the constant term versus the modulator                    |            |

|------|-----------------------------------------------------------------------------------------|------------|

|      | central frequency                                                                       | <b>7</b> 9 |

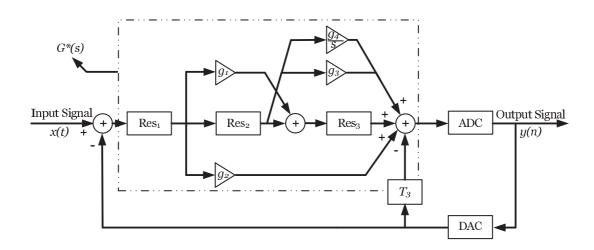

| 5.6  | Developed topology of figure 5.3                                                        | 80         |

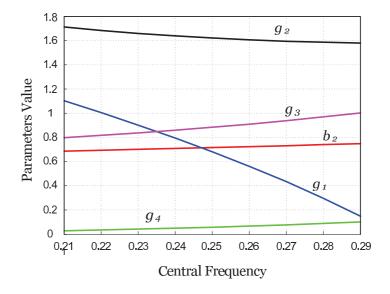

| 5.7  | Evolution of unknown parameters versus the modulator central frequency.                 | 81         |

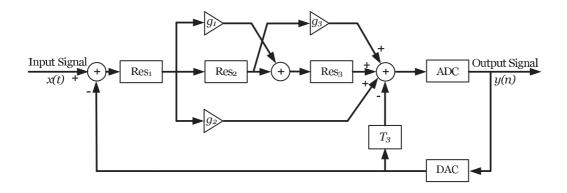

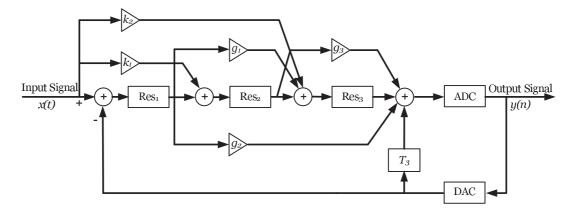

| 5.8  | Final topology of the modulator                                                         | 82         |

| 5.9  | Comparison of the performance of the topology of figure 5.6 with the                    |            |

|      | topology of figure 5.8                                                                  | 82         |

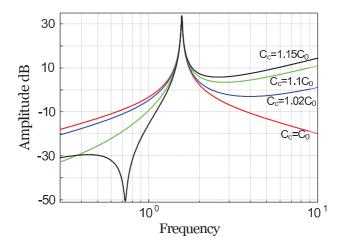

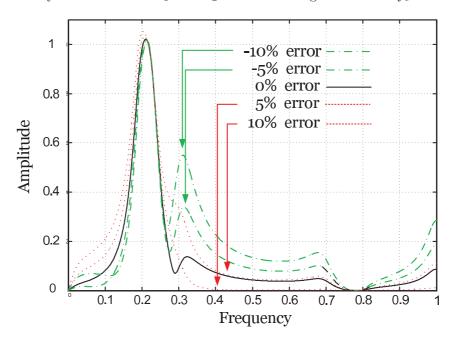

| 5.10 | Influence of the mismatch between $C_c$ and $C_0$ on the frequency response             |            |

|      | of th resonator for different values of error                                           | 83         |

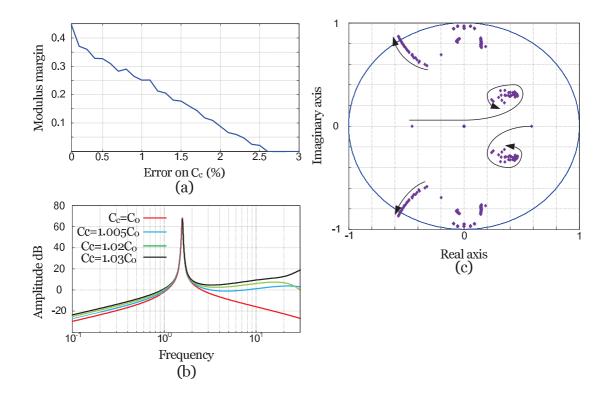

| 5.11 | Influence of mismatch between $C_c$ and $C_0$ on the modulus margin (a),                |            |

|      | the global filter transfer function $(G(s))$ (b) and the position of the NTF            |            |

|      | poles (c)                                                                               | 84         |

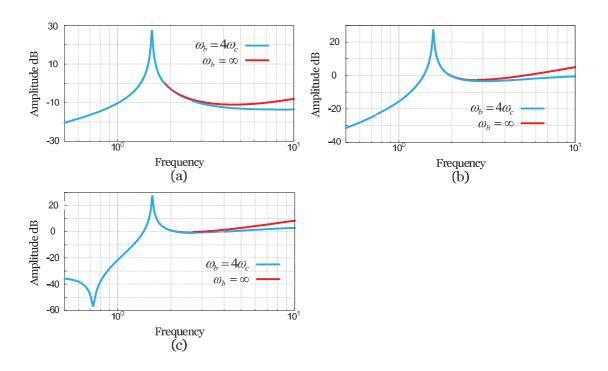

| 5.12 | Frequency response of the resonator for $C_c = 1.02C_0$ (a), $C_c = 1.10C_0$            |            |

|      | (b) and $C_c = 1.15C_0$ (c) when the buffers are ideal $(\omega_b = \infty)$ and when   |            |

|      | they have a pole at $\omega_b = 4\omega_c$                                              | 85         |

| 5.13 | Influence of an ohmic $z_{b1}$ and $z_{b2}$ on the modulus margin (a), the reso-        |            |

|      | lution (b), the global filter transfer function $(G(s))$ (c) and the position           |            |

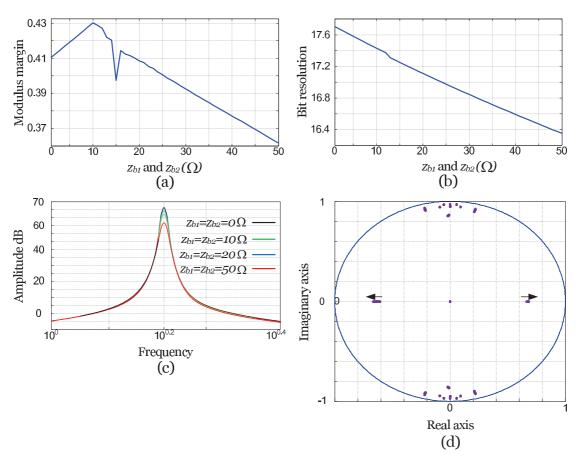

|      | of the NTF poles (d). $\hdots$                                                          | 86         |

| 5.14 | Influence of harmonics on the modulus margin (a), the global filter trans-              |            |

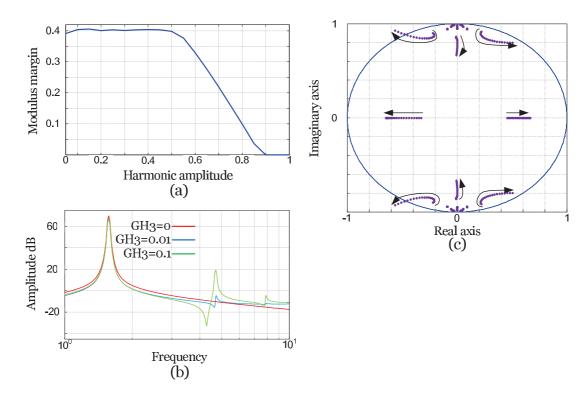

|      | fer function $(G(s))$ (b) and the position of the NTF poles (c)                         | 87         |

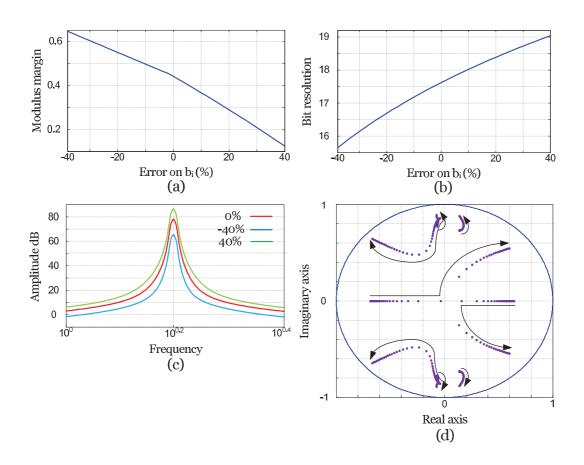

| 5.15 | Influence of the trans-impedance gains $(b_1, b_2 \text{ and } b_3)$ on the modulus     |            |

|      | margin (a), the modulator resolution (b), the global filter transfer func-              |            |

|      | tion $(G(s))$ (c) and the position of the NTF poles (d)                                 | 88         |

| 5.16 | Influence of feedforward coefficients $(g_1, g_2 \text{ and } g_3)$ on the modulus mar- |            |

|      | gin (a), the global filter transfer function $(G(s))$ (b) and the position of           |            |

|      | the NTF poles (c)                                                                       | 89         |

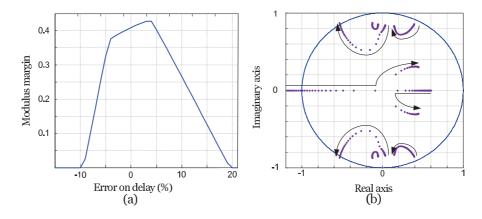

| 5.17 | Influence of $d$ on modulus margin (a) and position of the NTF poles (b).               | 89         |

| 5.18 | Modulus margin (a) and the bit resolution (b) of the proposed topology                  |            |

|      | for various modulator central frequencies accounting analog imperfec-                   |            |

|      | tions given by equation $5.12.$                                                         | 90         |

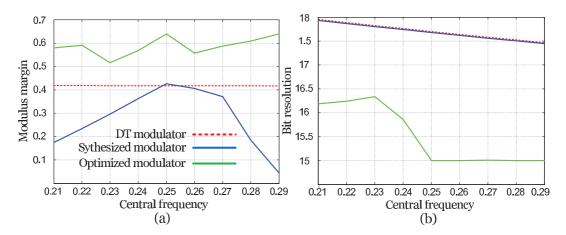

| 5.19 | Comparison of the modulus margin (a) and the bit resolution of the                      |            |

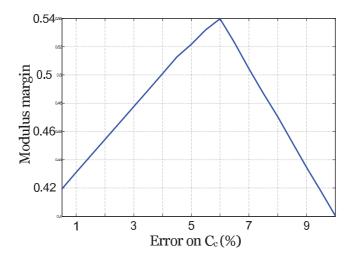

|      | optimized, synthesized and original DT modulator                                        | 93         |

| 5.20 | Sensitivity of the modulus margin of the optimized modulator to $C_c$    |     |

|------|--------------------------------------------------------------------------|-----|

|      | mismatch for $f_c = 0.29 f_s$                                            | 94  |

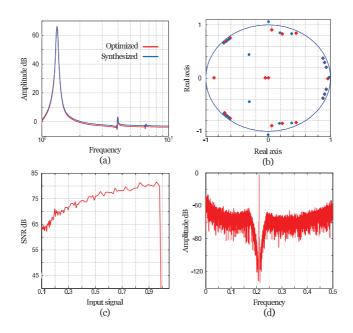

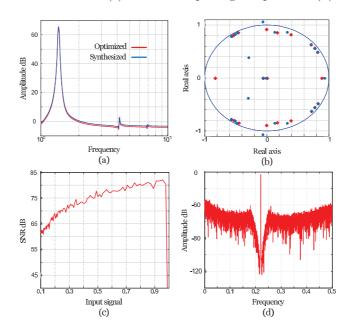

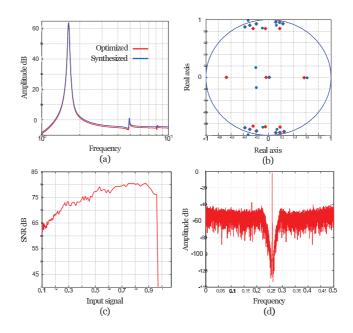

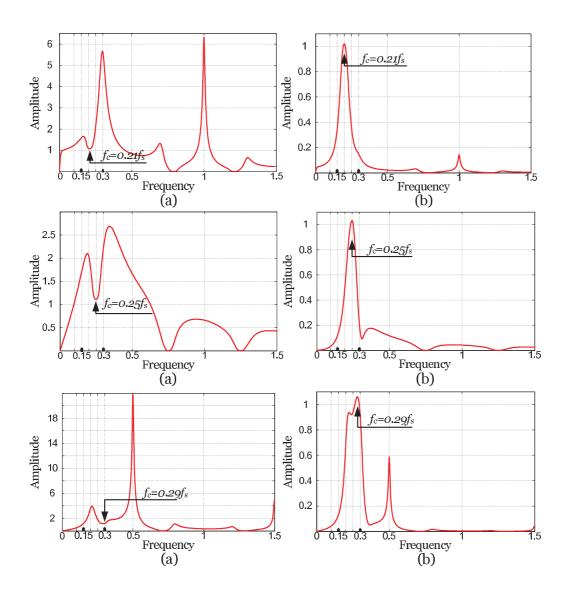

| 5.21 | G(s) (a) and the position of the NTF poles (b) for optimized and non     |     |

|      | optimized modulator. The SNR (c) and the output signal spectrum (d)      |     |

|      | for $f_c = 0.21 f_s$                                                     | 95  |

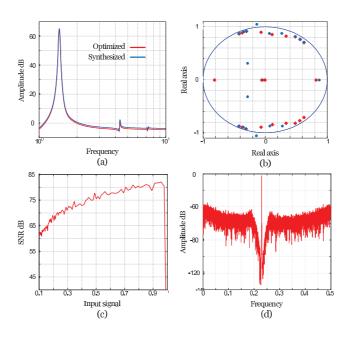

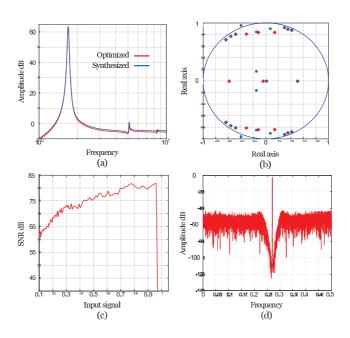

| 5.22 | G(s) (a) and the position of the NTF poles (b) for optimized and non     |     |

|      | optimized modulator. The SNR (c) and the output signal spectrum (d)      |     |

|      | for $f_c = 0.22 f_s$                                                     | 95  |

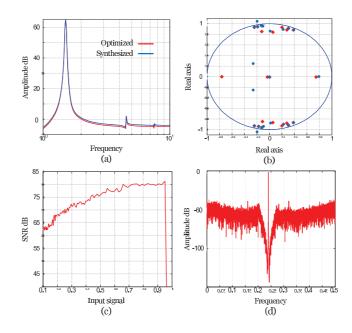

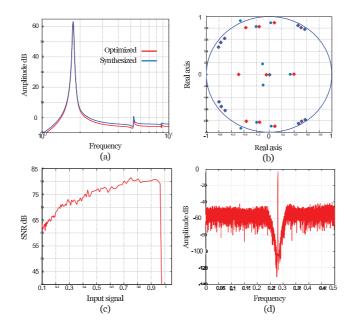

| 5.23 | G(s) (a) and the position of the NTF poles(b) for optimized and non      |     |

|      | optimized modulator. The SNR (c) and the output signal spectrum (d)      |     |

|      | for $f_c = 0.23 f_s$                                                     | 96  |

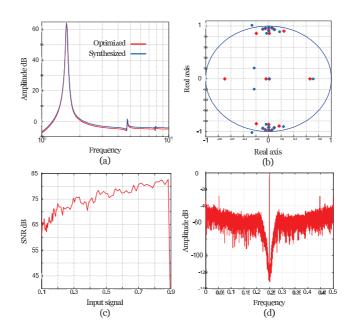

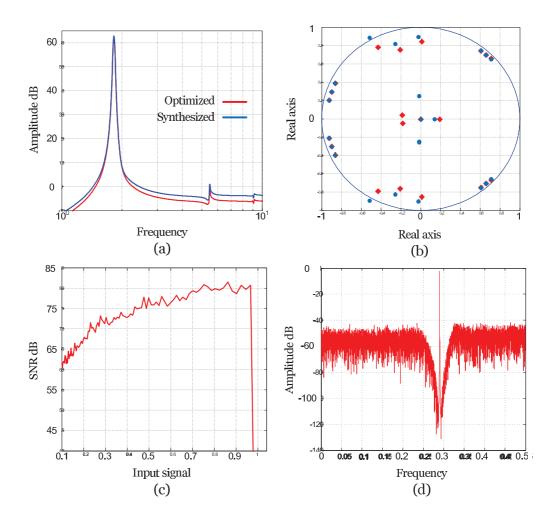

| 5.24 | G(s) (a) and the position of the NTF poles (b) for optimized and non     |     |

|      | optimized modulator. The SNR (c) and the output signal spectrum (d)      |     |

|      | for $f_c = 0.24 f_s$                                                     | 96  |

| 5.25 | G(s) (a) and the position of the NTF poles(b) for optimized and non      |     |

|      | optimized modulator. The SNR (c) and the output signal spectrum (d)      |     |

|      | for $f_c = 0.25 f_s$                                                     | 97  |

| 5.26 | G(s) (a) and the position of the NTF poles (b) for optimized and non     |     |

|      | optimized modulator. The SNR (c) and the output signal spectrum (d)      |     |

|      | for $f_c = 0.26 f_s$                                                     | 97  |

| 5.27 | G(s) (a) and the position of the NTF poles (b) for optimized and non     |     |

|      | optimized modulator. The SNR (c) and the output signal spectrum (d)      |     |

|      | for $f_c = 0.27 f_s$                                                     | 98  |

| 5.28 | G(s) (a) and the position of the NTF poles (b) for optimized and non     |     |

|      | optimized modulator. The SNR (c) and the output signal spectrum (d)      |     |

|      | for $f_c = 0.28 f_s$                                                     | 98  |

| 5.29 | G(s) (a) and the position of the NTF poles (b) for optimized and non     |     |

|      | optimized modulator. The SNR (c) and the output signal spectrum (d)      |     |

|      | for $f_c = 0.29 f_s$                                                     | 99  |

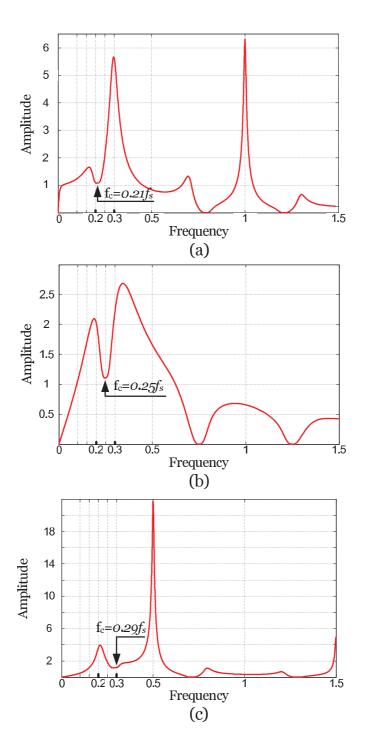

| 5.30 | STF for $f_c = 0.21 f_s$ (a), $f_c = 0.25 f_s$ (b), $f_c = 0.29 f_s$ (c) | 100 |

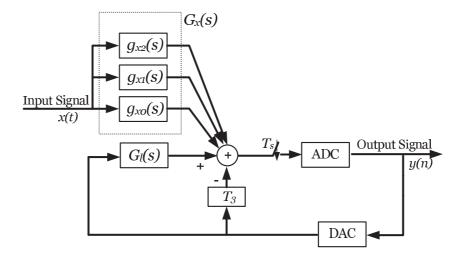

| 5.31 | Modifiable STF topology                                                  | 101 |

| 5.32 | Another representation of the modifiable STF topology.<br>$\dots$ .      | 101 |

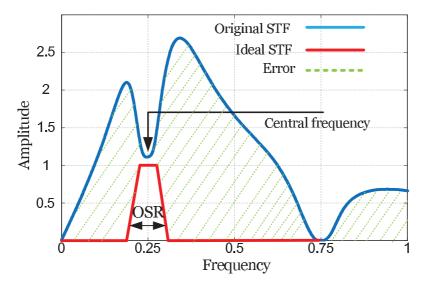

| 5.33 | The principle of $k_i$ optimization                                      | 102 |

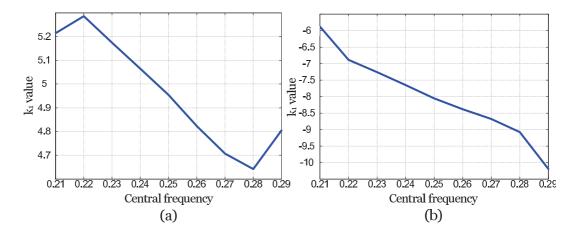

| 5.34 | Optimal values of $k_1$ and $k_2$                                                                                                                  | 103 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.35 | Sensitivity of the STF to variations of $k_1$ and $k_2$ for $f_c = 0.25 f_s$                                                                       | 103 |

| 5.36 | Comparing the STF before optimization when $k_1 = k_2 = 0$ (a) and after                                                                           |     |

|      | optimization (b) for several modulator central frequencies ( $f_c = 0.21 f_s$ ,                                                                    |     |

|      | $f_c = 0.25 f_s \text{ and } f_c = 0.29 f_s$ )                                                                                                     | 104 |

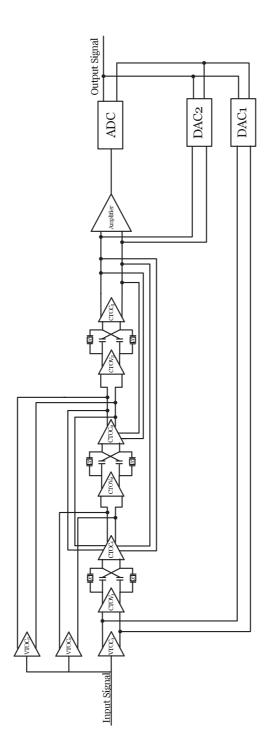

| 6.1  | Schematic of the proposed $6^{th}$ -order $\Sigma\Delta$ modulator                                                                                 | 108 |

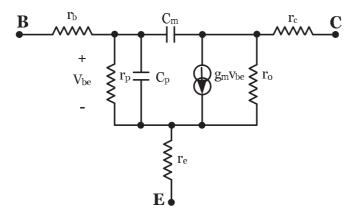

| 6.2  | $\pi\text{-hybrid}$ model of BJT transistors                                                                                                       | 110 |

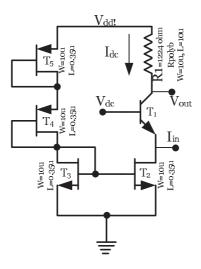

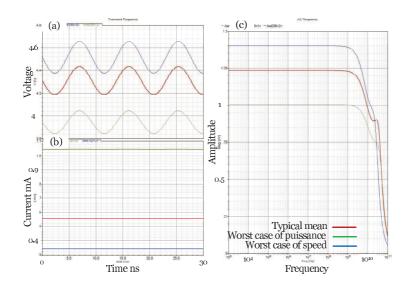

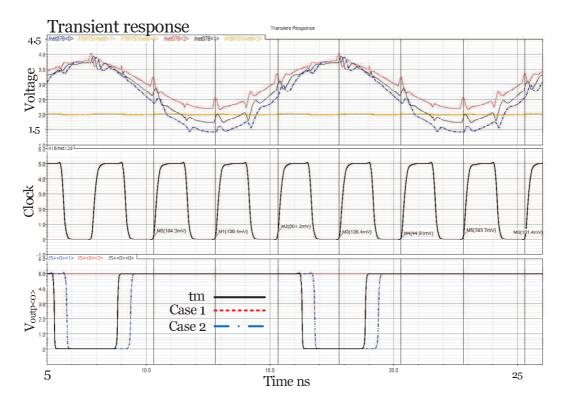

| 6.3  | Benchmark schematic to test the influence of the worst cases                                                                                       | 112 |

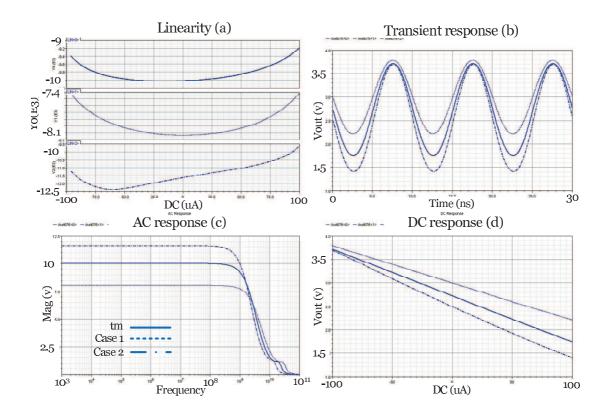

| 6.4  | Variations of $V_{out}$ (a), $I_{dc}$ (b) and AC response (c) for $tm$ and the worst                                                               |     |

|      | cases                                                                                                                                              | 112 |

| 6.5  | Schematic of the voltage to current converter                                                                                                      | 114 |

| 6.6  | Schematic of the current to voltage converter                                                                                                      | 115 |

| 6.7  | Driving voltage and current of the first LWR of the proposed structure.                                                                            | 116 |

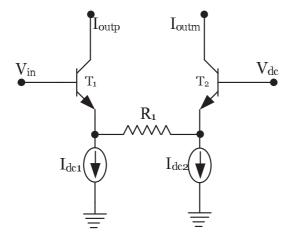

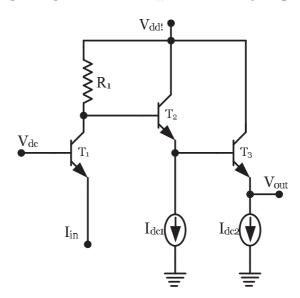

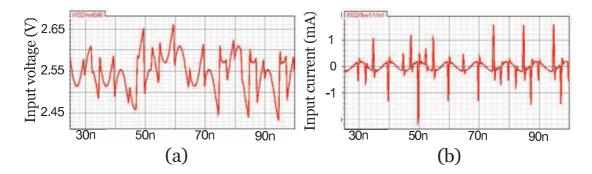

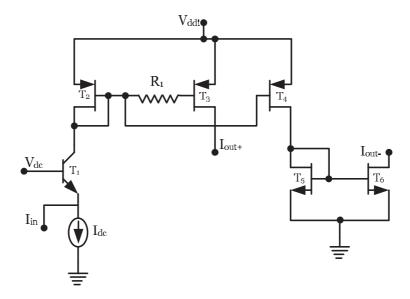

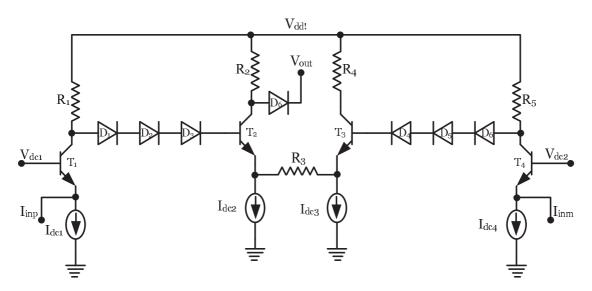

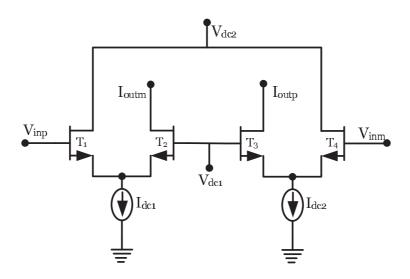

| 6.8  | Schematic of the current to current converter cell                                                                                                 | 117 |

| 6.9  | Global view of the differential buffer                                                                                                             | 117 |

| 6.10 | Schematic of the amplifier                                                                                                                         | 118 |

| 6.11 | Schematic of the $D_i$ stages (a) and a diode arrange (b)                                                                                          | 119 |

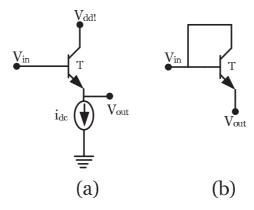

| 6.12 | 3-bits flash ADC                                                                                                                                   | 120 |

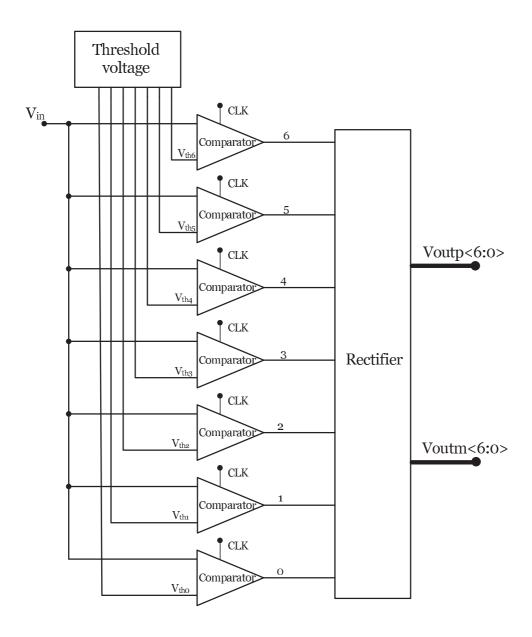

| 6.13 | Schematic of a dynamic voltage-mode comparator                                                                                                     | 121 |

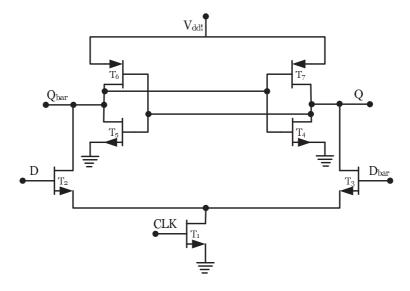

| 6.14 | Differential flip-flop                                                                                                                             | 122 |

| 6.15 | Schematic of the D-latch                                                                                                                           | 123 |

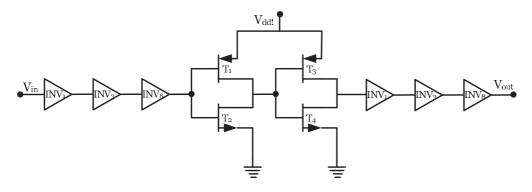

| 6.16 | Schematic of the delay                                                                                                                             | 123 |

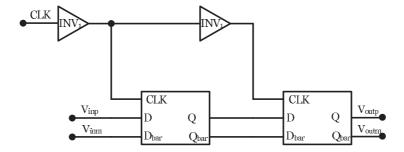

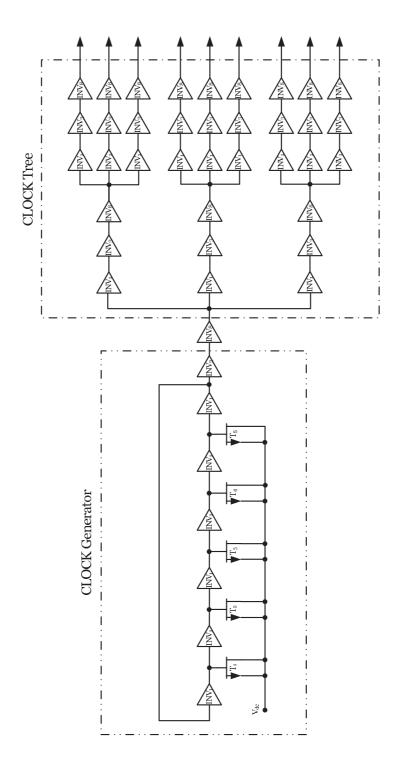

| 6.17 | Schematic of the clock generator and the clock tree                                                                                                | 125 |

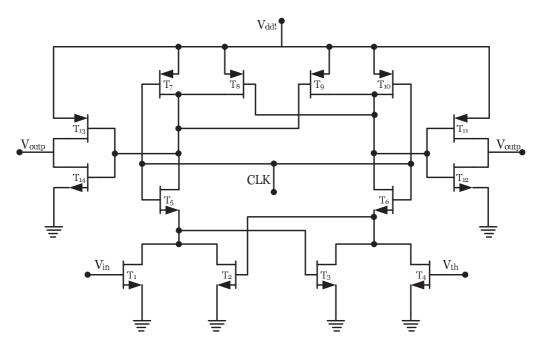

| 6.18 | Schematic of the DAC cell                                                                                                                          | 126 |

| 6.19 | Global topology of digital to analog converter                                                                                                     | 126 |

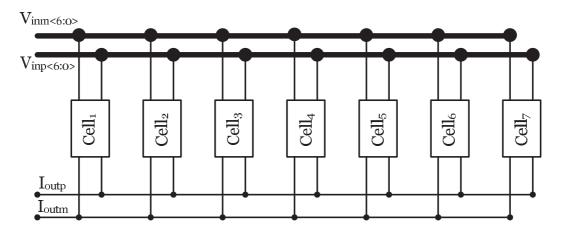

| 6.20 | Simple n-mode current mirror (a) Cascade n-mode current mirror (b)                                                                                 |     |

|      | and n-mode to p-mode current converter (c). $\ \ldots \ \ldots \ \ldots \ \ldots$                                                                  | 127 |

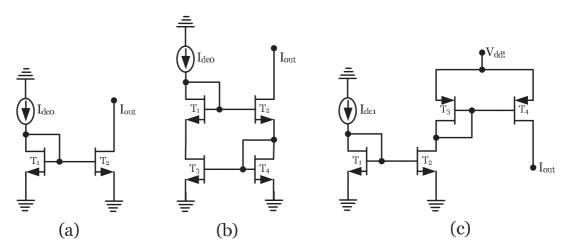

| 6.21 | p-MOS transistor resistor bridge (a) and resistor bridge (b)                                                                                       | 128 |

| 6.22 | Second-order single-stage $\Sigma\Delta$ modulator                                                                                                 | 128 |

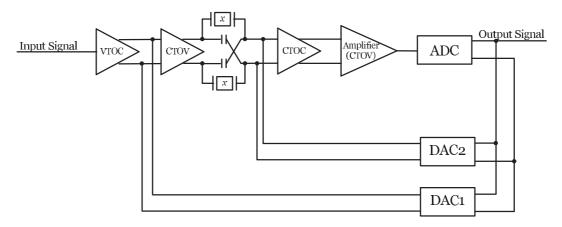

|      | Schematic of the second-order modulator                                                                                                            | 129 |

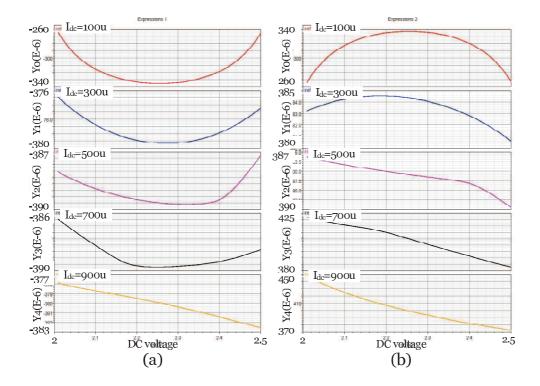

| 6.24 | Linearity $(\frac{\partial I_{\text{outp}}}{\partial V_{in_{dc}}})$ of VTOC output $(I_{\text{outp}}$ (a) and $I_{\text{outm}}$ (b)) for different |     |

|      | hias currents                                                                                                                                      | 130 |

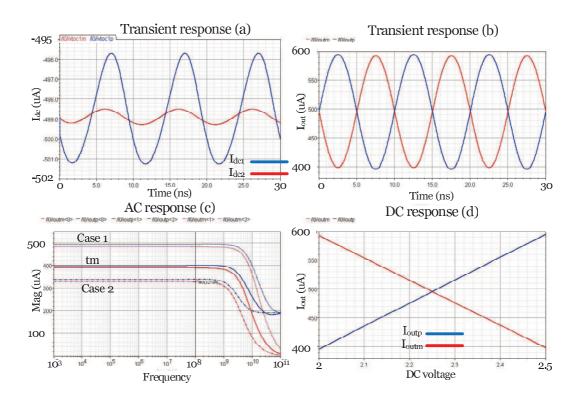

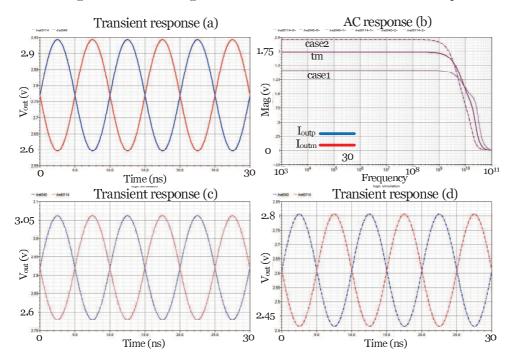

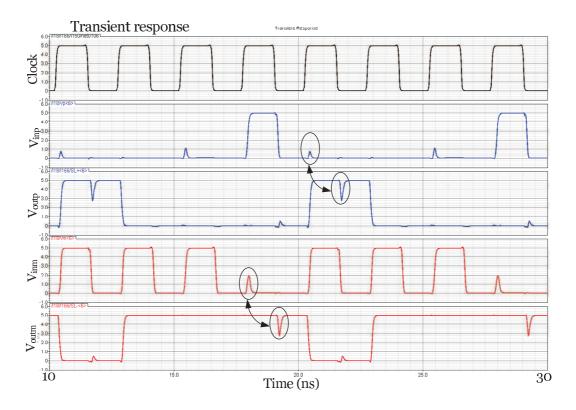

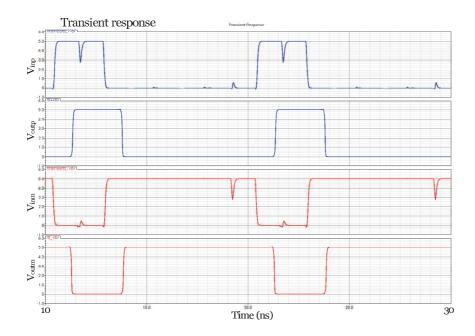

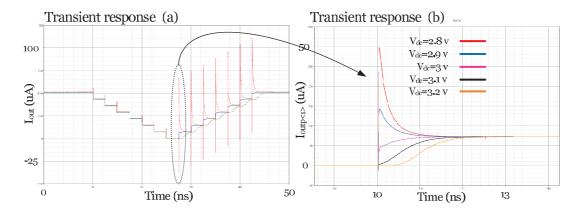

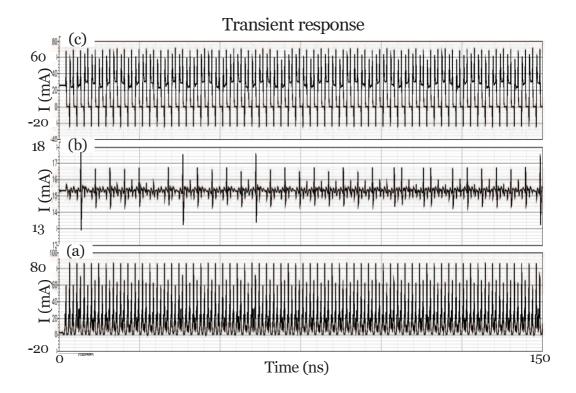

| 6.25 | Transient response of DC currents (a) and the output currents (b), the              |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | AC response (c) and the DC response of the VTOC output currents                     | 131 |

| 6.26 | Layout of the VTOC circuit                                                          | 131 |

| 6.27 | Transient response of the output voltage for the typical mean values                |     |

|      | (a), the first worst case (c) and the second worst case (d) and the AC              |     |

|      | response for the same cases for the unloaded CTOV                                   | 132 |

| 6.28 | Transient response of the input current(a), the output voltage (b) and              |     |

|      | the output current (c) of the loaded CTOV and its AC response (d)                   | 133 |

| 6.29 | Layout of the CTOV circuit                                                          | 134 |

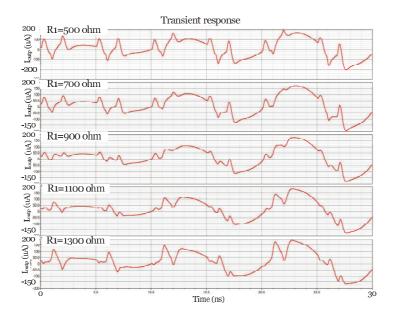

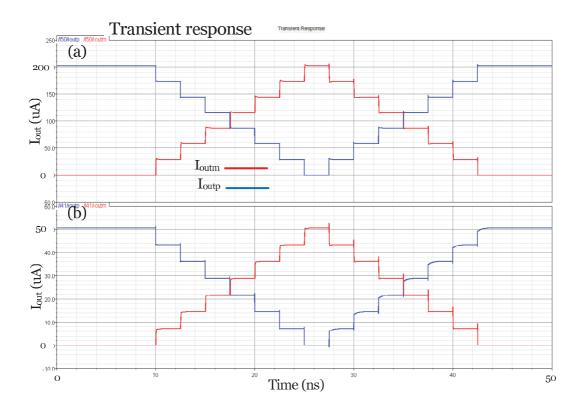

| 6.30 | CTOC output for different values of $R_1$                                           | 134 |

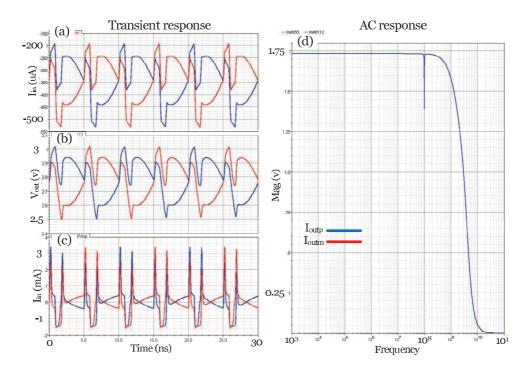

| 6.31 | Input current(a) and the output current (b) of CTOC for an input signal             |     |

|      | containing a pure sinusoidal current at 100 MHz combined with a pulse               |     |

|      | signal and the input current(c) and the output current (d) of CTOV for              |     |

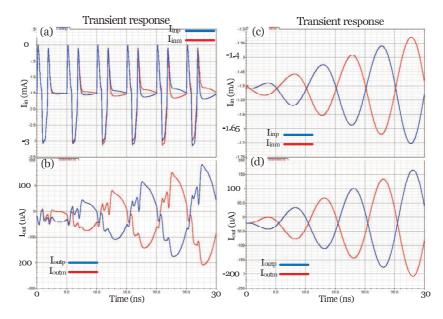

|      | a pure sinusoidal input at 100 MHz                                                  | 135 |

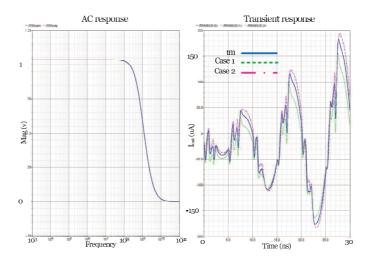

| 6.32 | AC response (a) and the transient response of the CTOC output                       | 136 |

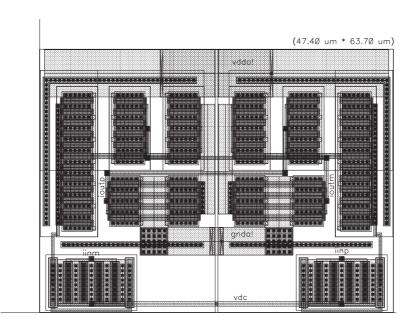

| 6.33 | Layout of the CTOC circuit                                                          | 136 |

| 6.34 | Linearity (a), the transient response (b) and the DC response (d) of the            |     |

|      | output voltage and the AC response (c) of the circuit                               | 138 |

| 6.35 | Layout of the amplifier circuit                                                     | 138 |

| 6.36 | Transient response of the comparators input, threshold voltages and the             |     |

|      | output of the comparators                                                           | 139 |

| 6.37 | Layout of the comparator circuit                                                    | 140 |

| 6.38 | Arrived clock signal, the input level and the output level of flip-flop $_{6}$      | 141 |

| 6.39 | Transient response of the delay input signal and the delay output                   | 142 |

| 6.40 | Input voltage, the clock signal and the DAC output for typical mean                 |     |

|      | values and the worst cases of the design                                            | 143 |

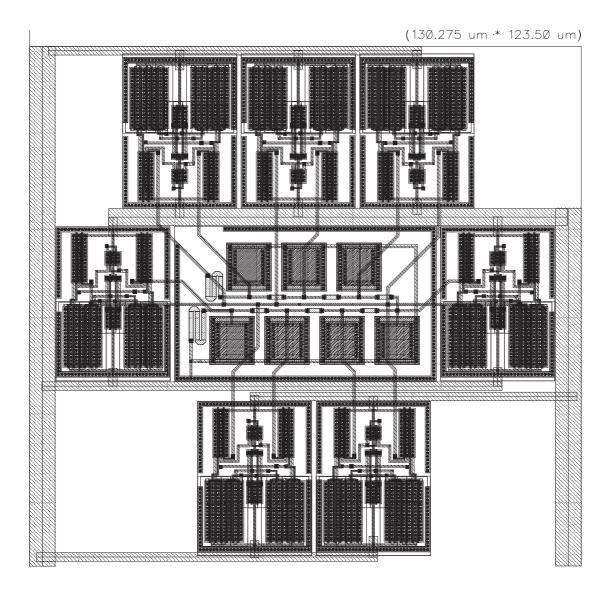

| 6.41 | Layout of the digital part of the ADC (being the rectifier system and               |     |

|      | the delay)                                                                          | 144 |

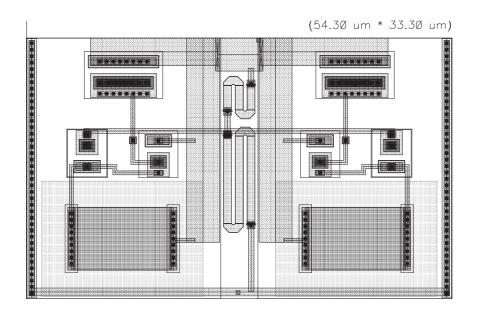

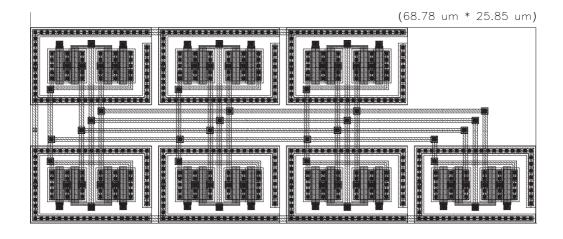

| 6.42 | Sensitivity of the rise-time of the output current of DAC <sub>2</sub> to $V_{dc2}$ | 145 |

| 6.43 | Transient response of the $DAC_1$ output (a) and the $DAC_2$ output                 | 146 |

| 6.44 | Layout of the DAC circuit                                                           | 146 |

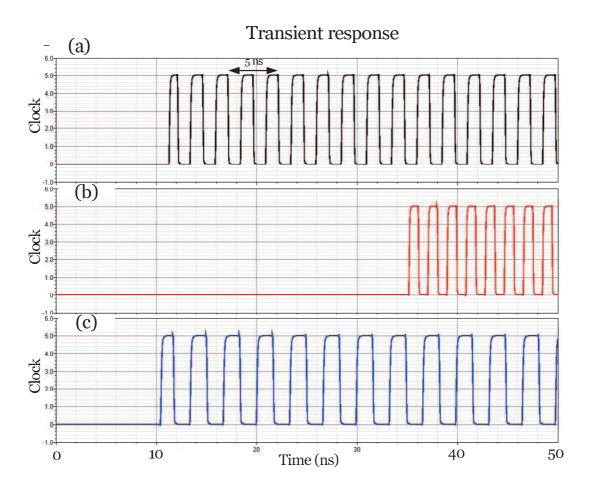

| 6.45 | Clock generator output for the typical mean values (a), the first worst             |     |

|      | case of the design (b) and the second one                                           | 147 |

| 6.46 | Layout of the clock circuit containing the clock generator and the clock              |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | tree                                                                                  | 148 |

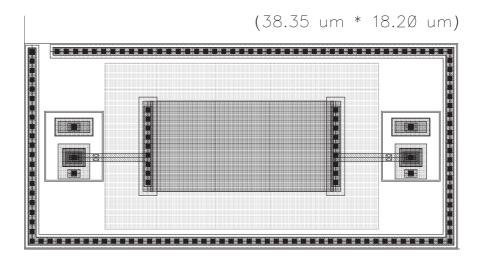

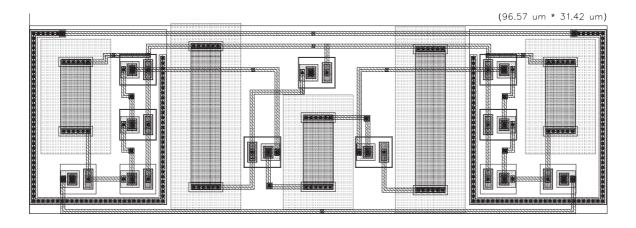

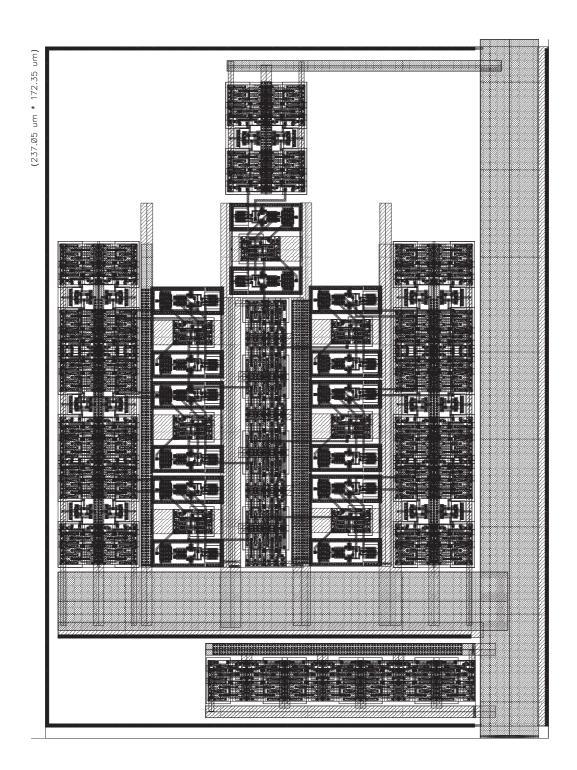

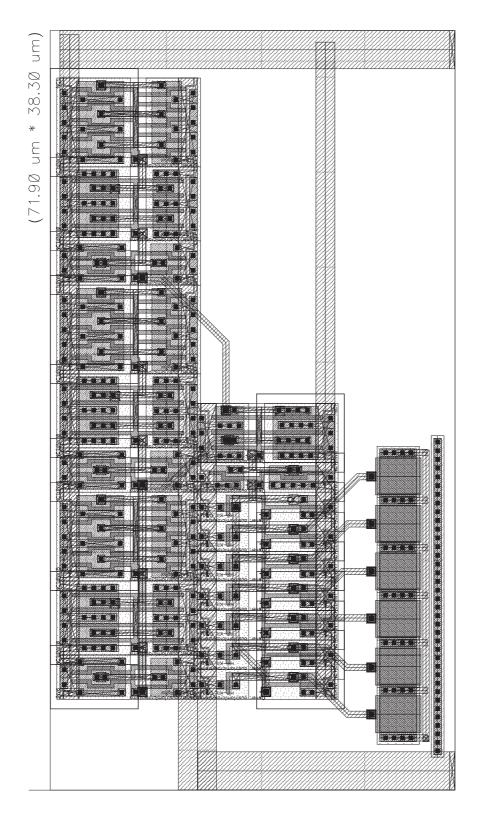

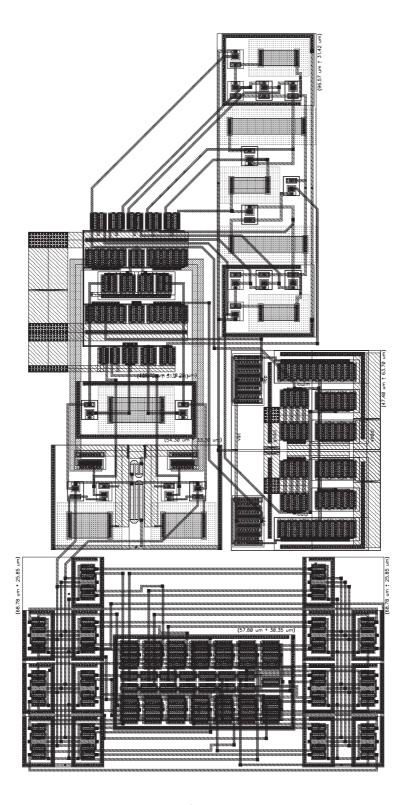

| 6.47 | Layout of the analog part (including the VTOC, the CTOV, the CTOC,                    |     |

|      | the DAC1, the DAC2 and the current mirrors) of the modulator                          | 150 |

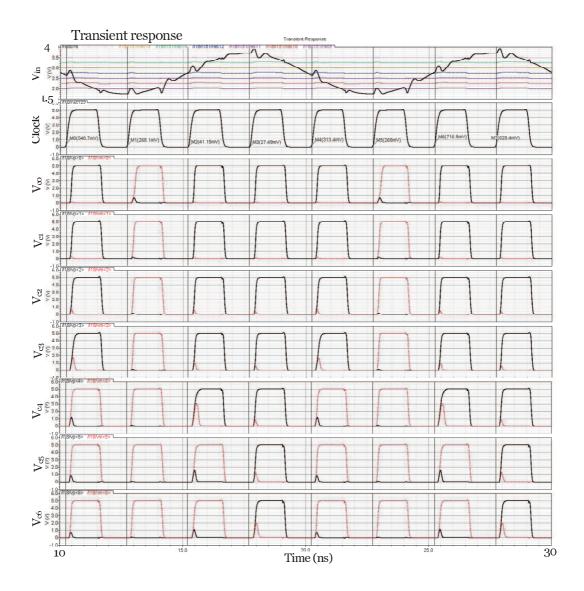

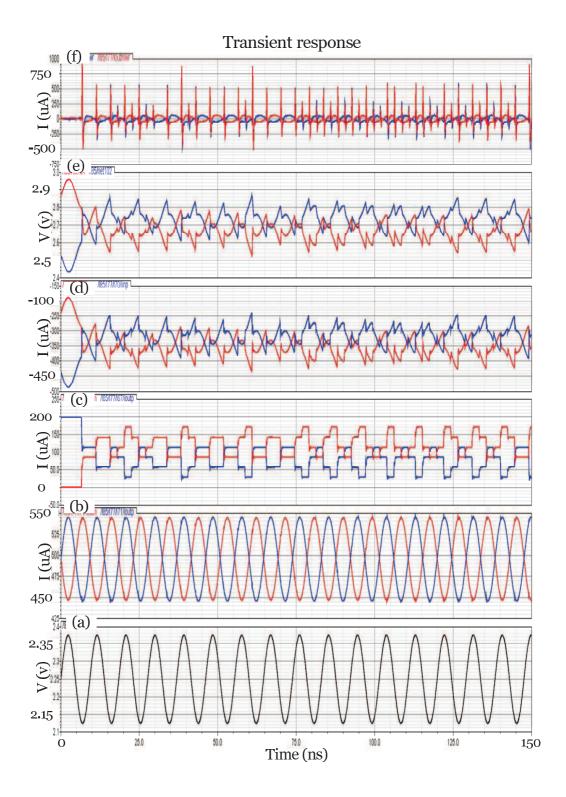

| 6.48 | Input voltage (a), the VTOC output (b), the first DAC output (c), the                 |     |

|      | CTOV input (d), the CTOV voltage output (e) and the CTOV current                      |     |

|      | output (f) for a layout-level simulation of the second-order $\Sigma\Delta$ modu-     |     |

|      | lator. Note that the blue signal corresponds to the positive differential             |     |

|      | signal and the red on corresponds to the negative one                                 | 151 |

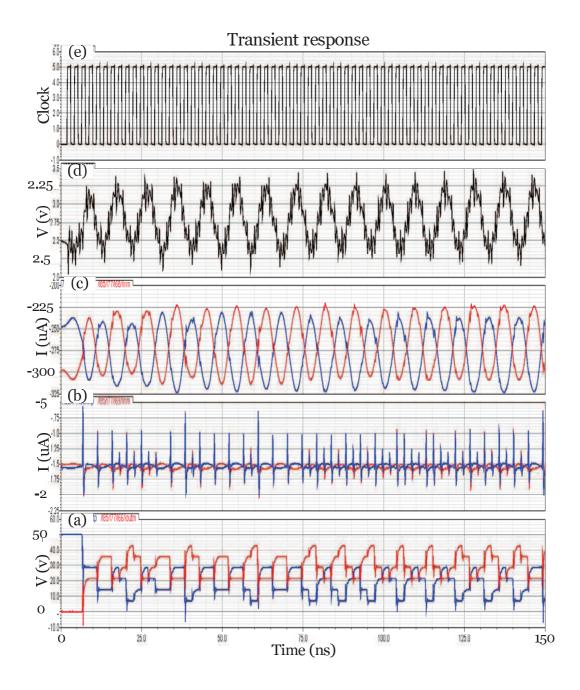

| 6.49 | Second DAC output (a), the CTOC input (b), the CTOC output (c), the                   |     |

|      | amplifier output (d) and the clock signal (e) for a layout-level simulation           |     |

|      | of the second-order $\Sigma\Delta$ modulator. Note that the blue signal corre-        |     |

|      | sponds to the positive differential signal and the red on corresponds to              |     |

|      | the negative one                                                                      | 152 |

| 6.50 | Consumed current by the comparators (a), the analog parts (b) and                     |     |

|      | the digital part (c) for a layout-level simulation of the second-order $\Sigma\Delta$ |     |

|      | $modulator. \ \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$  | 153 |

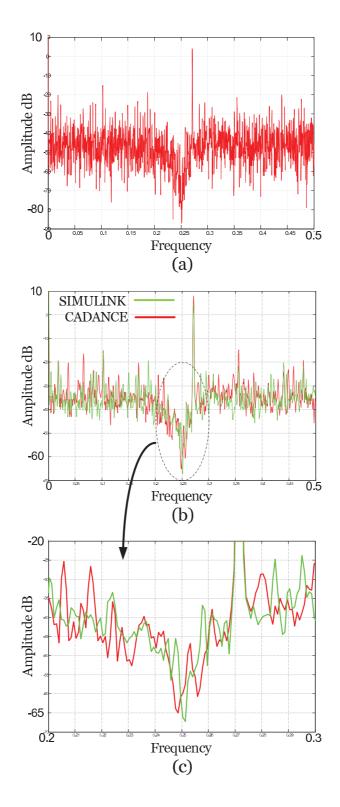

| 6.51 | Power spectrum density of the modulator output, simulated in layout-                  |     |

|      | level, for 4400 points of the simulation (a) compared with an ideal mod-              |     |

|      | ulator simulated by SIMULINK, where 1100 points are illustrated (b),                  |     |

|      | for the typical mean value                                                            | 155 |

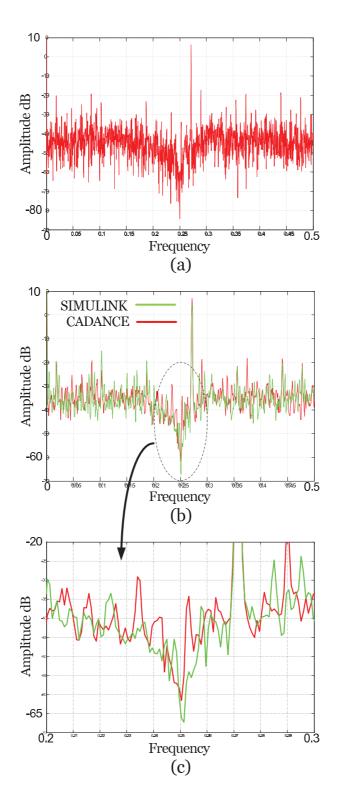

| 6.52 | Power spectrum density of the modulator output, simulated in layout-                  |     |

|      | level, for 4400 points of the simulation (a)compared with an ideal mod-               |     |

|      | ulator simulated by SIMULINK, where 1100 points are illustrated (b),                  |     |

|      | for the first worst case of the design                                                | 156 |

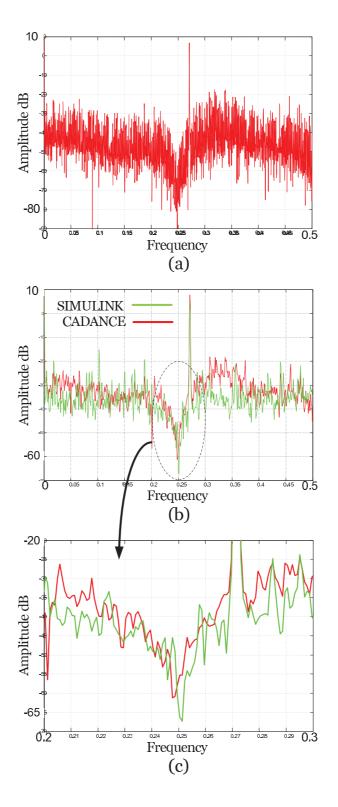

| 6.53 | Power spectrum density of the modulator output, simulated in layout-                  |     |

|      | level, for 4400 points of the simulation (a) compared with an ideal mod-              |     |

|      | ulator simulated by SIMULINK, where 1100 points are illustrated(b),                   |     |

|      | for the second worst case of the design                                               | 157 |

| A.1  | A second-order MSCL structure                                                         | 165 |

| A.2  | Equivalent model of a DT MSCL topology                                                | 166 |

# List of Tables

| 2.1 | Comparison various studies on CT modulators employing the classical        |     |

|-----|----------------------------------------------------------------------------|-----|

|     | resonators                                                                 | 31  |

| 4.1 | Employed LWR characteristics [131]                                         | 64  |

| 4.2 | State of the art of LWRs                                                   | 67  |

| 5.1 | Synthesized parameters for different modulator central frequencies         | 81  |

| 5.2 | Value of the modifiable parameters before and after optimization $\dots$ . | 93  |

| 6.1 | The worst combinations in the context of $\Sigma\Delta$ modulators         | 111 |

| 6.2 | Corresponding decimal and binary representation to the ADC output          | 119 |

| 6.3 | Comparison the in-band noise of the simulated modulator by CADENCE         |     |

|     | and that of the ideal modulator simulated by SIMUINK for OSR=64            | 154 |

## 1

## Outline

#### 1.1 Motivations

The new generations of mobile systems are not anymore a simple communication system limited to transmission of the human voice. Nowadays, the trend is to design multi-standard telecommunication systems able to process different standards. The integration of various applications (like GPS, TV, Bluetooth, etc) in mobile systems imposes new requirements including a larger frequency bandwidth to satisfy high data-rate transfer, and low power consumption for a longer autonomy. Thus highly-integrated, high-resolution and multi-standard systems are required [1].

The software radio solution was presented, for the first time, by J. Mitola [2], [3] to answer the new requirements of telecommunication markets. The concept of a software radio receiver is presented in figure 1.1. The idea is to replace the analog components by software to achieve a flexibility of reconfiguration without the need for material modification. For this aim, the Analog to Digital Converter (ADC) must be brought as close as possible to the antenna.

Figure 1.1: The principle of software radio solution.

Several issues must be overcome [4], [5]. Application Specific Integrated Circuits (ASICs) must be replaced by software implementation in DSPs. The system must support a large input dynamic range as there is no specification for applications. The main issue concerns the ADC functionality. A large band A/D converter to cover the frequency band of the integrated standards is required.

Parallelism is a solution to increase the ADC bandwidth without degrading its performance. The idea consists in putting ADCs in parallel where each of them process a portion of time or frequency of the input signal. In this context, because of wireless multi-function constraints, the employed converter must be able to work at high frequencies with high resolution. Moreover, the power consumption and the required chip area must be as small as possible.

Nyquist-rate ADCs are not able to meet the requirements of parallel structures. Pipeline ADCs [6], [7] and Approximations successive ADCs [8], [9] do not satisfy the demands in terms of speed. Flash ADCs [10], [11], are able to work at the required frequency but they have two major disadvantages in terms of chip area and power consumption. For an n-bits resolution Flash ADC,  $2^n - 1$  comparators are needed. As a result, high resolution Flash ADCs are big circuits with large power consumption because of the employed number of comparators. The number of comparators can be reduced by folding techniques [12], [13]. Indeed, during a ramp input signal, folding ADCs re-use the comparators multiple times. Although for a m-times n-bits resolution folding A/D the required number of comparators can be reduced from  $2^n - 1$  to  $\frac{2^n}{m}$ , they are still low-pass converters.

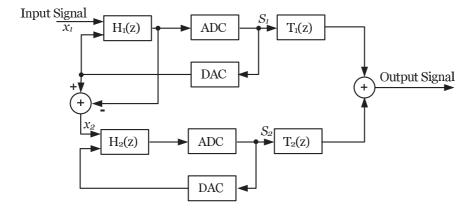

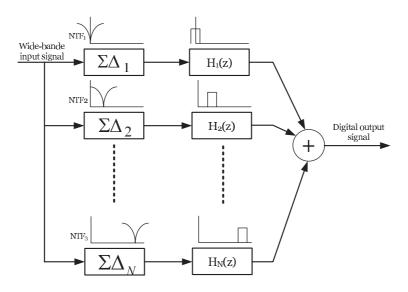

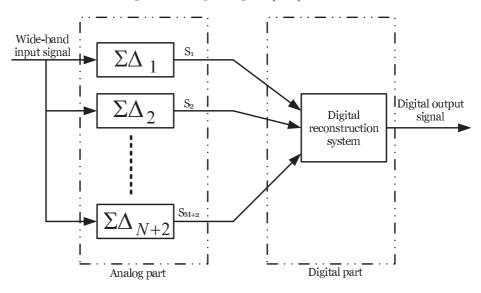

Continuous-Time (CT) Sigma-Delta ( $\Sigma\Delta$ ) modulator ADCs are good candidates to be employed in parallel systems. High-order  $\Sigma\Delta$  modulators are high resolution converters capable of working at high frequencies. Based on  $\Sigma\Delta$  modulators, various methods are proposed to implement a parallel ADC. Time Interleaved Sigma-Delta ( $TI\Sigma\Delta$ ) [14], Parallel Sigma-Delta ( $TI\Sigma\Delta$ ) [15], Frequency Band Decomposition (FBD) [16], [17] and Extended Frequency Band Decomposition (EFBD) [18] are the most well-known ones. A comparative study on the presented methods is done in [19].

The TI  $\Sigma\Delta$  solution has the lowest hardware complexity, but it has two main drawbacks. First, the whole frequency band between 0 Hz and the sampling frequency  $(f_s)$  is converted while the wanted signal band is generally a portion of the whole frequency band. Moreover, the TI solution is highly sensitive to both offset and gain mismatches of analog parameters resulting in distortion and unwanted tones.

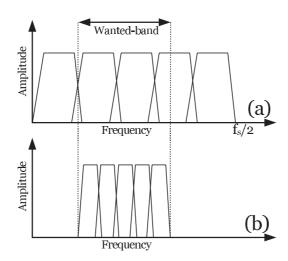

The FBD is another solution to widen the converter bandwidth by using N parallel band-pass modulators, where each modulator processes a portion of the frequency band of interest. Although analog mismatches may result in distortion of the FBD Signal Transfer Function (STF), they have no non-linear effects.

The EFBD is an improved system, compared with the FBD, based on the same principle. Two extra converters are employed to reduce the sensitivity of its STF to analog imperfections. This solution is vastly studied in [20].

Regardless of the chosen solution of parallelism, the used structure of  $\Sigma\Delta$  modulator must be able to provide the given resolution at high frequencies. Although high-order CT  $\Sigma\Delta$  modulators are mandatory to this end, they suffer seriously from instability issues and sensitivity to analog imperfections. A new methodology of design of high-order CT  $\Sigma\Delta$  modulators, compatible with the parallel context, is then required.

#### 1.2 Objectives and completed work

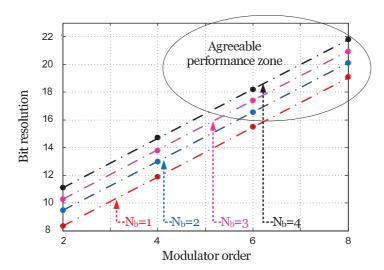

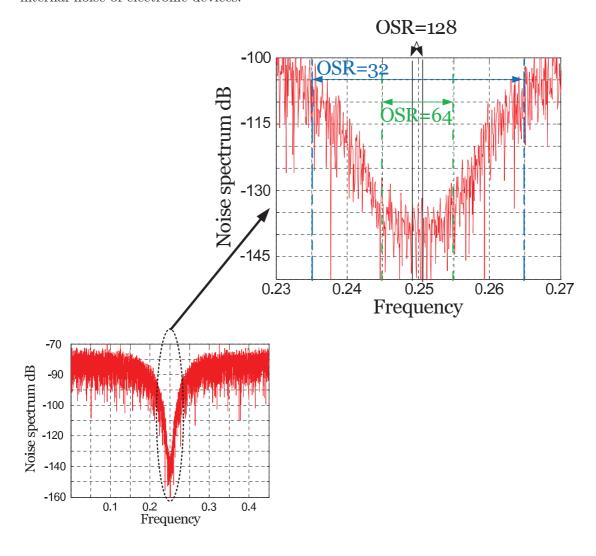

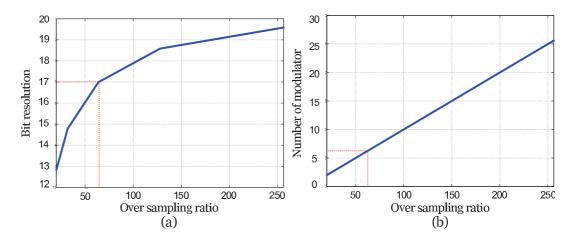

The design of an A/D converter able to provide a bit resolution equal to 16-bits across a frequency band between  $0.2f_s$  and  $0.3f_s$  accounting practical issues like analog imperfections is the main objective of the present work. Extracting the requirements of EFBD systems results in choosing  $6^{th}$ -order CT single-stage modulators. However in order to satisfy the requirements, two kinds of problems must be overcome which are the sensitivity of CT modulators to analog imperfections as well as the need of a resonator able to perform a high Q-factor.

To overcome the first problem, a new structure of  $6^{th}$ -order modulators based on weighted feedforward techniques is used. The main advantage is the possibility of establishing a robust stability regime by optimizing the value of few coefficients. Analog imperfections are also considered in the developed optimization method. On the other side the need of a high Q-factor leads us to use piezo-electric resonators. We will show that Lamb wave resonators are theoretically more interesting than other kinds of piezo-electric resonators. Finally the design of a second-order modulator is done to verify the reliability of the proposed solutions.

#### 1.3 Organization of the statement

In the **chapter II**, the basic concepts and the principle of the operation of  $\Sigma\Delta$  modulators are explained as well as different classes of them. The linear model of the quantizer allowing to apply linear analysis method on  $\Sigma\Delta$  modulators and various criterion to describe the performance of a modulator are also presented.

In the **chapter III**, the requirements of an EFBD system are studied and the characteristics of a proper modulator to attain the requirements are extracted. Afterward, the difficulties to implement the extracted characteristics are explained.

In the **chapter IV**, various sorts of resonators are studied in order to chose the most compatible with requirements. Lamb wave resonators being theoretically the most convenient have also some disadvantages. The relative advantage and disadvantages of them are studied and some solutions to overcome the major issues are then proposed.

In the **chapter V**, the major issues of high-order CT  $\Sigma\Delta$  modulators are studied. It is shown that a new methodology of design is required in order to establish a robust stability regime while maintaining the resolution. To this end, a new structure of  $6^{th}$ -order modulators based on weighted feedforward techniques is proposed. Although a simple synthesis of an equivalent DT modulator with the proposed structure does not satisfy the demands, it is possible to attain the objectives relying on the flexibility of this structure. Then an optimization method on the modifiable parameters of this structure is developed. In order to be reliable in practice, analog imperfections are considered in system-level.

In the **chapter VI**, the design of a second-order modulator in layout-level with AMS Bi-CMOS  $0.35\mu m$  technology is explained. Although the theoretical work of the present work is focused on the design of  $6^{th}$ -order modulators, the design of a second-order modulator is considered because of missing informations about practical behavior of Lamb wave resonators. Indeed, this design is done for the aim of testing the compatibility of Lamb wave resonators with the loop of  $\Sigma\Delta$  modulators.

The **conclusion** makes an overall review on the done works as well as presenting the perspectives to improve and accomplish the studied targets.

# Introduction

#### 2.1 Basic concepts

#### 2.1.1 Analog-to-digital conversion

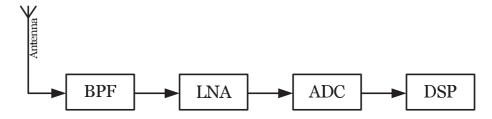

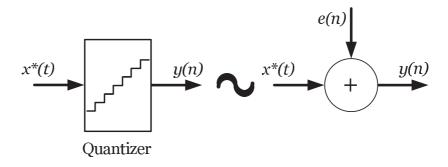

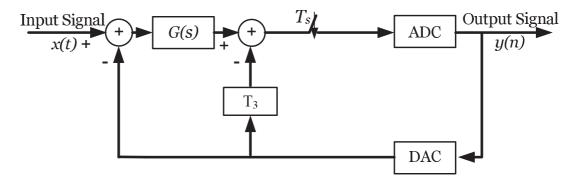

Analog-to-digital conversion is a process to convert a continuous-time signal (x(t)) into a multi-level or digital signal (y(n)) as it is shown in figure 2.1.

Figure 2.1: Analog-to-digital conversion.

The time index n of a digital signal (y(n)) is an integer number. The sampler output is a Discrete-Time (DT) signal presented by  $x^*(t)$  where t is equal to  $nT_s$  and  $T_s$  is the sampling period equal to  $\frac{1}{f_s}$  where  $f_s$  is the sampling frequency. The relation between x(t) and  $x^*(t)$  is as follows:

$$x^*(t) = \sum_{n=0}^{\infty} x(t)\delta(t - nT_s), \qquad (2.1)$$

where  $\delta(t)$  is:

$$\begin{cases} 1, & t = 0 \\ 0, & \text{elsewhere} \end{cases}$$

(2.2)

An ADC transforms first the CT input signal (x(t)) into a DT signal  $(x^*(t))$ . Afterward, each sample is approximated by a quantizer to transform  $x^*(t)$  into a digital signal (y(n)) containing a sequence of finite precision or quantized samples.

#### 2.1.2 Quantization error

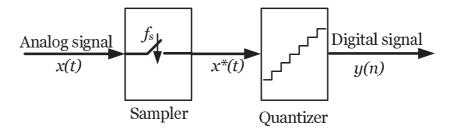

The quantizer rounds the input signal  $(x^*(t))$  to the nearest level, as illustrated in figure 2.2.

Figure 2.2: Quantization principle.

Quantization introduces an error signal that depends on how the signal is being approximated. This error, called the quantization error (e(n)), is on the order of one Least-Significant-Bit (LSB) in amplitude [21]. The quantization error is in general small compared with a full amplitude input signal range but it becomes relatively larger when the input signal gets smaller. The relation between e(n),  $x^*(t)$  and y(n) is given by:

$$e(n) = y(n) - x^*(t).$$

(2.3)

Although the quantizer is a non-linear system and e(n) is an unknown function, various approximate linear models of the quantizer are proposed to recognize e(n) and

to be able to apply the classical methods of analysis to systems containing a quantizer. These models are all based on the asymptotic results of Bennet [22] or the exact results of Widrow [23] and Sripad [24].

#### 2.1.2.1 Model of Bennet

Bennet describes the conditions under which the quantization error can be modeled by white noise. Assuming a B-bits quantizer, the number of available levels to quantize  $x^*(t)$  is equal to  $2^B$ . Thus, the interval between successive levels (q) is given by:

$$q = \frac{1}{2^B - 1}. (2.4)$$

In [22], it is shown that for the following conditions:

- 1. The input signal does not exceed the dynamic zone of the quantizer.

- 2. The quantizer number of bits (B) is sufficiently large.

- 3. The amplitude of the input signal is large compared with LSB.

e(n) is a random quantity in each quantization step with equal probability and the variance of e(n), the noise power  $(\sigma_e^2)$ , can be calculated as follows [25]:

$$\sigma_e^2 = \frac{1}{q} \int_{-q/2}^{q/2} e^2 \, \mathrm{d}e = \frac{q^2}{12} = \frac{2^{-2B}}{3}.$$

(2.5)

As a result, the quantizer can be replaced by its linear model presented in figure 2.3.

Figure 2.3: Quantizer linear model.

#### 2. INTRODUCTION

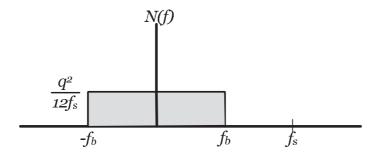

In analog-to-digital conversion since the noise power is spread over the entire frequency range equally, the level of the noise power spectral density can be expressed as follows:

$$N(f) = \frac{q^2}{12f_s} = \frac{2^{-2B}}{3f_s}. (2.6)$$

The noise level is a function of the quantizer number of bits and the sampling frequency. It becomes smaller when  $f_s$  or B get larger. Figure 2.4 shows the spectrum of the quantization noise in the signal frequency band  $[-f_b, f_b]$ .

Figure 2.4: Noise spectrum of the quantization error.

#### 2.1.2.2 Low-order quantizer

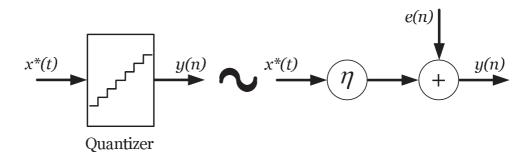

The linear model of the quantizer is indispensable to analyze  $\Sigma\Delta$  modulators [26]. The Noise Transfer Function (NTF) and the STF of  $\Sigma\Delta$  modulators are found through this model. Although the model of Bennet is valid in a high-order  $\Sigma\Delta$  modulator loop regardless of the quantizer number of bits, for low-order modulators this model is reliable when the quantizer number of bits is sufficiently large. The quantization noise of a low-order (second or fourth) modulator containing a low-order quantizer (B=1 or 2), does not have an equal probability for each quantization step [27], [28], [29]. It should be noted that in a  $\Sigma\Delta$  modulator loop, the quantizer number of bits is in general small because of practical considerations including chip area and power consumption.

The linear model may be modified, as it is shown in figure 2.5, to improve the approximation of low-order quantizers. The quantizer is modeled by a gain stage  $(\eta)$  associated with an additive white noise [30], [31], [32], [33], [34].

Figure 2.5: The linear model of a low-order quantizer.

Although  $\eta$  is almost equal to one for high-order quantizers, for low-order ones its value depends on the modulator structure and on the amplitude of the input signal. Therefore, it is a variable number which is difficult to be estimated. In order to release the analysis of the modulator from  $\eta$ , one may use a dither signal [35] which adds to the system an uncorrelated noise to minimize the correlation between the input signal and the quantization error. The dither must be small enough to not deteriorate the modulator performance and large enough to result in a whit noise. Other models of low-order quantizers are also proposed in [36], [37].

## 2.1.3 Oversampling and decimation

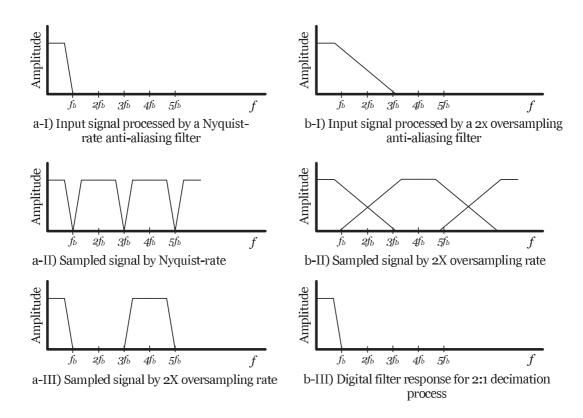

Regarding the sampling frequency, the ADCs may be categorized into Nyquist-rate ones and oversampling ones. The quantization process is different from one to another. Nyquist-rate ADCs sample the input signal with the minimum sampling rate required to avoid aliasing while oversampling ADCs use a sampling rate significantly larger than the Nyquist-rate. Afterward, a digital decimation filter is employed to reduce the signal rate to the Nyquist-rate.

Regardless of the quantization process, oversampling eases the design of the antialiasing filter. Assuming a typical signal with a bandwidth equal to  $f_b$ , figure 2.6.a compares the anti-aliasing filter required for a Nyquist-rate sampled signal  $(f_s = 2f_b)$ and a two-times oversampled signal  $(f_s = 4f_b)$ .

The anti-aliasing filter of Nyquist-rate ADCs requires a flat response with no phase distortion over the frequency band of interest. Moreover, in order to prevent signal distortion because of aliasing, all signals above  $f_b$  must be attenuated, for example, by at least 96-dB to achieve 16-bits of dynamic resolution. It should be noted that these

Figure 2.6: Comparison the Nyquist-rate anti-aliasing filter with two-times oversampling anti-aliasing filter (a), the quantization process of a 2x oversampling ADC(b).

requirements are tough to meet with an analog low-pass filter. Considering the same signal sampled at  $4f_b$ , the anti-aliasing filter must only present a flat performance up to  $f_b$  and eliminate signals above  $3f_b$  (figure 2.6.a). Clearly, the design of an oversampled anti-aliasing filter is much easier than a Nyquist-rate one. However, since the sampling rate is equal  $4f_b$ , a sample rate reduction filter is required but it is implemented in digital domain as opposed to anti-aliasing filters which are implemented with analog circuitry.

The two-times oversampling can be extended to N-times oversampling converters. Considering a full precision quantizer, the total noise power of oversampling converters and Nyquist-rate ones are the same and they are given by equation 2.5. However, the difference is in the power of the residual noise in the bandwidth of interest. The residual noise power is given by:

$$N_b = \int_{-f_b}^{f_b} N(f) \ df = \frac{2f_b q^2}{12f_s}.$$

(2.7)

The in-band noise of an oversampling converter is much smaller than the in-band noise of Nyquist-rate converters when  $f_s$  is much larger than  $f_b$ . Reducing the in-band noise is completed by using a decimation filter to provide increased resolution. Figure 2.7 compares the level of the in-band noise of a Nyquist-rate ADC with a two-times and a three-times oversampling ADCs.

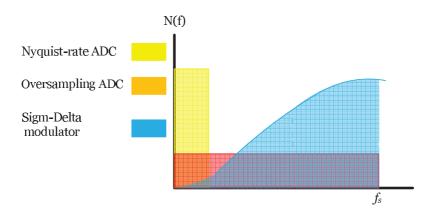

**Figure 2.7:** Comparison the in-band noise of Nyquist-rate ADCs and that of oversampling ADCs.

## 2.1.4 Noise shaping

Although the oversampling process increases the ADC resolution, the main disadvantage is the linear relation between the noise level and  $\frac{1}{f_s}$ . Considering the technology limits, it is not possible to increase arbitrarily the sampling frequency. Therefore, the resolution of oversampling ADCs is limited by technology. In order to improve the resolution, oversampling ADCs must be associated with a noise shaping system. The idea consists in rejecting the quantization noise from the frequency band of interest to out-of-band frequencies.

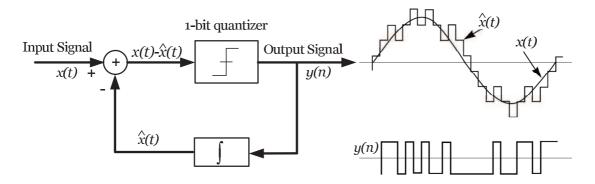

## 2.1.4.1 Delta conversion

Using feedbacks to reject the in-band noise has been introduced in Delta modulation for the first time [38]. Delta modulation is based on quantizing the change in the signal

from sample to sample rather than the absolute value of the signal at each sample. The error term  $(x(t) - \hat{x}(t))$ , in each sample, is quantized and used to make the next error term (figure 2.8).

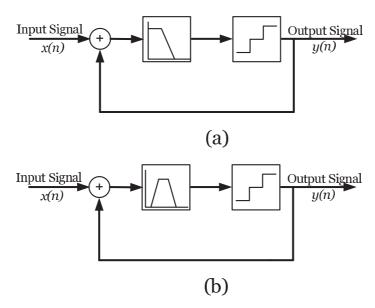

Figure 2.8: Delta modulation principle.

The error signal is smoothed by a low-pass filter. As a result, for a high frequency input signal or a high speed rise of the input signal, the modulator is overloaded. Then, the performance of Delta modulation is limited in terms of speed.

## 2.1.4.2 Sigma-delta conversion

The arrangement shown in figure 2.9 is called a  $\Sigma\Delta$  modulator [39]. The name  $\Sigma\Delta$

Figure 2.9:  $\Sigma\Delta$  modulation.

modulator comes from putting the integrator ( $\Sigma$ ) in front of the delta modulator.  $\Sigma\Delta$  modulation is based on two beneficent function being the oversampling and the noise shaping [40], [41], [42], [43].

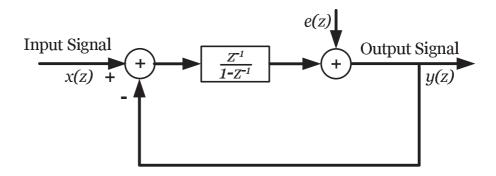

A first-order low-pass DT  $\Sigma\Delta$  modulator is chosen for explaining the noise shaping principle. Note that the modulator order corresponds to the number of employed integrators in low-pass context and two-times of the number of employed resonators in band-pass context. Figure 2.10 shows the linear model of the first-order low-pass modulator.

Figure 2.10: Linear model of a first-order low-pass DT  $\Sigma\Delta$  modulator.

The system equation (the relation between y(z), x(z) and e(z)) is:

$$y(z) = (x(z) - y(z))\frac{z^{-1}}{1 - z^{-1}} + e(z).$$

(2.8)

This results to calculate the STF and the NTF as follows:

$$\begin{cases}

STF = \frac{y(z)}{x(z)} = z^{-1}, \\

NTF = \frac{y(z)}{e(z)} = \frac{1-z^{-1}}{z^{-1}}.

\end{cases}$$

(2.9)

Since the STF is a delay function, the input signal is left unchanged as long as its frequency content does not exceed the filter cut-off frequency. On the other side, the NTF is a high-pass filter and rejects the noise into a higher frequency band. A  $\Sigma\Delta$  modulator generates an output which can be averaged over several input sample periods to produce a very precise result. The averaging is performed by decimation filters following the modulator. The noise spectrum of a Nyquist-rate ADC, an oversampling ADC and a first-order low-pass  $\Sigma\Delta$  modulator are compared in figure 2.11.

Figure 2.11: Comparison the noise spectrum of a Nyquist-rate ADC, an oversampling ADC and a first-order low-pass  $\Sigma\Delta$  modulator.

## 2.1.5 From low-pass to band-pass conversion

Converting a high frequency signal requires a corresponding band-pass modulator. Indeed, the modulator central frequency (at which the in-band noise is minimal) must match the input signal frequency. Figure 2.12 compares the structure of a low-pass and a band-pass  $\Sigma\Delta$  modulator. In DT domain, a band-pass modulator is obtained

Figure 2.12: Low-pass modulator (a) and band-pass modulator (b) in DT domain.

from a low-pass one by replacing the integrators with resonators. Shifting the low-pass

modulator to the desired frequency can be done by the transfer given by [44], [46]:

$$z^{-1} \iff z^{-1} \frac{z^{-1} - \frac{p}{2}}{1 - \frac{p}{2}z^{-1}},$$

(2.10)

where p determines the desired central frequency  $(f_c)$  and is given by:

$$p = 2\cos\left(2\pi \frac{f_c}{f_s}\right). \tag{2.11}$$

The resonator obtained from an integrator through equation 2.10 is given by:

$$\frac{z^{-1}}{1-z^{-1}} \iff \frac{\frac{p}{2}z^{-1}-z^{-2}}{1-pz^{-1}+z^{-2}}.$$

(2.12)

The properties of the low-pass modulator in terms of stability and resolution are conserved after the transfer.

## 2.2 Band-pass continuous-time sigma-delta modulator

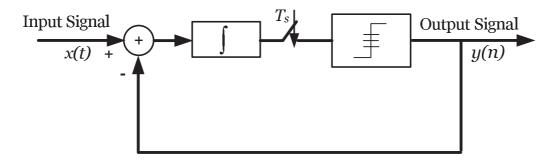

## 2.2.1 Discrete-time or continuous time

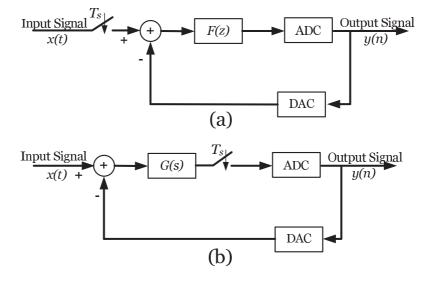

The structure of a CT  $\Sigma\Delta$  modulator is compared with that of a DT modulator in figure 2.13. The input signal of DT modulators is in discrete-time domain (already

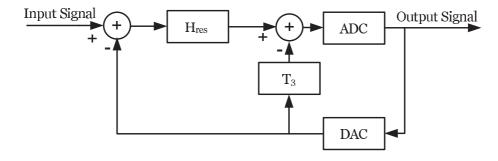

Figure 2.13: DT  $\Sigma\Delta$  modulator structure (a), CT  $\Sigma\Delta$  modulator structure (b).

sampled). Therefore, the modulator filters are also implemented in DT domain. On

#### 2. INTRODUCTION

the contrary, sampling is done before the quantizer in CT modulators and the modulator filters are implemented in CT domain. DT filters are generally designed by switched capacitor techniques. Although switched capacitor techniques are advantageous in terms of flexibility of design and precision, their speed cannot exceed from tens of MHz because of the limited bandwidth of the required operational amplifiers [47]. In addition, the speed of the charge transmission of the commutators is also limited. Another disadvantage which results in limiting the speed of DT modulators, is the sampling noise which is combined with the input signal while in CT modulators the sampling noise becomes a part of the quantization noise and is rejected into out-of-band frequencies by the NTF [48].

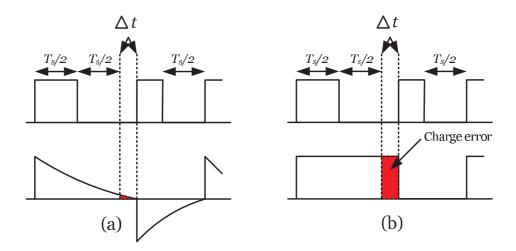

CT modulators are able to perform at high frequencies because of CT filter techniques [49]. It is generally feasible to clock CT  $\Sigma\Delta$  modulators at much higher frequencies than DT  $\Sigma\Delta$  modulators. Additionally, sampling in the modulator loop results in diminishing the thermal noise in the modulator frequency band [50]. Furthermore, CT analog circuits are less demanding than their DT counterparts in terms of power consumption. However, they are not an ideal solution. The design of Digital to Analog Converter (DAC) in the feedback path of CT modulators is difficult because of the sensitivity of the modulator performance to the DAC functionality. Compared with DT modulators, CT modulators are sensitive to clock jitter defined as the time variation or the peak-to-peak displacement ( $\Delta t$ ) of the clock signal [51]. The feedback signal of DT modulators has an exponential form and the charge transmission is almost completed at the clock rise-time (figure 2.14.a). On the contrary, DAC output of CT modulators is a rectangular signal (figure 2.14.b). Therefore, clock jitter results in losing an important quantity of charge.

In addition, CT modulators are sensitive to the loop delay. This delay is the sum of the delays produced by all the analog and digital components of the modulator loop. In chapter IV, it is shown that modifying the loop delay changes the NTF poles position. A non-optimized loop delay may bring the NTF poles out of the unit circle and make the system unstable. Nevertheless, the increasing demand for high-speed high-resolution and low-consumption analog-to-digital conversion can be satisfied only by using CT  $\Sigma\Delta$  modulators.

Figure 2.14: Influence of clock jitter on charge loss in DT (a) and CT (b) modulators.

## 2.2.2 From discrete-time to continuous-time

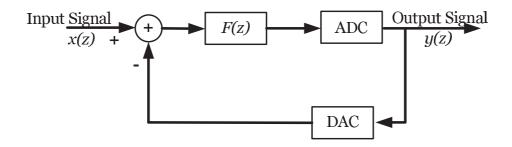

There exist various methods and toolboxes to find the global filter of a DT modulator corresponding to demands. Indeed, the design of DT modulators has progressed and the design of CT modulators may lean to this progress through the synthesis of CT modulators from their DT counterparts. However, the problem is not a simple transform from z domain (F(z)) to s domain (G(s)). The modulators in figure 2.13 are equivalent if they produce the same output for the same input at each sampling period.

As a result, the functionality of the ADC and the DAC should be taken into account in the transformation in order to ensure the equivalence between DT and CT circuits. The parameters to be considered include the internal delays and the non-linearity of the ADC and the DAC as well as the rise time and the form of the ADC+DAC output [52], [53]. An approach with these objectives is presented in [54]. The delays introduced by both the DAC and the ADC and the shape of the DAC output signal are taken into account. Standard tools available in symbolic calculation softwares, such as Laplace and z-transforms, are employed. This approach is put in equation as follows:

$$F(z) = (1 - z^{-1}) Z_T \{ L^{-1}[G(s)B(s)] \} + \underbrace{\sum_{k} a_k z^{-k}}_{D(z)},$$

(2.13)

where  $L^{-1}$  denotes the inverse Laplace transform,  $Z_T$  is the z-transform at the sampling period  $(T_s)$  and B(s) denotes the delay and the non-ideality parts of DAC and ADC

functionalities. The response of the DAC and the ADC, considered as a single block, is modeled by figure 2.15.

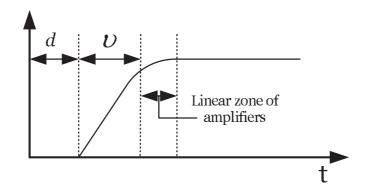

Figure 2.15: Model of the response of the ADC+DAC.

In this model, the speed of the ADC+DAC is described by the rise time  $(\nu)$  and the loop delay is described by d. For the sake of the simplicity, the linear zone of the employed amplifier resulting in a non-linear zone of the ADC+DAC response is neglected. Then B(s) is given by:

$$B(s) = \frac{e^{-ds} - e^{-(d+\nu)s}}{\nu s}. (2.14)$$

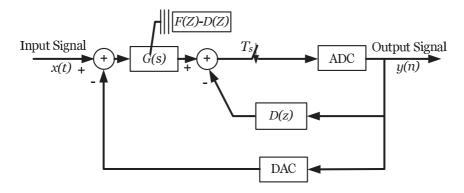

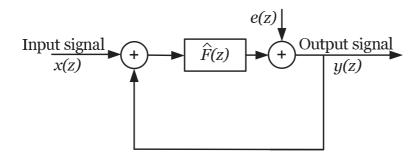

D(z) is added for ensuring an exact solution of equation 2.13. Indeed, without D(z), it is possible that when  $d \neq 0$  or  $\nu \neq 0$ , equation 2.13 has no exact solution. Implementing D(z) demands some system modifications. Figure 2.16 shows a possible implementation when the ADC delay is sufficiently small.

Figure 2.16: A possible implementation of equation 2.13.

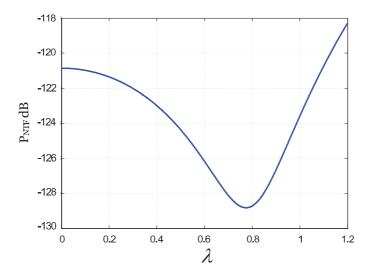

When the internal delay of the ADC is larger than  $1T_s$  (which is usually the case), not all the terms of D(z), especially the low-order terms, can be implemented through the ADC output. Therefore, the topology of figure 2.16 is useless in practice. New implementation methods are required when the ADC delay is large. In [54] an alternative topology is proposed. This topology is shown in figure 2.17.

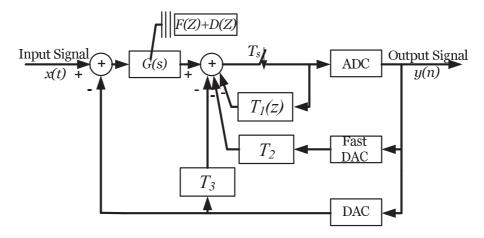

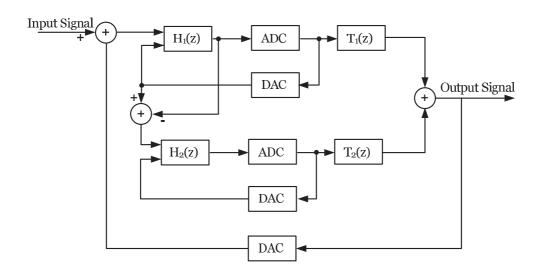

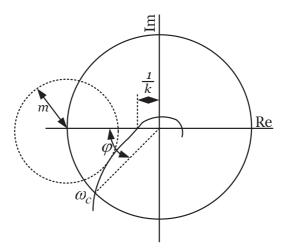

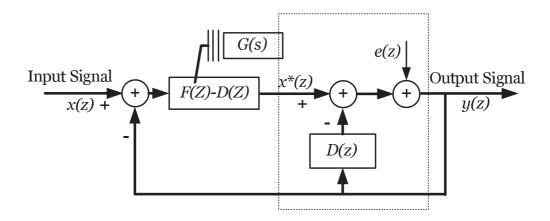

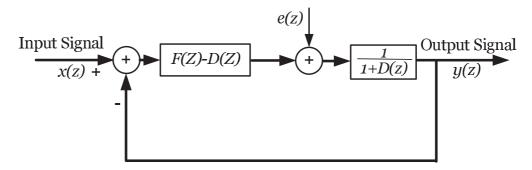

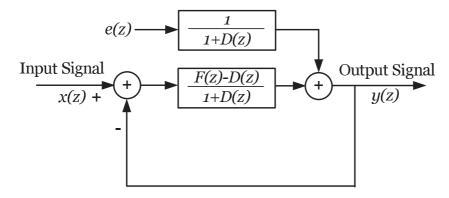

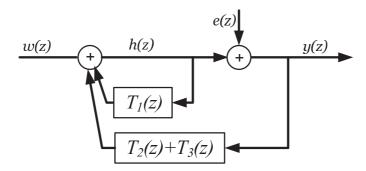

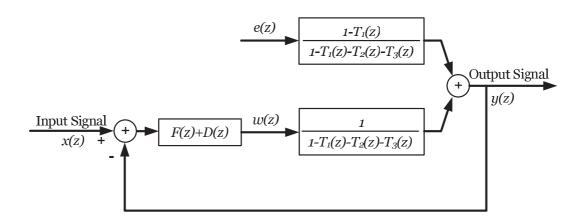

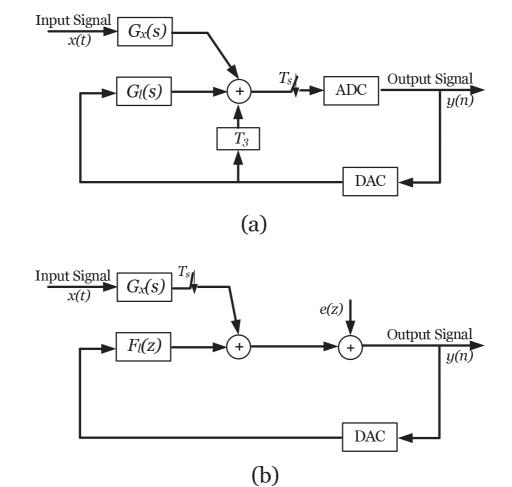

**Figure 2.17:** Proposed topology in [54] for implementing D(z).

As it is shown, the terms of D(z) are implemented in three ways:

- 1.  $T_1(z)$ : The first terms of D(z), corresponding to a delay value less than the ADC delay, are implemented through the sampler output to avoid the ADC delay.

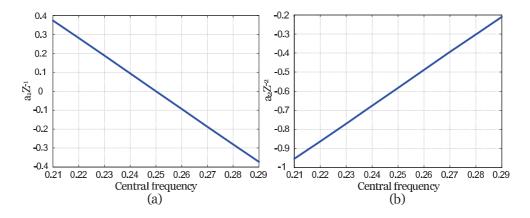

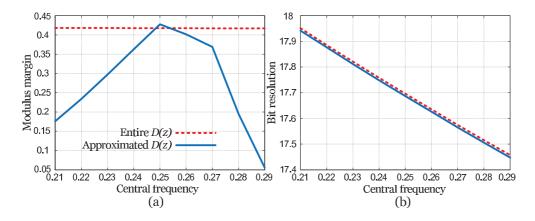

- 2.  $T_2$ : The intermediate terms of D(z), corresponding to a delay value larger than the ADC delay but less than the loop delay (ADC+DAC delay), may be implemented by a fast DAC through the ADC output.