# **Etude et validation de boucles d'asservissement permettant le contrôle avancé des procédés en microélectronique : Application à l'étape d'isolation par tranchées peu profondes en technologie CMOS.**

Djaffar Belharet

## ► To cite this version:

Djaffar Belharet. Etude et validation de boucles d'asservissement permettant le contrôle avancé des procédés en microélectronique : Application à l'étape d'isolation par tranchées peu profondes en technologie CMOS.. Micro et nanotechnologies/Microélectronique. Ecole Nationale Supérieure des Mines de Saint-Etienne, 2009. Français. NNT: . tel-00467446

**HAL Id: tel-00467446**

<https://theses.hal.science/tel-00467446>

Submitted on 26 Mar 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre : **515M**

**THESE**

présentée par

*Djaffar BELHARET*

Pour obtenir le grade de Docteur

de l'Ecole Nationale Supérieure des Mines de Saint-Etienne

Spécialité : MICROELECTRONIQUE

*Etude et validation de boucles d'asservissement permettant le contrôle avancé des procédés en microélectronique : Application à l'étape d'isolation par tranchées peu profondes en technologie CMOS.*

Soutenue à Gardanne le 26 Février 2009

Membres du jury

Jean Pierre LANDESMAN

Bernard LEROY

Jacques PINATON

Agnès ROUSSY

Philippe COLLOT

Professeur/ Institut des matériaux Jean Rouxel, Nantes

Docteur d'Etat

Ingénieur/ ST Microelectronics

Maître-Assistante/ Ecole des Mines de Saint- Etienne

Professeur / Ecole des Mines de Saint- Etienne

*A mes parents*

## **Remerciements**

Les travaux de cette thèse sont l'œuvre d'une collaboration entre le CMP-GC (EMSE) et ST Microelectronics de Rousset. Dans un premier temps, je remercie Philippe COLLOT, professeur à l'école des Mines de Saint-Etienne et directeur du CMP-GC pour m'avoir accueilli et encadré au cours de ces années de thèse. J'exprime aussi toute ma reconnaissance à Monsieur Stéphane DAUZERE-PEREZ, professeur à l'école des Mines de Saint-Etienne de m'avoir intégré dans le groupe SFL (Sciences de fabrication et logistique). J'adresse également mes remerciements à Mme Agnès Roussy, Maître assistante à l'école des mines de Saint-Etienne pour m'avoir conseillé et co-encadré au cours de ces années de thèse.

Toute ma gratitude va également à mes deux rapporteurs de thèse. Merci à M. Jean Pierre LANDESMAN, Professeur à l'institut des matériaux Jean Rouxel (Nantes) d'avoir accepté de présider mon jury de thèse et de juger mes travaux de recherches. Je veux également remercier M. Bernard LEROY pour avoir accepté les charges de rapporteur et pour ses innombrables remarques constructives.

Je n'oublie pas le personnel de ST Microelectronics, et je tiens à souligner que ces résultats ne seraient pas dans ce manuscrit sans leur précieuse assistance. Je remercie M. Jacques PINATON, ingénieur à ST Microelectronics pour ses conseils, ses encouragements, son aide et toute la confiance qu'il m'a accordée. J'adresse aussi mes remerciements à M. Pascal FORNARA pour avoir co-encadré ma thèse et pour avoir partagé son savoir-faire technologique. Merci à toutes les personnes qui m'ont aidé à réaliser mes travaux expérimentaux et en particulier à Jérôme CIRES (gravure humide), Lydie le PREVOST (PECVD) et toute l'équipe du process CMP. Je n'oublie pas l'équipe de métrologie et en particulier Geslaine et Emilienne et Sébastien. Je remercie également Damien PALMIER pour ses conseils et son aide. Merci à toute l'équipe de process control et en particulier à Franck (extraction des données par SAS) et Laurent (FDC).

Je ne peux pas oublier de remercier M.me Isabelle CONSTANT, qui m'a co-encadré en début de thèse et qui travaille maintenant dans le milieu industriel. De la même façon, je remercie M. Christian RIVERO, ingénieur à ST Microelectronics pour toute son aide et ses conseils. Je veux également remercier tous les anciens doctorants du CMP-GC (Stéphanie, Moustafa, Cathy, Said...) ainsi que tout le personnel actuel de l'équipe SFL (Bernard, Pierre, Claude, Nabil...) et du CMP-GC en général et en particulier M.me Véronique VILLAREAL.

Et enfin, je remercie toute ma famille qui m'a soutenu pendant toute cette période. Ce soutien a toujours été pour moi une source intarissable de motivation. Merci beaucoup papa et maman, malgré la distance qui nous sépare, vous êtes toujours dans mon cœur. Je remercie également mes frère et sœurs pour leurs encouragements et leur soutien permanent. Merci à Nordine, sa femme et Mahdi (l'aixois).

# TABLE DES MATIERES

|                                                                                   |     |

|-----------------------------------------------------------------------------------|-----|

| <b>Table des matières</b>                                                         | iii |

| <b>Liste des figures</b>                                                          | vi  |

| <b>Liste des tableaux</b>                                                         | xii |

| <b>Liste des abréviations</b>                                                     | xii |

| <b>Introduction générale</b>                                                      | 1   |

| <b>1 Le contrôle des procédés</b>                                                 | 6   |

| 1.1 Les techniques de contrôle.....                                               | 7   |

| 1.1.1 Les méthodes de contrôle .....                                              | 7   |

| 1.1.2 Les enjeux du contrôle des procédés face aux nouvelles technologies.....    | 8   |

| 1.1.3 Le temps de cycle.....                                                      | 10  |

| 1.1.4 Les sources de variations dans la production des semi-conducteurs.....      | 11  |

| 1.1.5 Le contrôle des procédés et équipements .....                               | 12  |

| 1.2 Etat de l'art sur le contrôle et la modélisation des procédés .....           | 16  |

| 1.2.1 Travaux sur le contrôle et la modélisation des procédés .....               | 16  |

| 1.2.2 Le contrôle avancé des procédés dans le milieu industriel.....              | 17  |

| 1.2.3 La conception de contrôleur R2R .....                                       | 20  |

| 1.3 Stratégie de l'étude et outils statistiques .....                             | 21  |

| 1.3.1 Evaluation de la variabilité du procédé .....                               | 22  |

| 1.3.2 Identification de l'étape et de ses paramètres critiques .....              | 27  |

| 1.3.3 Modèle du procédé .....                                                     | 32  |

| 1.3.4 Validation du modèle .....                                                  | 35  |

| 1.3.5 Contraintes de production .....                                             | 35  |

| 1.3.6 Evaluation du gain sur la réduction de la variabilité .....                 | 36  |

| 1.4 Conclusion .....                                                              | 37  |

| <b>2 Isolation par les tranchées peu profondes (STI) dans la technologie CMOS</b> | 41  |

| 2.1 La technologie CMOS.....                                                      | 42  |

| 2.1.1 La loi de Moore .....                                                       | 42  |

| 2.1.2 Introduction de la technologie CMOS .....                                   | 44  |

| 2.1.3 Les procédés de fabrication d'un circuit CMOS .....                         | 45  |

| 2.2 Techniques d'isolation pour les Circuits Intégrés .....                       | 45  |

| 2.2.1 Introduction sur l'isolation dans les circuits intégrés .....               | 46  |

| 2.2.2 La technologie LOCOS .....                                                  | 48  |

| 2.2.3 La technologie LOCOS modifiée ou améliorée .....                            | 52  |

| 2.2.4 Technologies NON LOCOS – Tranchées d'isolation .....                        | 55  |

| 2.3 Impact du STI sur le rendement électrique des circuits.....                   | 62  |

| 2.3.1 Impact du STI sur les paramètres électriques.....                           | 62  |

| 2.3.2 Impact du STI sur les contraintes mécaniques.....                           | 63  |

| 2.4 Conclusion .....                                                              | 65  |

|                                                                                                                              |            |

|------------------------------------------------------------------------------------------------------------------------------|------------|

| <b>3 Corrélation entre la morphologie de la tranchée d'isolation et les propriétés électriques des transistors</b>           | <b>69</b>  |

| 3.1 Introduction.....                                                                                                        | 70         |

| 3.1 Corrélations entre la morphologie de la tranchée d'isolation et les propriétés électriques des transistors .....         | 72         |

| 3.2.1 Mesures de résistances.....                                                                                            | 72         |

| 3.2.2 Principales caractéristiques des transistors .....                                                                     | 81         |

| 3.2.3 Indicateur électrique de suivi des boucles de régulations R2R du module STI.....                                       | 85         |

| 3.3 Corrélation entre la morphologie de la tranchée d'isolation et les contraintes mécaniques.....                           | 85         |

| 3.3.1 Rappel sur l'effet des contraintes STI .....                                                                           | 85         |

| 3.3.2 Cristal soumis aux contraintes de l'isolement STI.....                                                                 | 86         |

| 3.3.3 Effet sur la mobilité des porteurs .....                                                                               | 87         |

| 3.3.4 Influence de la distance entre la grille et le STI .....                                                               | 89         |

| 3.3.5 Modélisation numérique.....                                                                                            | 95         |

| 3.4 Conclusion.....                                                                                                          | 101        |

| <b>4 Boucles de régulation R2R sur le module STI</b>                                                                         | <b>104</b> |

| <b>4.1 Analyses de variabilités</b>                                                                                          | <b>105</b> |

| 4.1.1 Introduction.....                                                                                                      | 105        |

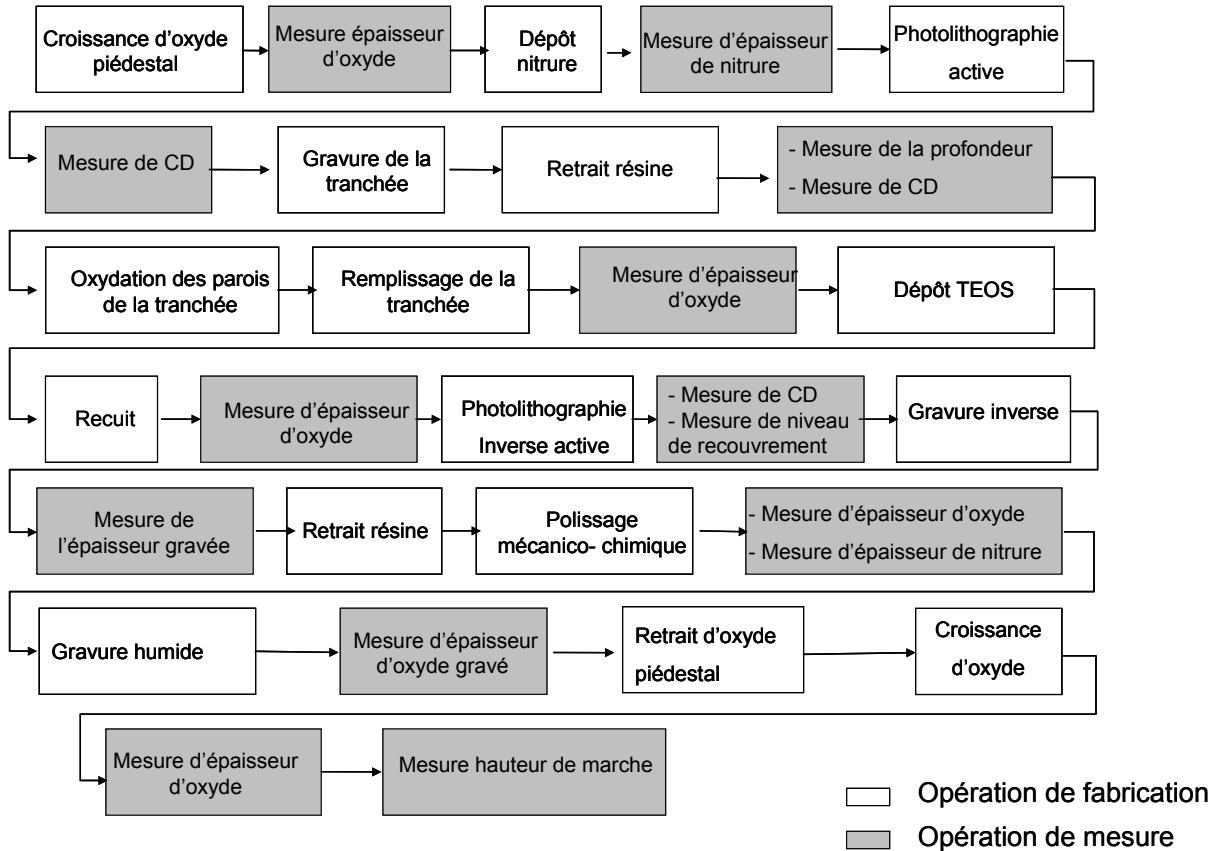

| 4.1.2 Rappel du procédé de la réalisation de la brique STI.....                                                              | 106        |

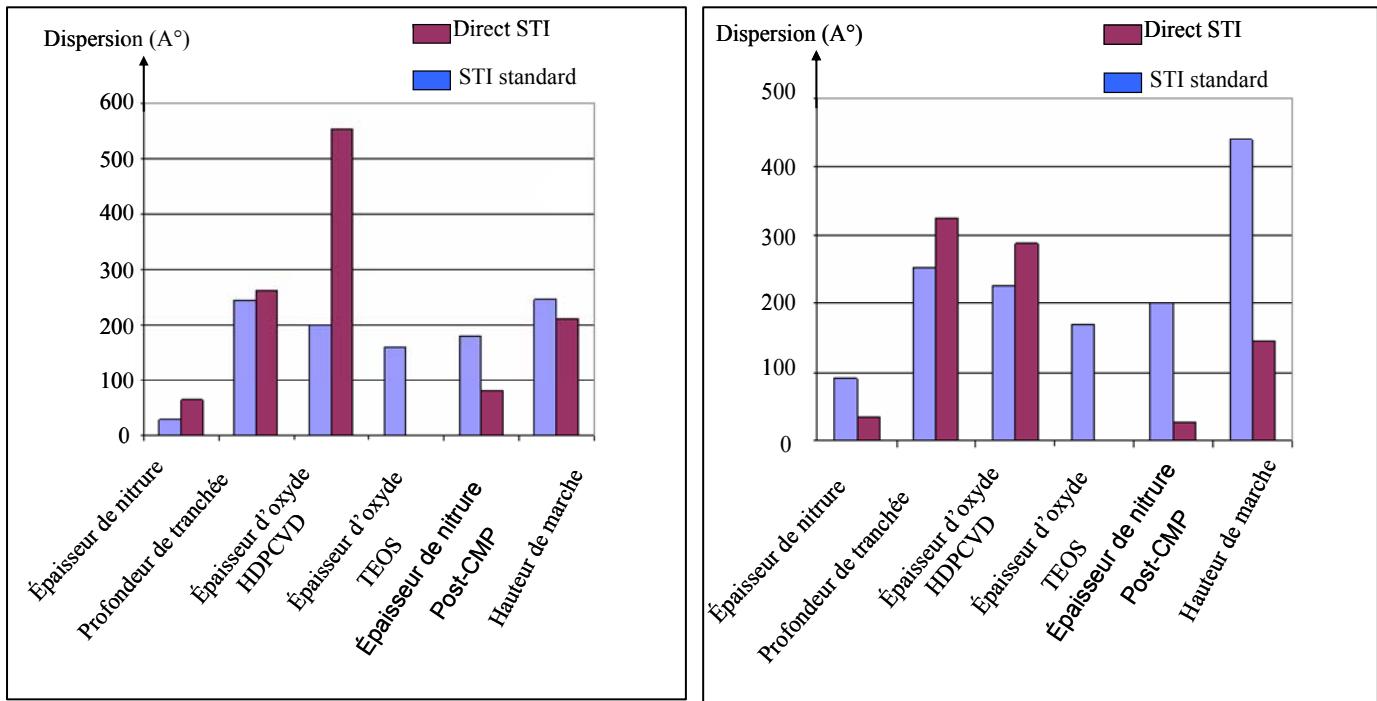

| 4.1.3 Étude de la variabilité.....                                                                                           | 107        |

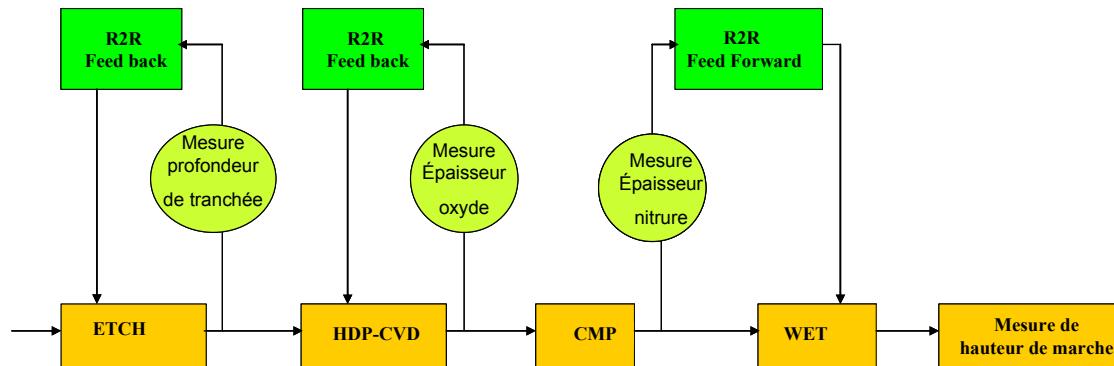

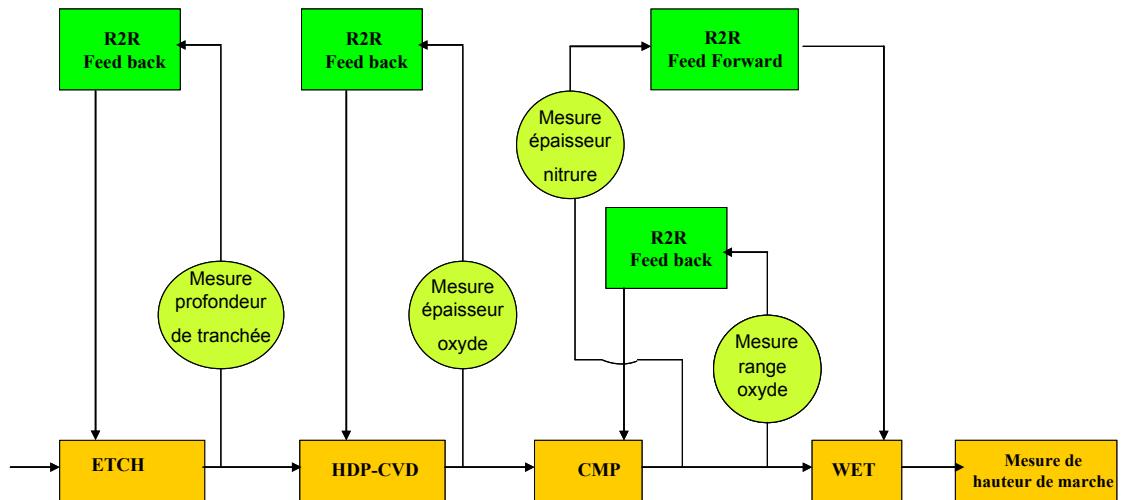

| 4.1.4 Boucles de régulation sur le module STI.....                                                                           | 108        |

| 4.1.5 Organisation du travail.....                                                                                           | 110        |

| <b>4.2 Procédé de dépôt chimique en phase vapeur assisté par plasma haute densité (HDP-CVD)</b>                              | <b>112</b> |

| 4.2.1 Introduction.....                                                                                                      | 113        |

| 4.2.2 Principe du dépôt HDP-CVD.....                                                                                         | 113        |

| 4.2.3 Les axes principaux de recherches consacrés à l'implémentation des boucles de régulation R2R pour le procédé CVD ..... | 119        |

| 4.2.4 Variabilités du procédé HDP-CVD.....                                                                                   | 121        |

| 4.2.5 Modélisation du Procédé HDP-CVD.....                                                                                   | 129        |

| 4.2.6 Conclusion.....                                                                                                        | 139        |

| <b>4.3 Le procédé de polissage mécanico-chimique (CMP)</b>                                                                   | <b>140</b> |

| 4.3.1 Introduction.....                                                                                                      | 141        |

| 4.3.2 Description du procédé CMP.....                                                                                        | 142        |

| 4.3.3 La modélisation du polissage mécano-chimique.....                                                                      | 144        |

| 4.3.4 Définition de la non uniformité à travers la plaque .....                                                              | 150        |

| 4.3.5 La distribution de la pression.....                                                                                    | 151        |

| 4.3.6 Modélisation du procédé.....                                                                                           | 154        |

| 4.3.7 Corrélation du profil post- CMP avec les résultats électriques.....                                                    | 161        |

| 4.3.8 Corrélation entre le profil du CMP et les défauts générés.....                                                         | 162        |

| 4.3.9 Conclusion.....                                                                                                        | 164        |

|                                                                |            |

|----------------------------------------------------------------|------------|

| <b>4.4 Le polissage mécanico-chimique et la gravure humide</b> | <b>165</b> |

| 4.4.1 Introduction.....                                        | 166        |

| 4.4.2 Contexte de l'étude.....                                 | 168        |

| 4.4.3 Le procédé de la gravure humide.....                     | 169        |

| 4.4.4 Analyses multivariées.....                               | 172        |

| 4.4.5 Modélisation du procédé.....                             | 174        |

| 4.4.6 Premiers résultats de la pré- production.....            | 182        |

| 4.4.7 Surveillance de la boucle de régulation.....             | 183        |

| 4.4.8 Conclusion.....                                          | 185        |

| <b>Conclusion et perspectives</b>                              | <b>191</b> |

# Liste des figures

- Figure 1.1 Pyramide représentant les différentes techniques de contrôle

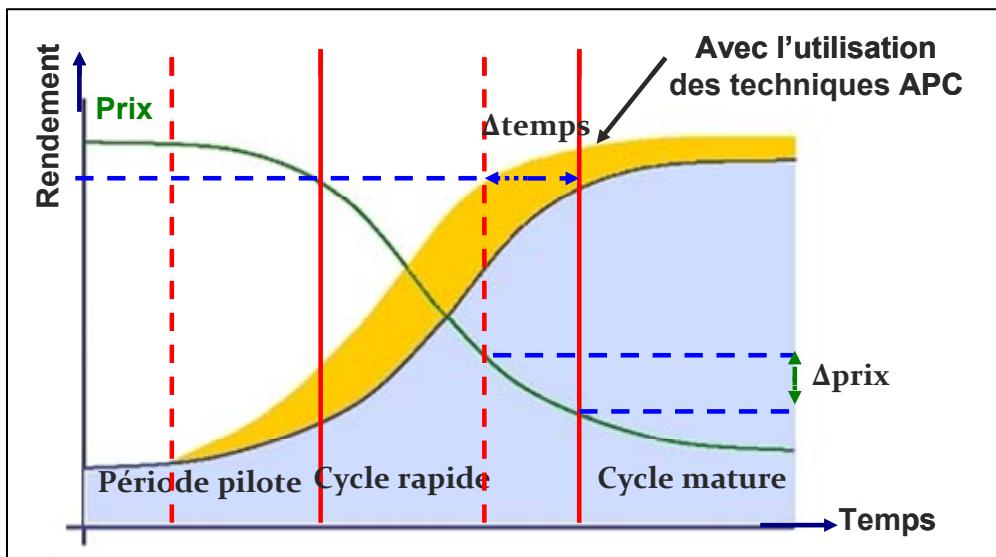

Figure 1.2 Evolution du rendement en fonction du temps et du prix des puces

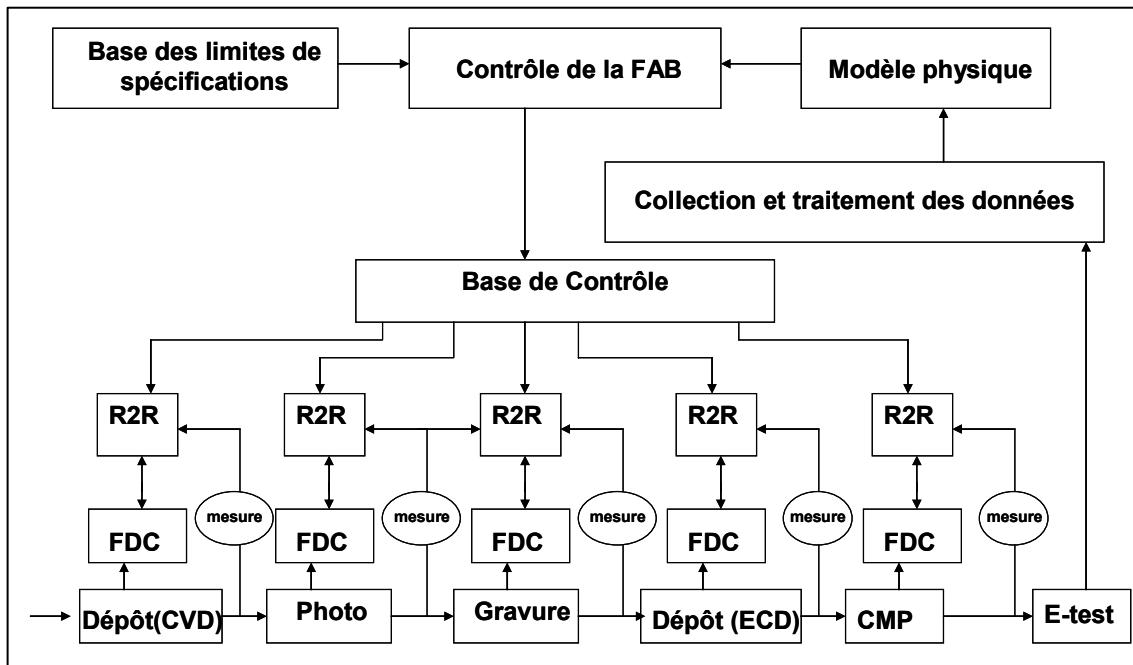

Figure 1.3 Architecture de la FAB automatisée

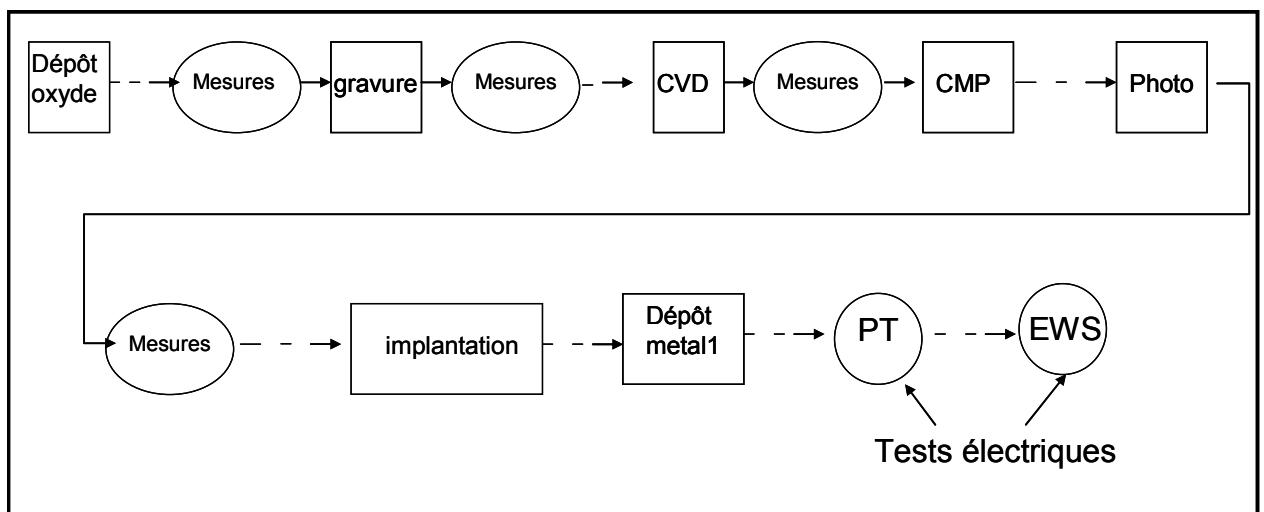

Figure 1.4 Enchaînement des opérations de fabrication des circuits

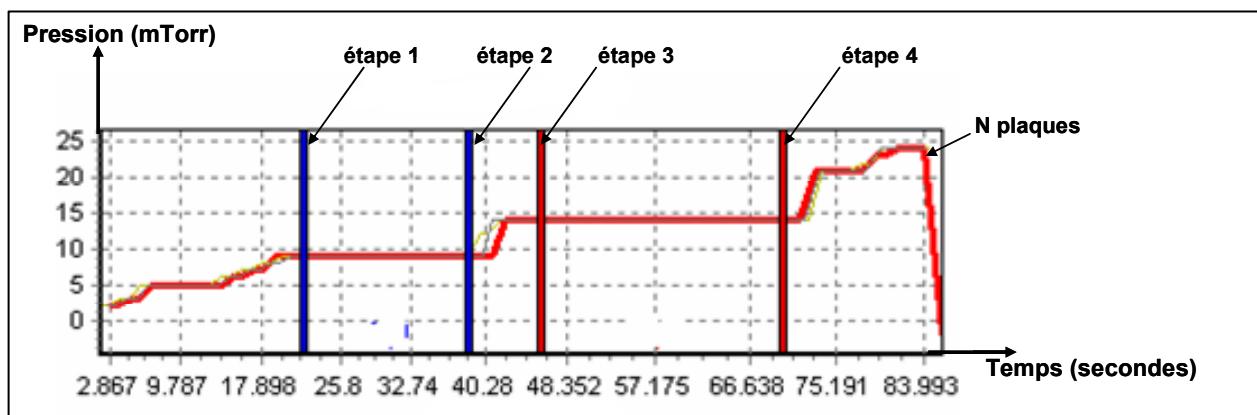

Figure 1.5 Représentation temporelle de l'évolution de la pression pendant le procédé de dépôt chimique en phase vapeur

Figure 1.6 Schéma de deux boucles de régulation Feed back et Feed forward

Figure 1.7 Le taux de déploiement de la FDC par type d'équipements

Figure 1.8 Taux de déploiement de la FDC en fonction du temps

Figure 1.9 Les différents types des outils de la FDC en fonction de temps

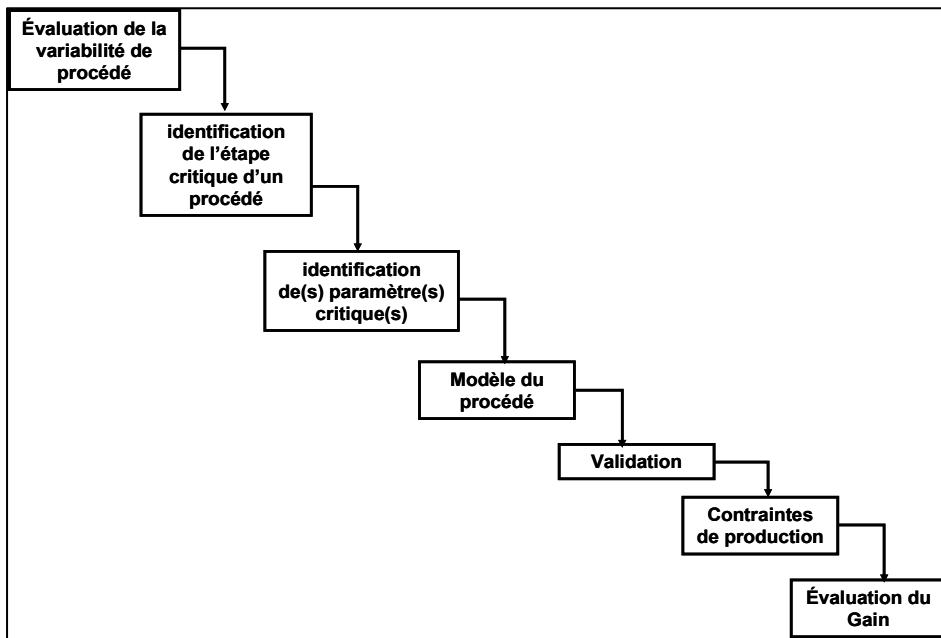

Figure 1.10 Stratégie de l'étude du déploiement d'une boucle de régulation

Figure 1.11 Exemple de représentation d'un box plot

Figure 1.12 a) Cartographie en 49 points b) Profil de la plaque après une opération de dépôt CVD mesuré en 49 points

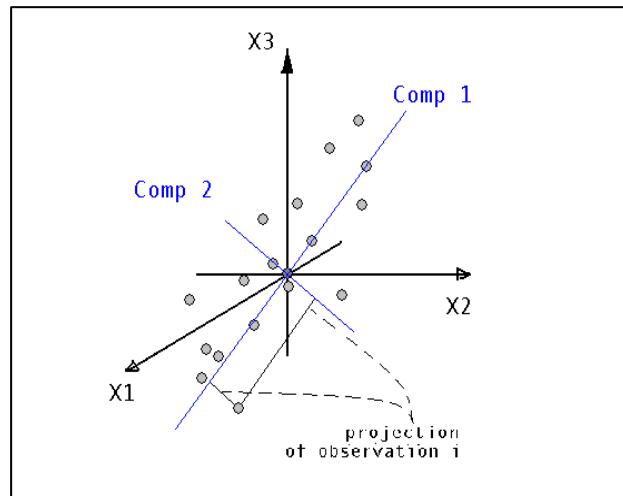

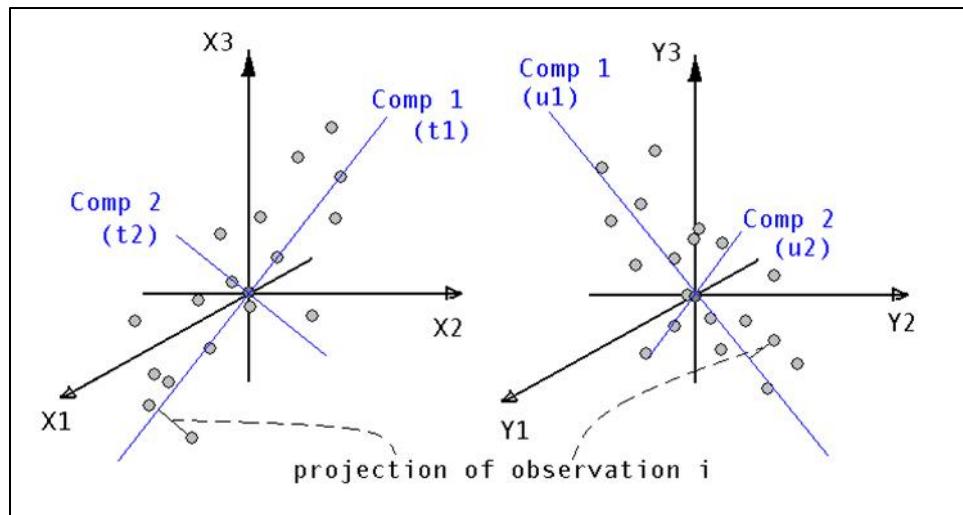

Figure 1.13 Principe de la régression ACP pour un système à 3 dimensions.

Figure 1.14 Représentation des observations dans le nouvel espace

Figure 1.15 Représentation des observations lors d'une analyse PLS

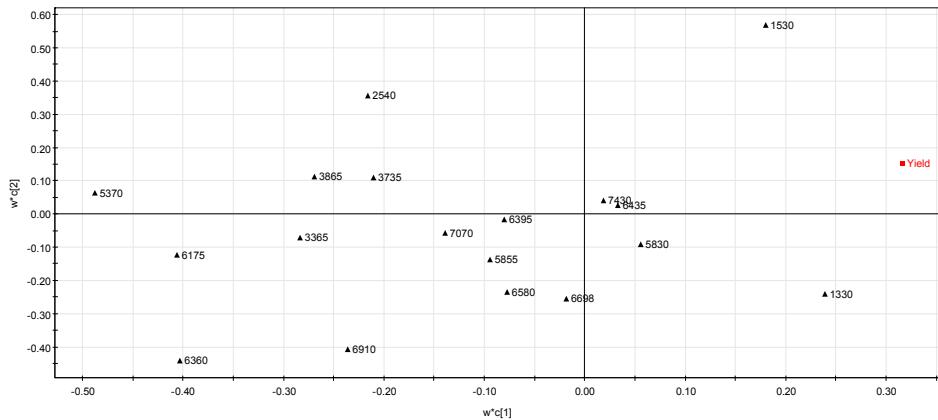

Figure 1.16 Les coefficients de corrélations des différentes variables sur les deux composantes

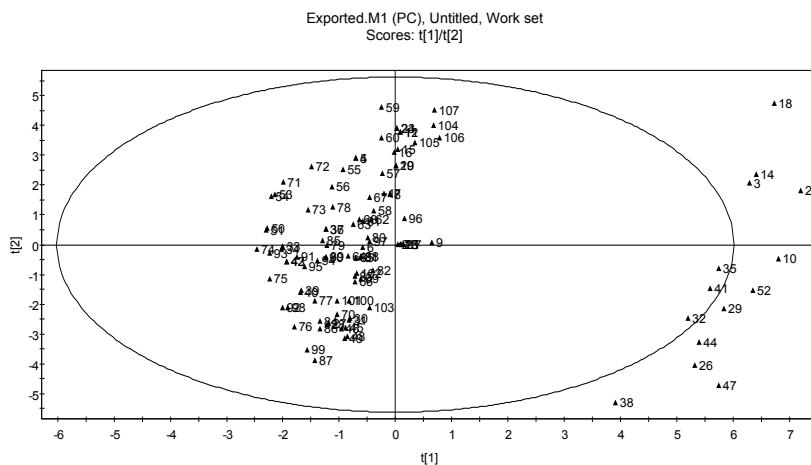

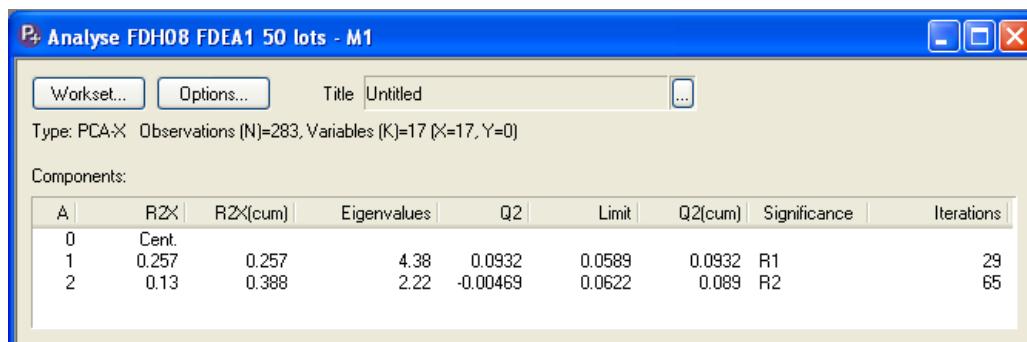

Figure 1.17 Résultats d'une analyse à partir de Simca-P

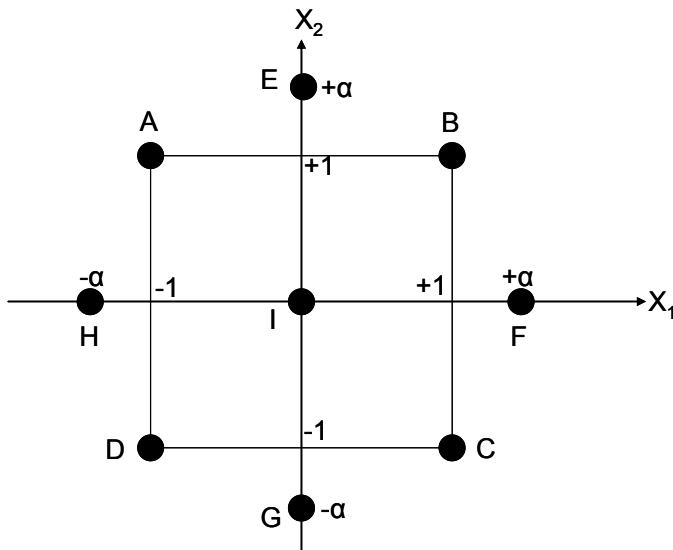

Figure 1.18 Plan composite pour deux facteurs

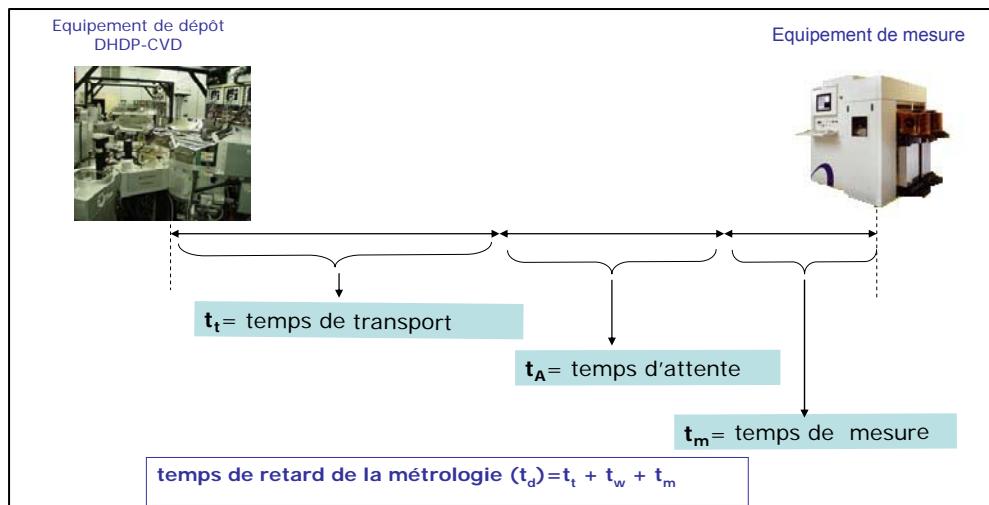

Figure 1.19 Représentation de temps total d'attente.

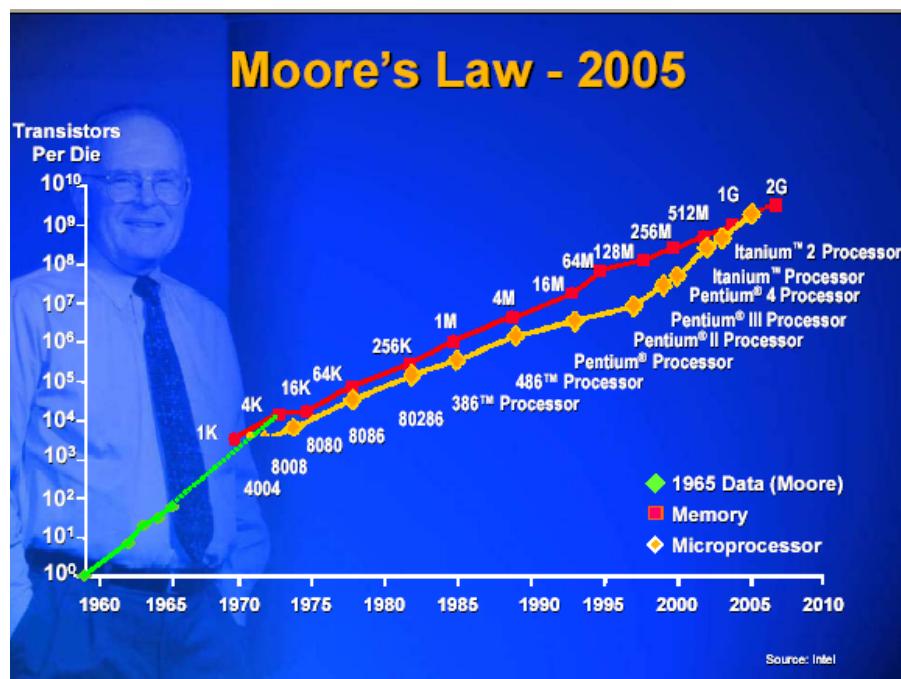

Figure 2.1 Evolution des produits en fonction du temps suivant la loi de Moore (augmentation de la densité d'intégration et réduction des dimensions critiques)

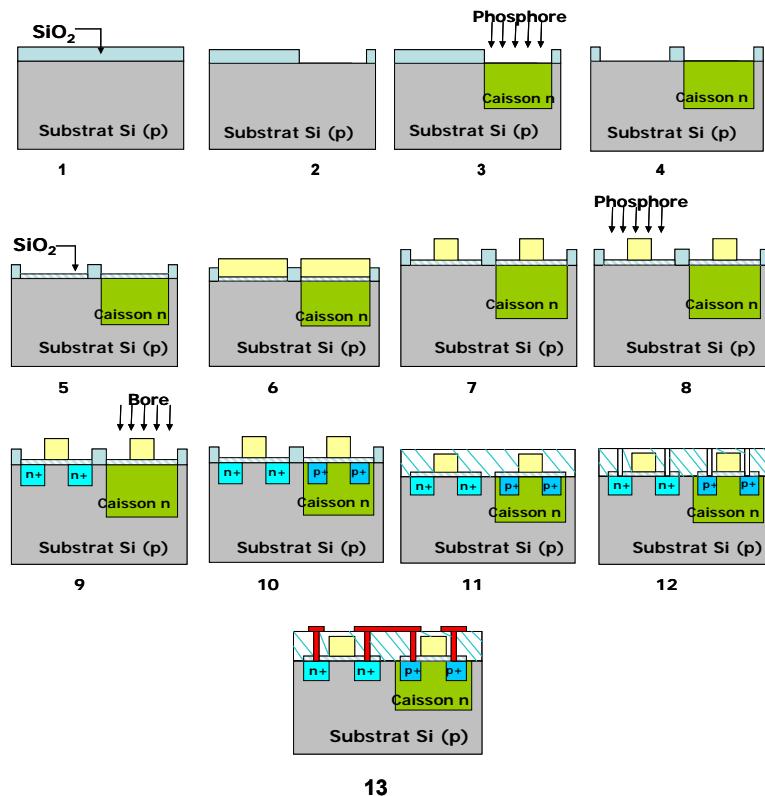

Figure 2.2 Opérations élémentaires dans la technologie CMOS

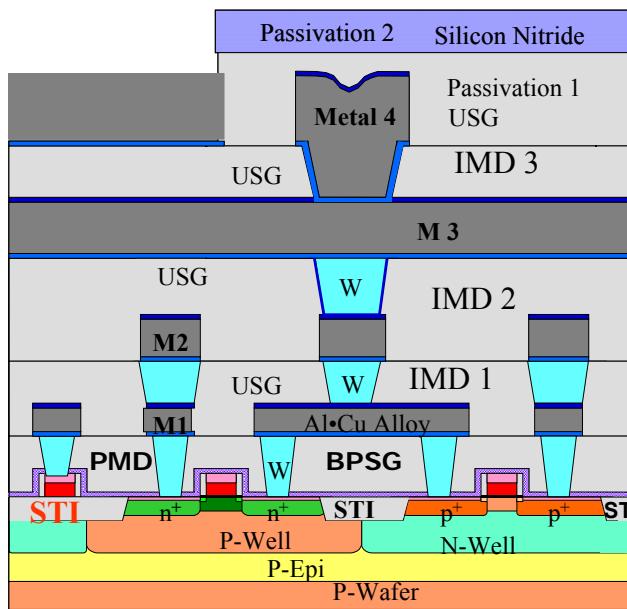

Figure 2.3 Coupe d'un circuit après toutes les étapes de fabrication.

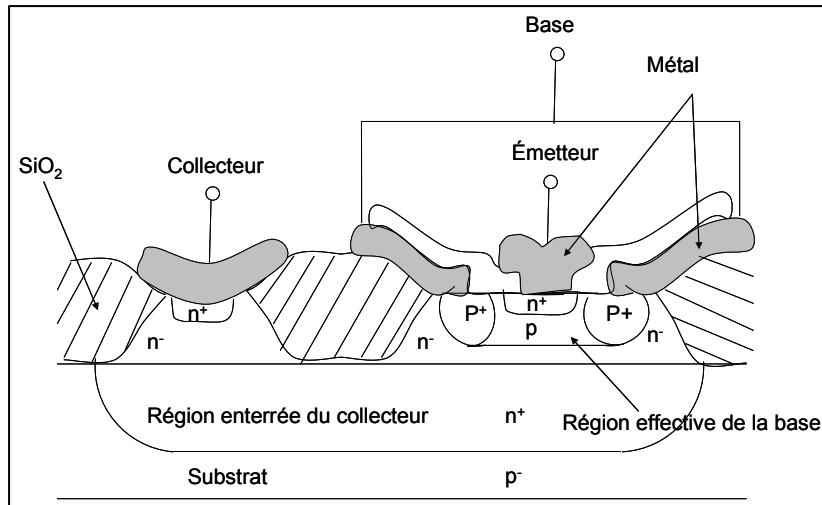

Figure 2.4 Représentation schématique d'un transistor bipolaire

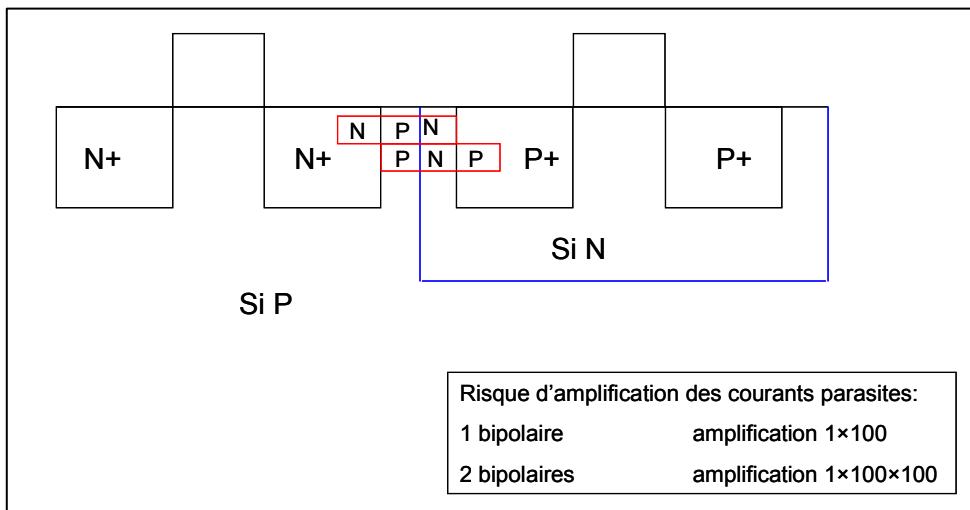

Figure 2.5 Une structure CMOS faisant apparaître l'existence de deux transistors montés en série.

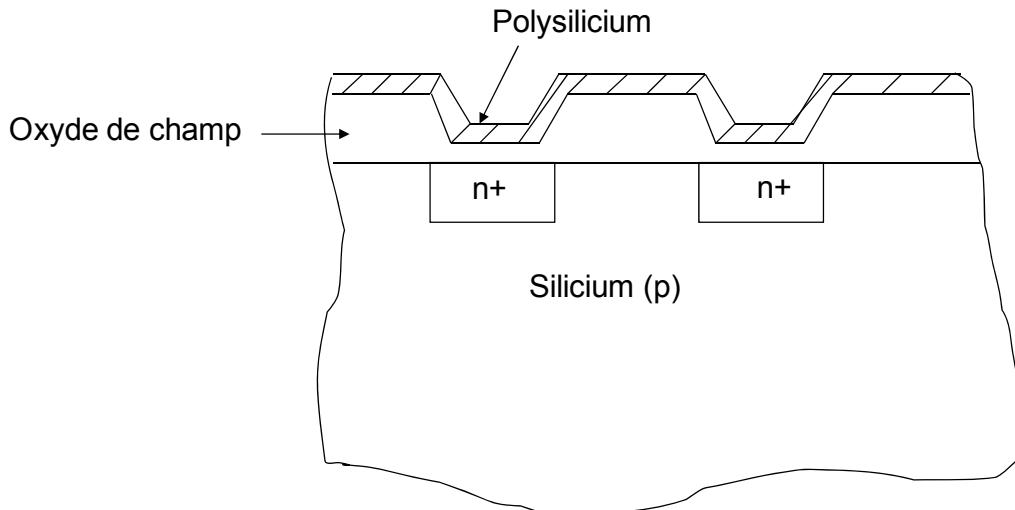

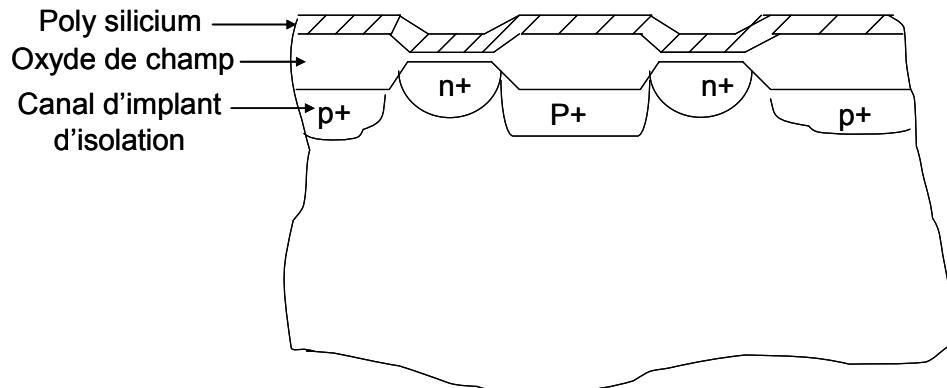

Figure 2.6 Schématisation des premiers modèles d'isolation

Figure 2.7 Schématisation de l'approche de l'oxydation sélective

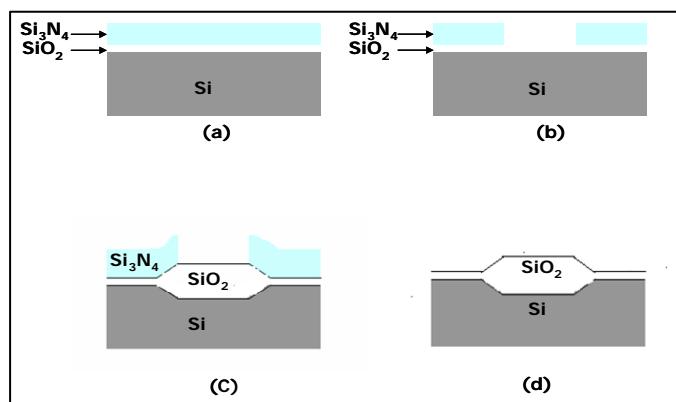

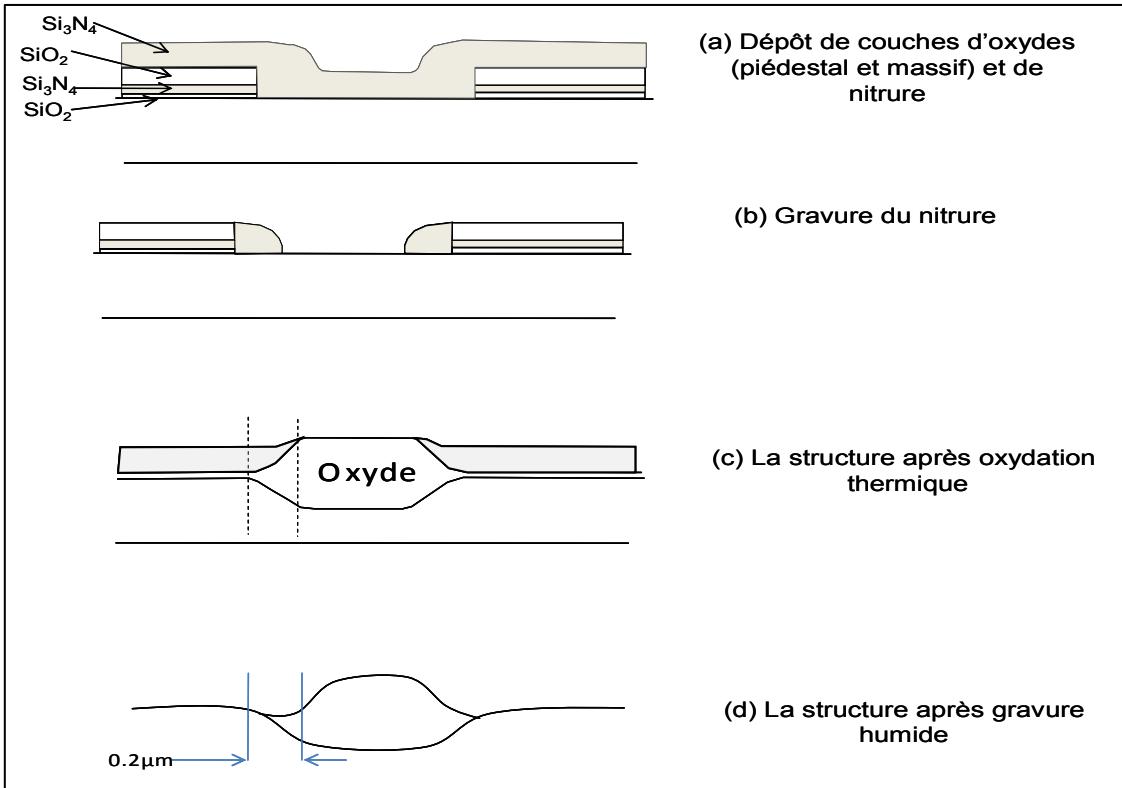

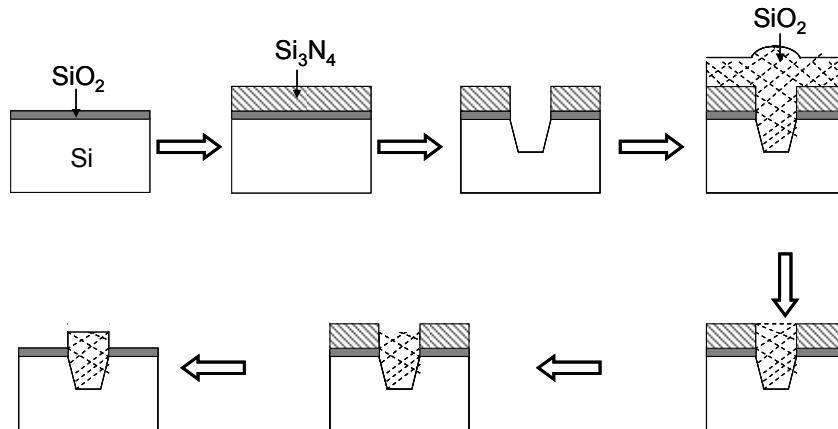

Figure 2.8 Différentes étapes de fabrication pour la réalisation du LOCOS : a) Dépôt du padox et du nitre b) Après la gravure c) Oxydation d) Retrait du nitre de silicium et du padox

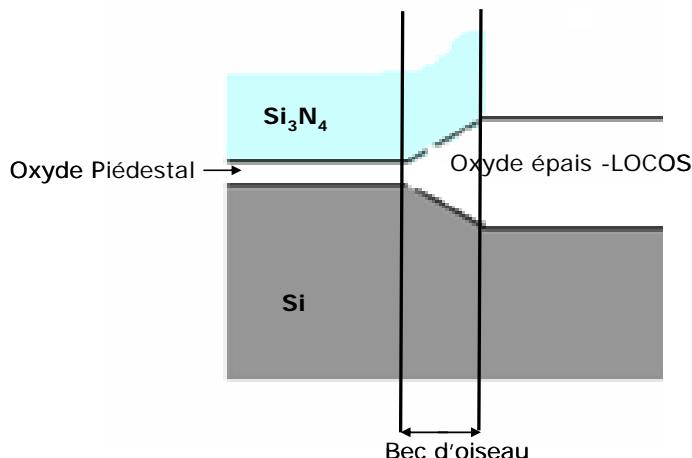

Figure 2.9 Schématisation de phénomène de bec d'oiseau

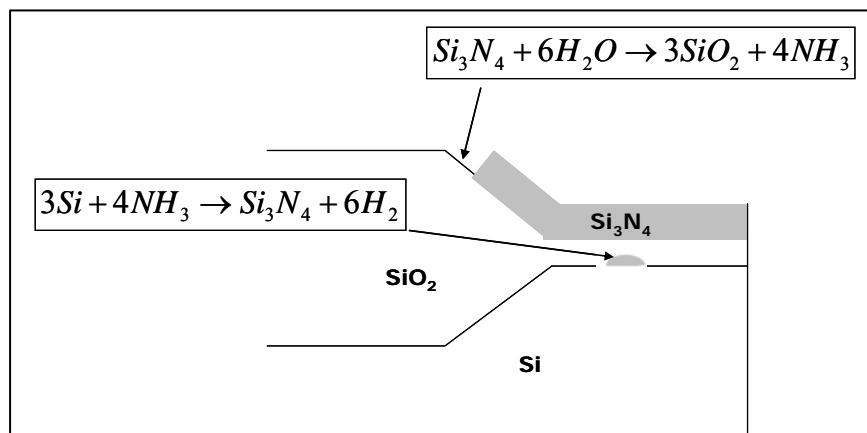

Figure 2.10 Représentation du modèle de Kooi

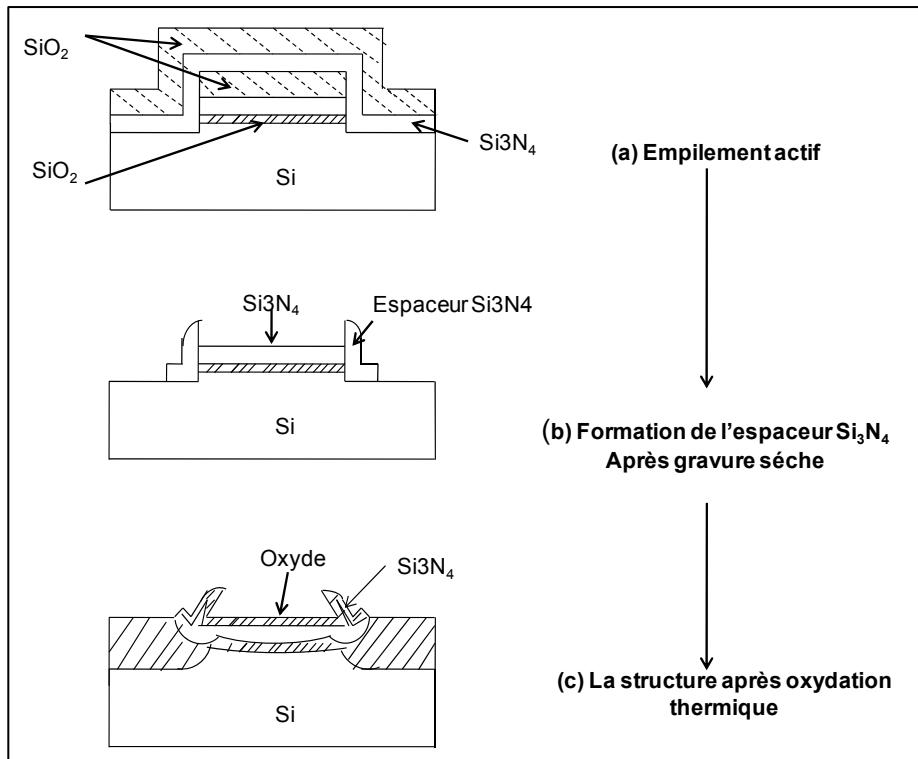

Figure 2.11 Schématisation de la méthode d'oxydation locale scellée latéralement

Figure 2.12 Représentation du procédé POP SILO

Figure 2.13 Schématisation de la méthode BOX

Figure 2.14 Schématisation des étapes élémentaires pour la réalisation du BOXES

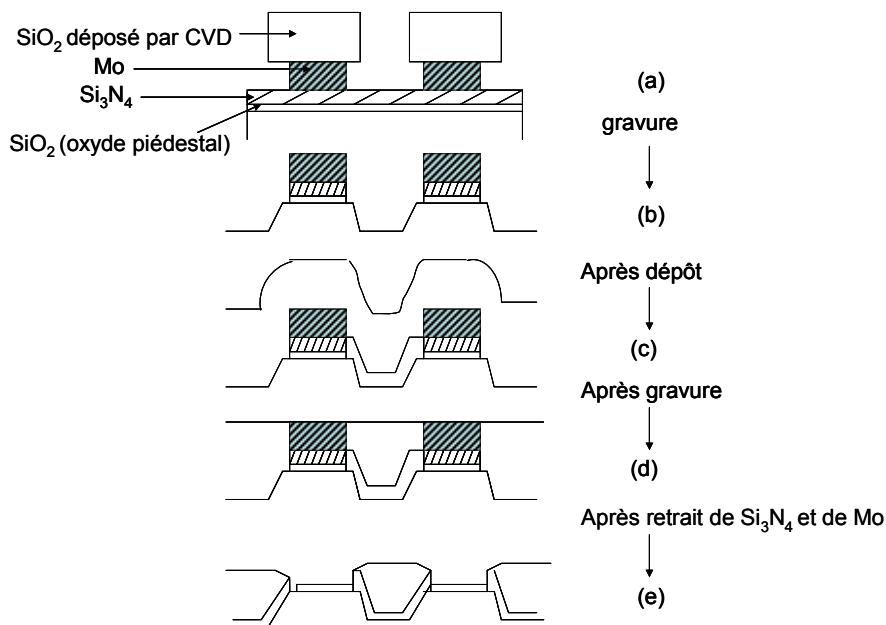

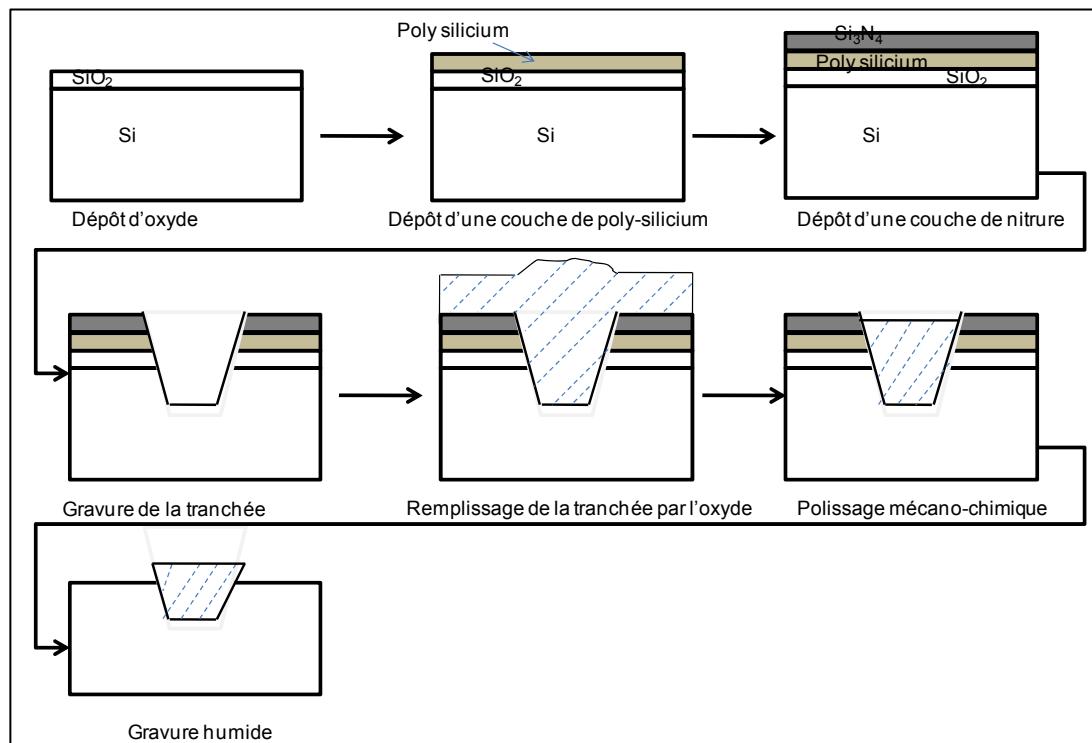

Figure 2.15 Représentation de la fabrication du STI

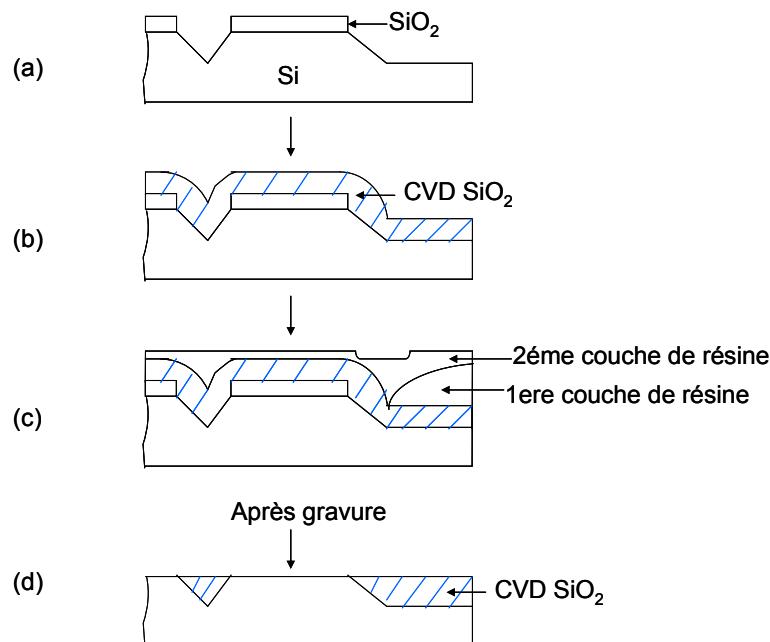

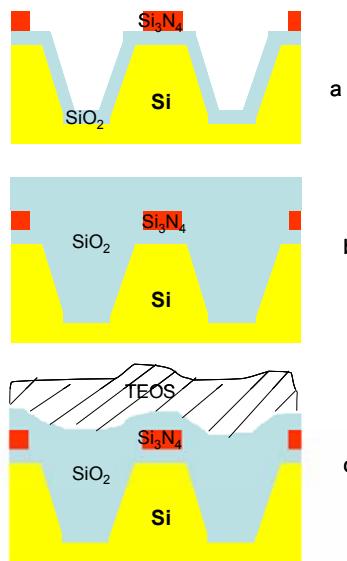

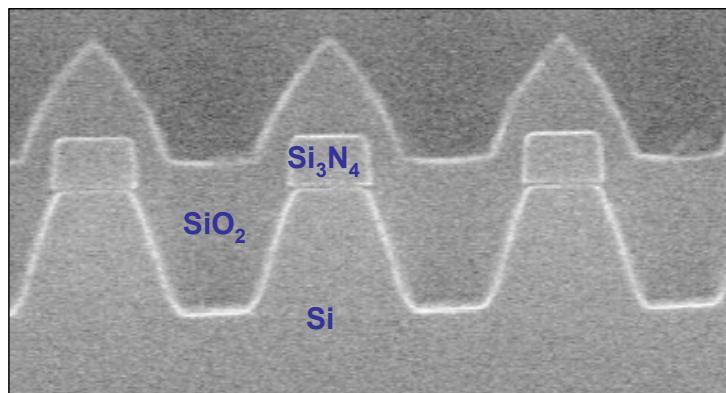

Figure 2.16 Procédé du dépôt dans la tranchée : a) Oxydation thermique des bords de tranchée b) Remplissage par HDP-CVD c) Remplissage par dépôt TEOS

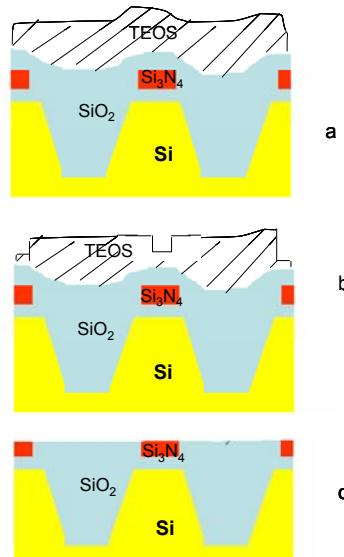

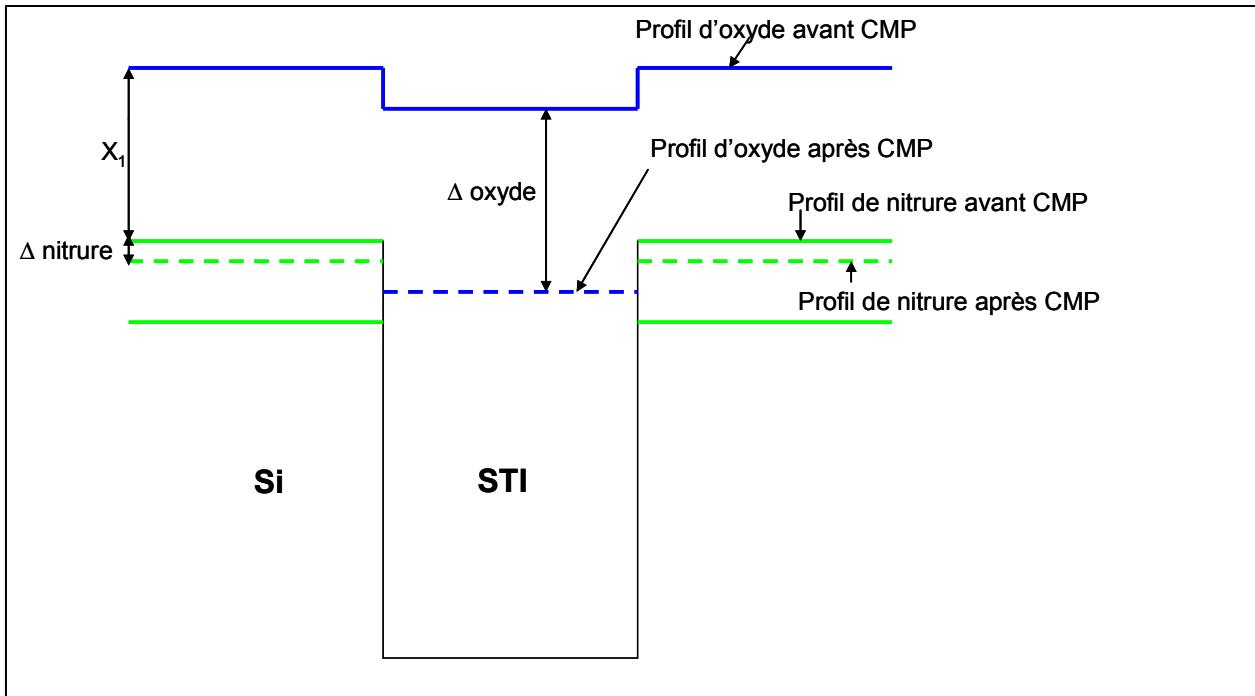

Figure 2.17 Procédés de polissage mécanico-chimique : a) Etat Initial b) Gravure de l'oxyde avec un motif inversé par rapport à la gravure active c) Polissage d'oxyde jusqu'au nitre

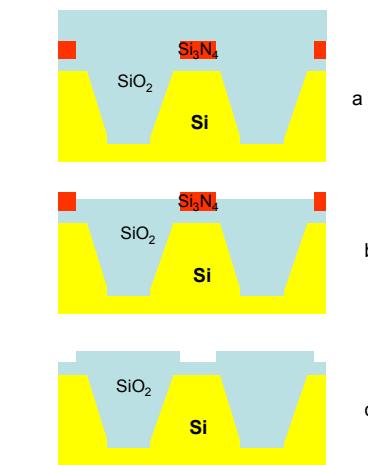

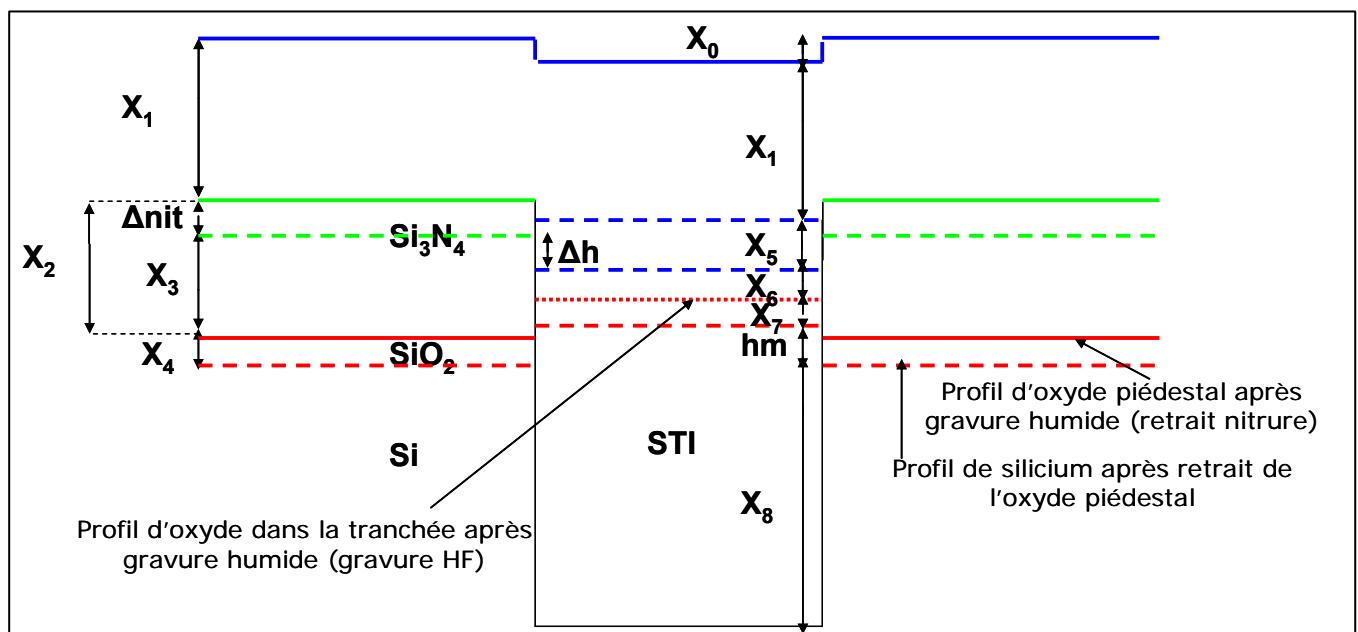

- Figure 2.18 Etapes du procédé de la gravure humide : a) STI après CMP b) Désoxydation de la surface de nitrure et ajustement de la marche c) Retrait Nitrure

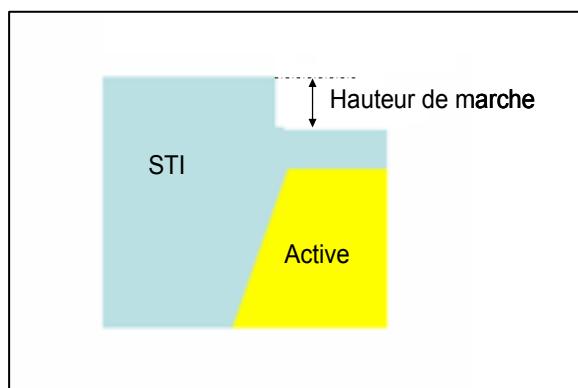

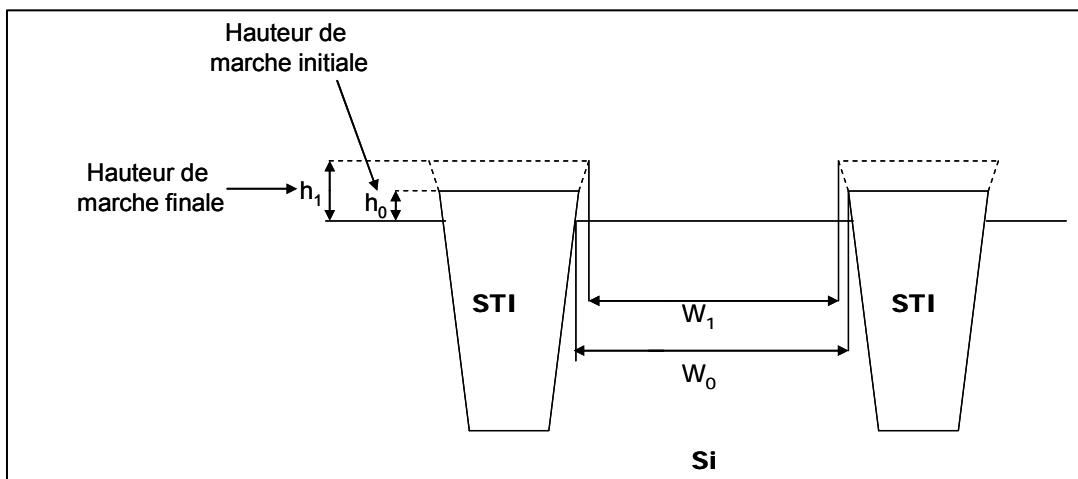

- Figure 2.19 Schématisation de la hauteur de marche

- Figure 2.20 Représentation de la fabrication du PB-STI

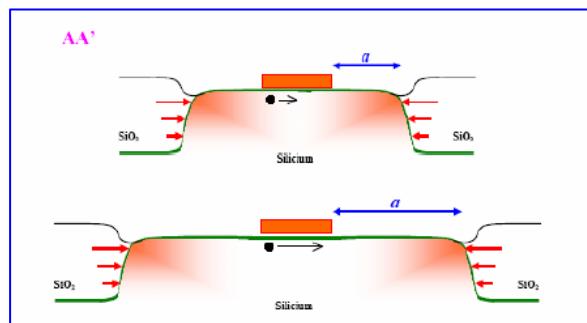

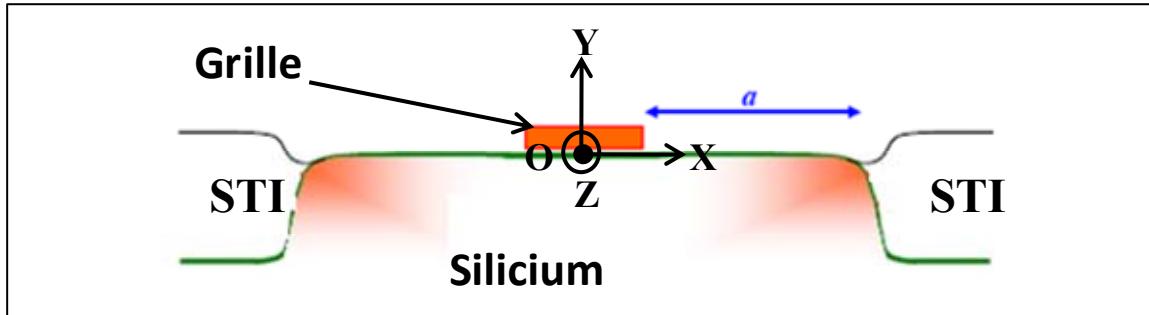

- Figure 2.21 Comparaison de deux structures ayant différentes valeurs de la distance « a »

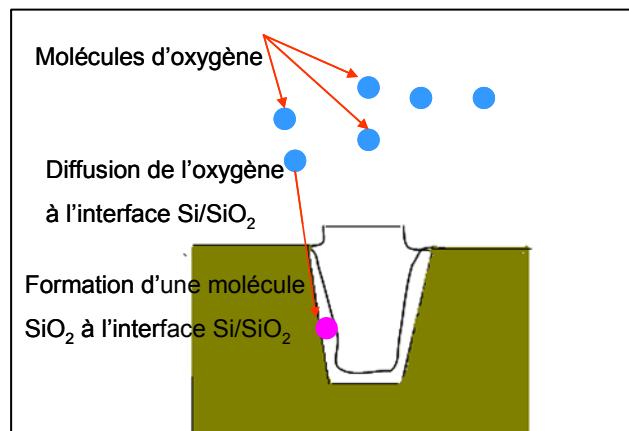

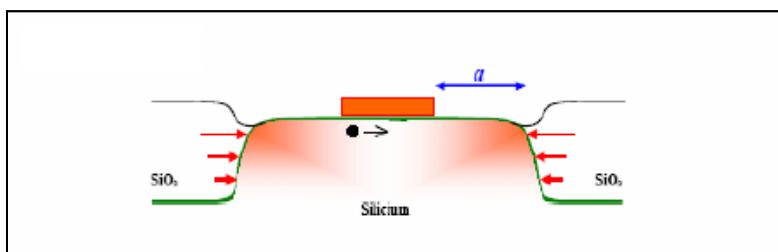

- Figure 2.22 Compression de la zone active par croissance d'oxyde

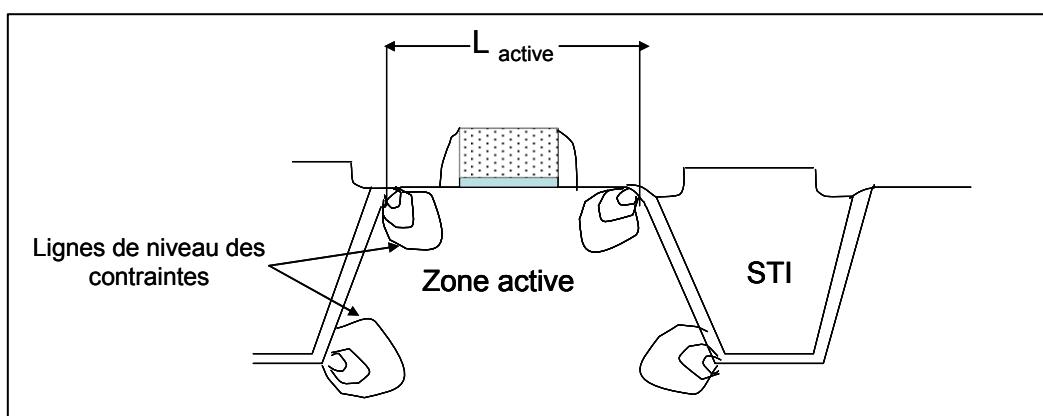

- Figure 2.23 Localisation des contraintes maximales en bord du STI.

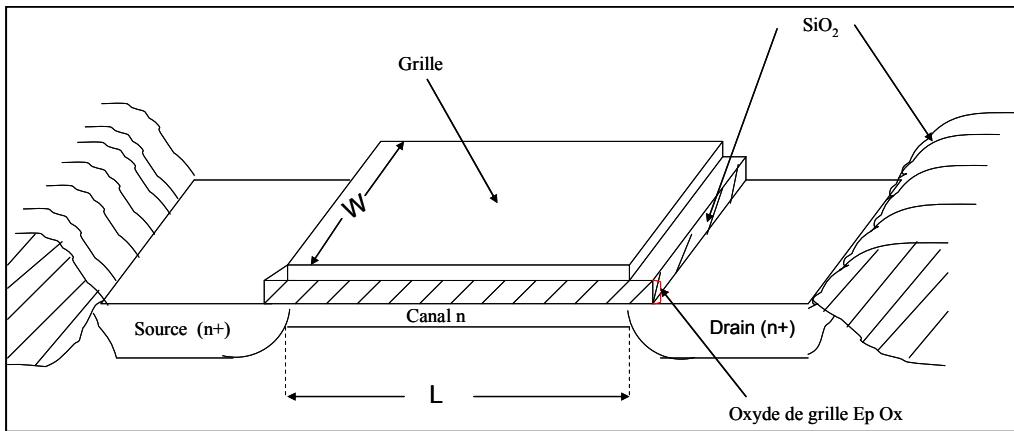

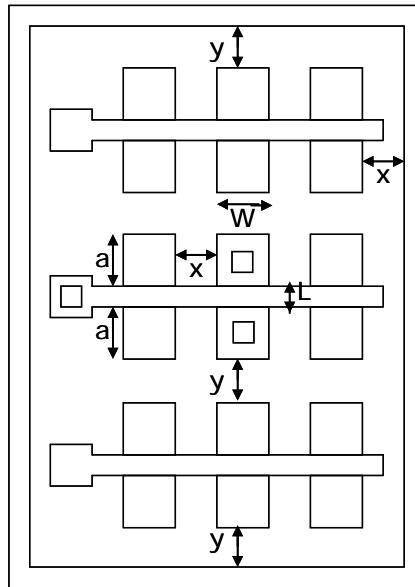

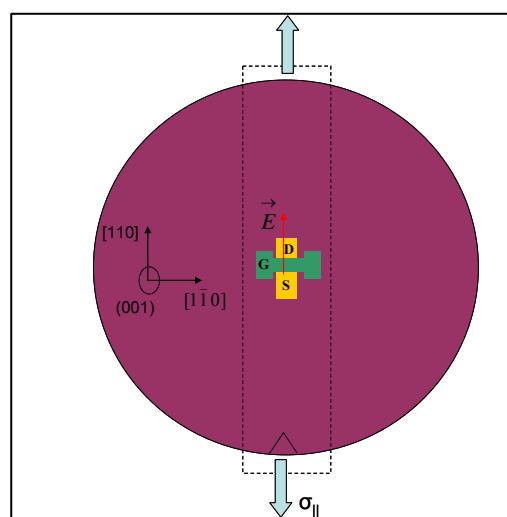

- Figure 3.1 Coupe schématique d'un transistor MOS avec une vue de dessus

- Figure 3.2 Caractéristique de transfert d'un transistor MOS avec une tension  $V_{DS}$  constante

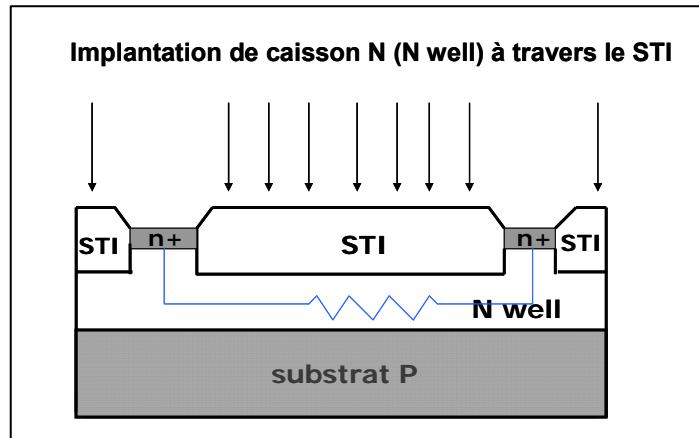

- Figure 3.3 Structure de test employée pour la mesure de la résistance carrée Nwell STI dans une structure PMOS

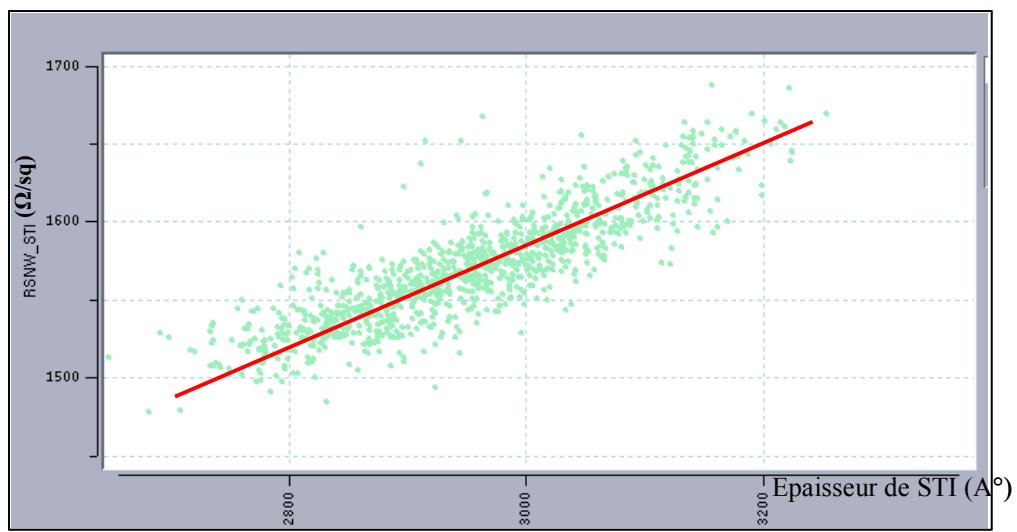

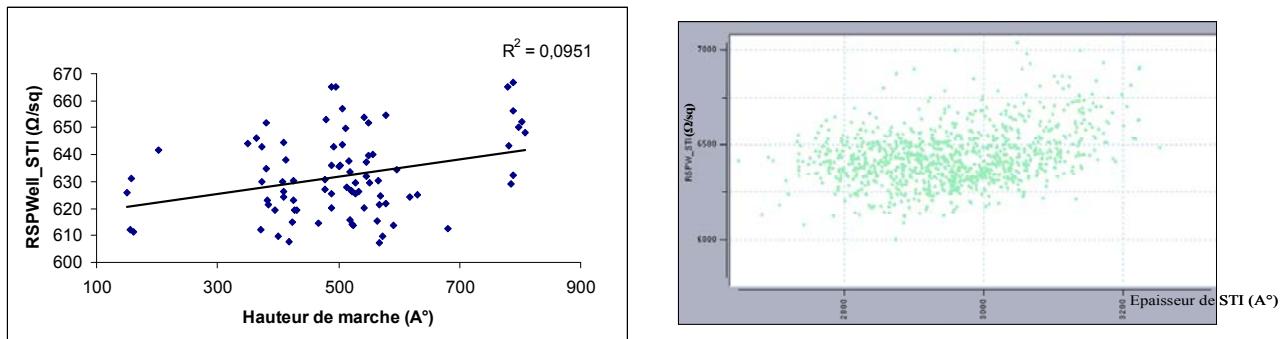

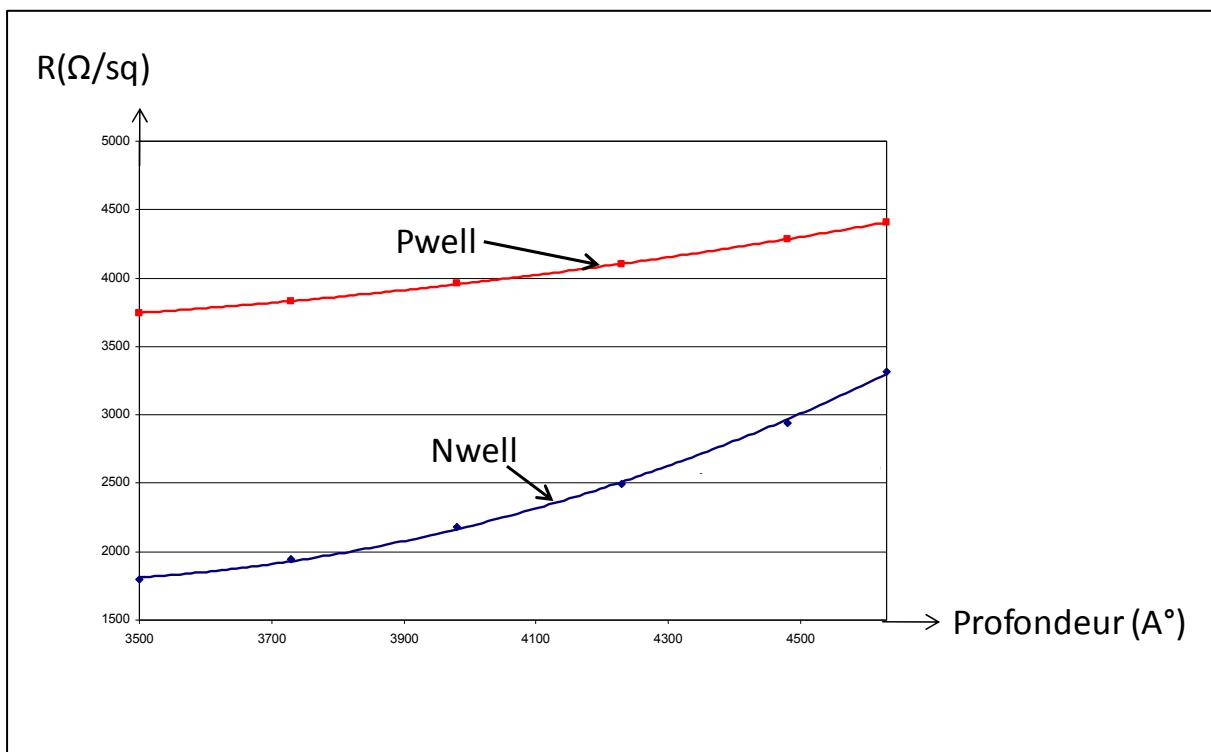

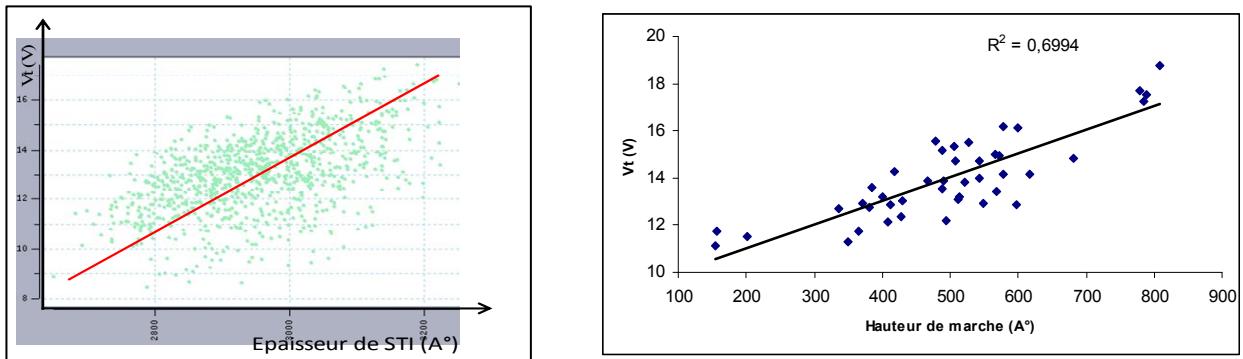

- Figure 3.4 Evolution de la résistance carrée Nwell STI en fonction de l'épaisseur de STI

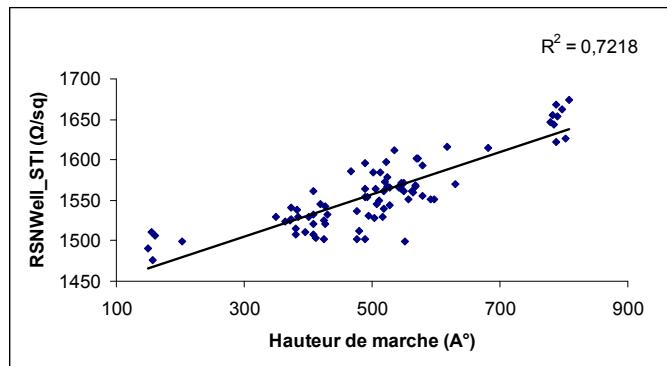

- Figure 3.5 Evolution de la résistance carrée Nwell STI en fonction de la hauteur de marche

- Figure 3.6 Evolution de la résistance carrée Pwell STI en fonction de a) l'épaisseur STI et b) la hauteur de marche

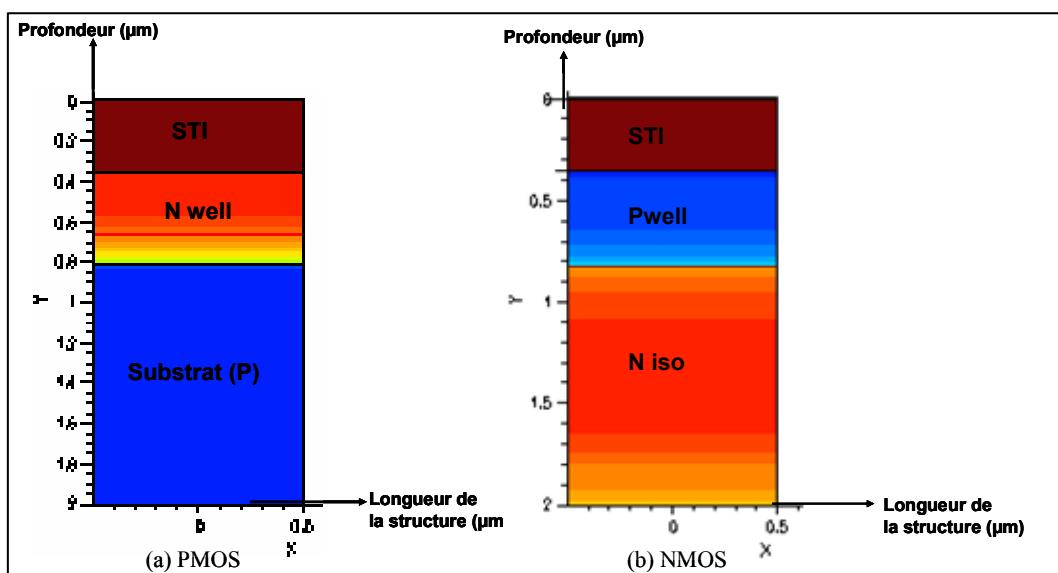

- Figure 3.7 Coupe 1D de la structure pour les transistors PMOS et NMOS

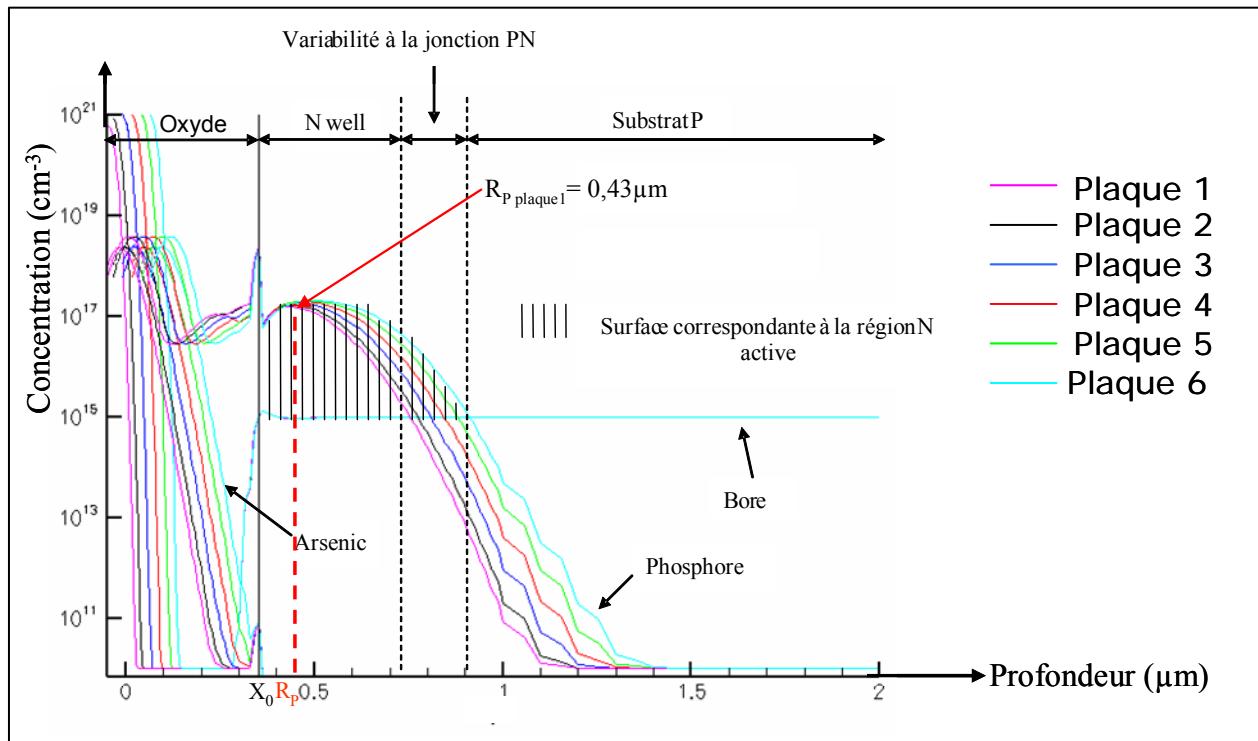

- Figure 3.8 Profil des dopants dans le Nwell STI

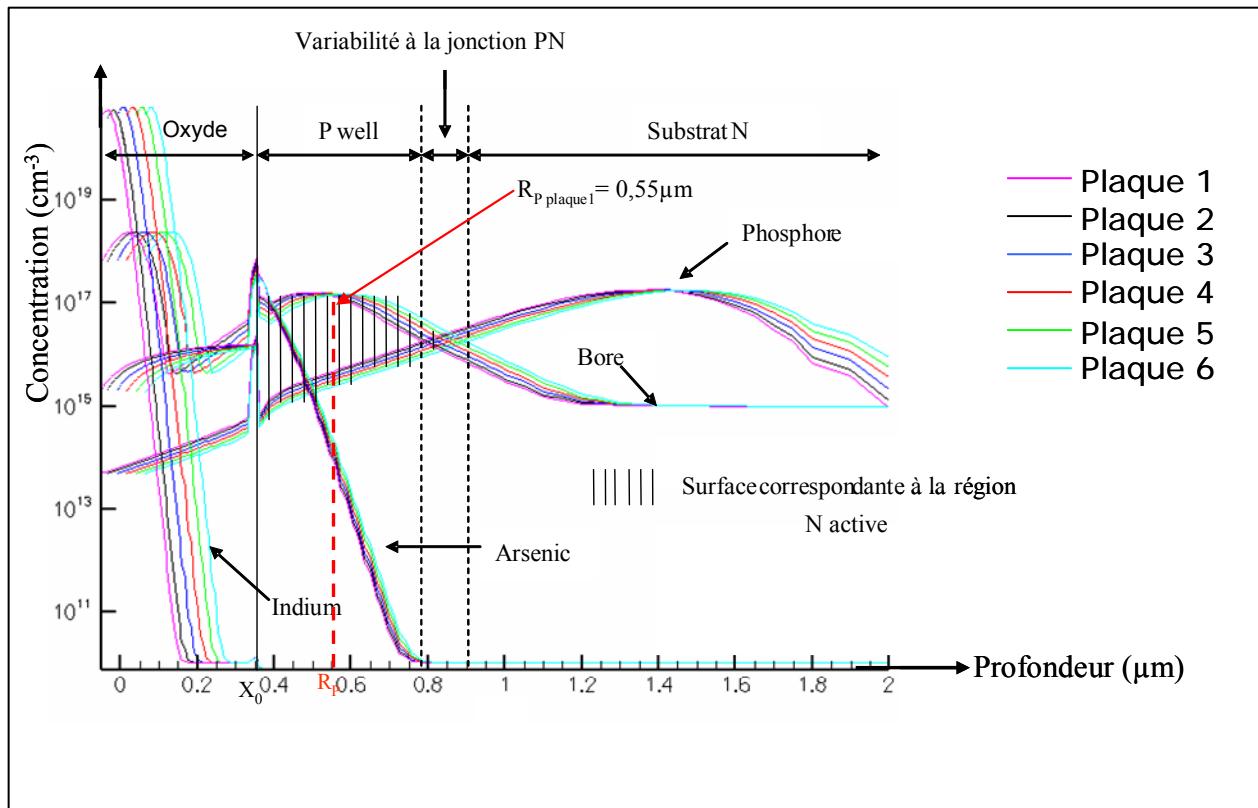

- Figure 3.9 Profil des dopants dans le Pwell STI

- Figure 3.10 Simulations de la résistance carrée de la couche implantée sous le STI.

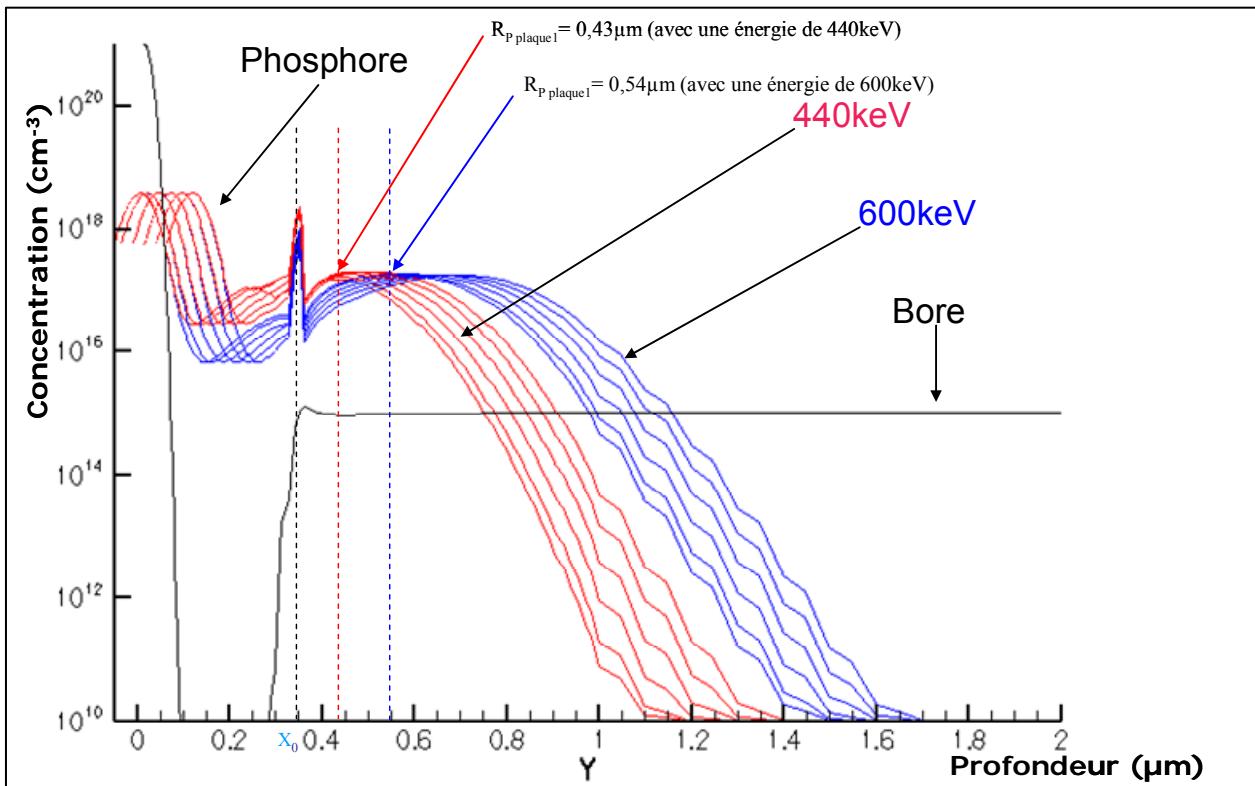

- Figure 3.11 Effet de translation du pic d'implantation avec des énergies différentes lors d'implantation de Nwell

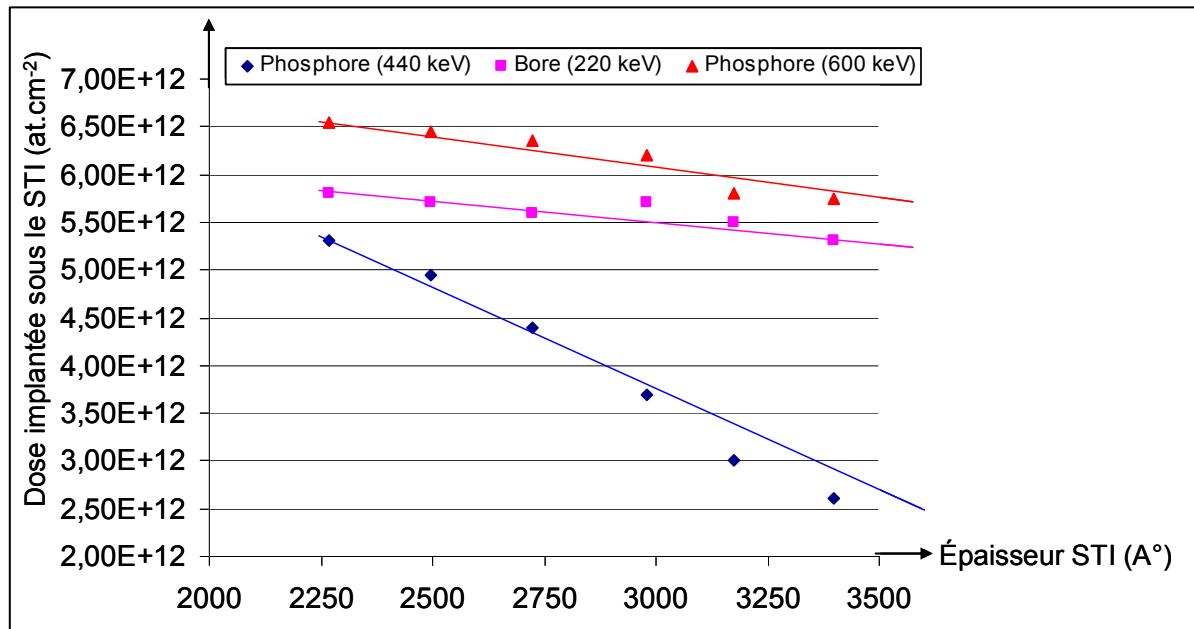

- Figure 3.12 Calcul de l'intégral des concentrations des atomes après implantation d'un Nwell et d'un Pwell avec différentes énergies d'implantation

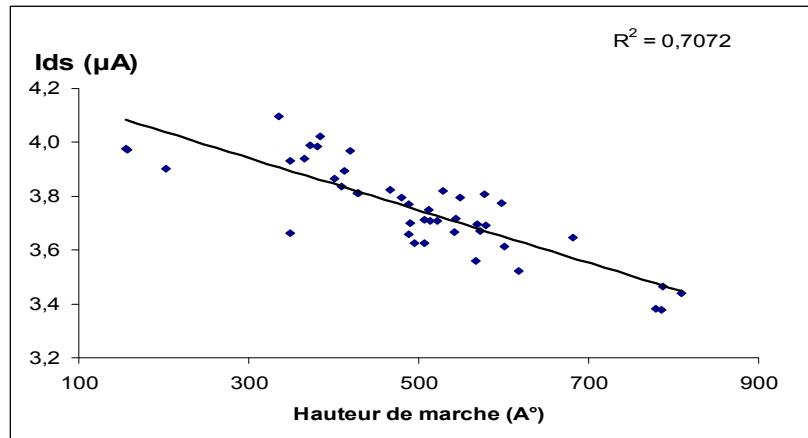

- Figure 3.13 Evolution de courant  $I_{DS}$  en fonction de la hauteur de marche pour les transistors NMOS( $W=0,25\mu m$   $L=10\mu m$ )

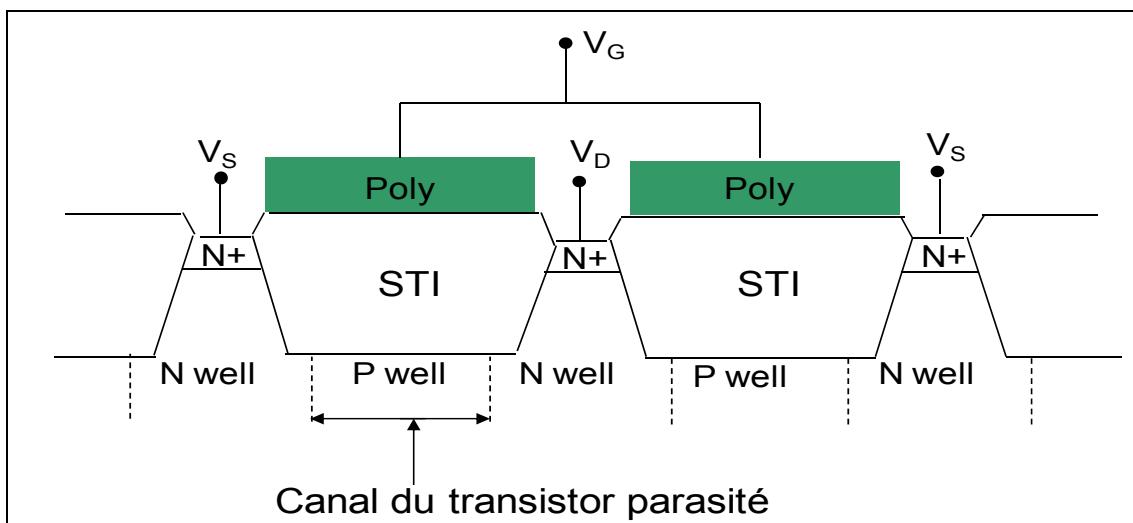

- Figure 3.14 Schématisation du transistor

- Figure 3.15 Structure de test conçue pour le monitoring de la tension de seuil  $V_t$

- Figure 3.16 Evolution de la tension de seuil en fonction : a) de l'épaisseur STI b) de la hauteur de marche STI

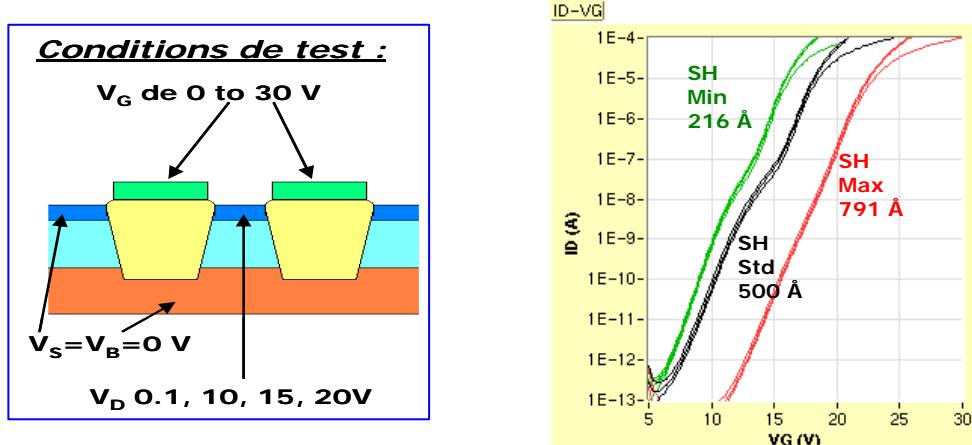

- Figure 3.17 a) Conditions de test b) La caractéristique  $I_d(V_g)$

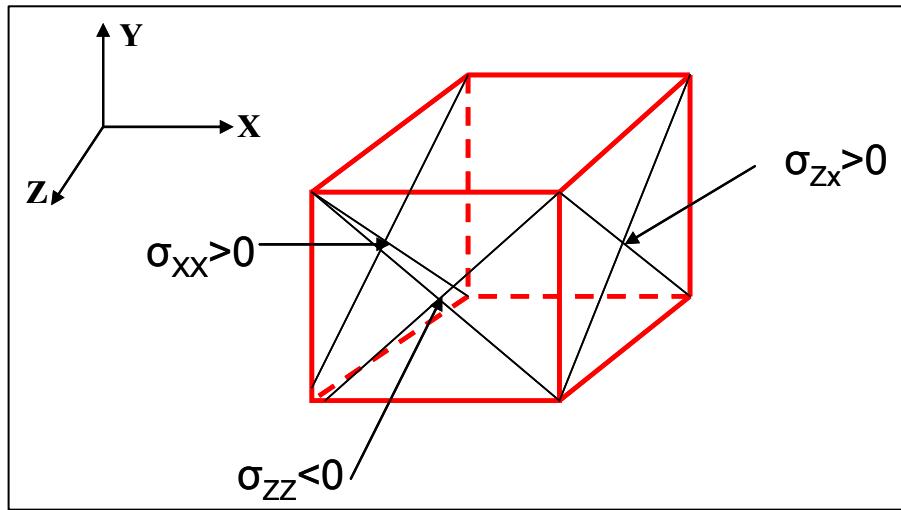

- Figure 3.18 Direction et plan associé à une contrainte

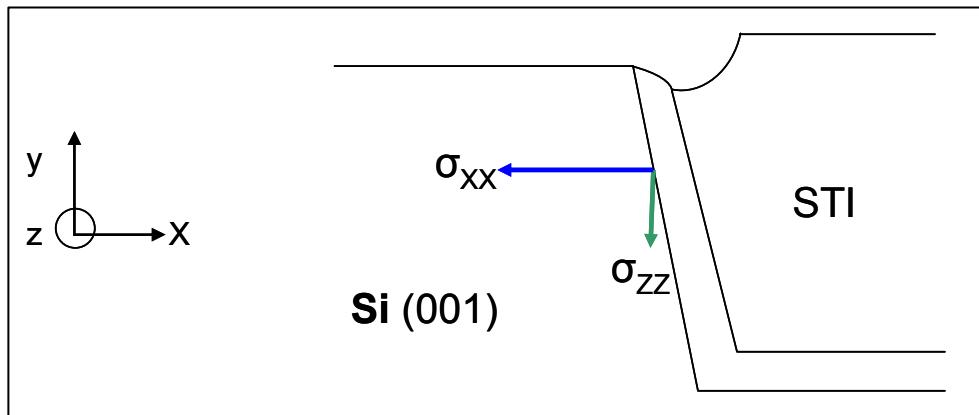

- Figure 3.19 Contraintes d'isolement normales aux interfaces zone active/STI

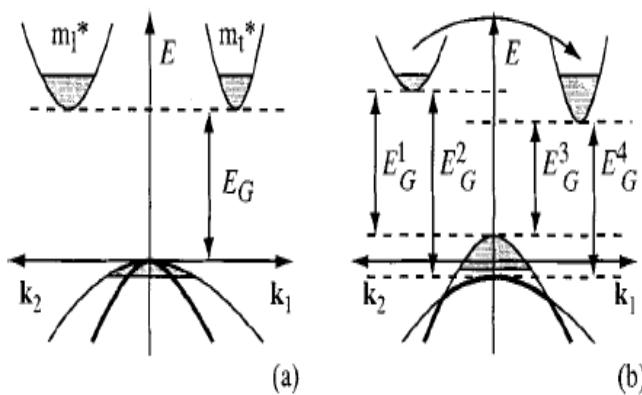

- Figure 3.20 Diagramme des bandes d'énergie a) sans contraintes b) sous contraintes mécaniques

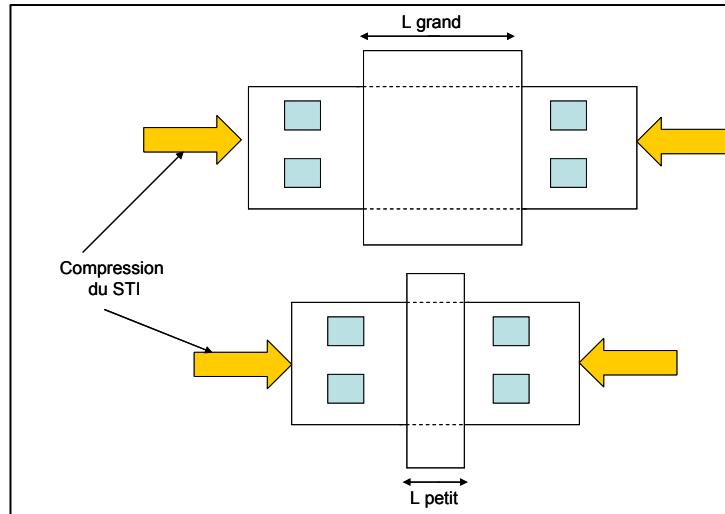

- Figure 3.21 Effet des contraintes du STI sur les parties actives

- Figure 3.22 Structure de test pour surveiller le stress

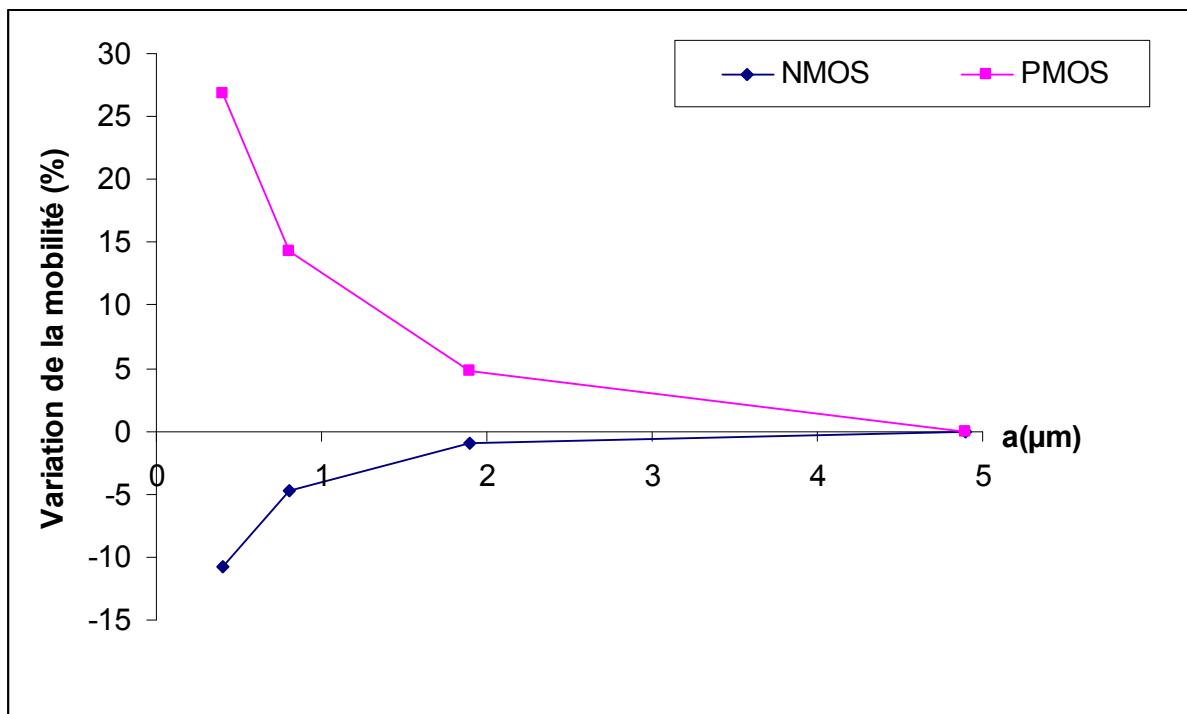

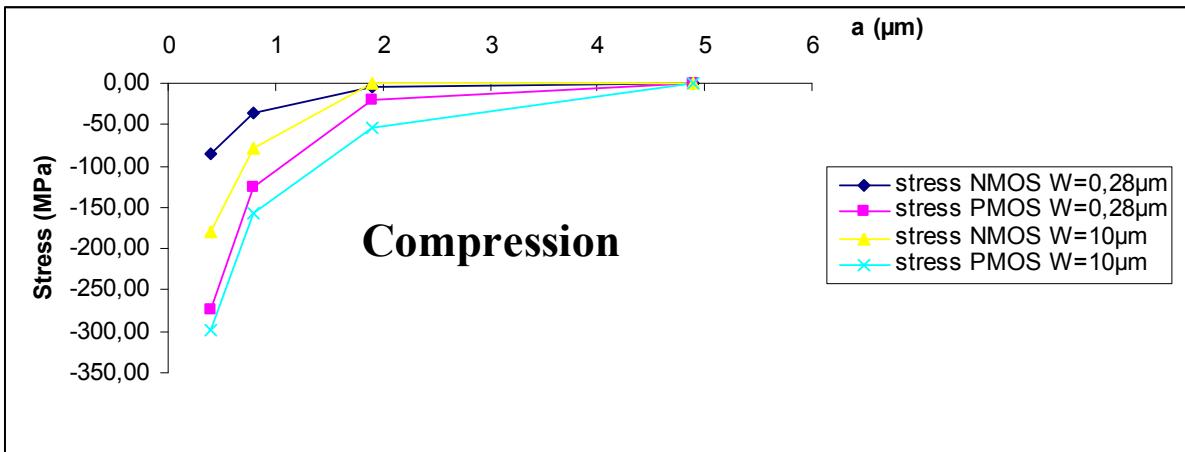

- Figure 3.23 Variation de la mobilité en fonction de la distance « a » pour les transistors NMOS et PMOS dont les dimensions ( $L=0,18\mu m$  et  $W=0,28\mu m$ ) par rapport à une référence non stressée mécaniquement.

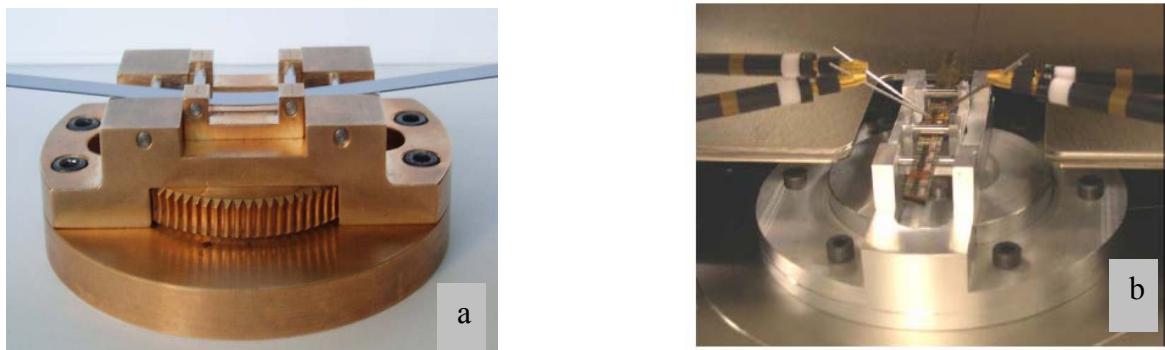

- Figure 3.24 Dispositif expérimental : a) Machine de flexion b) mesures de flexion 4 points

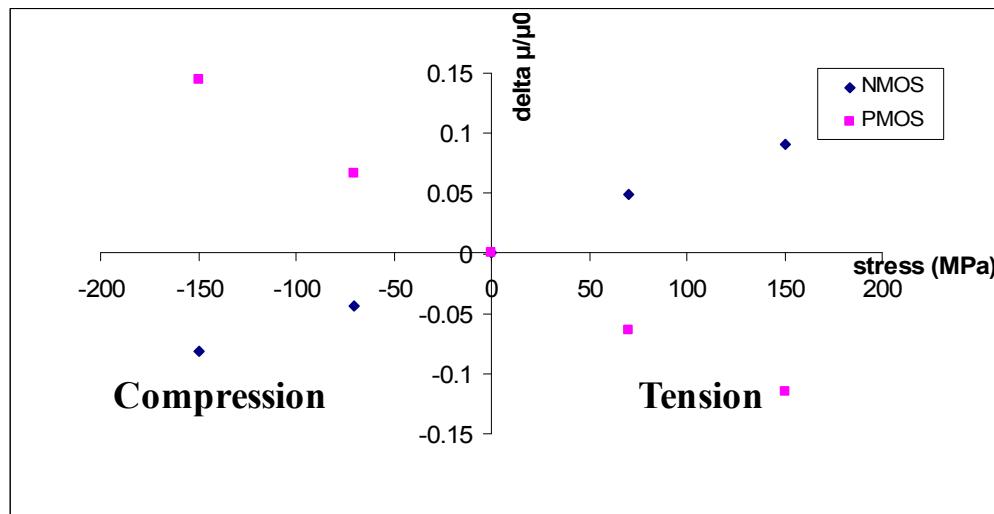

- Figure 3.25 Variation de la mobilité en fonction de la contrainte appliquée

- Figure 3.26 Représentation de l'orientation de champ électrique et la contrainte appliquée

- Figure 3.27 Extraction de niveaux de contraintes en fonction de la distance « a » pour les transistors NMOS & PMOS

- Figure 3.28 Représentation d'un transistor contraint dans les 3 directions (X,Y,Z).

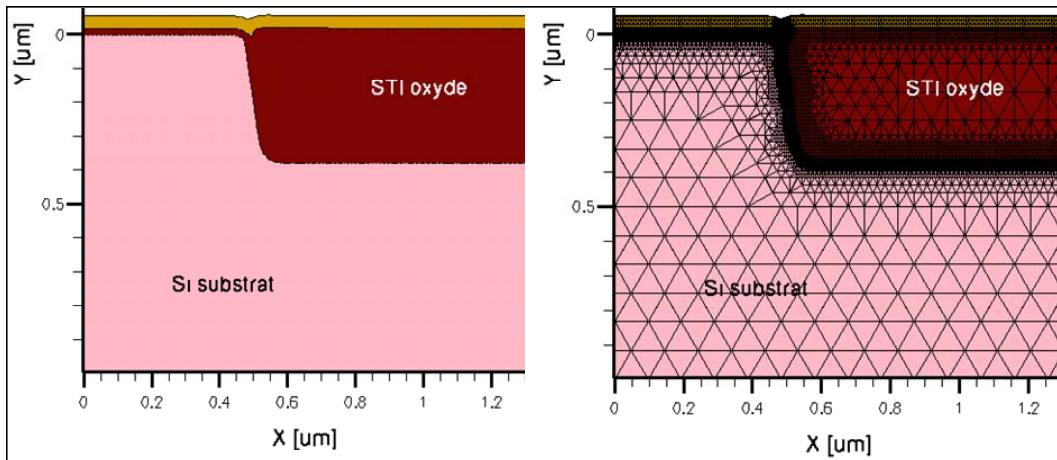

- Figure 3.29 Structure de base pour la simulation de la contrainte mécanique, utilisation du maillage adaptatif.

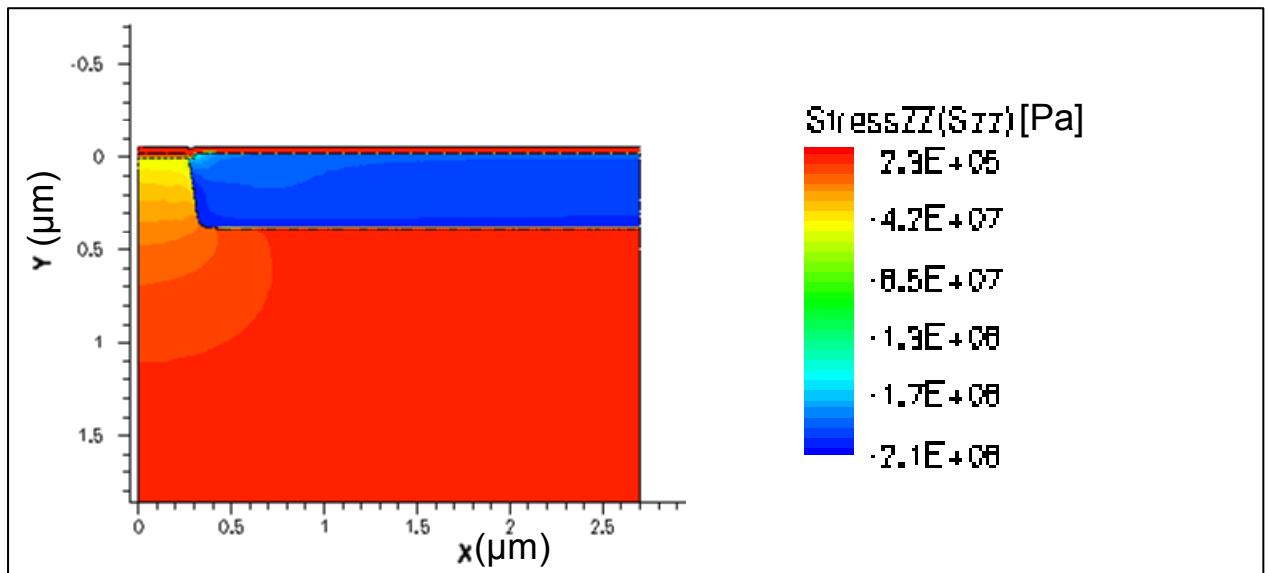

- Figure 3.30 Répartition du stress dans la zone active pour une valeur de «  $a=0.2\mu m$  »

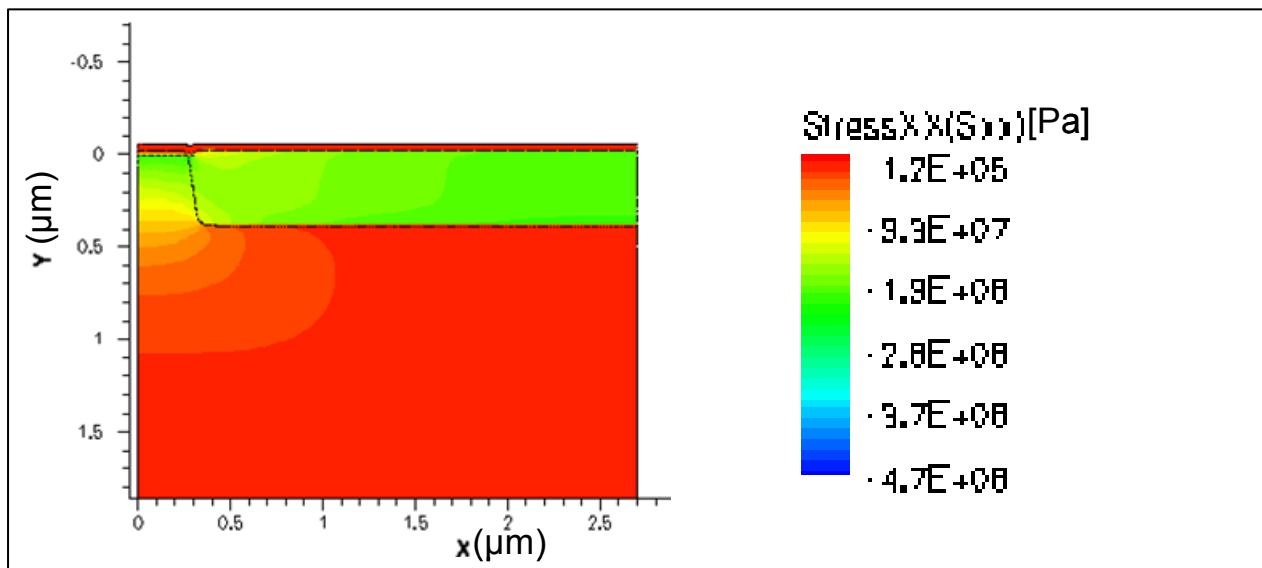

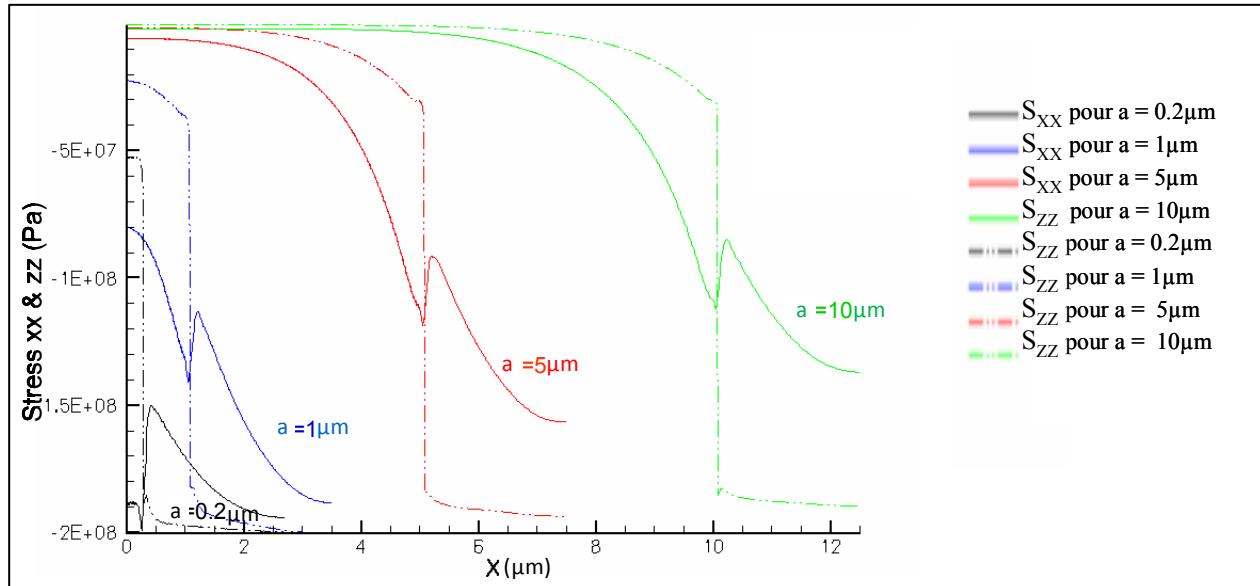

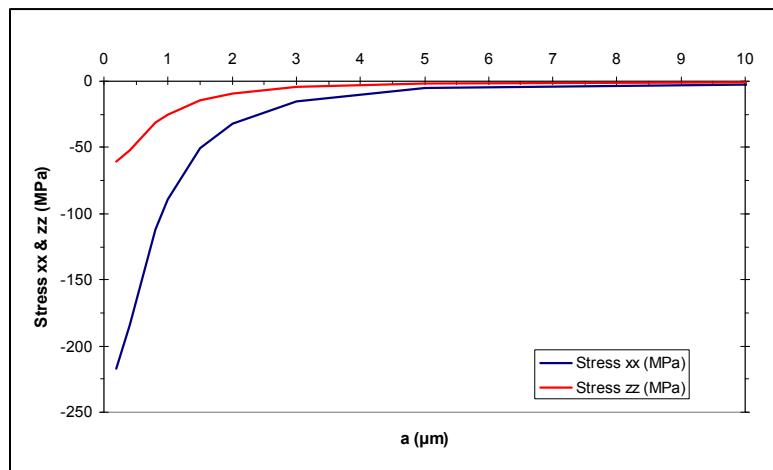

- Figure 3.31 Représentation de stress en fonction de la longueur (suivant la direction x du canal) pour différentes valeurs de « a » au milieu du canal.

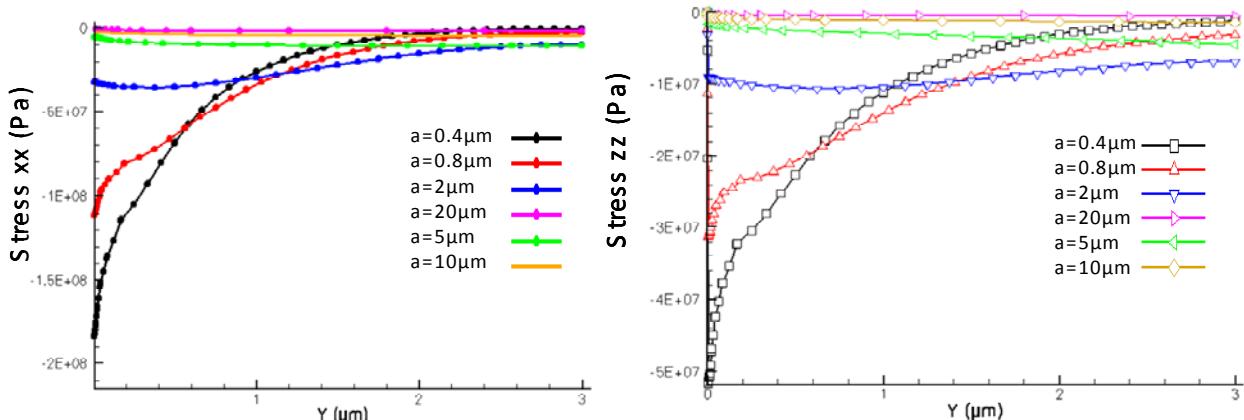

- Figure 3.32 Représentation de stress en fonction de la profondeur de tranchée

- Figure 3.33 Variation du niveau des contraintes en fonction de la distance « a » pour les transistors NMOS (pour les transistors W=10µm)

- Figure 3.34 Représentation schématique de l'effet des contraintes du STI lorsque nous réduisons la longueur de grille.

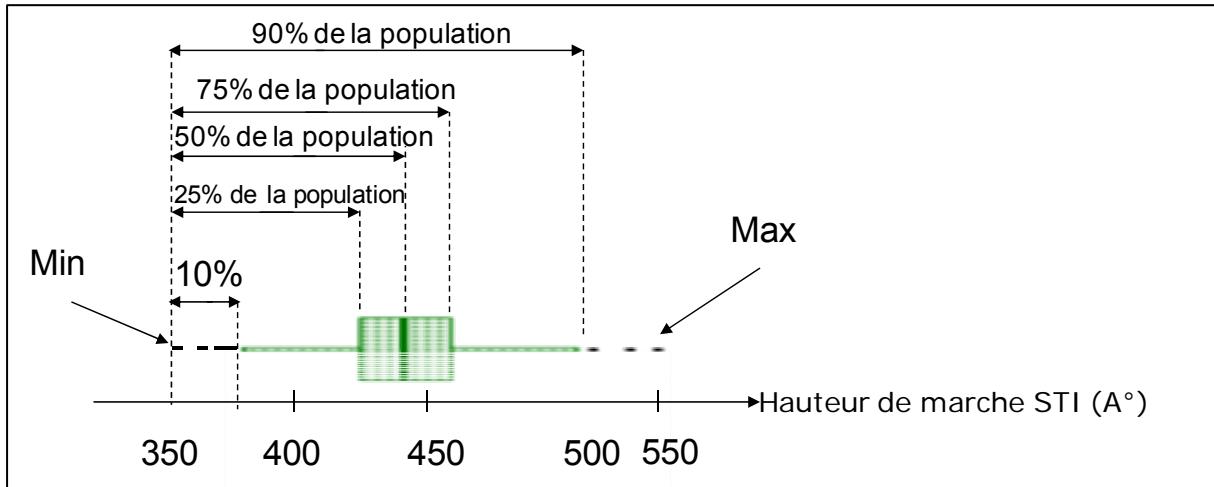

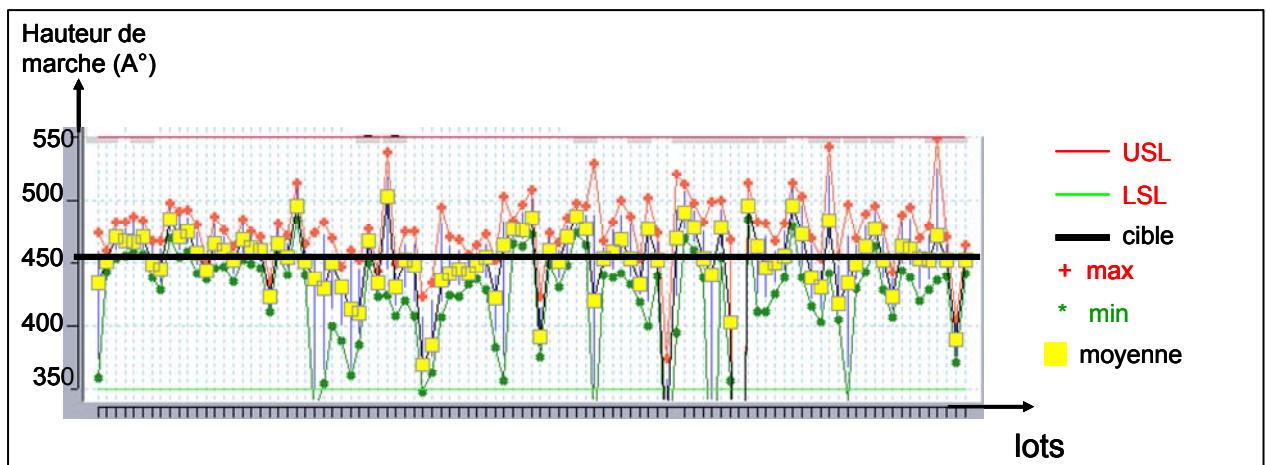

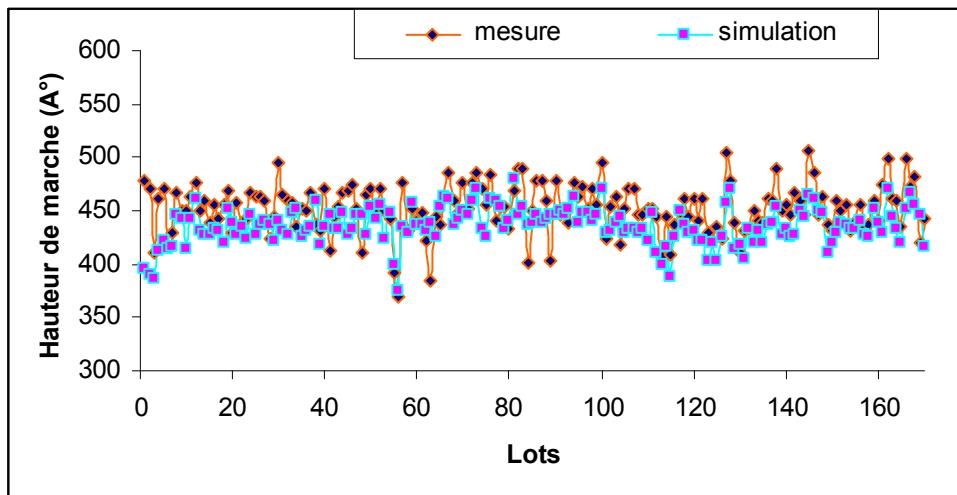

- Figure 4.1 Dispersion de la hauteur de marche de lot à lot

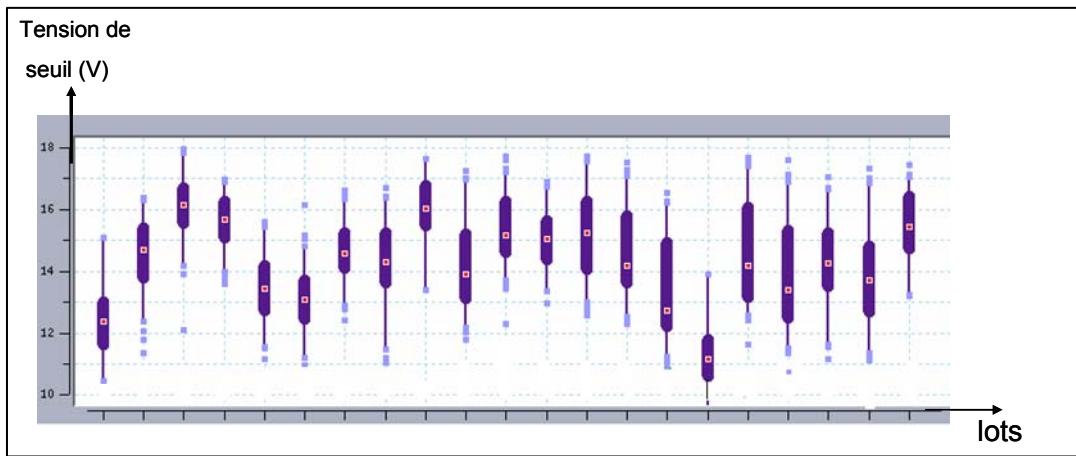

- Figure 4.2 Dispersion de la tension de seuil.

- Figure 4.3 Récapitulatif des opérations de fabrication de la brique STI

- Figure 4.4 Un exemple d'étude de variabilité des paramètres de mesures du module STI

a)de lot à lot b) de plaque à plaque

- Figure 4.5 Boucles de régulations envisagées sur le module STI (Direct STI)

- Figure 4.6 Boucles de régulations envisagées sur le module STI (STI standard)

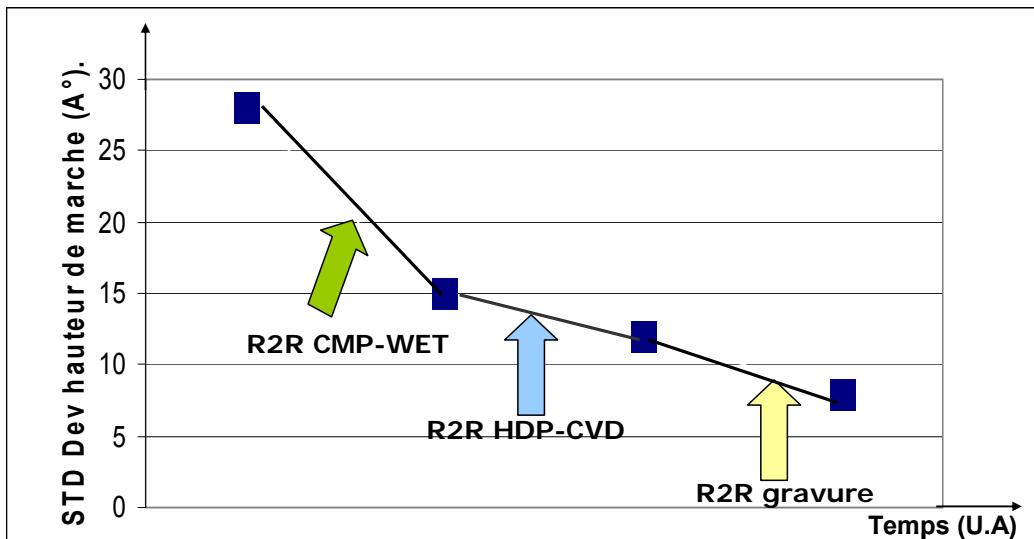

- Figure 4.7 Exemple de simulation sur le gain en dispersion de la hauteur de marche pour le Direct STI suite aux actions proposées.

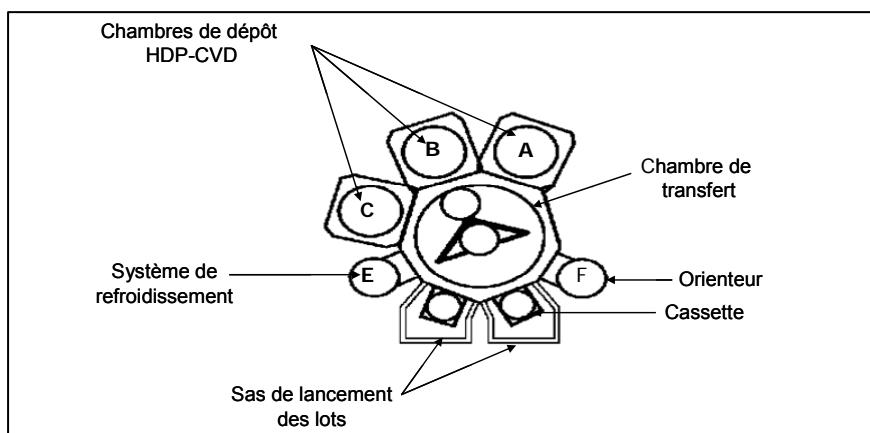

- Figure 4.8 Remplissage des tranchées de STI (dépôt HDP-CVD + TEOS)

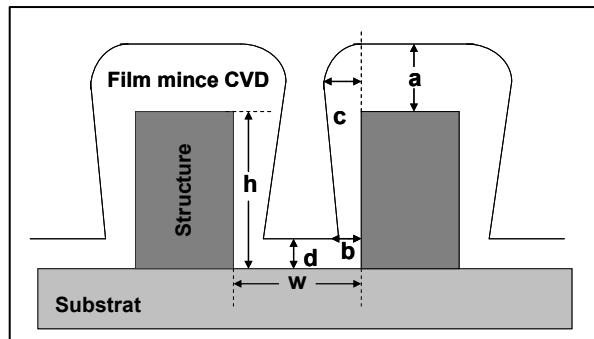

- Figure 4.9 Schématisation des principaux indices géométriques caractérisant le dépôt

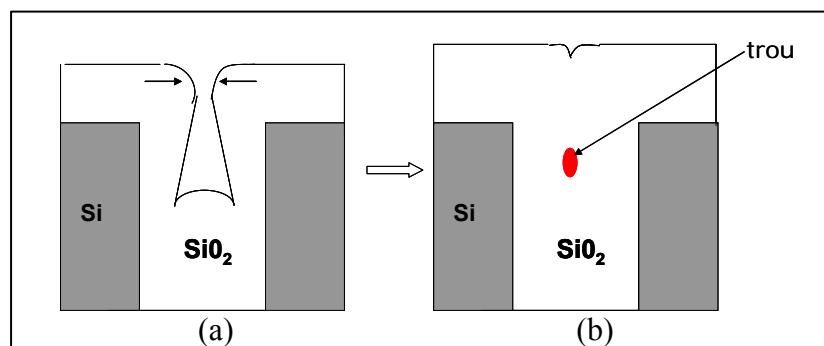

- Figure 4.10 (a)Vue en coupe d'un dépôt PECVD classique (b) apparition d'un trou dans la tranchée

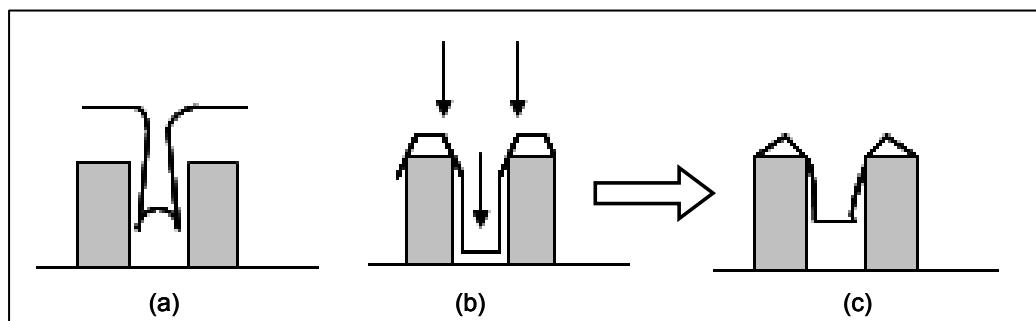

- Figure 4.11 Mécanisme du procédé (a) dépôt (b) gravure (c) dépôt HDP-CVD.

- Figure 4.12 Dépôt d'oxyde en deux étapes

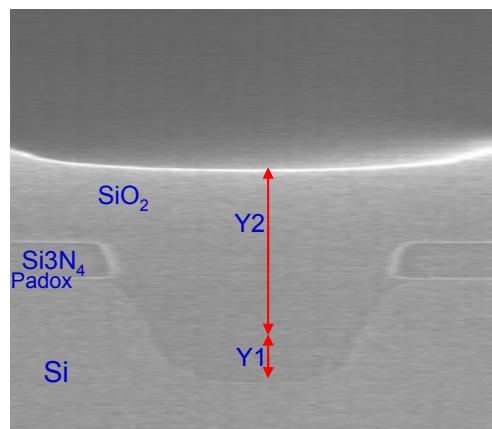

- Figure 4.13 Configuration de l'équipement HDP-CVD.

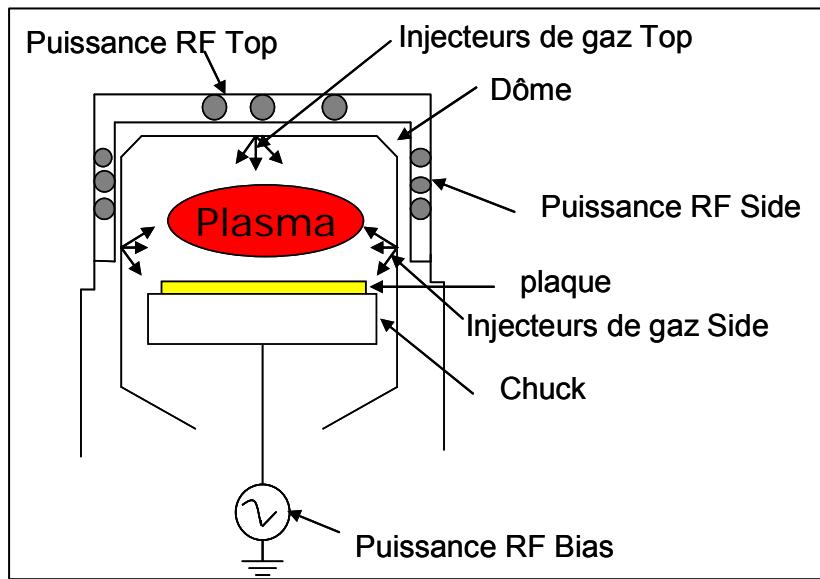

- Figure 4.14 Schéma d'une chambre de dépôt

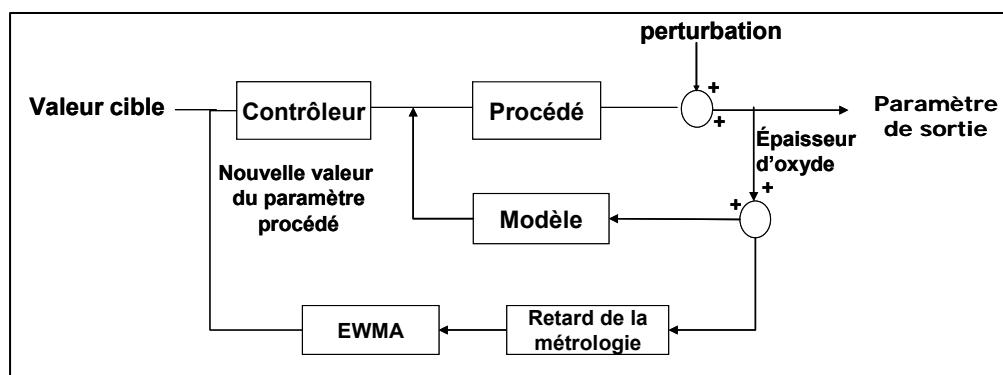

- Figure 4.15 Schématisation de la boucle de régulation R2R

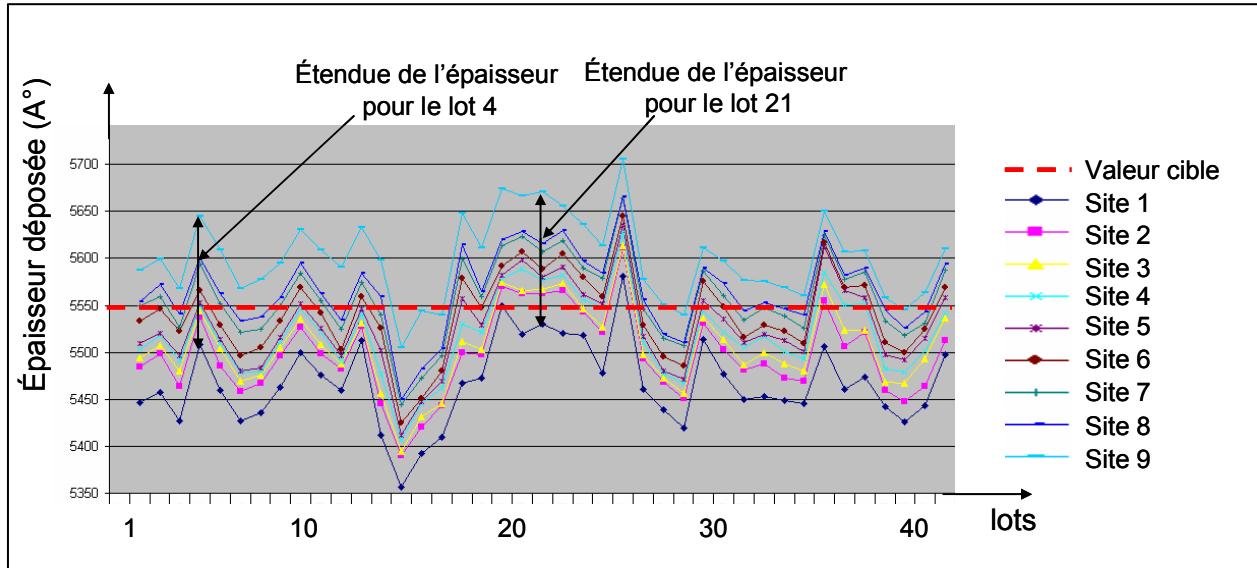

- Figure 4.16 Evolution de l'épaisseur déposée lot à lot pour différents sites de mesures.

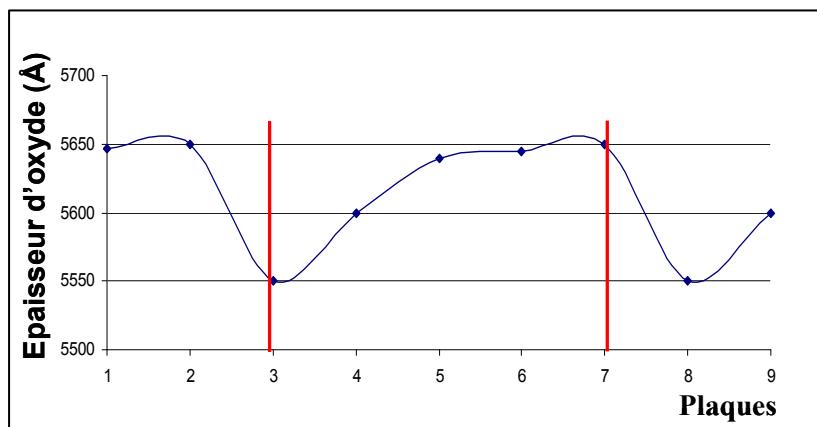

- Figure 4.17 Evolution de l'épaisseur totale pendant les 2 steps.

- Figure 4.18 Evolution de l'épaisseur d'oxyde avant et après le nettoyage de la chambre

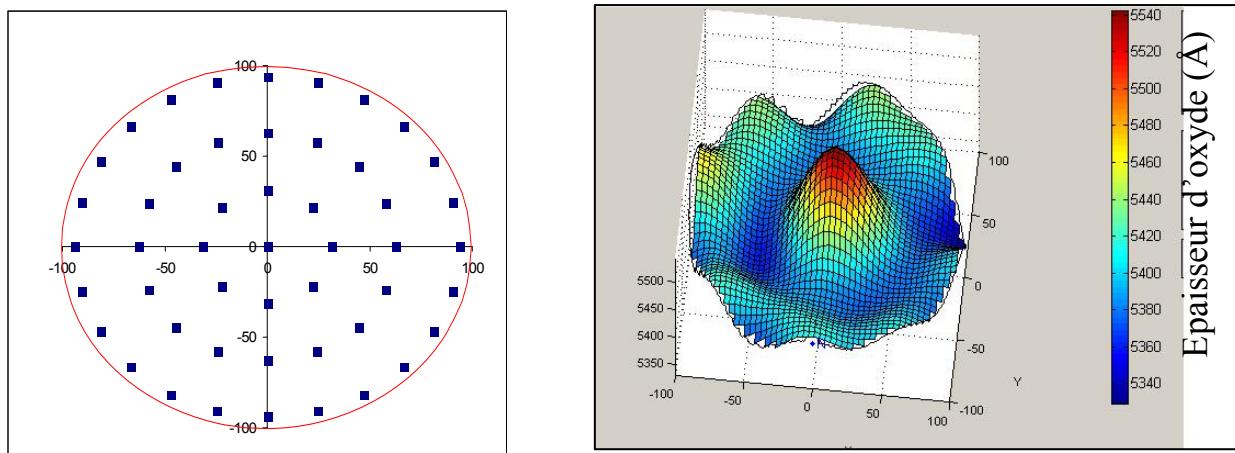

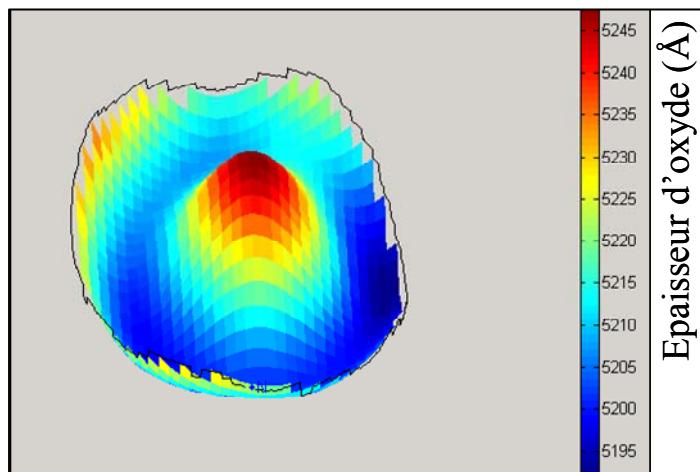

- Figure 4.19 Exemple illustrant la variabilité intra-plaque de l'épaisseur d'oxyde déposé

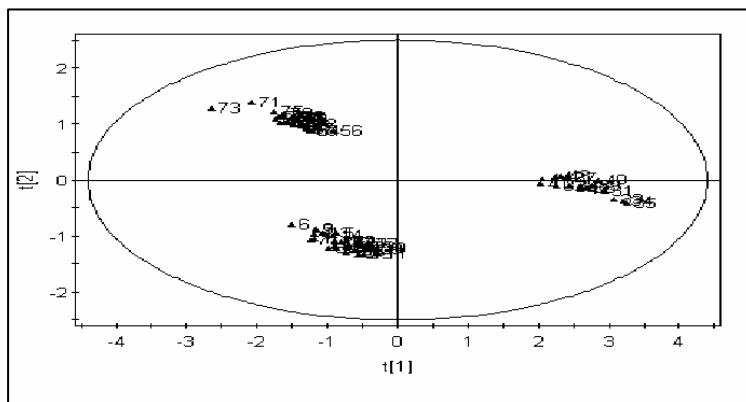

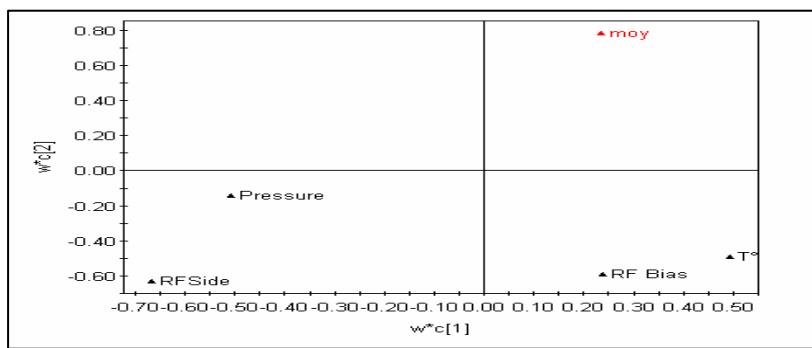

- Figure 4.20 Résultats de l'analyse des composantes principales

- Figure 4.21 Résultats de l'analyse PLS

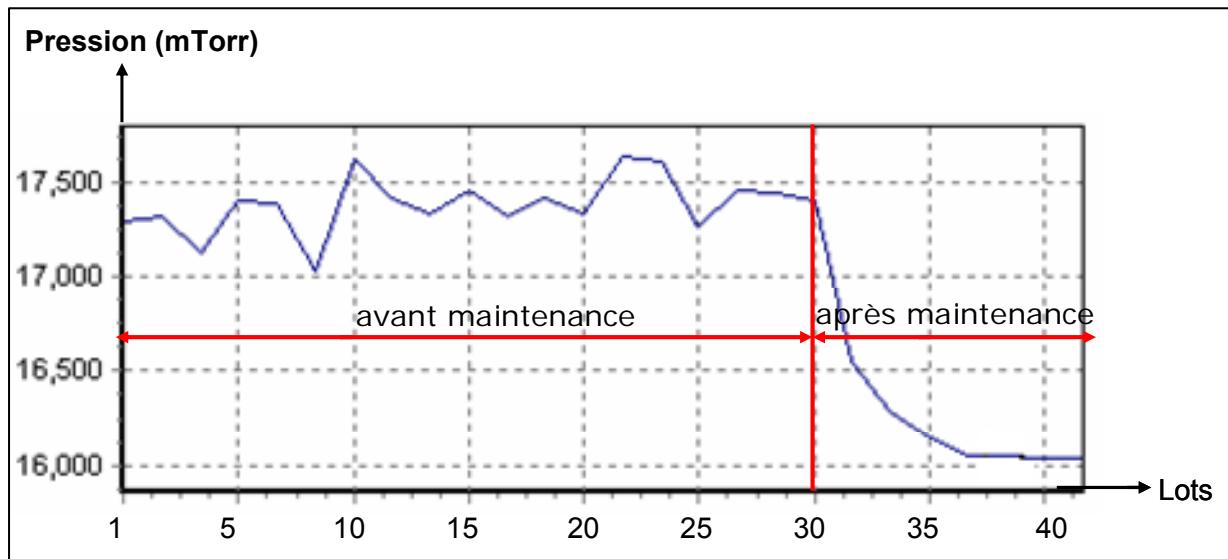

- Figure 4.22 Evolution de la pression avant et après une maintenance préventive

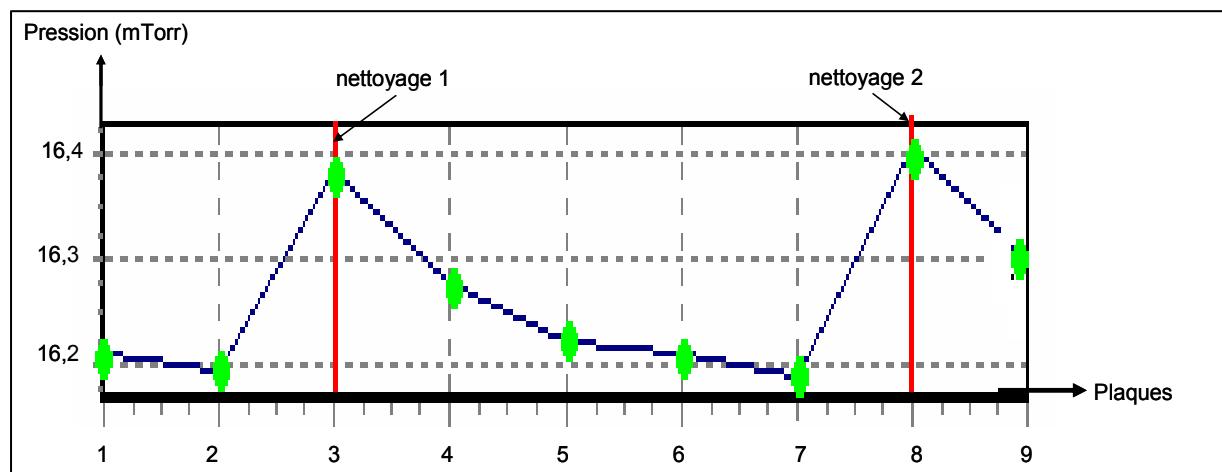

- Figure 4.23 Evolution de la pression avant et après le nettoyage de la chambre

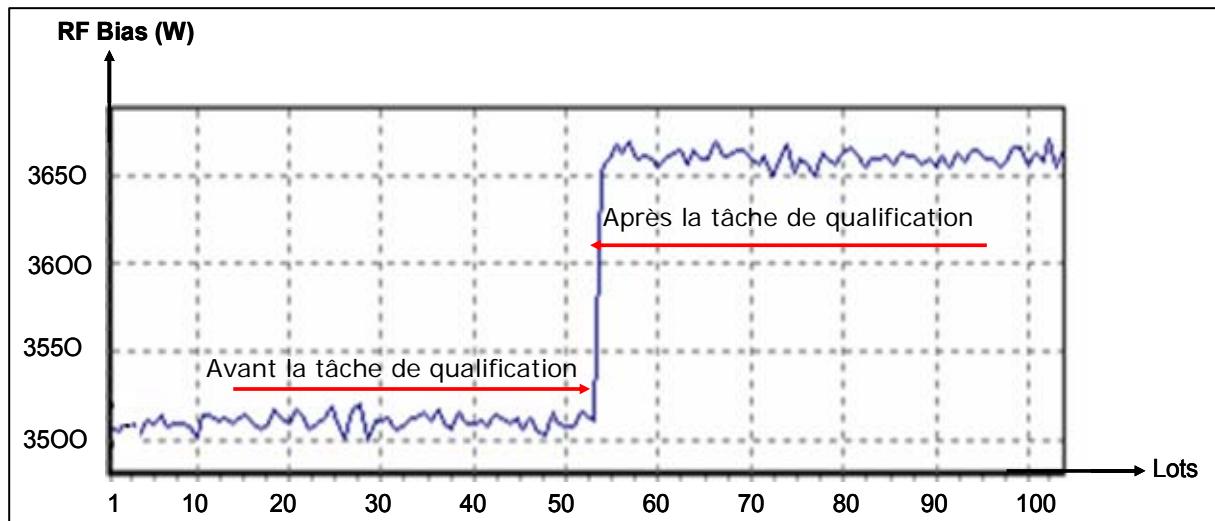

- Figure 4.24 Evolution de la puissance RF Bias avant et après la tache de qualification

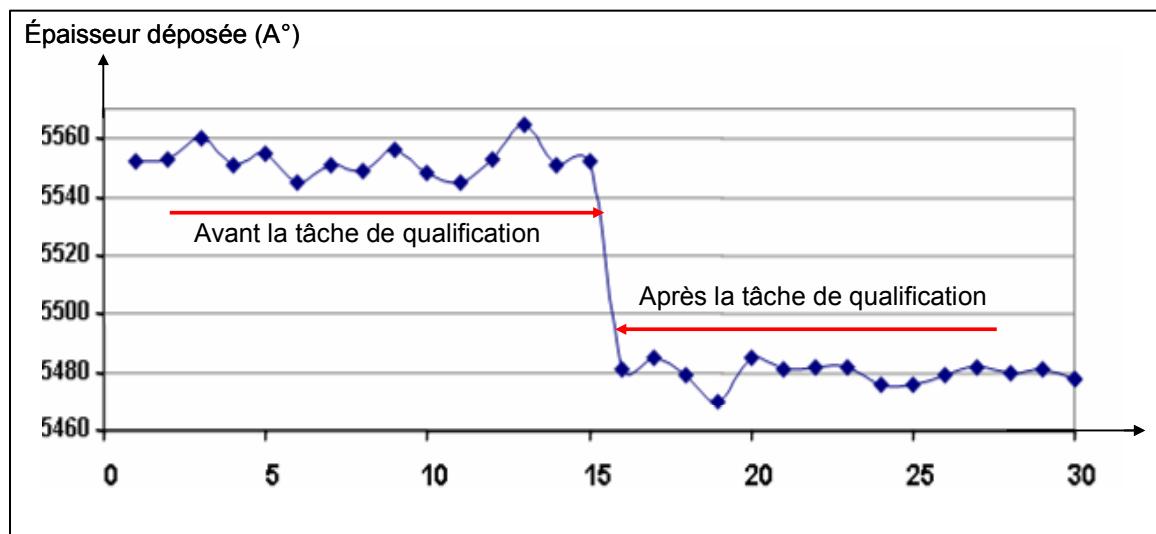

- Figure 4.25 Evolution de l'épaisseur d'oxyde avant et après la tache de qualification

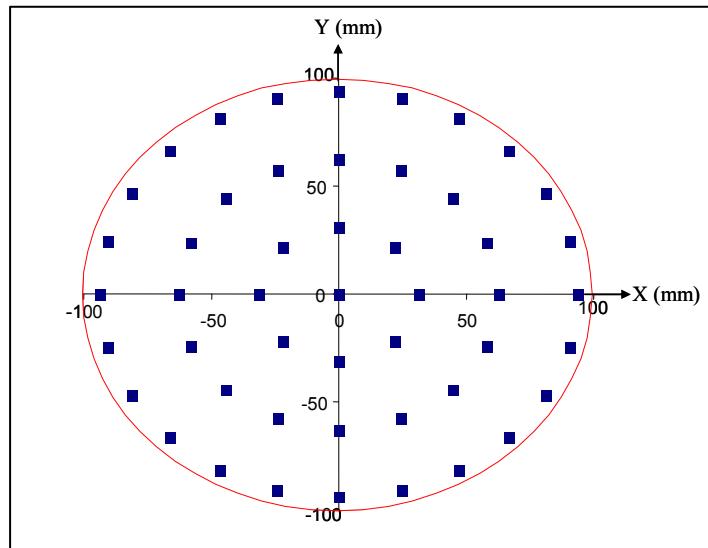

- Figure 4.26 Cartographie de mesures en forme de couronne de 49 points

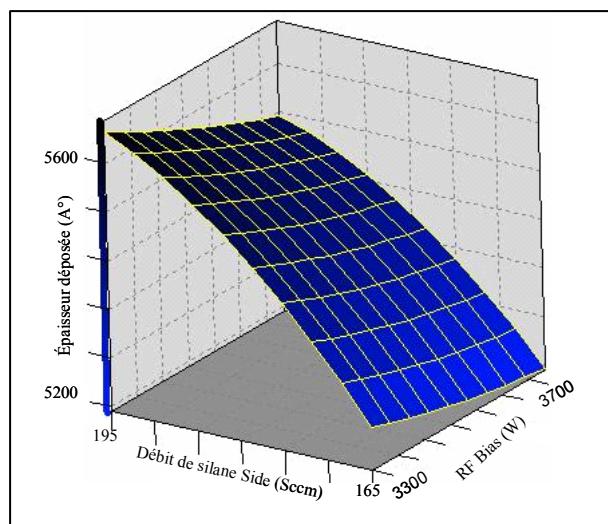

- Figure 4.27 Evolution de l'épaisseur déposée en fonction de la RF Bias et du silane side pour une valeur de silane top de 25 Sccm.

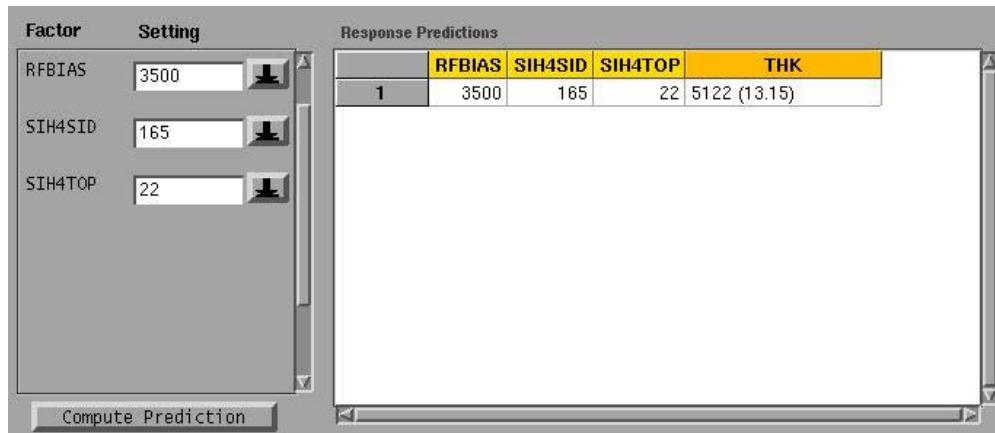

- Figure 4.28 Exemple d'une simulation à l'aide du logiciel SAS.

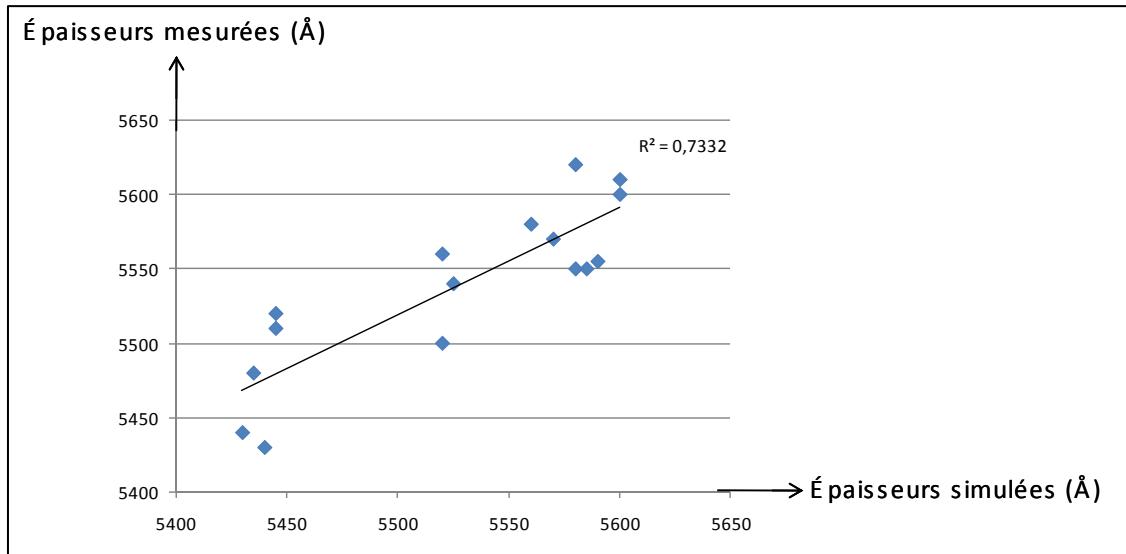

- Figure 4.29 Comparaison entre les données de simulation et les données expérimentales

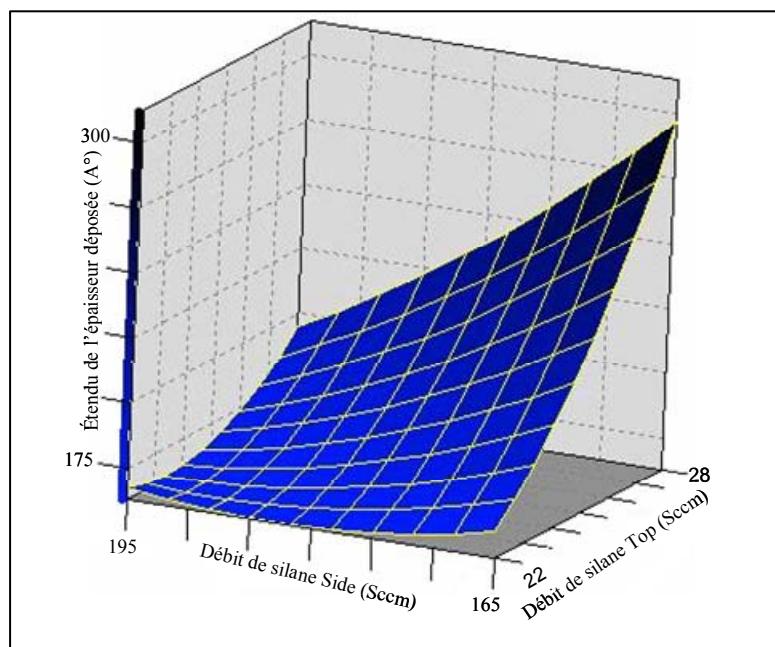

- Figure 4.30 Evolution de l'épaisseur déposée en fonction du Silane Top et du Silane side pour une valeur de la RF Bias de 3500W

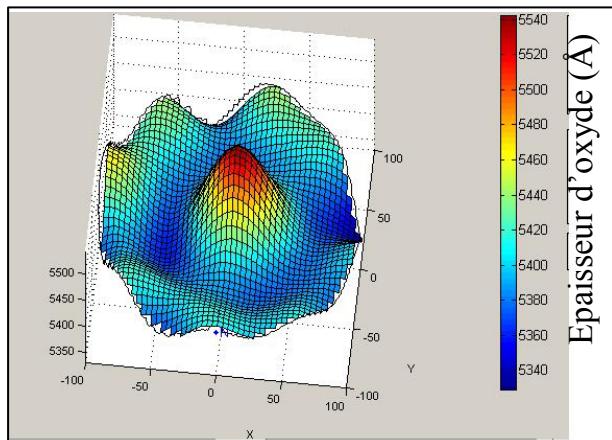

- Figure 4.31 Profil de dépôt en 3-D mesuré en 49 points

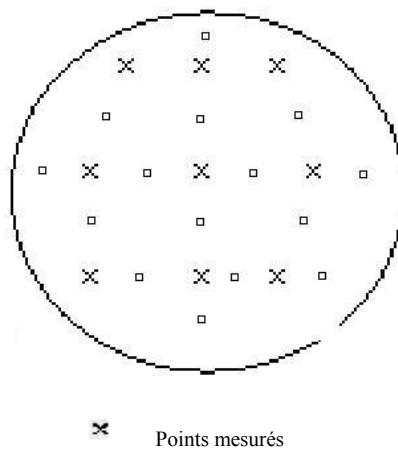

- Figure 4.32 Représentation des points mesurés et points non mesurés

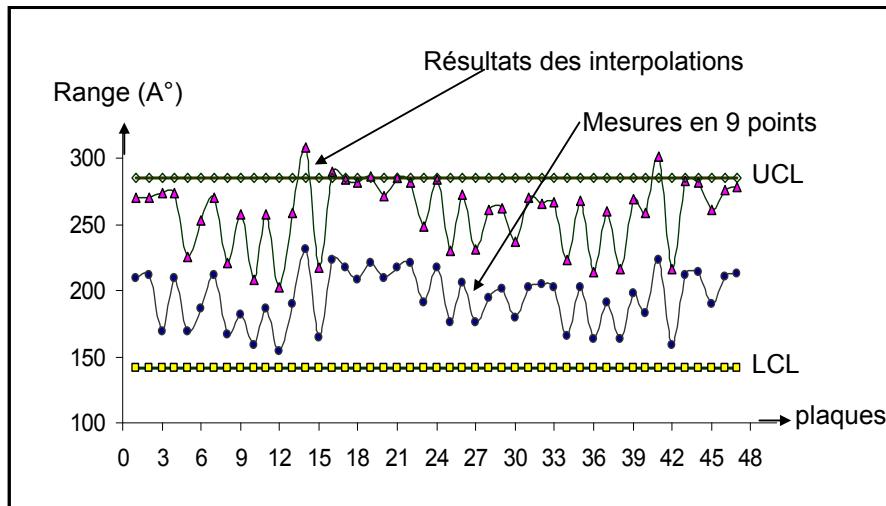

- Figure 4.33 Evolution de l'étendue d'épaisseur avec le temps (mesures issues des 9points de mesures et les résultats de l'interpolation des 9 points de mesures)

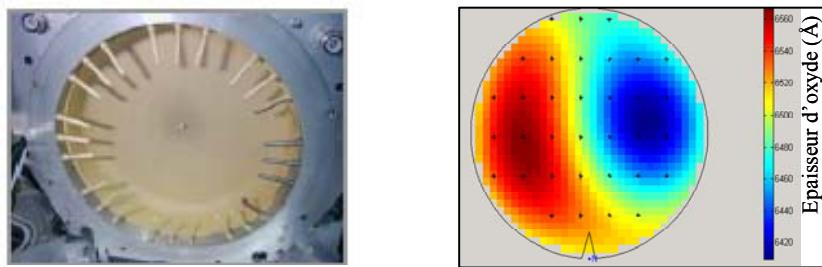

- Figure 4.34 a) La répartition symétrique des injecteurs des gaz. b) profil après dépôt mesuré avec une cartographie de 49 points (présentant le problème d'injecteurs encrassés)

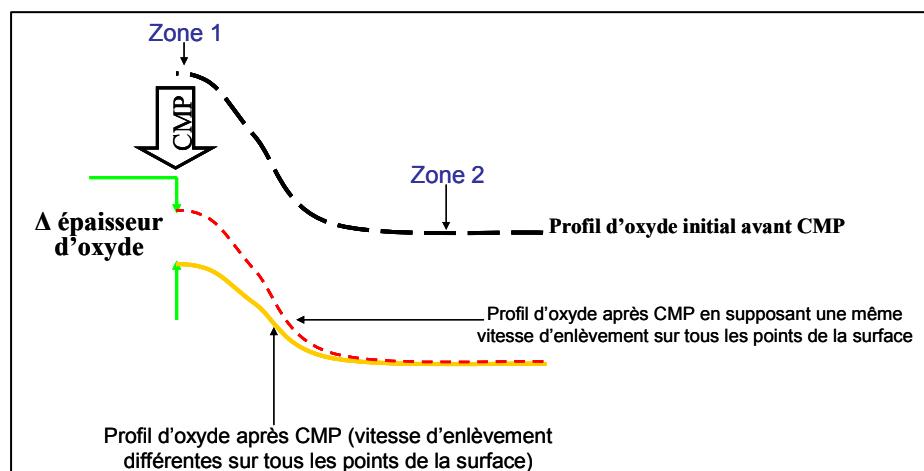

- Figure 4.35 Profils d'oxyde après CMP

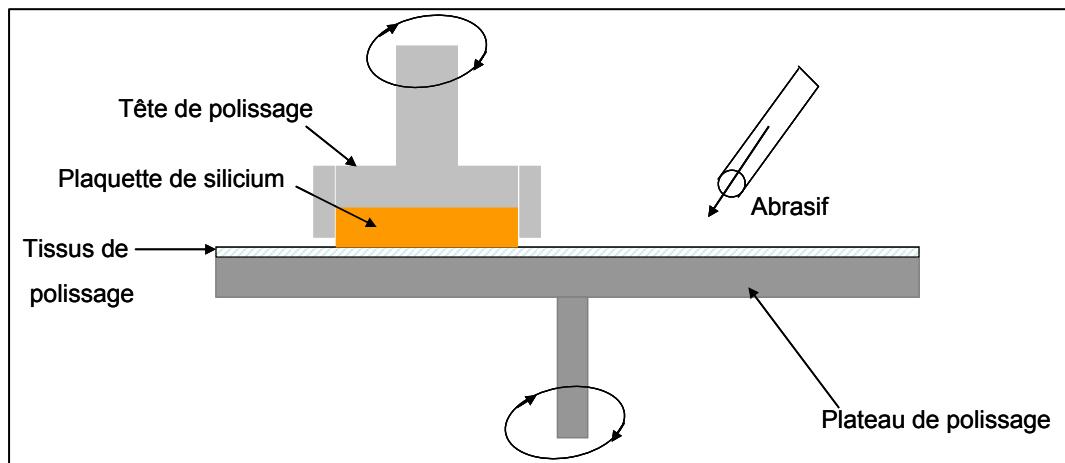

- Figure 4.36 Représentation schématique de la machine de polissage

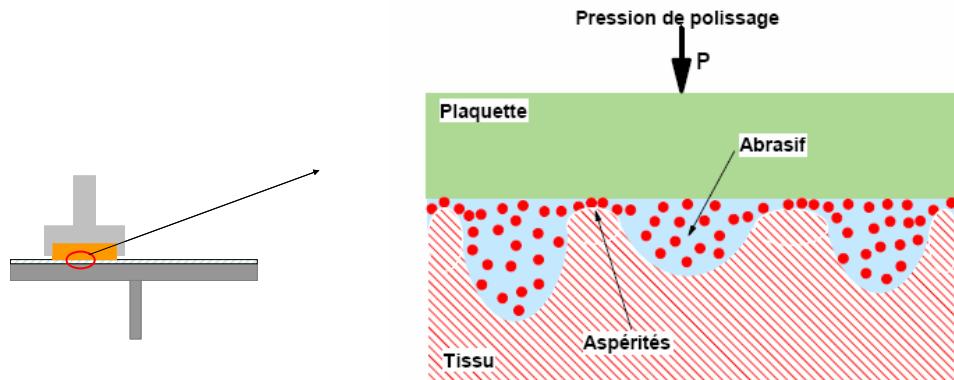

- Figure 4.37 Représentation de l'interface plaquette- tissu de polissage.

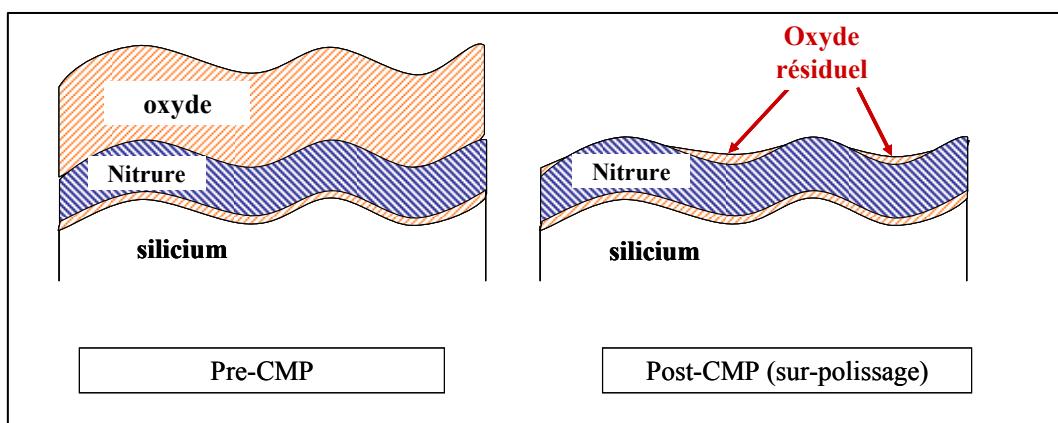

- Figure 4.38 a) Structure d'un film avant CMP b) Après CMP : oxyde résiduel reste dans certains endroits.

- Figure 4.39 Modélisation du procédé CMP

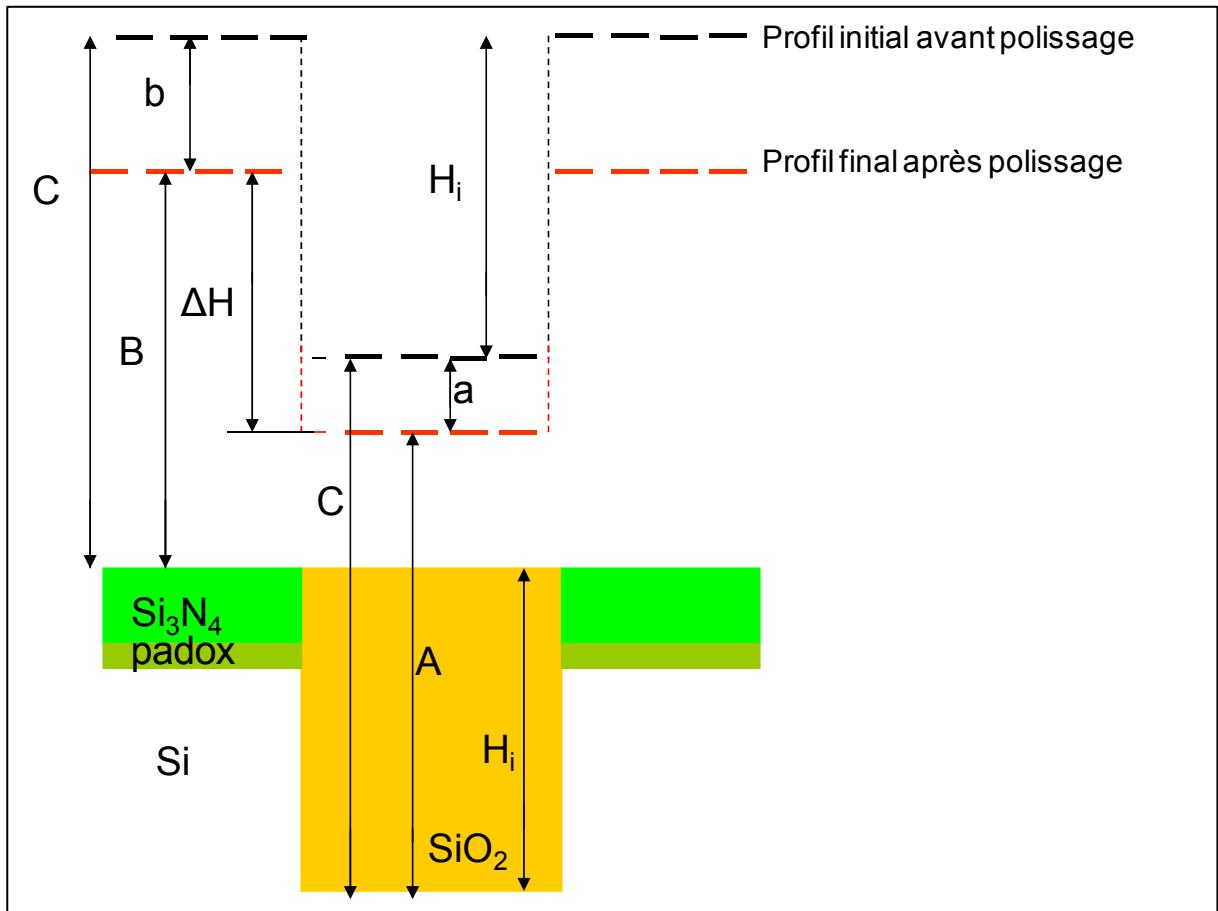

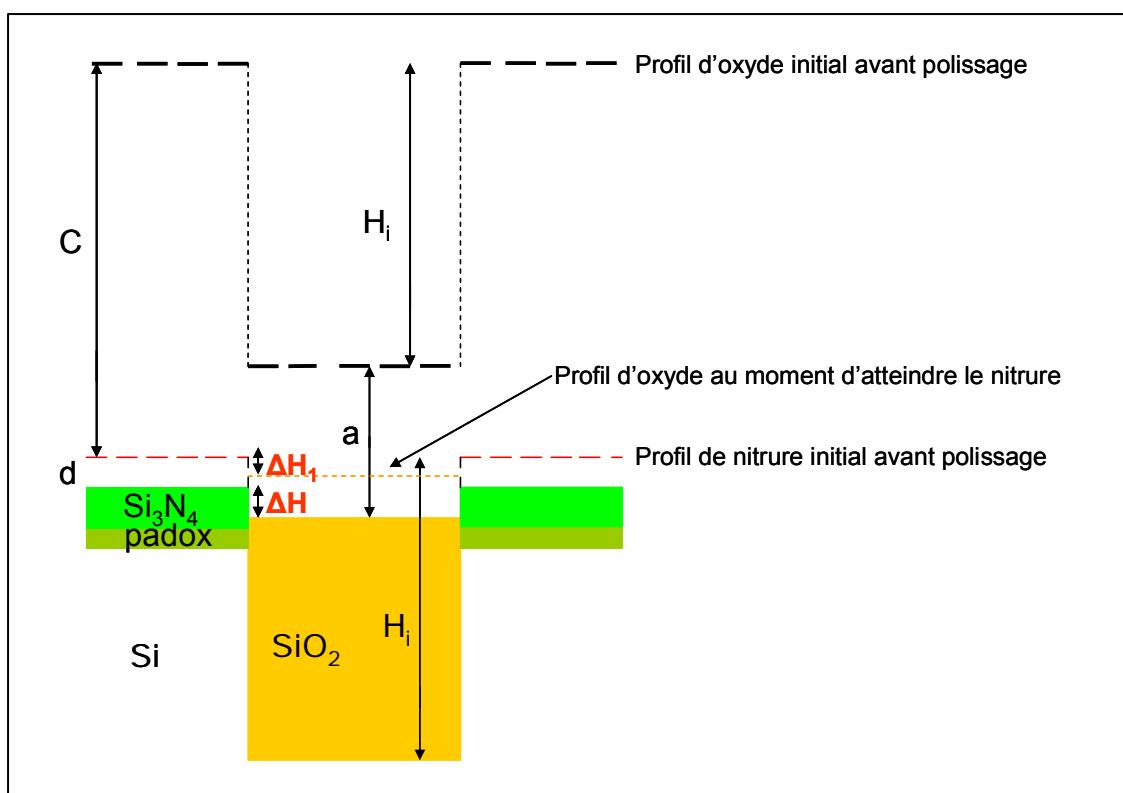

- Figure 4.40 Représentation schématique des marches initiales et finales

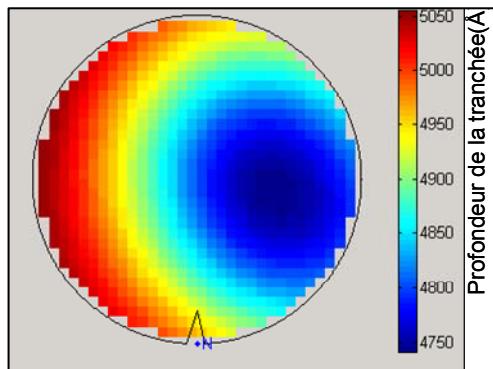

- Figure 4.41 Profil de la profondeur de tranchée après gravure

- Figure 4.42 Hauteur de marche finale après polissage

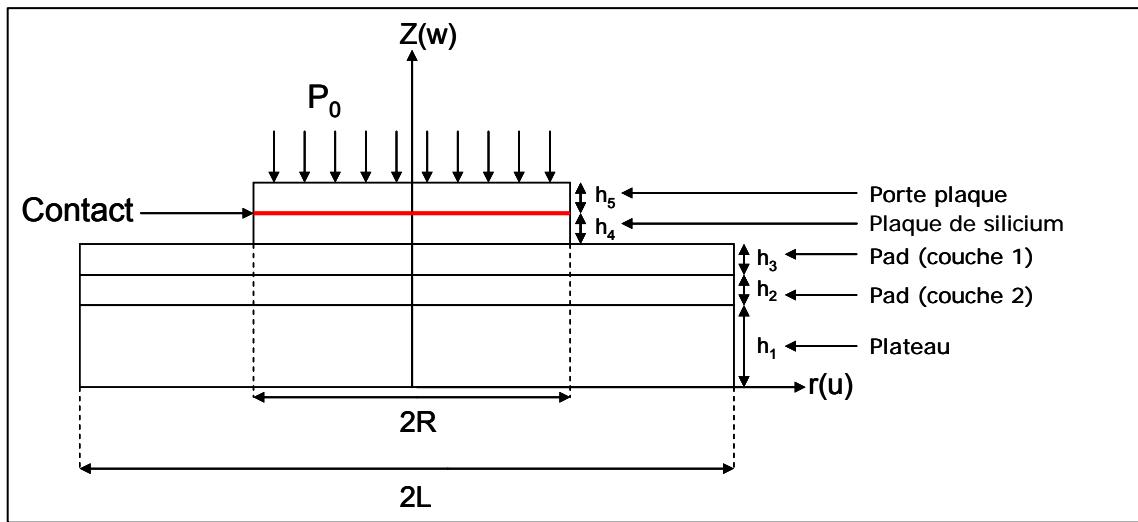

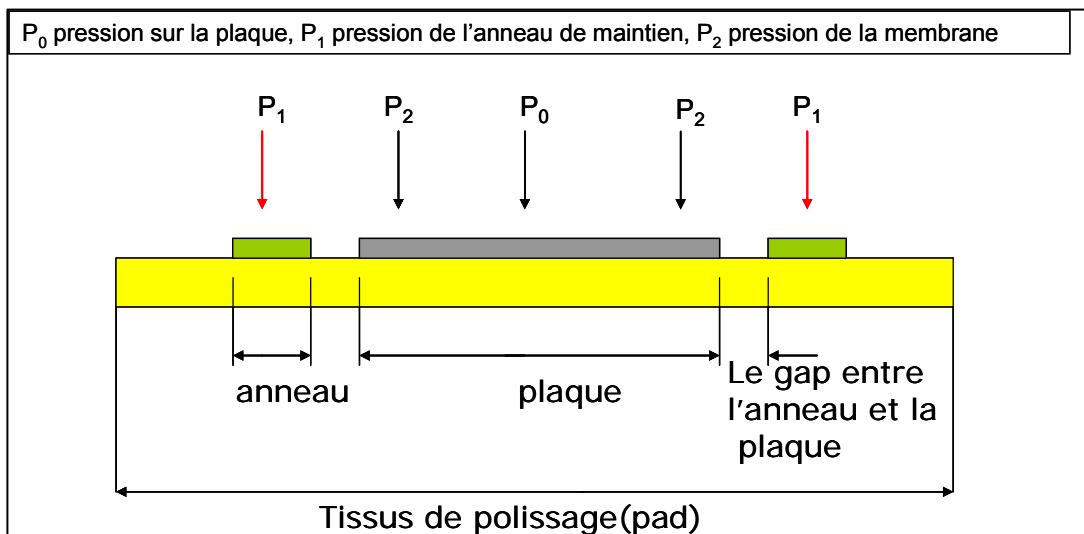

- Figure 4.43 Schématisation de l'interface plaque/pad

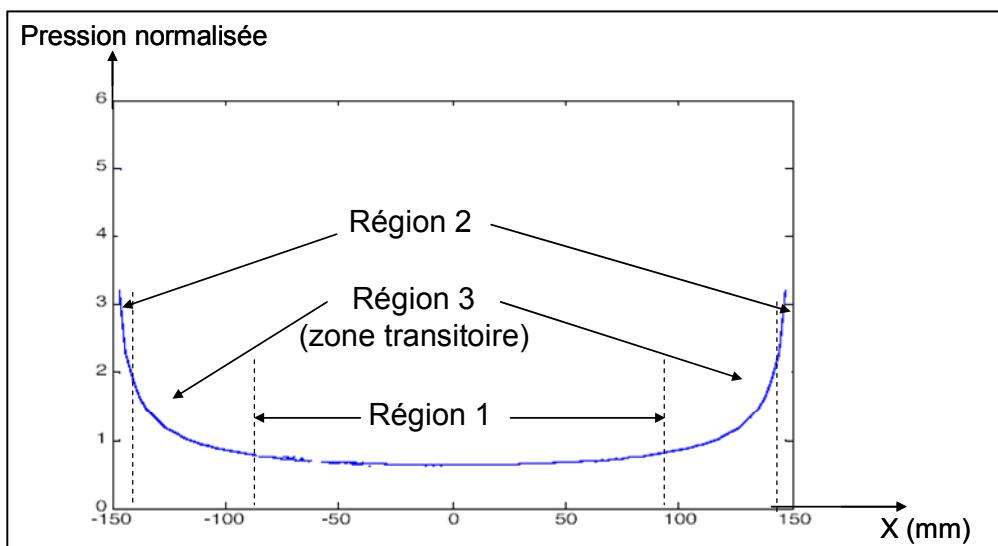

- Figure 4.44 Distribution de la pression à travers la plaque

- Figure 4.45 Coupe d'une machine de polissage CMP

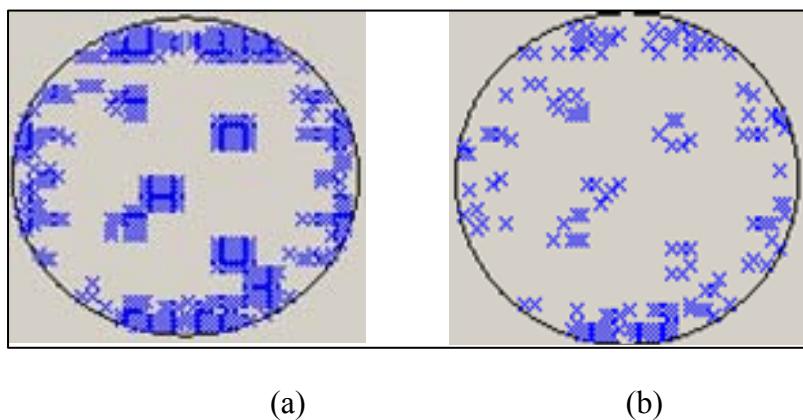

- Figure 4.46 a) cartographie de mesure de 460 points b) cartographie de mesure réduite à 109 points

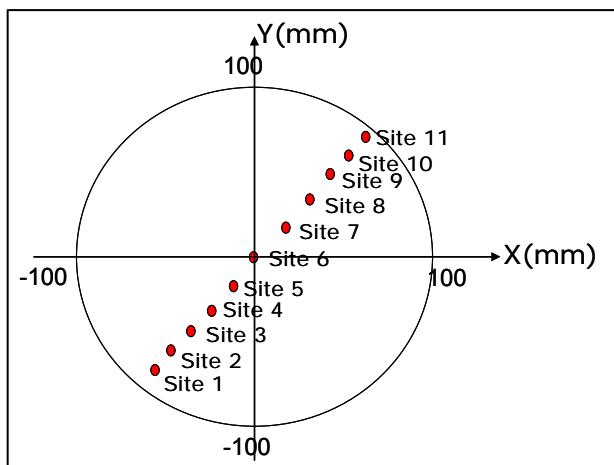

- Figure 4.47 Exemple de cartographie de mesure de type radial des mesures de la hauteur de marche

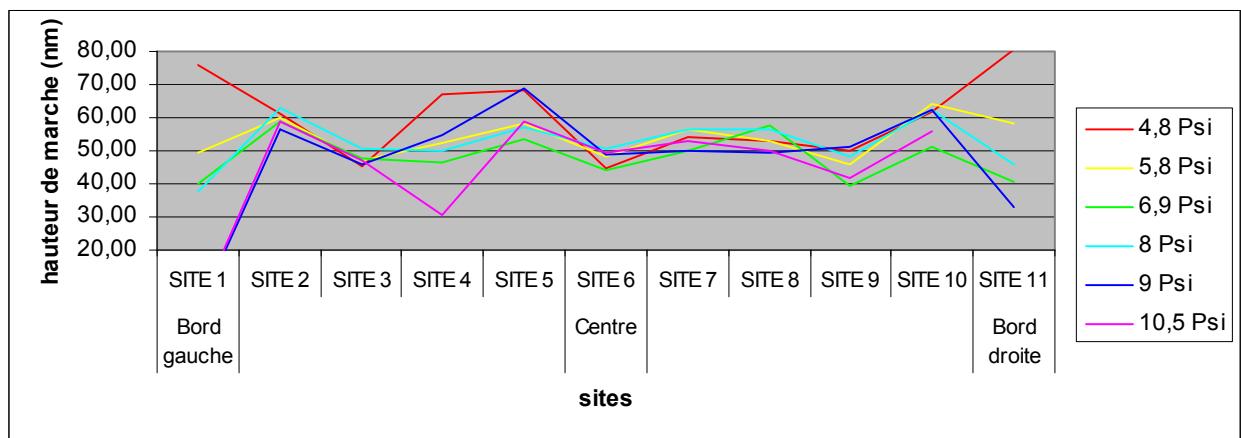

- Figure 4.48 Variation de la hauteur de marche au niveau du produit suivant les valeurs de pression de l'anneau de maintien

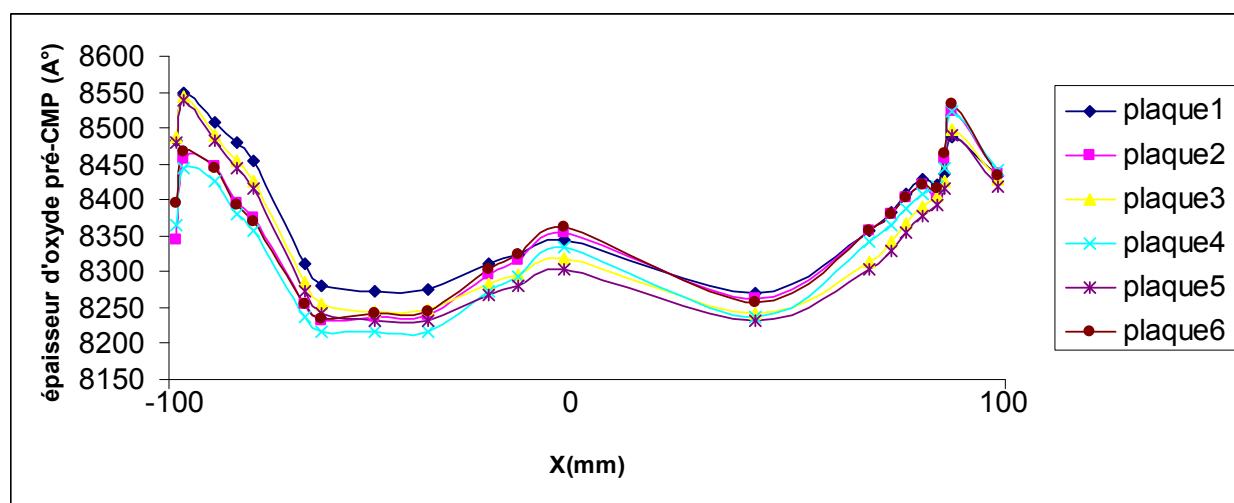

- Figure 4.49 Evolution de l'épaisseur d'oxyde pré- CMP au sein de la plaque

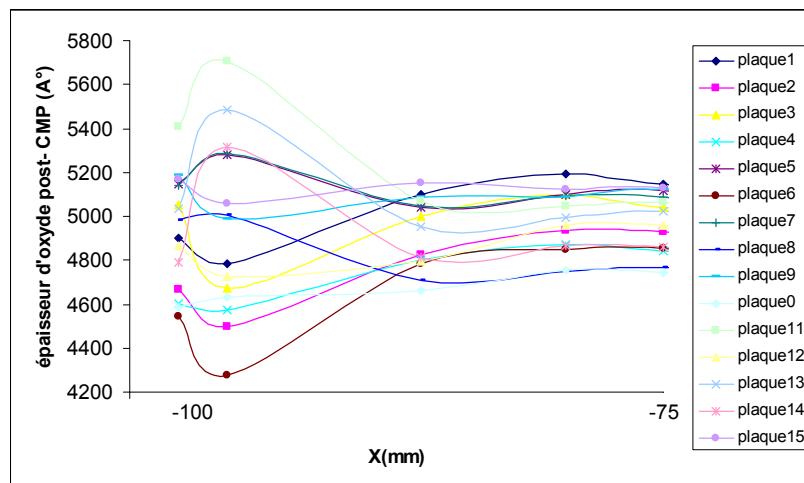

- Figure 4.50 Evolution de l'épaisseur d'oxyde post- CMP au sein de la plaque (sur les 25 derniers mm)

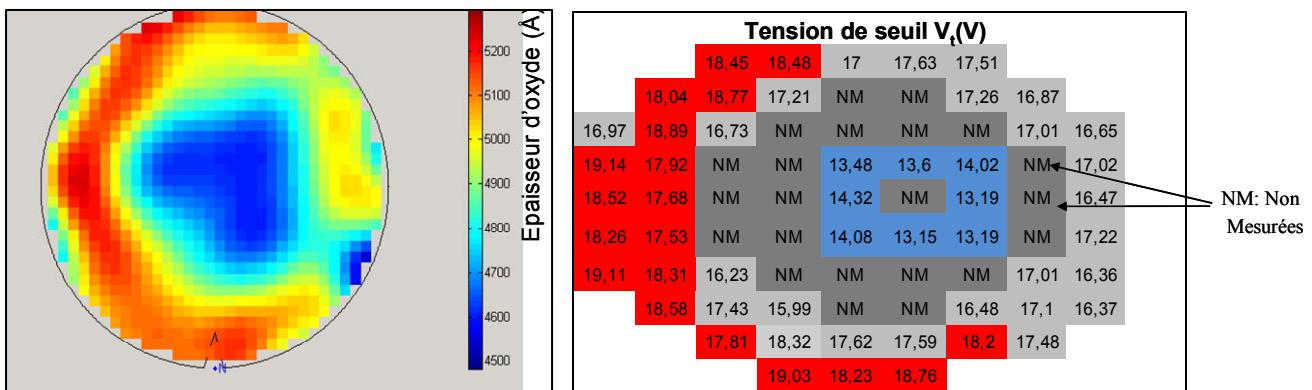

- Figure 4.51 Corrélation entre le profil d'oxyde post CMP et les résultats de test électrique sur le paramètre de tension de seuil

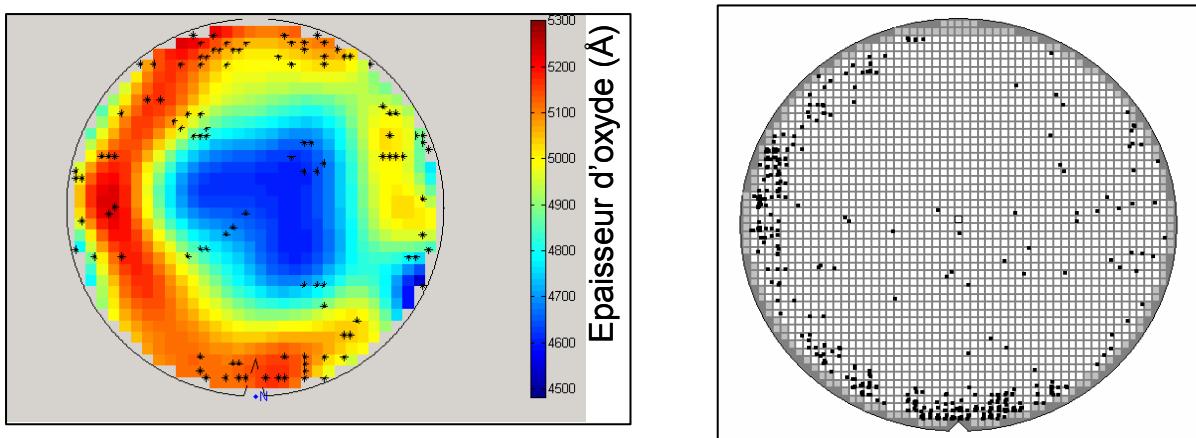

- Figure 4.52 Comparaison de profil d'oxyde après CMP avec le profil de la densité des défauts

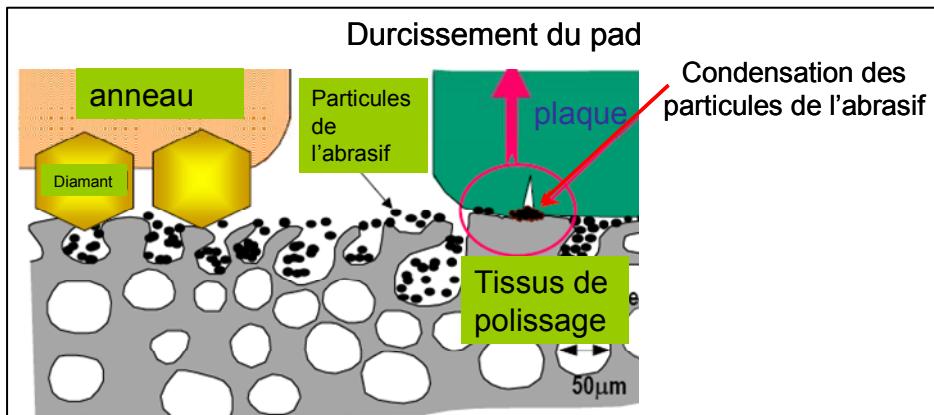

- Figure 4.53 Condensation des particules de l'abrasif dans certaines zones du tissus de polissage en contact avec la plaque

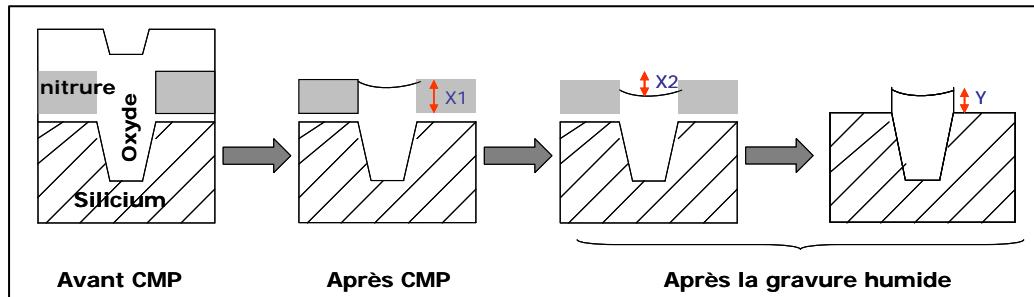

- Figure 4.54 Représentation simplifiée des étapes des procédés STI

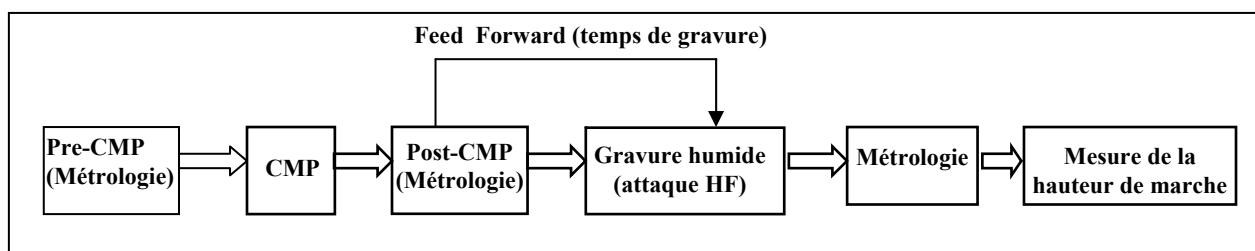

- Figure 4.55 Schéma synoptique de la boucle CMP- gravure humide

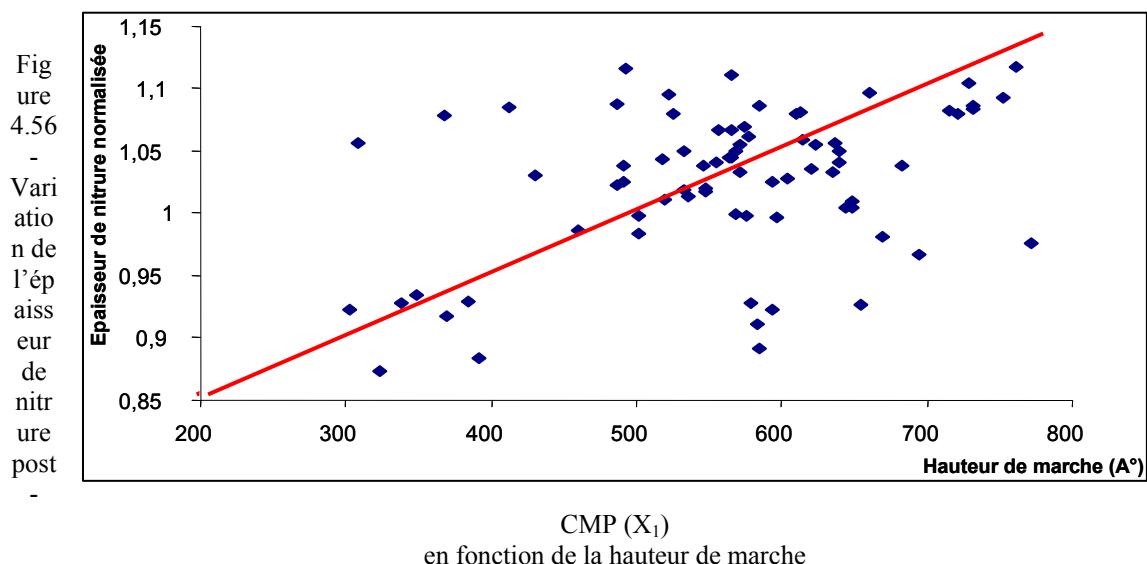

- Figure 4.56 Variation de la hauteur de marche en fonction de l'épaisseur de nitrure post-CMP

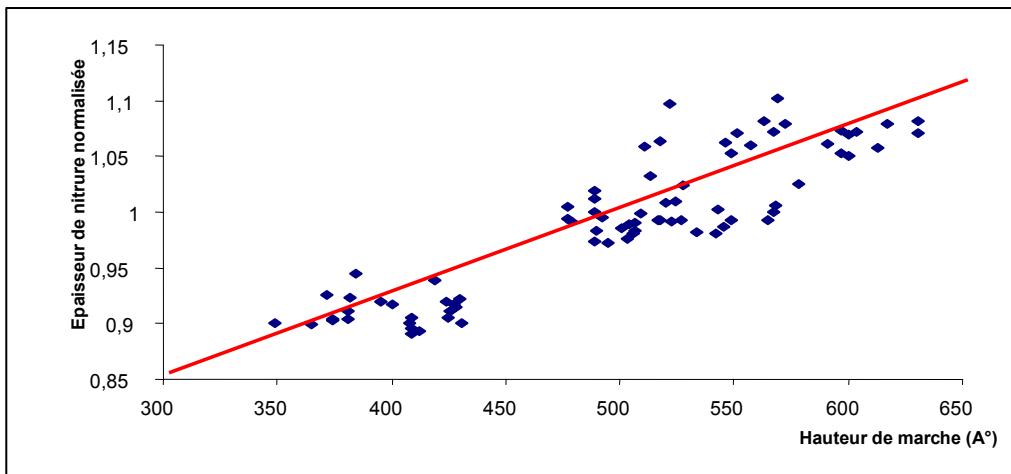

- Figure 4.57 Variation de la hauteur de marche en fonction de l'épaisseur de nitrure post-CMP ( $X_1$ ) dans le cas du direct STI

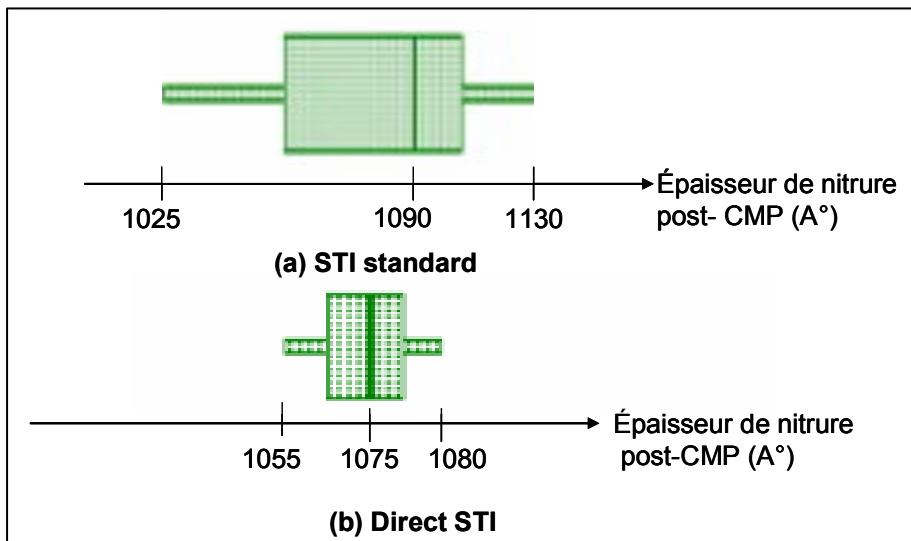

- Figure 4.58 Comparaison de deux structures « box plot » représentant la distribution de l'épaisseur de nitrure post-CMP à travers la plaque dans le cas du STI standard et du Direct STI

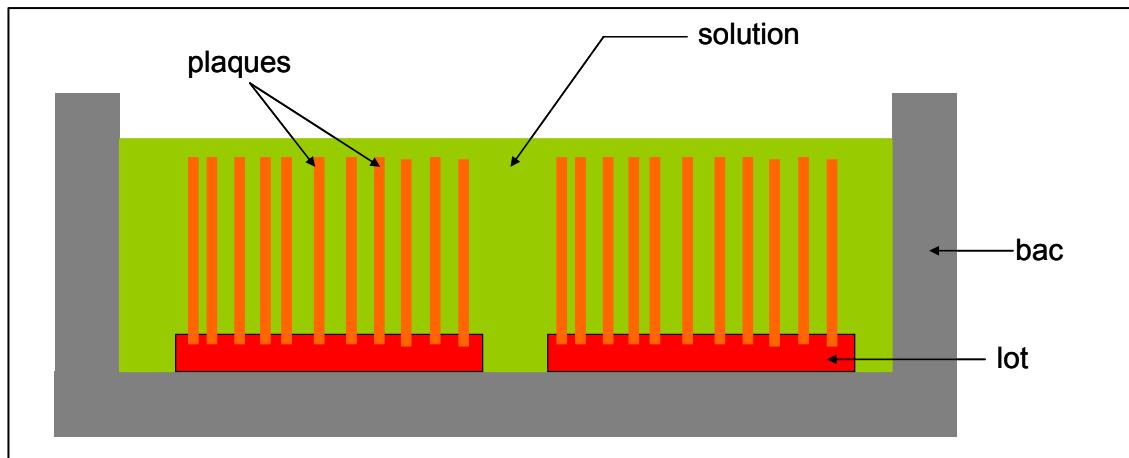

- Figure 4.59 Gravure de deux lots par voie humide

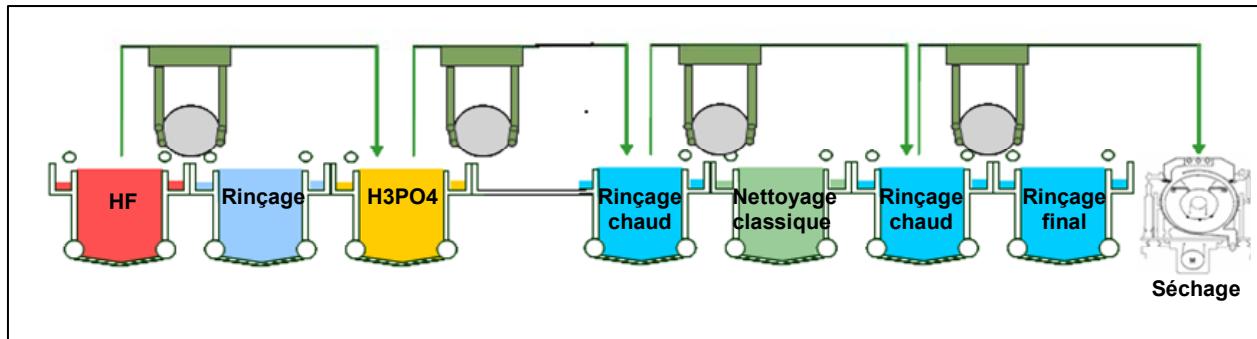

- Figure 4.60 Les différents bains constituant la machine de gravure humide

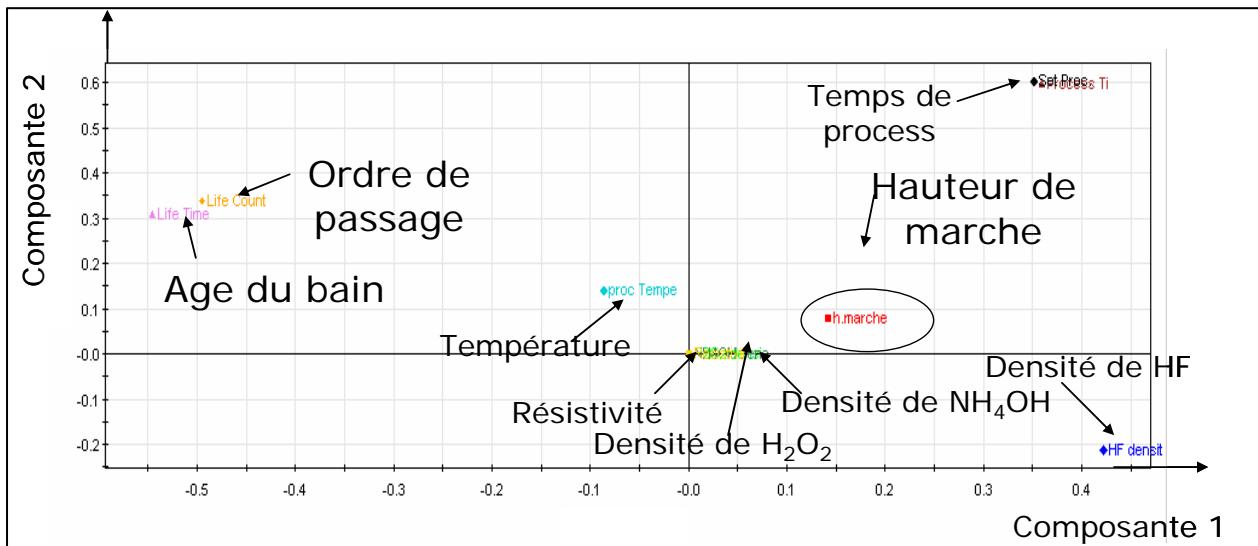

- Figure 4.61 Résultats de l'analyse PLS

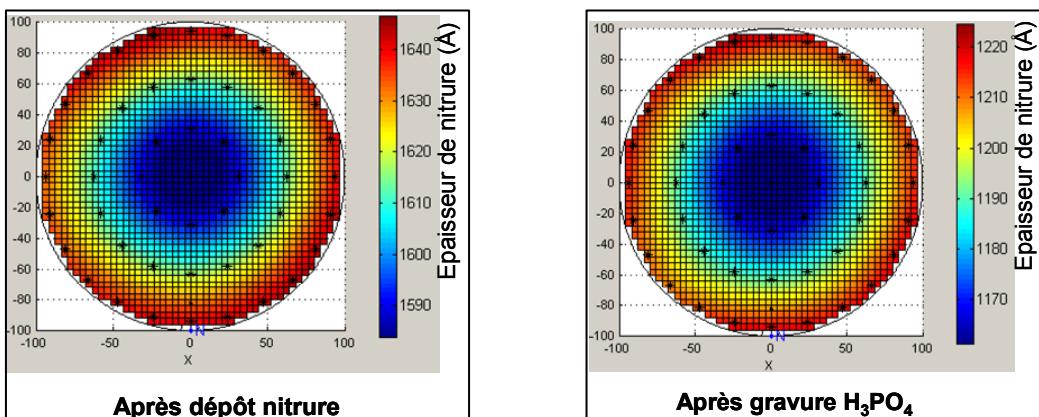

- Figure 4.62 Comparaison des profils : a)après CMP b) après gravure humide

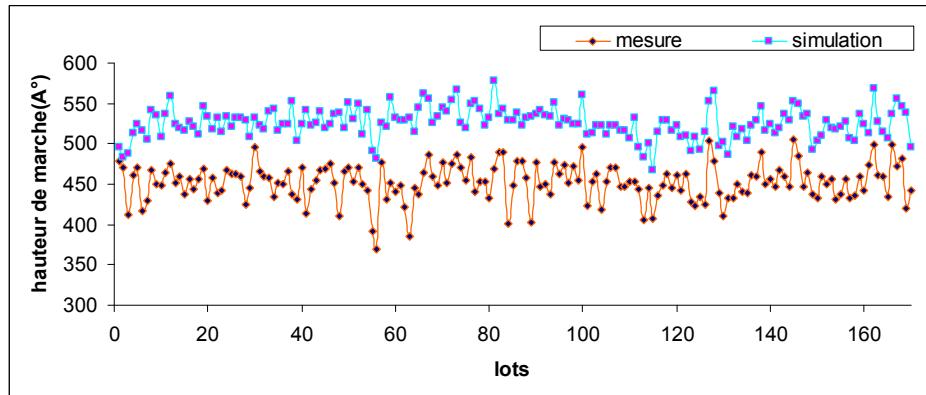

- Figure 4.63 Comparaison entre les valeurs de mesure et de simulation

- Figure 4.64 Illustration de l'épaisseur polie après le procédé CMP

- Figure 4.65 Représentation schématique du modèle.

- Figure 4.66 Comparaison entre les données mesurées et la simulation

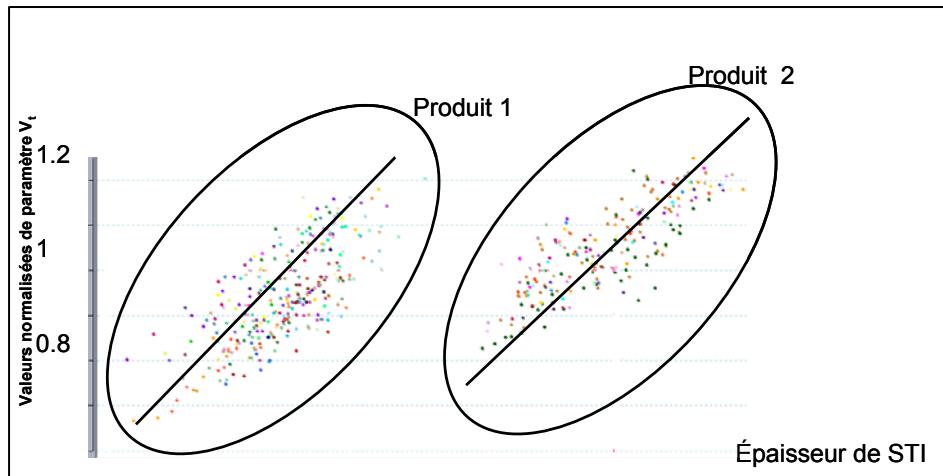

- Figure 4.67 Evolution de la tension de seuil en fonction de l'épaisseur STI

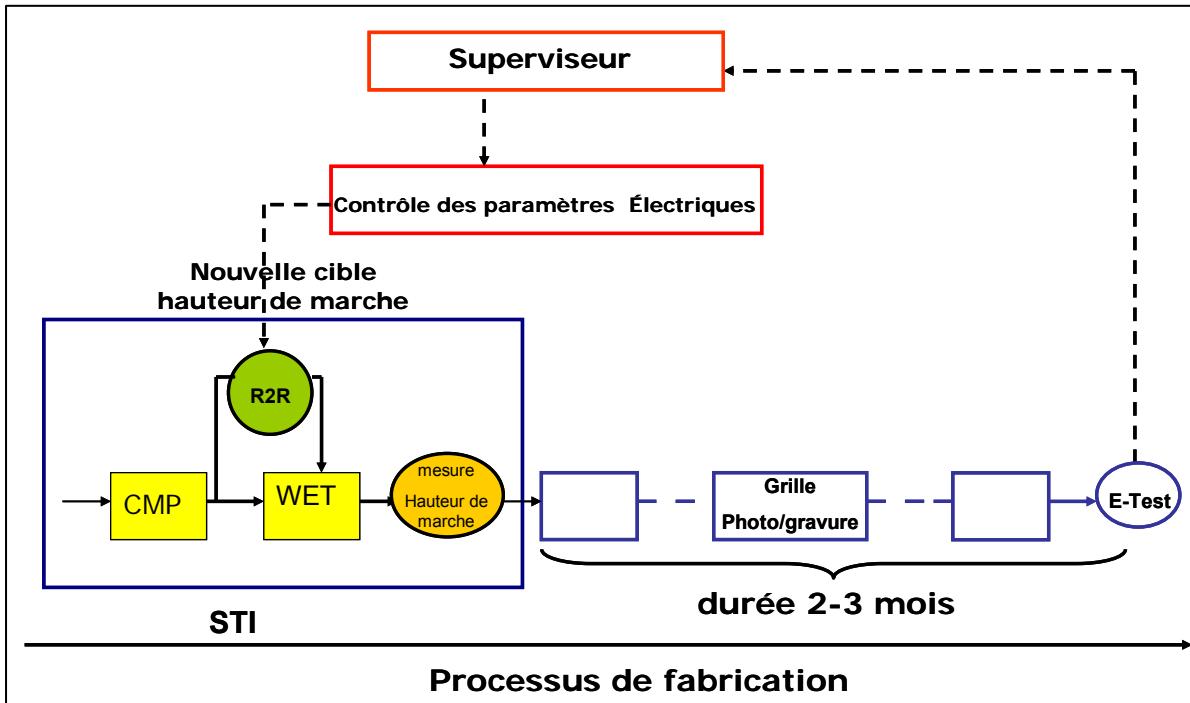

- Figure 4.68 Schéma synoptique du superviseur

# Liste des tableaux

- Tableau 2.1 Evolution des technologies en fonction du temps

Tableau 3.1 Valeurs des épaisseurs STI pour les six plaques

Tableau 3.2 Densité de dopage du substrat en fonction de l'épaisseur ST

Tableau 3.3 Données de la distance « a »

Tableau 4.1 Temps du procédé par plaques

Tableau 4.2 Récapitulatif des conditions expérimentales du plan d'expériences

Tableau 4.3 Valeurs de P-value obtenues sous SAS.

Tableau 4.4 Valeurs de P-value obtenues sous SAS

Tableau 4.5 Conditions expérimentales

Tableau 4.6 Ecart type normalisé de la hauteur de marche des plaques

Tableau 4.7 Conditions expérimentales des plaques sélectionnées pour le plan d'expériences

Tableau 4.8 Ecart type normalisée de l'étendue d'épaisseur d'oxyde avant CMP.

Tableau 4.9 Exemple des conditions de procédé.

Tableau 4.10 Mesures avant et après gravure H<sub>3</sub>PO<sub>4</sub>

Tableau 4.11 Conditions expérimentales visées pour le plan d'expériences.

Tableau 4.12 Résultats expérimentaux

Tableau 4.13 Valeurs de (P-value) obtenus sous SAS

Tableau 4.14 Les résultats des mesures sur les lots de la pré- production

# Liste des abréviations

|         |                                    |

|---------|------------------------------------|

| APC     | Advanced Process Control           |

| BPSG    | Boron Phosphorus Silicate Glass    |

| BOX     | Buried Oxide                       |

| CD      | Critical Dimension                 |

| CMOS    | Complementary Metal Oxide Silicon  |

| CMP     | Chemical Mechanical Polishing      |

| CVD     | Chemical Vapor Deposition          |

| DCS     | Distributed Control System         |

| DOE     | Design of experiments              |

| EWS     | Electrical Wafer Test              |

| FDC     | Fault Detection and Classification |

| HDP-CVD | High Density Plasma CVD            |

| IMD     | Inter Metal Dielectric             |

| LCL     | Lower Control Limit                |

| LOCOS   | Local Oxidation of Silicon         |

| LPCVD   | Low Pressure CVD                   |

| LSL     | Lower Specification Limit          |

| PBL     | LOCOS Poly Buffered LOCOS          |

| PECVD   | Plasma Enhanced CVD                |

| PMD     | Pre Metal Dielectric               |

| PSG     | Phosphorus Silicate Glass          |

| PT      | Parametric Test                    |

| R2R     | Run to Run                         |

| RTO     | Real Time Optimisation             |

| SILO    | Sealed Interface Local Oxidation   |

| SPC     | Statistical Process Control        |

| STI     | Shallow Trench Isolation           |

| TEOS    | Tetra Ethyl Orto Silicate          |

| UCL     | Upper Control Limit                |

| USL     | Upper Specification Limit          |

| WIWNU   | Within Wafer Non Uniformity        |

| ZA      | Zone Active                        |

# Introduction générale

Le marché des semi-conducteurs représente un total de plus de 250 milliards de dollars et se maintient avec une croissance annuelle allant de 8 à 10%. Ces dernières années, les applications des semi-conducteurs se sont beaucoup diversifiées et touchent désormais plusieurs secteurs: la téléphonie mobile, les télécommunications, internet... Le marché des semi-conducteurs est constitué à plus de 95% de la technologie CMOS (Complementary Metal Oxide Semiconductor).

Depuis plus de 40 ans, les industriels augmentent ainsi la densité de leur circuits. Pour cela, ils réduisent la taille des éléments qui les constituent, autrement dit les transistors. L'association de l'industrie des semi-conducteurs : SIA (Semiconductor International Association) publie chaque année une feuille de route : ITRS (International Technology Road map for Semiconductor). Cette feuille de route définit les spécifications en terme de dimensions, de composants, de matériaux et aussi d'équipements à intégrer pour la fabrication. Pour respecter les spécifications exigées, il faut alors contrôler avec rigueur les procédés de fabrication.

Généralement, les procédés sont incapables de reproduire toujours à l'identique un produit. Lorsqu'on effectue le contrôle d'une des caractéristiques d'un produit, on observe une dispersion des valeurs mesurées autour de la valeur cible (visée), on parle alors de variabilité. Pour mieux contrôler les procédés, il est nécessaire de réduire ou d'éliminer si possible cette variabilité mais avant tout, il faut comprendre l'origine de la variabilité et le type de variabilité.

L'industrie du semi-conducteur utilise depuis plusieurs années les techniques de contrôle des procédés tel que le SPC (Statistical Process Control). Le contrôle SPC est basé sur l'utilisation de cartes de contrôle. On considère un procédé sous contrôle statistique

lorsque toutes les valeurs des échantillons mesurés se situent à l'intérieur des limites de tolérance du procédé définies par l'intermédiaire de cartes de contrôle. Tant que la valeur est dans ces limites, il n'y a pas de raison d'agir sur le procédé. On risquerait de décentrer un procédé bien centré. Si une valeur est en dehors de ces limites, il y a une forte probabilité que le procédé ne soit plus maîtrisé et qu'une variation anormale en soit la cause. Il faut alors le recentrer.

Le contrôle par la technique SPC classique n'est plus adéquat avec les nouvelles technologies car ces dernières imposent des limites de contrôle très serrées. Un contrôle plus rigoureux est donc nécessaire d'où le recours à la technique de contrôle avancé des procédés ou APC (Advanced Process Control). Le contrôle avancé des procédés associe trois techniques dont le SPC classique et le contrôle des équipements connu sous le nom de FDC (Fault Detection and Classification). La troisième composante est une technique de régulation de type Run à Run (Run to Run : R2R) permettant l'ajustement de certains paramètres de procédés en temps réel afin de s'approcher de la valeur cible.

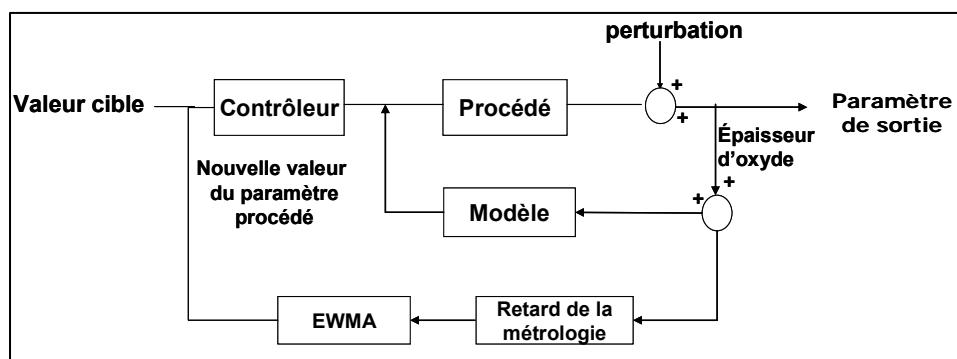

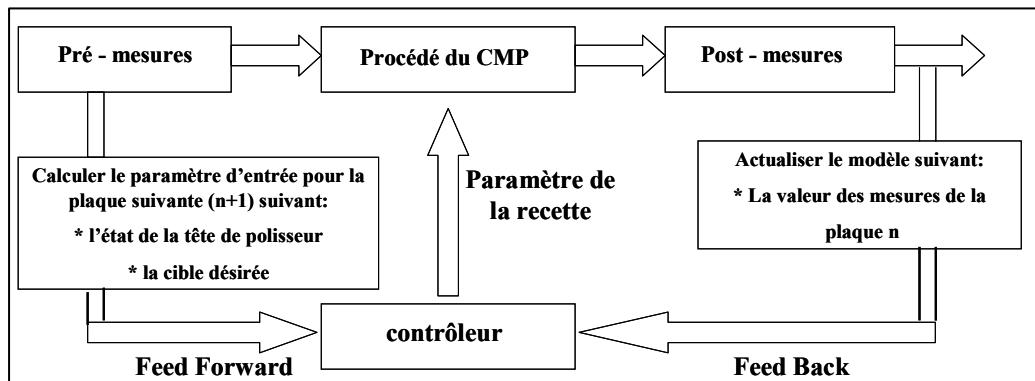

Figure 1. Exemple d'un schéma synoptique d'une boucle de régulation de type R2R

La réduction des dimensions entraîne également des changements de procédés au niveau des briques principales des circuits (isolation, grille, métal et interconnexions). La brique qui sera abordée tout au long de ce manuscrit est la brique concernant l'isolation entre les transistors. Pour les technologies  $<0,25\mu\text{m}$ , le procédé d'isolation employé est basé sur des tranchées d'isolations peu profondes ou bien le STI (Shallow Trench Isolation). En effet, les procédés d'isolation étaient déjà connus bien avant l'introduction de la technique d'isolation par tranchées, pour les problèmes qu'ils engendraient, comme par exemple, la création de dislocations. Le STI, basé sur des tranchées d'oxydes peu profondes, offre une bonne isolation entre les transistors.

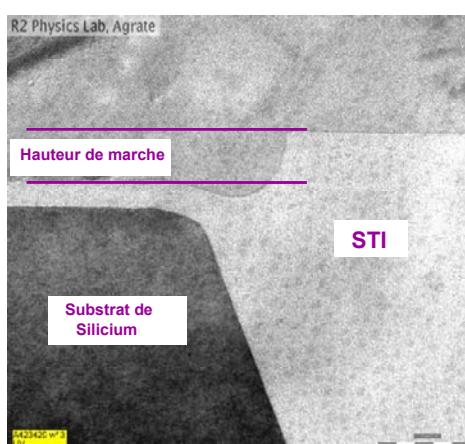

Figure 2. Représentation schématique du STI

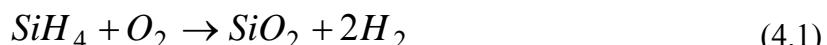

Le STI est caractérisé généralement par une grandeur géométrique appelée hauteur de marche comme cela est illustré sur la figure 2. Cette hauteur de marche est le résultat de différentes étapes technologiques que nous décrirons ultérieurement. Si cette hauteur dépasse quelques nm, les effets résultants seront néfastes sur le rendement final et ne peuvent être constatés que lors des tests électriques et du test final pour la sélection des bonnes puces.

Des variabilités (dispersion de la mesure par rapport à la valeur cible) de la hauteur de marche ont été observées. Les variabilités peuvent se manifester de lot<sup>1</sup> à lot, de plaque à plaque et même au sein d'une plaque (variabilité intra-plaque). La variabilité de la hauteur de marche est la conséquence des différentes variabilités observées au niveau des paramètres de sortie (paramètres de mesures physiques) des procédés associés à la brique STI. Les analyses de variabilité permettent de conclure quels procédés/paramètres contribuent plus à la dispersion de la hauteur de marche.

Nous allons, tout au long de ce manuscrit, nous pencher sur les différents procédés identifiés comme paramètres contributeurs à la dispersion de la hauteur de marche. Le défi est d'arriver à mieux contrôler cette dispersion.

Les solutions aux problèmes de dispersion des mesures peuvent être abordées selon deux volets :

- le changement des procédés impliquant un certain nombre de modifications sur les recettes et les étapes des procédés. Ceci est une bonne voie mais elle ne s'inscrit pas dans le cadre de notre travail, donc nous ne focaliserons notre attention que sur les procédés considérés comme matures.

- le contrôle des procédés qui consiste à apporter des solutions pour stabiliser le procédé et éviter des dérives (atteinte ou dépassement des limites de contrôle). C'est sur ce deuxième volet que nous allons travailler.

L'objectif de ces travaux de thèse est d'obtenir une meilleure compréhension des variabilités générées au niveau du module STI, de les quantifier et de mesurer leur impact sur le rendement. On pourra justifier ainsi les actions de contrôle avancé des procédés menées en vue de réduire la dispersion de la hauteur de marche et proposer des solutions telles que les boucles de régulation de type R2R. Les produits technologiques qui sont concernés par cette étude sont des produits mémoires (longueur de grille des transistors est de 0,18µm). Le choix de ce type de produits est justifié par le fait que ces produits sont plus sensibles au STI que les produits logiques. Cette forte sensibilité est due aux procédés thermiques additionnels comme le procédé de recuit au niveau des opérations post-STI.

Dans le chapitre 1, nous rappellerons les méthodes de contrôle utilisées dans l'industrie en général et les enjeux économiques importants favorisant l'introduction de telles actions. Ensuite, nous dresserons un état de l'art détaillé sur les différents travaux industriels et académiques sur l'APC dans le milieu des semi-conducteurs. Suite à cet état de l'art, nous exposerons la stratégie de l'étude proposée et nous décrirons tous les outils statistiques utilisés au cours de la thèse. Ce premier chapitre va surtout servir de référence et nous y ferons régulièrement appel tout au long des autres chapitres.

Le chapitre 2 sera consacré au STI. Au début du chapitre, nous rappellerons quelques bases élémentaires sur la technologie CMOS, la loi de Moore et une brève description des procédés de fabrication nécessaires pour la réalisation des circuits. Nous ne nous focaliserons

---

<sup>1</sup> Un ensemble de plaques, généralement un lot est composé de 25 plaques.

par la suite que sur la brique technologique d'isolation. Avant de décrire le STI, nous rappellerons les techniques employées avant l'introduction du STI. Nous verrons bien que les changements de procédés effectués jusqu'au STI répondent souvent à un souci généralement lié aux performances électriques. Après ce rappel, nous décrirons tous les procédés de fabrication permettant la réalisation de la brique STI et enfin nous discuterons de l'impact du STI sur le rendement final. Nous mettrons l'accent en particulier sur l'influence du STI sur certains paramètres électriques (résistance carrée, tension de seuil...) et également sur les contraintes mécaniques. Cette partie sera importante pour situer notre travail dans cet axe de recherche et éventuellement, y apporter notre contribution. Nous évoquerons également dans ce chapitre, un nouveau mode de STI ou STI amélioré : le direct STI, nous verrons que c'est un mode qui présente un enjeu économique en permettant de se passer de deux étapes de fabrications. En plus de ça, il permet d'avoir une bonne uniformité de la hauteur de marche.

Une grande partie expérimentale sera décrite dans le chapitre 3 pour illustrer les différentes expériences menées en vue de démontrer et de quantifier l'impact du STI sur les paramètres électriques et les contraintes mécaniques, suivra une partie statistique sur l'analyse des données de mesures électriques. Nous allons appuyer ces travaux sur des simulations et des caractérisations pour mieux expliquer physiquement les résultats obtenus. Nous terminerons ce chapitre par des propositions et des conclusions, parmi lesquelles l'obtention d'un indicateur électrique pour le suivi des boucles de régulations R2R.

Après ce travail d'analyses et de corrélations, nous aborderons le chapitre 4. Nous exposerons les analyses de variabilité effectuées sur les procédés de fabrication au niveau de la brique STI. Cette analyse nous permettra d'identifier les paramètres critiques qui contribuent le plus à la variabilité de la hauteur de marche. Ce chapitre est composé de trois grandes parties correspondant aux trois boucles de régulation proposées pour la réduction de la dispersion de la hauteur de marche.

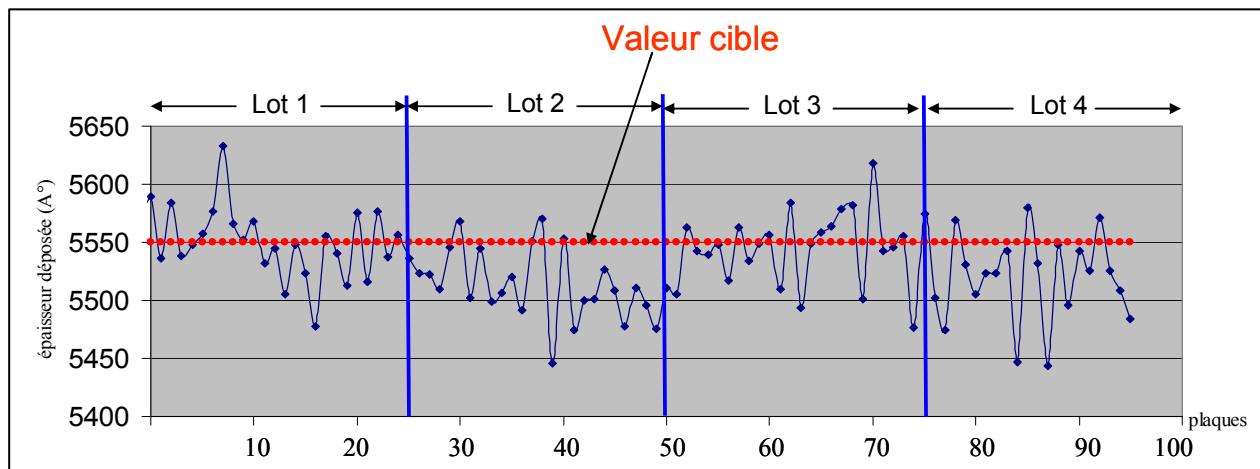

La première partie traite de la réalisation de la boucle de régulation de type « feed back » de la boucle de dépôt HDP-CVD (High Density Plasma Chemical Vapor Deposition). Nous rappellerons les principes physiques du HDP-CVD. Nous détaillerons ensuite les analyses multi-variées effectuées qui serviront à identifier les étapes/paramètres critiques. Ces résultats seront interprétés par la suite pour définir les plans d'expériences. Deux modèles de procédés sont recherchés: le modèle d'épaisseur déposée et le modèle de l'étendue de l'épaisseur d'oxyde. Ces modèles seront simulés pour tester leur robustesse de prédiction. Nous proposerons une méthode originale basée sur des algorithmes d'apprentissage statistique pour éliminer l'effet des injecteurs de gaz.

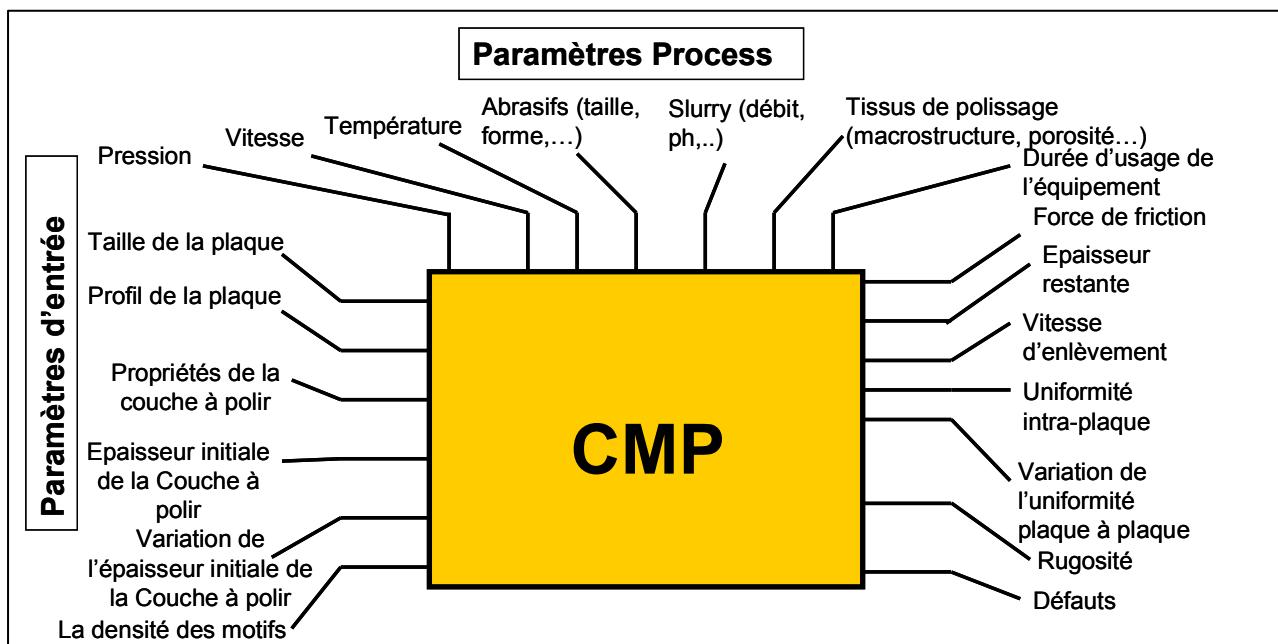

La deuxième partie de ce chapitre sera consacrée à la boucle de régulation de type « feed back » sur le procédé polissage mécano- chimique CMP (Chemical Mechanical polishing). Cette boucle ne concernera que le STI standard marqué par une non uniformité de la hauteur de marche, résultat de la non uniformité des paramètres de mesures post- CMP. Nous rappellerons brièvement les définitions de base du procédé CMP ainsi que les différents travaux de recherches effectués pour modéliser le CMP. Nous situerons notre travail dans l'axe « modélisation de l'uniformité sur la plaque ». Nous allons voir que la pression est un paramètre très critique sur l'uniformité de l'oxyde post-CMP sur la plaque et en particulier sur les bords des plaques. L'approche proposée consiste à modifier la pression au niveau des bords de plaque. Nous détaillerons notre approche et les différents plans d'expériences effectués pour retrouver le modèle du procédé. Nous terminerons enfin cette partie par l'interprétation de tous les résultats.

La dernière partie de ce chapitre traite la boucle de régulation de type « feed-forward » entre les procédés de CMP et de gravure humide (WET). Au début de ce chapitre,

nous insisterons sur l'originalité de ce travail. L'équipement de gravure humide sera décrit en détails. Ensuite, nous exposerons les résultats de l'analyse multivariée pour identifier les paramètres critiques qui nous permettront par la suite de concevoir et de réaliser le modèle du procédé. Le modèle établi sera proposé à la production afin de le tester. Nous exposerons tous les résultats expérimentaux et de simulations.

Nous terminerons ce chapitre par une proposition concernant la surveillance des boucles de régulation R2R. Cette surveillance est basée sur un superviseur. Dans le but d'éliminer l'effet produit et les variations induites lors des changements de procédés, une calibration périodique de certains éléments des boucles s'impose. Les valeurs cibles de certains paramètres des procédés doivent donc être actualisées pour assurer à la fin de bonnes performances électriques.

Enfin, nous pourrons conclure sur les différents travaux réalisés, et nous proposerons les perspectives à venir.

# **Chapitre I**

## **Le contrôle des procédés**

Le contrôle des procédés dans le domaine industriel constitue un enjeu économique très important. Le développement des techniques de contrôle est favorisé par la croissance des vitesses des microprocesseurs. Ce développement a accompagné la création de nouveaux outils et logiciels plus performants. Ces derniers ont contribué à la naissance d'une technique de contrôle plus robuste et plus rapide appelée « contrôle avancé des procédés » ou APC : Advanced Process Control [BONAVITA 1998]. Les industries chimiques et pétrochimiques sont de loin les industries leaders en terme d'usage des techniques de contrôle avancé des procédés. L'industrie pharmaceutique utilise aussi ces techniques avancées de contrôle. Contrairement à l'industrie des semi-conducteurs, les lignes de production des autres industries sont caractérisées par le fait que les opérations des procédés suivent un flux continu et leur nombre est limité. Dans l'industrie des semi-conducteurs, le nombre d'opérations pour réaliser des circuits est de l'ordre de 350 à 400 pour les technologies actuelles. Le flux des procédés est discontinu et le délai de réalisation des dispositifs est en moyenne de 2 à 3 mois. Ces différences majeures ont fait que l'industrie des semi-conducteurs a enregistré un retard pour l'application des techniques de contrôle avancé des procédés. Le défi principal est de surmonter les contraintes liées à cette industrie.

Dans les paragraphes suivants, l'évolution des techniques de contrôle dans le domaine de l'industrie pétrolière sera décrite et nous dresserons un état de l'art des techniques de contrôle des procédés dans le domaine des semi-conducteurs. Nous donnerons également des exemples d'industrialisation des systèmes de contrôle avancé des procédés.

## 1.1 Les techniques de contrôle

### 1.1.1 Les méthodes de contrôle

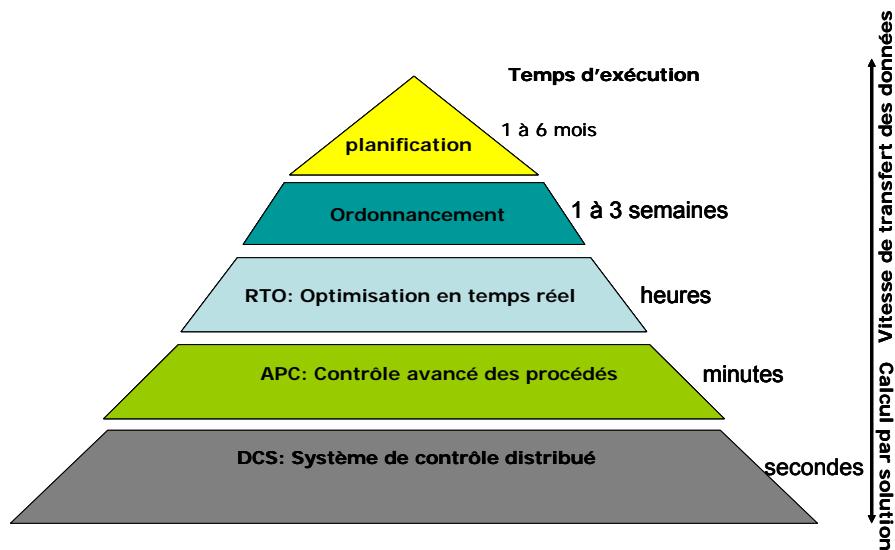

Beaucoup de techniques de contrôle ont été proposées pour contrôler les procédés. Le succès de certaines méthodes de contrôle dans une industrie suscite beaucoup d'intérêts pour le généraliser à d'autres industries. C'est le cas du Système de Contrôle Distribué (DCS) qui a eu un grand succès dans l'industrie pétrolière dans les années 70 et qui a ouvert la voie à l'utilisation des techniques d'asservissement telle que : la cascade, le « Feed Forward<sup>2</sup> », le « Feed Back<sup>3</sup> », le contrôle non linéaire, etc ... Nous reviendrons longuement dans ce manuscrit sur l'application des techniques de « Feed Forward » et de « Feed Back ».

Figure 1.1- Pyramide représentant les différentes techniques de contrôle [APC network 2007].

Dans les années 80, un nouveau type de contrôleurs a vu le jour. Il s'agit de contrôleur prédictif multivarié<sup>4</sup> qui non seulement assure des techniques telles que le « Feed Forward » et le « Feed Back » mais qui a permis de franchir une autre étape plus avancée. Si des interactions entre les paramètres du procédé existent, ce contrôleur est beaucoup plus efficace. Par contre, les capacités de calcul de ce contrôleur sont plus importantes que ceux du DCS [APC network 2007].

Depuis la fabrication des ordinateurs puissants, capables de surveiller une usine en collectant des données en temps réel, cette invention a ouvert la voie à l'apparition des technologies complémentaires comme les réseaux de neurones. Un autre exemple de contrôle avancé est la technologie des systèmes. Cette technologie a vu le jour à la fin des années 80. Le principe de cette technologie repose sur l'exploitation des idées des meilleurs collaborateurs. Ensuite, les données sont complétées en temps réel. Cette technologie a connu un succès dans la l'industrie pétrolière.

<sup>2</sup> Contrôle par anticipation

<sup>3</sup> Contrôle par rétroaction

<sup>4</sup> Modèle capable de prédire les paramètres de sortie d'un système ayant en entrée plusieurs paramètres

Dans les années 1990, les entreprises ont manifesté un besoin d'avoir des interfaces robustes entre les ingénieurs et les opérateurs. Les fournisseurs de la technologie DCS ont inclus dans leurs matériels des contrôleurs de prédiction par modèles. Cette technique est connue sous le nom de technique d'optimisation en temps réel (RTO : Real Time Optimisation). Au départ, cette technologie n'a pas réussi à s'imposer dans les applications industrielles à cause de temps de calcul des différentes équations jugés très long. Il a fallu donc attendre l'arrivée sur le marché d'ordinateurs plus puissants pour réduire les temps de calculs. La technologie RTO a réussi à résoudre des cas compliqués dans l'industrie pétrolière. Il est à souligner que la RTO ne remplace pas la programmation linéaire qui est adoptée depuis plus de 50 ans [APC network 2007].

## 1.1.2      **Les enjeux du contrôle des procédés face aux nouvelles technologies**

### 1.1.2.1    **La vie d'une technologie**

Un circuit intégré se compose de plusieurs couches minces. Chaque couche a ses propres propriétés chimiques pour réaliser au final les caractéristiques électriques désirées. Les dispositifs subissent lors de la fabrication différentes opérations physiques et chimiques. Le nombre des opérations diffère d'une technologie à une autre. Pour les technologies actuelles produites sur le site ST-Rousset, ce nombre avoisine les 350 étapes. Pour élaborer l'ensemble de ces couches, on utilise une plaque de silicium de type monocristallin. Le diamètre des plaques est de 100 à 300mm. Sur le site de ST-Rousset, le diamètre des plaques utilisées est de 200mm. Avec les nouvelles technologies (réduction des dimensions des circuits), des problèmes liés aux procédés de fabrication apparaissent et impactent négativement le rendement. Des efforts sont à déployer sur les 3 principaux domaines incontournables de la réalisation des dispositifs en vue d'assurer un bon rendement :

- au niveau de la conception (design) en proposant de nouvelles architectures adéquates aux nouvelles technologies.

- au niveau de la fabrication en introduisant de nouveaux équipements et de nouveaux procédés pour assurer la reproductibilité des fonctions des produits.

- au niveau de l'industrialisation et de la mise sous contrôle en proposant de nouvelles méthodes de surveillance des procédés et des équipements afin de mieux quantifier et contrôler les variations des mesures sur les produits observées dans le temps.

Dans ce manuscrit, nous nous intéressons uniquement à ce dernier domaine et plus particulièrement aux méthodes de contrôle des procédés de fabrication qui sont devenues un secteur primordial dans le fonctionnement d'une usine de fabrication des semi-conducteurs (FAB<sup>5</sup>). La figure 1.2 représente grossièrement la vie d'une technologie. Nous représentons le rendement final de fabrication en fonction du temps avec et sans utilisation des techniques de contrôle avancé des procédés. La première période, appelée « période pilote » est marquée par

---

<sup>5</sup> Dans l'industrie de fabrication de semi-conducteur, nous désignons couramment sous le nom de FAB (de l'anglais *fabrication plant*). Le cœur d'une *fab* réside dans sa salle blanche, une zone où l'environnement est contrôlé pour éviter toute micropoussière et où la moindre micro-vibration est proscrite. La salle blanche est remplie d'équipements très coûteux nécessaires aux nombreuses étapes de fabrication

le développement de nouveaux modules procédés. Les modules, issus des générations antérieures qui ne répondent plus aux besoins sont identifiés. Dans la seconde période (cycle rapide), on intègre les nouveaux modules dans une séquence complète de fabrication. Après plusieurs itérations, la séquence de fabrication est affinée et optimisée pour limiter la sensibilité de fonctionnement aux paramètres des procédés de fabrication. A la fin de cette étape, la capacité de production et le rendement sont augmentés. La dernière période correspond à la production de masse des circuits.

Figure 1.2- Evolution du rendement en fonction du temps [KRIGER 2005]

Au début le prix du produit et la demande sont hauts. Ces deux quantités diminuent plus ou moins rapidement avec l'arrivée des concurrents sur le marché. Après un certain temps (quelques mois), la technologie des produits les plus avancés est dépassée par de nouvelles générations et les prix continuent à chuter comme cela est illustré sur la figure 1.2. Le déploiement des techniques de contrôle avancé des procédés permet de limiter le temps de la période de cycle rapide et d'améliorer le rendement pendant cette période et pendant la période mature. Pour déployer ce type de techniques, il est impératif que la FAB dispose d'outils modernes, on parle souvent d'une FAB moderne.

### 1.1.2.2      Une usine de fabrication des semi-conducteurs automatisée

Typiquement une usine de fabrication de semi-conducteurs (FAB) moderne a les caractéristiques suivantes disponibles pour l'analyse et le contrôle :

- les données en temps réel fournies par les différents capteurs qui reflètent l'état de santé de l'équipement.

- la métrologie intégrée et les données de métrologie en ligne disponibles après plusieurs étapes de procédés de fabrication afin de remédier aux problèmes de retards de la métrologie. Le retard de la métrologie peut être défini comme étant le temps d'attente pour avoir l'information sur les résultats de métrologie suite au procédé de fabrication.

- une base de données des paramètres électriques au niveau du test final des puces.

Ces trois conditions constituent les blocs importants de l'architecture du système de la FAB automatisée. Une première version de l'architecture de la FAB automatisée a été présentée par T.Sonderman & J.Qin en 2002 [Qin 2006] comme cela est illustré sur la figure 1.3.

Figure 1.3- Architecture de la FAB automatisée [SONDERMAN 2005] [Qin 2006]

Cette représentation de la FAB automatisée est le résultat de l'analogie FAB semi-conducteurs – usine de chimie. Nous distinguons sur la figure 1.3 plusieurs niveaux de contrôle. Le premier niveau de contrôle concerne la maîtrise de l'équipement. Il s'agit généralement de la mise en place des systèmes de contrôle pour s'assurer du bon fonctionnement de l'équipement. Le second niveau est un système de contrôle des procédés. Ce système utilise les données de mesure et les paramètres des procédés. Nous reviendrons en détail sur les deux premiers systèmes de contrôle dans les prochains paragraphes. Le troisième niveau est une base de données qui regroupe toutes les données fournies par les deux premiers systèmes de contrôle. Le dernier niveau collecte et traite les données de tests électriques et ensuite les compare avec les données théoriques (calculées à partir de modèles physiques déjà établis). Suivant les spécifications souhaitées, des recommandations peuvent être formulées pour les systèmes de contrôle. L'enjeu économique de la modernisation d'une FAB est de réduire le temps de cycle, ce dernier impacte directement le rendement de la production.

### 1.1.3 Le temps de cycle

Le temps de cycle<sup>6</sup> de fabrication constitue une partie des coûts de fabrication d'une ligne de production. Le défi est de réduire au maximum ce temps de cycle, car, plus ce temps est long, plus les coûts de fabrication sont élevés.

<sup>6</sup> Le temps de cycle de production, appelé aussi temps de séjour ou délai de fabrication, est le temps total nécessaire pour fabriquer un lot de plaques. Il mesure le temps écoulé entre le moment où le lot entre dans la fab

En général, le temps de cycle dépend [ROBINSON 2005, ROBINSON 2007] :

- du temps d'utilisation de l'équipement.

- du nombre des équipements qualifiés à chaque opération.

- de la variabilité<sup>7</sup> ou dispersion qui provient de l'absence de la répétitivité parfaite des mesures.

Sur le premier point, on peut améliorer le temps de cycle en augmentant le temps de disponibilité de l'équipement. Sur le deuxième point, il est possible d'augmenter le nombre des équipements qualifiés<sup>8</sup> et s'assurer que chaque opération de fabrication est réalisable sur au moins deux équipements qualifiés. Sur ce dernier point, il faut chercher à identifier la source de variabilité et trouver une solution pour l'éliminer.

## 1.1.4 Les sources de variations dans la FAB

Il y a beaucoup de facteurs qui contribuent à la variabilité des paramètres de sortie (mesures).

### 1.1.4.1 Variabilité due à l'équipement :

- le temps d'attente au niveau de l'équipement (fabrication ou mesure)

- le temps de transport des lots (d'un atelier à un autre)

- le problème lié à la gestion des lots (le choix des équipements pour les prochaines opérations).

- le temps de maintien des lots. Pour des raisons d'inspection ou d'analyse des données, certains lots restent inactifs pendant un certain temps pour valider les résultats des inspections.

### 1.1.4.2 Variabilité due au temps du procédé :

- le rejet des plaques. Quand les résultats des mesures après un procédé sont hors des plages des limites de tolérances (limites de spécifications), les plaques ne vont pas continuer les opérations suivantes et par conséquent elles seront recyclées.

- le re-traitement des plaques. Si, dans certains cas, les mesures des plaques après une opération de fabrication ne sont pas satisfaisantes, si le degré de criticité du procédé n'est pas très important, il est possible de re-traiter (re-processer) les plaques. Le phénomène est appelé généralement « Re-work » ou « Re-travail ».

- le mixage des recettes<sup>9</sup> des différents produits procédés sur le même équipement

---

et le moment où il en sort. Le temps de cycle inclut le temps effectif de fabrication (temps de process), le temps de transfert entre les opérations, le temps d'attente devant les machines, et le temps d'attente pour le transfert.

<sup>7</sup> Généralement, les procédés sont incapables de reproduire toujours à l'identique un produit. Lorsqu'on effectue le contrôle d'une des caractéristiques d'un produit, on observe une dispersion des valeurs mesurées autour de la valeur cible (visée), on parle alors de variabilité.

<sup>8</sup> Tous les équipements n'ont pas la capacité de réaliser une opération donnée d'un lot. Pour qu'un équipement soit apte à réaliser une opération ou une recette on doit le qualifier pour cette recette. Un équipement qui n'est pas qualifié à un instant donné peut l'être à l'instant suivant moyennant les réglages nécessaires.

<sup>9</sup> Fichier présent sur chaque équipement comportant les consignes des différents paramètres du procédé (pression, puissance RF, flux des gaz...)

- le mixage des produits procédés sur le même équipement

- l'arrêt d'une machine pour une maintenance

- l'occupation de la machine pour des expériences spécifiques<sup>10</sup>.

- le temps de prise de décision lors d'un problème.

- le temps entre deux étapes consécutives

Dans ce manuscrit, on va s'intéresser uniquement aux variations liées au procédé. L'ensemble des actions qui seront décrites dans les prochains chapitres vise à réduire la variabilité liée au procédé. L'objectif de ces actions est de réduire le nombre de rejet de plaques et donc, d'améliorer le rendement et le temps de cycle. Le développement des nouvelles techniques de contrôle pour la réduction de la variabilité surtout sur les nouvelles technologies est un moyen pour atteindre cet objectif.

## 1.1.5      **Le contrôle des procédés et des équipements**

Le concept de contrôle des équipements et des procédés est connu sous le nom de contrôle avancé des équipements/contrôle avancé des procédés (AEC/APC : advanced Equipment Control/Advanced Process Control). Pour une meilleure maîtrise de la FAB, le contrôle des équipements et des procédés est nécessaire. Le contrôle avancé des procédés est composé de trois composantes principales que nous allons décrire en détail dans les paragraphes suivants.

### 1.1.5.1    **Le contrôle statistique du procédé (SPC: Statistical Process Control)**

Depuis 1920, le SPC est le moyen de contrôle des procédés de fabrication adopté par la plupart des industries. Il est basé sur des indicateurs statistiques (moyenne, étendue, écart type....) [MONTEGOMERY 2001]. Nous détaillerons ces indices statistiques dans la troisième partie de ce chapitre. Les mesures prélevées après l'étape de fabrication sont comparées avec certaines limites fixées par les technologues. Ce type de contrôle est assisté par des cartes de contrôle.

#### 1.1.5.1.a   **Les principes de base des cartes de contrôle**

Les cartes de contrôle sont les outils indispensables pour réaliser un pilotage rationnel du procédé de fabrication. Une application rigoureuse de cette méthode permet d'améliorer de manière significative la capabilité<sup>11</sup> du procédé.

Il existe généralement deux types de limites :

- les limites de spécifications : ce sont les limites qu'il ne faut pas franchir, sinon les plaques seront rejetées car il y a un risque de dysfonctionnement. Ces limites sont souvent symbolisées par « LSL » et « USL » limite basse et limite haute.

---

<sup>10</sup> Expériences faites par des ingénieurs soit pour explorer un phénomène physique, soit pour qualifier un procédé.

<sup>11</sup> Nous utilisons généralement la notion de « capabilité des procédés » (ou  $C_{pk}$ ) pour analyser la variabilité des procédés et des mesures électriques en regard des spécifications associées.

- les limites de contrôle sont les barrières qualifiant le bon fonctionnement d'une opération. Ces limites sont souvent symbolisées par « LCL » et « UCL » limite basse et limite haute.

### 1.1.5.1.b Echantillonnage des mesures

Dans un milieu de production, les plaques ne peuvent pas toutes être mesurées. Seuls, quelques lots sont mesurés et seules quelques plaques d'un même lot sont mesurées également. Cette méthode est appelée échantillonnage des mesures. Cette méthodologie s'applique à 3 types de mesures comme cela est illustré sur la figure 1.4.

Figure 1.4- Enchaînement des opérations de fabrication des circuits

Nous pouvons distinguer :

- métrologie ou mesures physiques : à la fin de chaque opération de fabrication, les plaques sont mesurées pour s'assurer du bon déroulement de l'opération. Généralement, les mesures se font sur des structures de test et non sur le produit pour ne pas l'abîmer.

- tests paramétriques (PT: parametric test) : à la fin de la formation de la grille et des interconnexions, des tests sont faits sur chacune des plaques. Ces tests sont réalisés sur des structures de test. Le test PT est considéré comme un test préliminaire pour la sélection des bonnes plaques avant le test électrique final.

- test électrique Final (EWS: Electrical Wafer Sort): le test EWS<sup>12</sup> est le dernier maillon de la chaîne de mesures de fabrication des composants. Le test permet de tester la qualité des circuits.

### 1.1.5.1.c Maintien du procédé sous contrôle

<sup>12</sup> Chaque circuit est testé individuellement sur les paramètres qui le caractérisent, il s'agit des tests électriques. Si un test est hors spécification, alors le circuit est déclaré mauvais. Le pourcentage de puces bonnes (qui fonctionnent) après ce test correspond au rendement. C'est une donnée économique essentielle et un critère décisif de compétitivité de l'unité de fabrication.

En analysant finement la dispersion d'un procédé, on peut extraire deux causes essentielles de dispersion. Il s'agit de perturbations communes qui sont liées à des phénomènes aléatoires et de perturbations non aléatoires (ou spéciales) qui sont des causes de dispersion identifiables. Ces perturbations peuvent être modélisées. Contrairement aux perturbations aléatoires, les perturbations non aléatoires nécessitent une intervention sur le procédé.

### 1.1.5.2 Détection et classification des défauts (FDC : Fault Detection and Classification)

La méthode classique pour suivre le bon fonctionnement des équipements de fabrication consiste à surveiller les équipements après une étape de fabrication. Ceci induit un temps de cycle énorme et un risque de rejet de plaques important. Donc, ces méthodes de contrôle de surveillance des équipements ne sont plus adaptées aux nouvelles technologies où la perte liée au nombre de plaques rejetées constitue un enjeu économique très important. En vue de détecter les dérives (écart entre les valeurs des mesures et les valeurs cible) des équipements en temps réel et d'éventuellement déduire les origines de ces dérives et de classifier les anomalies, un contrôle en temps réel s'impose. C'est le principe de la FDC. Les outils FDC utilisent des systèmes d'analyses univariées et multivariées. Un exemple d'une analyse univariée est illustré sur la figure 1.5. On observe l'évolution temporelle de la pression de l'équipement avec le temps durant un procédé de dépôt chimique en phase vapeur. Cette méthode de contrôle nous permet de surveiller ce paramètre pour chaque étape de dépôt. Si les valeurs de la pression dépassent les limites de contrôle fixées, une alarme sera générée et l'équipement sera arrêté.

Figure 1.5- Représentation temporelle de l'évolution de la pression pendant le procédé de dépôt chimique en phase vapeur

### 1.1.5.3 Boucles de régulation Run to Run (R2R)

Chaque étape du procédé de fabrication induit une variabilité au niveau des plaques. Cette variabilité peut être traduite de batch<sup>13</sup> à batch  $\sigma_{batch}$ , de lot à lot  $\sigma_{lot}$  (variabilité inter-lot), de plaque à plaque  $\sigma_{plaque}$  (variabilité inter-plaque), de site à site  $\sigma_{site}$  (variabilité intra-plaque), des variabilités liées à l'équipement de mesure  $\sigma_{équipement}$  de mesure et enfin des

<sup>13</sup> Le batch est défini comme un ensemble de deux ou plusieurs lots, par exemple lors d'une opération de diffusion, 6 lots sont disposés ensemble dans le four. On parle donc d'un batch de 6 lots)

variabilités liées à la nature de produit  $\sigma_{produit}$ . La variabilité non expliquée constitue les résidus<sup>14</sup>. On définit la variabilité totale alors comme étant la somme :

$$\sigma_{Tot}^2 = \sigma_{batch}^2 + \sigma_{Lot}^2 + \sigma_{Plaque}^2 + \sigma_{sites\ de\ mesures}^2 + \sigma_{Equipement\ de\ fabrication}^2 + \sigma_{Equipement\ de\ mesure}^2 + \sigma_{produit}^2 + Résidus \quad (1.1)$$

Afin de réduire ces variabilités, des boucles de régulations sont conçues. Le principe est de réajuster un ou plusieurs paramètres du procédé en temps réel en fonction des mesures physiques ou électriques des lots précédents ; ceci, suivant un modèle établi à partir des expériences ou à partir d'un historique de données regroupant des mesures de métrologie et des données équipements. Il faut noter qu'on ne peut réguler que sur les perturbations non aléatoires (perturbations qui peuvent être modélisées). On peut distinguer deux types de boucles de régulation :

- les boucles de régulation de type « Feed Forward ». Ce type de boucle est utilisé pour rattraper la variabilité (la dispersion) observée sur l'étape de fabrication N en modifiant les paramètres de la recette de l'étape (N+1). Ce type de boucles est connu aussi sous le nom de « Boucles inter-process » quand il s'agit d'agir sur le procédé (N+1) connaissant la dispersion du procédé N. Par exemple, dans le cas de la boucle entre le procédé de dépôt chimique en phase vapeur et le procédé de polissage mécano-chimique (CVD – CMP) comme c'est illustré sur la figure 1.6. La vitesse d'enlèvement est modifiée de plaque à plaque suivant les valeurs des épaisseurs de dépôt sur chaque plaque.

Figure 1.6- Schéma de deux boucles de régulation Feed back et Feed forward

- les boucles de régulation de type « Feed Back » sont déployées généralement sur un même équipement à partir des mesures de métrologie des lots précédents (N-1). L'écart de la valeur mesurée de la plaque du lot (N-1) permet d'estimer la valeur du paramètre équipement pour le lot (N). La figure 1.6 montre un exemple de boucle « Feed back » au niveau du procédé de polissage mécano-chimique (CMP). La valeur de l'épaisseur d'oxyde enlevée est renvoyée au contrôleur pour calculer un nouveau temps de polissage (une nouvelle vitesse d'enlèvement).

Ce concept de déploiement des boucles de régulation a fait ses preuves dans les sites de production dans le monde des semi-conducteurs. AMD a été le premier fabricant de composants à semi-conducteurs à se lancer dans l'automatisation de la FAB en implémentant des boucles de régulation (R2R) au niveau de l'étape de fabrication de polissage mécano-

<sup>14</sup> La différence entre la valeur de la variabilité totale observée et la variabilité totale estimée.

chimique (CMP). Le rendement de fabrication au niveau de cette opération de fabrication a été amélioré grâce à l'implémentation de ces boucles.

Toutefois avant de déployer une telle boucle, il faut identifier les étapes critiques<sup>15</sup>. Ceci passe généralement par une étude de la variabilité de l'état actuel des procédés et l'estimation du gain attendu avec le contrôle.

Nous verrons dans l'état de l'art qui suit les différents travaux relatifs aux techniques de contrôle dans le milieu académique ainsi que le succès qu'ont eu ces techniques dans le milieu industriel.

## 1.2 Etat de l'art sur le contrôle et la modélisation des procédés

Dans cette partie, nous exposerons un état de l'art détaillé sur le contrôle et la modélisation des procédés au niveau académique et industriel. Suite à cet état de l'art, une stratégie sera définie pour déterminer les actions à effectuer en vue du déploiement des boucles de régulation R2R

### 1.2.1 Travaux sur le contrôle et la modélisation des procédés

Les problèmes de contrôle des procédés en microélectronique peuvent être classés en quatre catégories [EDGAR 2000]:

- la gestion ou le management de l'usine (FAB)

- le contrôle des contaminations (défectivité)

- la manipulation des matériaux

- le contrôle des opérations de fabrication

Sur ce dernier point, beaucoup d'efforts ont été déployés au niveau de l'ordonnancement des lots et au niveau du flux de transfert des lots sur les différents équipements qualifiés. Par contre, moins d'efforts ont été mis en œuvre dans le cadre de l'amélioration du contrôle des différentes opérations de fabrication.

Les principales opérations de fabrication sont : l'oxydation, le dépôt (de diélectriques et de métaux), la diffusion, le dépôt physique en phase vapeur, l'implantation ionique, la photolithographie<sup>16</sup>, la gravure<sup>17</sup> (sèche ou humide) et le polissage mécanico-chimique. Les premières études de modélisation et de contrôle ont été focalisées sur les opérations de photolithographie, de dépôt et de gravure sèche. Des travaux sur la modélisation et le contrôle des opérations de fabrication (photolithographie, dépôt et gravure sèche) ont été présentés par Badgwell en 1995[BADGWELL 1995]. Dans le milieu industriel, les procédés de dépôt et de gravure sèche sont modélisés de manière empirique. Cette modélisation est souvent faite avec l'aide de la connaissance approfondie des mécanismes physiques/chimiques régissant les procédés. Comme les limites de spécifications deviennent de plus en plus serrées pour les

---

<sup>15</sup> Etapes ayant une influence importante sur la suite des opérations.

<sup>16</sup> Une technique qui permet de délimiter des zones à la surface de la plaque pour les traiter différemment du reste de la surface lors d'une opération ultérieure (gravure, dopage).

<sup>17</sup> Une technique qui permet d'attaquer un matériau présent sur la plaque dans des zones non protégées par un masque.

nouvelles technologies, ce manque de connaissances approfondies des mécanismes physiques/chimiques régissant les procédés va poser problème.

Le contrôle des procédés de fabrication de composants à semi-conducteur a été étudié par à un certain nombre d'universités et de laboratoires de recherche industrielle parmi lesquels, U.C. Berkeley [LEE 1995] et [MAY 1991]. Leur travail portait sur la modélisation statistique et le contrôle des équipements de gravure plasma. Les équipes de l'université du Michigan [HAMBY 1998] travaillaient sur les boucles R2R en utilisant une modélisation multivariée et un contrôle en temps réel. Le laboratoire MIT [BONING 1995, BONING 2004] s'est focalisé sur l'étude des capteurs et sondes pour les équipements et les systèmes de contrôle. Les groupes de recherche de l'université du Maryland [ADIVIKOLANU 2000, BARAS 1996, ZAFIRIOU 1995] ont développé beaucoup de travaux relatifs aux algorithmes R2R. De son côté, SEMATECH<sup>18</sup> [BAKSHI 1997], a publié plusieurs papiers relatifs aux problèmes rencontrés par la FDC sur les équipements de gravure sèche.

Le contrôle non-linéaire des opérations de R2R a été proposé par [DEL CASTILLO 1998]. À l'université d'Austin ont été développées des boucles de régulation à base de cartes de contrôle de type moyenne mobile avec pondération exponentielle (EWMA : Exponentially Weighted Moving Average) et de double EWMA qui tiennent compte du retard de la métrologie [Good 2002] et [Good 2005]. Le but de ces travaux est d'apporter une robustesse et une stabilité<sup>19</sup> aux boucles. Ils ont aussi travaillé sur la surveillance statistique multivariée des équipements RTA (Rapid Thermal Annealing) ou bien (Recuit Thermique Rapide), sur les équipements de gravure [Yue 2000] et [Yue 2001] ainsi que sur le contrôle statistique multivarié des données de métrologie des dimensions critiques de la grille du transistor, ces dimensions sont généralement symbolisées par CD (Critical Dimensions) [Cherry 2003]. D'autres applications de contrôle avec la FDC sont rapportées par Del Castillo et Hurwitz [DEL CASTILLO 2000] et par James Moyne [MOYNE 2001].

## **1.2.2 Le contrôle avancé des procédés (APC : Advanced Process Control) dans le milieu industriel**

### **1.2.2.1 Chez ST Microelectronics**

En 2000, une boucle de contrôle a été mise en place sur les équipements de diffusion<sup>20</sup>. Les équipements sont des fours fonctionnant à de hautes températures. Pendant la même année, une autre boucle a été réalisée sur les équipements de photolithographie au niveau de la fabrication de la grille du transistor. L'objectif de cette boucle était de contrôler le CD et l'indice de recouvrement appelé autrement Overlay au niveau de la fabrication de la grille du transistor. Le logiciel qui gère la gestion de cette boucle est « EPCC ». Ce programme a été développé sur ST-Crolles. En 2002, une boucle de régulation au niveau du procédé de polissage mécanico-chimique (CMP) a été réalisée. Le principe de cette boucle était de réajuster le temps de polissage afin de garantir la même épaisseur enlevée. Le réajustement ne se fait pas de lot à lot mais après chaque tâche de qualification<sup>21</sup> sur l'équipement. En 2005, une boucle sur les équipements de dépôt d'oxyde (CVD) a été réalisée. L'objectif de cette boucle était d'automatiser les tâches de qualifications qui se

---

<sup>18</sup> SEMATECH un consortium réunissant les principaux fabricants de semi-conducteur

<sup>19</sup> Le bon fonctionnement d'un procédé de contrôle actif est conditionné par la stabilité comportementale du système en boucle fermée. Il est courant d'étudier les pôles du système afin d'en déterminer ses conditions de stabilité.

<sup>20</sup> Procédé thermique permettant l'obtention des films d'oxydes

<sup>21</sup> Les premières opérations pour qualifier un procédé.

faisaient avant manuellement. En 2006, une boucle de type feed-forward a été réalisée sur le module de la grille et en 2007, les boucles sur le module STI faisant partie de mon sujet de thèse ont été mises en pré-production. Nous reviendrons en détails sur le principe de ces boucles dans le chapitre 4.

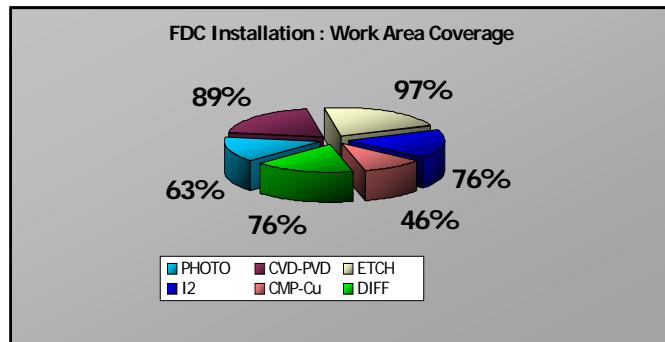

Sur le volet du déploiement de la FDC, le taux de déploiement des outils de la FDC a touché la plupart des équipements utilisés dans la FAB (200mm) comme c'est illustré sur la figure 1.7.

Figure 1.7- Le taux de déploiement de la FDC par type d'équipements

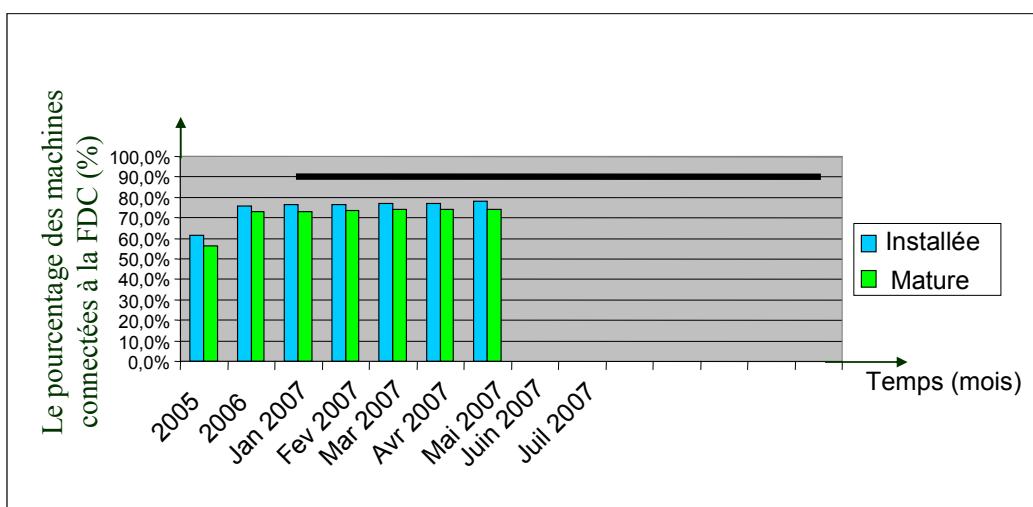

On constate que sur les équipements de gravure (etch), 97% des équipements sont équipés de la FDC. Le déploiement de la FDC a commencé en 2004. Le taux de déploiement est en forte progression, comme cela est illustré sur la figure 1.8. Il est évident qu'avant de lancer la FDC sur un équipement donné en production, il faut déjà installer l'outil FDC pour collecter le maximum de données. Si le mécanisme de collecte de données et le nombre de variables choisies à surveiller sont satisfaisants, il faut ensuite passer à l'étape de la mise en production. Ce protocole de la mise en production explique l'écart de pourcentage entre les outils de la FDC installés et les outils matures<sup>22</sup> comme cela est aussi illustré sur la figure 1.8.

Figure 1.8- Taux de déploiement de la FDC en fonction du temps

Les outils de FDC à installer diffèrent d'un équipement à un autre car certains fabricants d'équipements développent leurs propres outils de FDC et par conséquence ils n'acceptent pas que d'autres outils soient connectés sur leurs équipements. On peut citer : la

<sup>22</sup> Mise en production.

société TEL (spécialisée dans la fabrication des fours) qui a développé un logiciel « Ingénio ». Un autre fabricant, Lam Station a développé un logiciel pour le suivi de la FDC sur les équipements de gravure sèche. Les autres équipements sont connectés pour la plupart par les outils « Maestria » développés par la société PDF Solutions. On peut voir cette tendance en fonction du temps sur la figure 1.9.

Figure 1.9- Les différents types des outils de la FDC en fonction de temps

En mai 2007, le nombre d'équipements équipés de la FDC est évalué à 241 sur un nombre total de 308 équipements. Comme pour toutes les autres compagnies de fabrication des semi-conducteurs, l'objectif est d'atteindre la barre des 100% [LAHAV 2005]. ST Microelectronics continue ses actions pour améliorer le taux d'équipements équipés par la FDC pour atteindre à terme la barre des 100%.

### 1.2.2.2 Les autres compagnies

Les réalisations APC dans les autres compagnies de fabrication de semi-conducteurs