## Design of CMOS analog integrated circuits as readout electronics for High-TC superconductor and semiconductor terahertz bolometric sensors

Vratislav Michal

## ▶ To cite this version:

Vratislav Michal. Design of CMOS analog integrated circuits as readout electronics for High-TC superconductor and semiconductor terahertz bolometric sensors. Micro and nanotechnologies/Microelectronics. Université Pierre et Marie Curie - Paris VI, 2006. English. NNT: . tel-00417838v2

## HAL Id: tel-00417838 https://theses.hal.science/tel-00417838v2

Submitted on 21 Sep 2009

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Ph.D. THESIS

# DESIGN OF CMOS ANALOG INTEGRATED CIRCUITS AS READOUT ELECTRONICS FOR HIGH-T<sub>C</sub> SUPERCONDUCTOR AND SEMICONDUCTOR TERAHERTZ BOLOMETRIC SENSORS

Вy

### **VRATISLAV MICHAL**

THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSPHY

### UNIVERSITY PIERRE ET MARIE CURIE,

Laboratory: Laboratoire de Génie Electrique de Paris

Approved by: BRNO UNIVERSITY OF TECHNOLOGY

Laboratory: Department of Theoretical and Experimental Electrical Engineering

Defended: 10th of June 2009

## Committee in charge:

| Prof. Alain Kreisler            | UPMC Univ. Paris 6                 | Supervisor       |

|---------------------------------|------------------------------------|------------------|

| Assoc. Prof. Jiří Sedláček      | Brno University of Technology      | Supervisor       |

| Prof. Pascal Fouillat           | Université de Bordeaux 1           | Examiner         |

| Assoc. Prof. Pravoslav Martínek | Czech Technical University, Prague | Examiner         |

| Prof. Aziz Benlarbi-Delaï       | UPMC Univ. Paris 6                 | Committee Member |

| Prof. Dalibor Biolek            | Brno University of Technology      | Committee Member |

| Dr. Geoffry Klisnick            | UPMC Univ. Paris 6                 | Invited member   |

| Prof. Annick Dégardin           | UPMC Univ. Paris 6                 | Invited member   |

#### THESE DE DOCTORAT DE L'UNIVERSITÉ PIERRE ET MARIE CURIE

Spécialité : Sciences pour l'ingénieur - Mention : Électronique

Approuvée par:

### L'UNIVERSITÉ TECHNIQUE DE BRNO

Présentée par

M. Vratislav Michal

Pour obtenir le grade de

### DOCTEUR DE l'UNIVERSITÉ PIERRE ET MARIE CURIE

#### Sujet de la thèse :

CONCEPTION DE CIRCUITS INTÉGRÉS CMOS ANALOGIQUES POUR L'ELECTRONIQUE DE LECTURE DE CAPTEURS BOLOMÉTRIQUES THZ À BASE DE SEMICONDUCTEURS OU DE SUPRACONDUCTEURS À HAUTE TEMPÉRATURE CRITIQUE

Soutenue le 10 Juin 2009

Devant le jury composé de :

UPMC Univ. Paris 6 Directeur de thèse **Prof. Alain Kreisler** Assoc. Prof. Jiří Sedláček Brno University of Technology Directeur de thèse Prof. Pascal Fouillat Université de Bordeaux 1 Rapporteur Assoc. Prof. Pravoslav Martínek Czech Technical University, Prague Rapporteur Prof. Aziz Benlarbi-Delaï UPMC Univ. Paris 6 Examinateur Prof. Dalibor Biolek Brno University of Technology Examinateur Dr. Geoffry Klisnick UPMC Univ. Paris 6 Invité UPMC Univ. Paris 6 Invité Prof. Annick Dégardin

Université Pierre & Marie Curie - Paris 6 Bureau d'accueil, inscription des doctorants et base de données Esc G, 2ème étage 15 rue de l'école de médecine 75270-PARIS CEDEX 06 Brno University of Technology Faculty of Electrical Engineering and Communication Údolní 244/53, 602 00 BRNO CZECH REPUBLIC

$\underline{\text{E-mail author}}: vratislav.michal@gmail.com$

## Acknowledgements

My PhD thesis presents a work elaborated in an intense collaborative context. It is therefore my pleasant task to express my gratitude to the persons and institutions which contributed to the thesis and helped me to develop my professional skills. First of all, I am very grateful that my supervisors accepted me for this thesis: Mr. *Jiří Sedláček* from UTEE VUT in Brno (Czech Republic) and Mr. *Alain Kreisler* from LGEP-Supélec (France).

My first contact with the research area started long before my thesis, by the contact with first named Mr. J. Sedláček. Mr. Sedláček permitted me to pass from the passionate amateur-radio world encountered in the electronics group of the Olomouc youth centre, leaded by Karel Vrtěl OK2VNJ, - to the word of academic and industrial research. At this period, Mr. Sedláček actively supplied me with interesting research tasks and helped me to acquire appropriate specific competences. Thanks to him, I also made acquaintance with people such as Bohumír Sviežený from ISEP-Paris engineering school, Karel Hájek from Military Academy of Brno or Stanislav Sedlák from S3 electronic company, all confirmed in the field of analog electronics. I was fortunate to spend long time with Professor Hájek, in a unique way by working, experimenting, and having unending discussions. This, looking back, mostly influenced my future centre of interests and workflow, and motivated me for my future work in the field of analogue electronics and analog signal processing.

Starting the Ph.D thesis at the end of 2004 has been based on the collaboration and excellent guidance of all these mentioned persons. As the work progressed, my attention has been more and more attracted to electronics, rather integrated than discrete ones. This because I estimated some electrical performances as being limited in the discrete-components word, and the neverending drilling of the printed circuit boards started to be boring. Therefore, I applied to the internship Nanotime located in the Paris engineering school Supélec, leaded by Ms. *Annick Dégardin*. This internship, of which the results expressively contributed to the thesis, gave me a possibility to discover the domains of the ultimate quantum and low-temperature physics, and allowed me to capitalize my experiences from the previous work and research in the field of applied analogue electronics.

A major importance of this internship was the possibility to collaborate with L2E laboratory of Paris 6 university (LISIF at the time). This presented dissertation would not have been possible without the expert guidance of the colleagues which I meet there, namely *Geoffry Klisnick, Gérard Sou, Michael Redon and Damien Prêle*. The initiations to the design of CMOS circuits or layout were always extremely perceptive, helpful, and appropriate; the passionate "eternal" discussions about the designed circuits are only a small fragment of the good memories which I will remember from this collaboration.

The role of my colleagues at L2E laboratory was also essential during the final – and difficult phase of the thesis writing. I executed many long travels from Grenoble, when I was employed at the time in "Commissariat à l'Energie Atomique". During these staying in L2E, I obtained many corrections and remarks of a crucial importance. During the long discussion with all above named colleagues, we clarified the basic ideas to be highlighted in the thesis. Here, I wish to underline my gratitude to Professor M. Redon for his time-expensing and rigorous verification of all mathematical theorems presented in the thesis. The provided instructions, together with the clear and well-oriented instructions and advices of Mr. Sedláček presented the main guide-line during the thesis writing. The final typographic and form checking was a last important phase to ensure a best impression of the assembled thesis and I thank Prof. A. Kreisler to have taken part in this task.

During the elaboration of the thesis, I was surrounded by many skillful people, both from the academic and the research world. Even thought many discussions were important for the thesis elaboration, they also helped me to organize my thesis and socially survive some difficult situations during the thesis preparation. I give hereby only an incomplete list of names: Prof. Jarmila Dědková, and Prof. Karel Bartušek, who helped me with the preparation of the thesis contract. Next, Petr Drexler, Radek Kubásek, Mattia Longhin and Mario Aurino, the friends being on the Ph.D preparation at the time. Here, I have to thank also to other friends and colleagues who helped me during the thesis writing, especially with the English grammar: Vilém Guryča, Laurent Maingault, Panayotis Spathis, Bianca Hugo, and others. The finalization of the thesis was facilitated by the gratitude of Jean-Claude Villegier from CEA-INAC laboratory in Grenoble, which employed me at the second half-period of the thesis and allowed me to perform almost complete cryogenic characterization of the fabricated circuits in INAC laboratory. I also thank to Monique and Gilbert Zambetti, my favorite professor of the ballroom dancing for contributing to a meaningful stay and integration in Paris.

At the end, my sincere gratitude goes to my parents and my whole family, who supported me during my youth "radiometers" age, as well as during the following engineering studies. They sometimes made considerable efforts to surmount some "difficulties" related to my interest in electronics; such as the disorder continuously diffused from my "ham-shack", or by providing a protection against the attacks from our neighbors, perturbed by my unwanted electromagnetic radiation.

I therefore express, once again, my gratitude to all these above mentioned persons as well as to many others who could not be named in this short, but important paragraph.

# Table of contents

| Introduction | <br>vi |

|--------------|--------|

|              |        |

# I Theoretical introduction

| Bolometric Detectors                                 |     |

|------------------------------------------------------|-----|

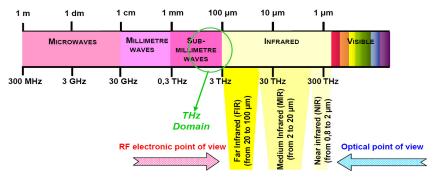

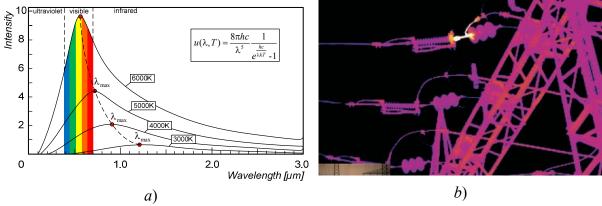

| 1.1 Terahertz Imaging                                |     |

| 1.2 Principal Detectors for the THz Area             |     |

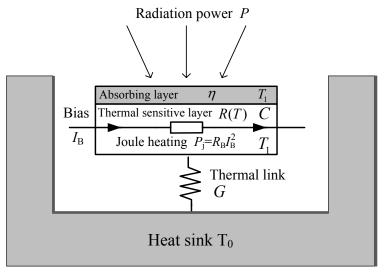

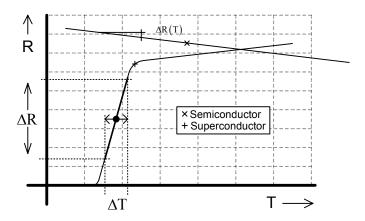

| 1.2.1 Bolometric Detectors                           |     |

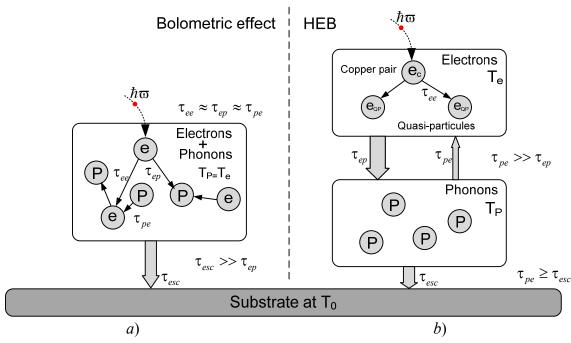

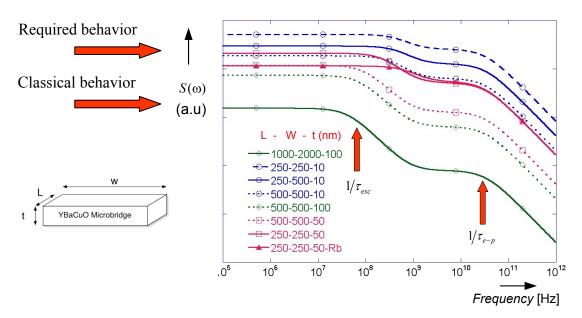

| 1.2.2 Hot Electron Bolometric Effect.                |     |

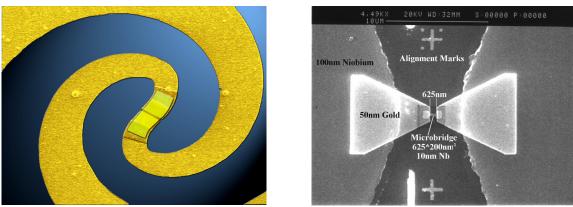

| 1.2.3 Variety of Bolometric Sensors                  |     |

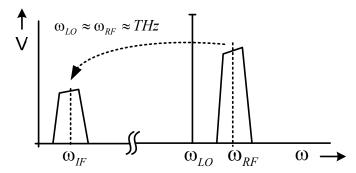

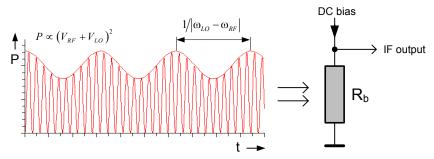

| 1.3 Heterodyne Detection                             |     |

| 1.4 Noise in Bolometric Detectors                    |     |

|                                                      |     |

| The Transistor MOS                                   | 9   |

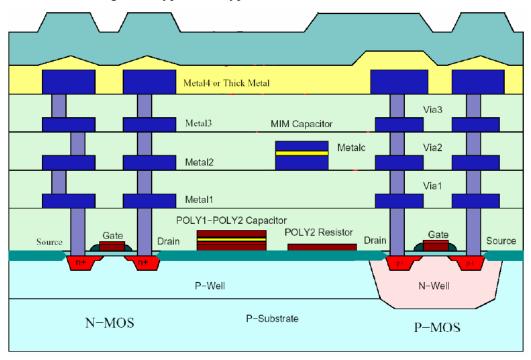

| 2.1 CMOS Device Overview                             | 9   |

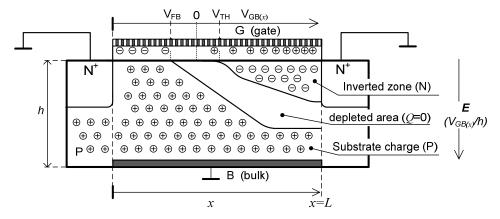

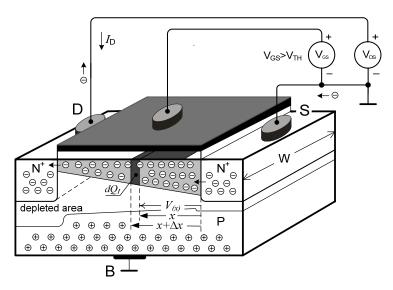

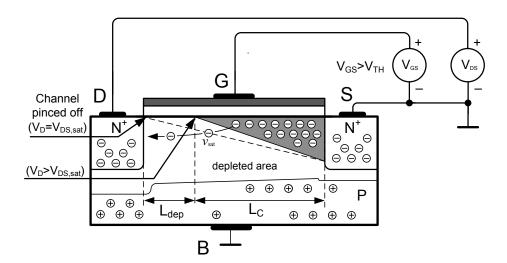

| 2.2 Physics of the MOS Transistor                    |     |

| 2.2.1 Semiconductors                                 |     |

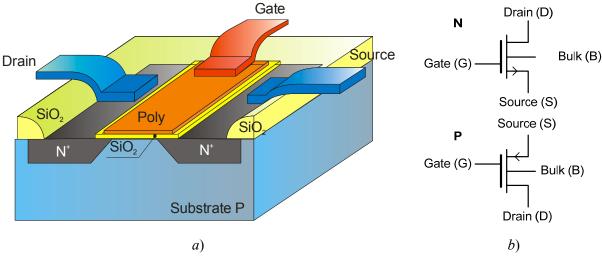

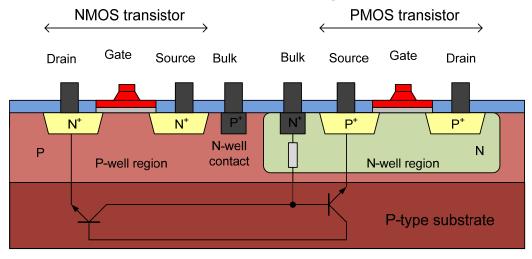

| 2.2.2 Physical Overview of the MOS Transistor        |     |

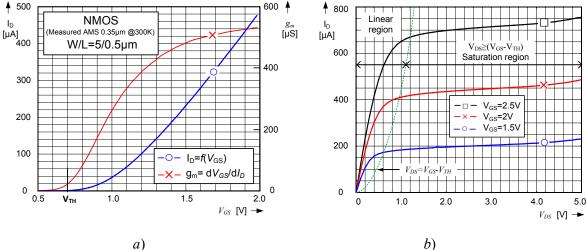

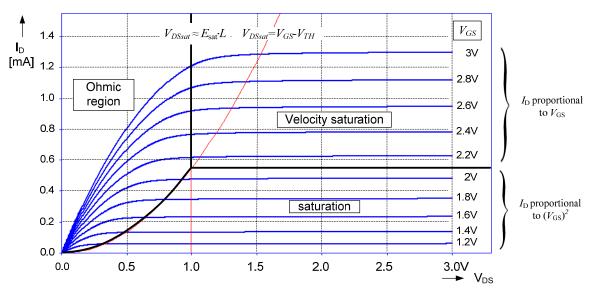

| 2.3 Electrical Characteristics of the MOS Transistor |     |

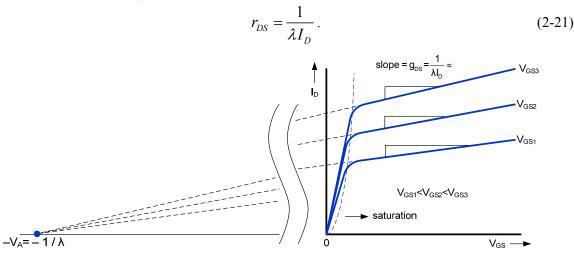

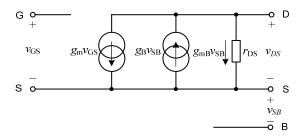

| 2.3.1 Static I-V Characteristic                      | 1.7 |

|                                                      | 16  |

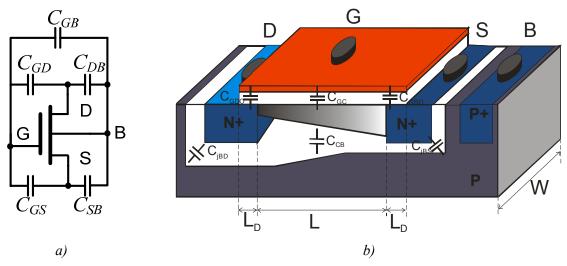

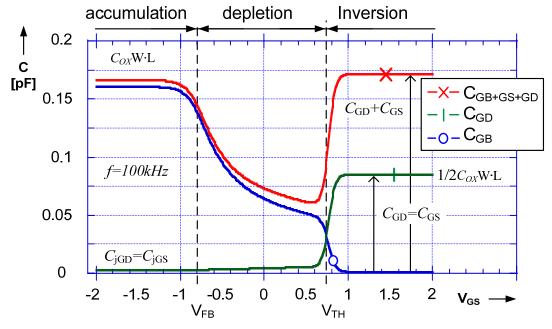

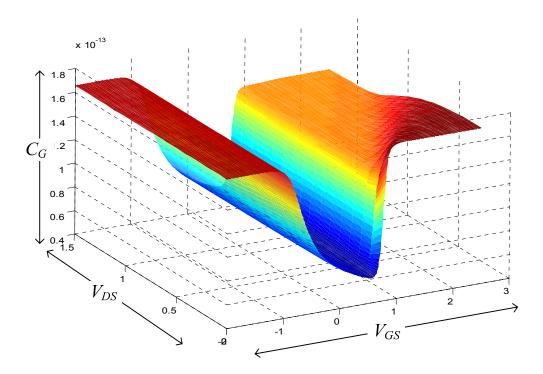

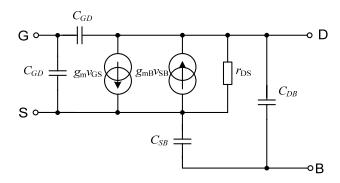

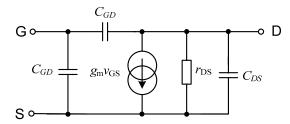

| 2.4 Parasitic Elements in the MOS Device            | 20   |

|-----------------------------------------------------|------|

| 2.4.1 Capacities in the MOS transistor              | 20   |

| 2.4.2 Small Scale Transistor Devices                | 23   |

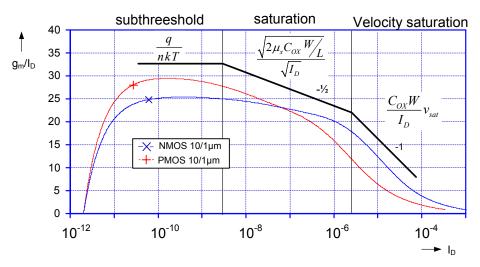

| 2.4.3 Figure of Merit of the MOS Transistor         | 25   |

| 2.5 Basic process parameters                        |      |

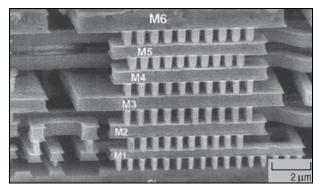

| 2.6 Trends in CMOS development                      | 27   |

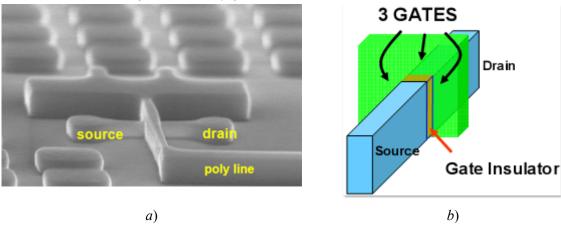

| 2.6.1 Very Low Dimension Transistors                | 28   |

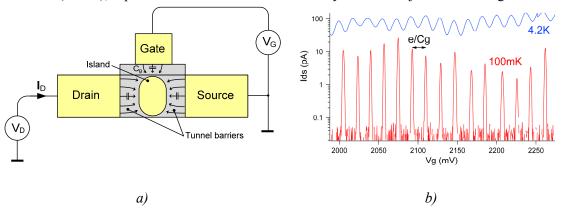

| 2.6.2 Single Electron Transistor                    |      |

|                                                     |      |

| Noise in Electronic Circuits.                       | . 30 |

| 3.1 Noise in Electronic Circuits                    |      |

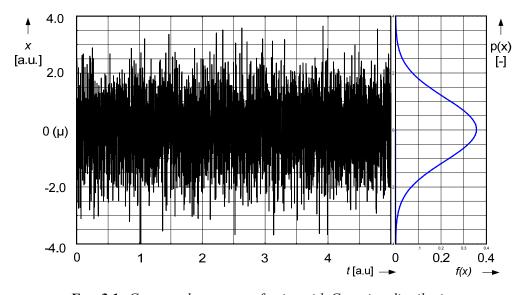

| 3.1.1 The Random Nature of Noise                    | 31   |

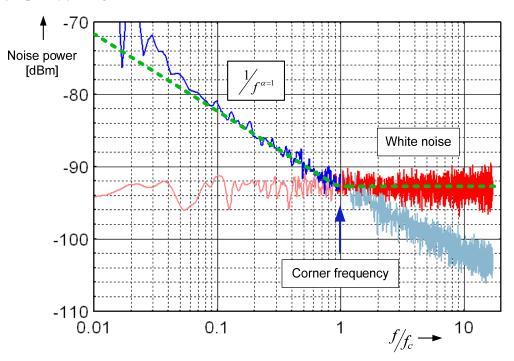

| 3.2 Noise Sources in Electronic Systems             | 32   |

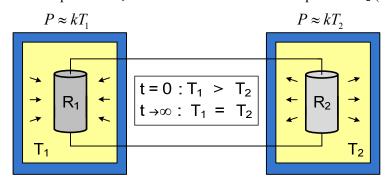

| 3.2.1 Thermal Noise                                 |      |

| 3.2.2 The 1/f <sup>\alpha</sup> Low Frequency Noise |      |

| 3.2.3 Shot Noise                                    |      |

| 3.2.4 Non-Electrical Noise Sources                  |      |

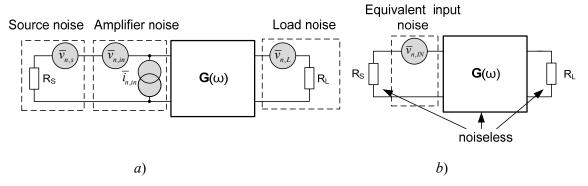

| 3.3 Noise Analysis, Basic Noise Characteristics     |      |

| 3.3.1 Signal to Noise Ratio SNR                     |      |

| 3.3.2 Noise Figure NF                               |      |

| 3.3.3 Noise Temperature                             |      |

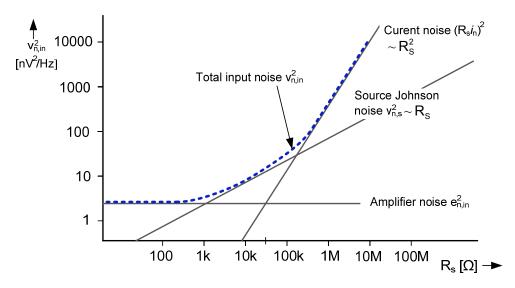

| 3.3.4 Equivalent Input Noise Voltage                |      |

| 3.3.5 Correlation                                   |      |

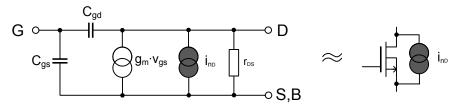

| 3.4 Noise in the MOS Transistors                    |      |

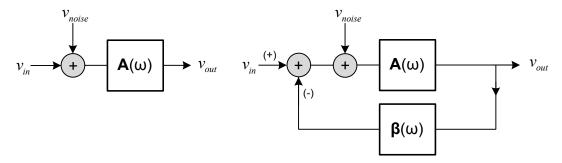

| 3.5 Low Noise Design                                |      |

| 3.5.1 Feedback in Electrical Circuits               |      |

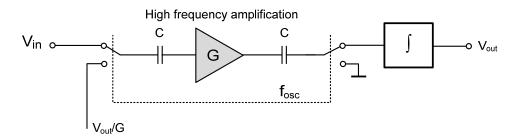

| 3.5.2 Chopper Amplifier                             |      |

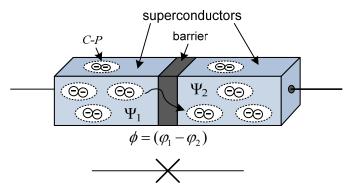

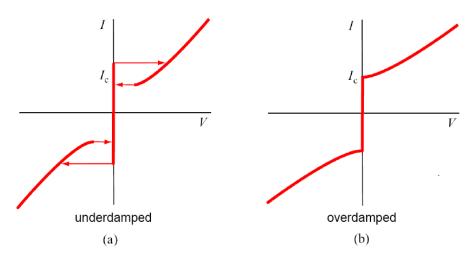

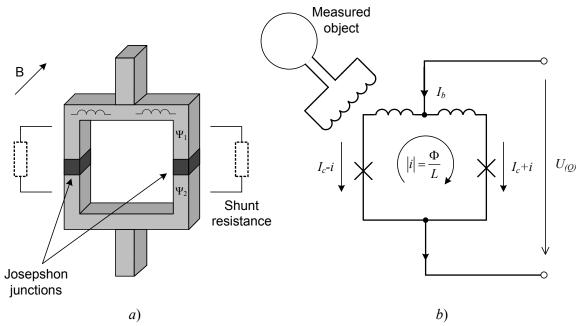

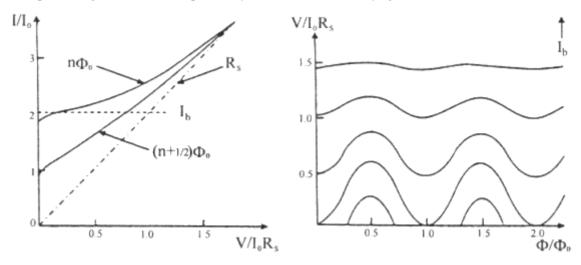

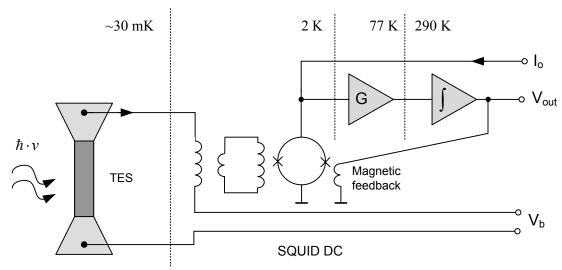

| 3.5.3 Superconducting Quantum Interference Device   |      |

| II Architecture of readout electronics              |      |

| Architecture of Readout Electronics.                | . 46 |

| 4.1 Electrical Specification of Sensors             |      |

| 4.2 Basic Concepts of Readout Electronics           |      |

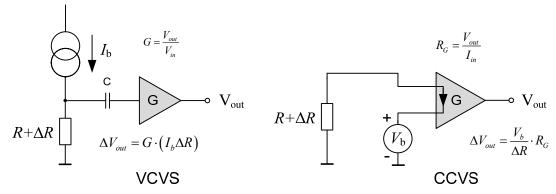

| 4.2.1 Current and Voltage Bias                      |      |

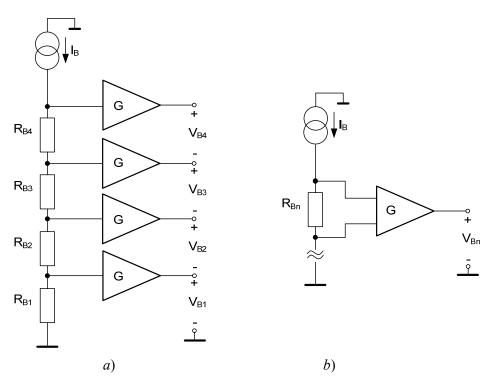

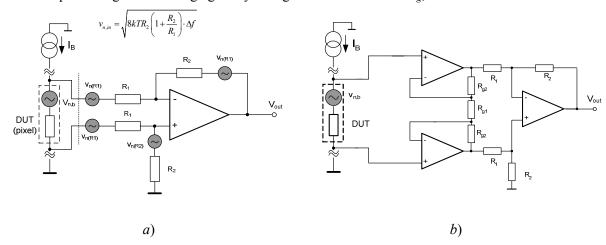

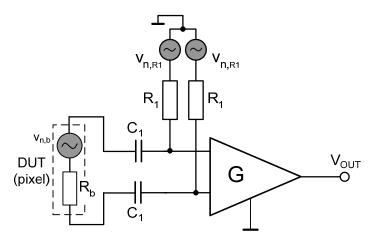

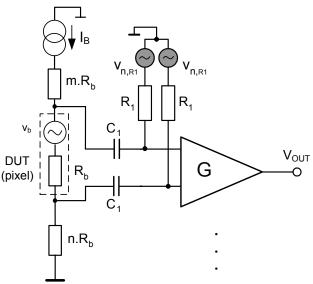

| 4.2.2 Differential Technique of Readout             | 49   |

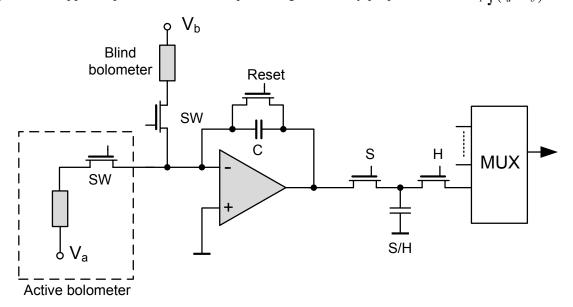

| 4.2.3 Special Readout Techniques                    | 50   |

| 4.3 Choice of Readout Configuration                 |      |

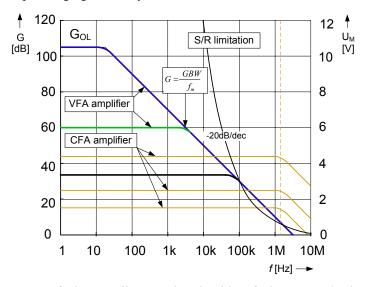

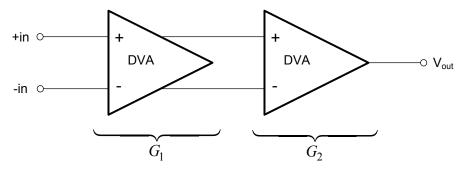

| 4.4 Differential Voltage Amplifiers                 | 52   |

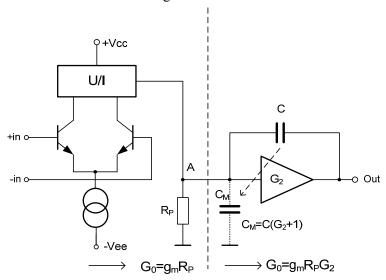

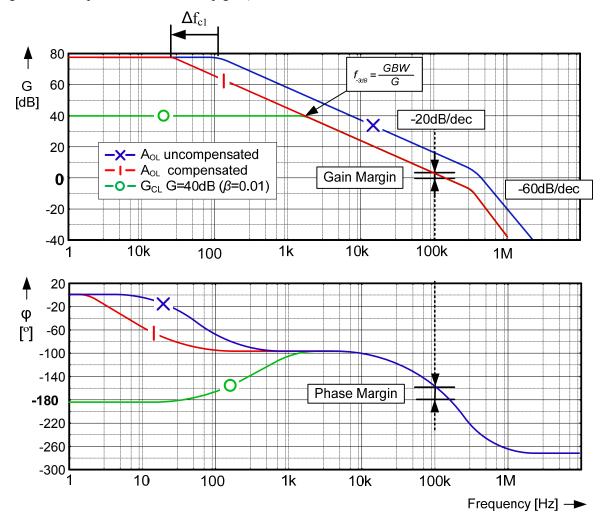

| 4.4.1 Dynamic Model of Operational Amplifier        |      |

| 4.5 Applications of Operational Amplifiers          | 57   |

| 4.5.1 Inverting Amplifier                           |      |

| 4.5.2 Differential Amplifiers                       |      |

| 4.5.3 Cryogenic Aspects                             |      |

| 4.6 Specification of Amplifiers to be Designed      | 60   |

| 4.6.1 Choice of CMOS/Bipolar Process                |      |

| 4.6.2 Choice of Amplifier Topology                  |      |

| 4.6.3 Specifications of Electrical Performances     |      |

| 4.7 Conclusion                                      |      |

# III Design of CMOS amplifiers

| Design of CMOS Fixed-Gain Differential Amplifiers                     | 64  |

|-----------------------------------------------------------------------|-----|

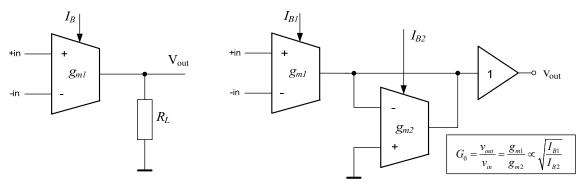

| 5.1 Constant Gain Amplifiers, Design Approaches                       | 64  |

| 5.1.1 Structures of Feedback-Free Voltage Amplifiers                  | 65  |

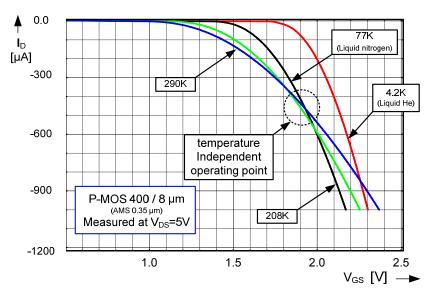

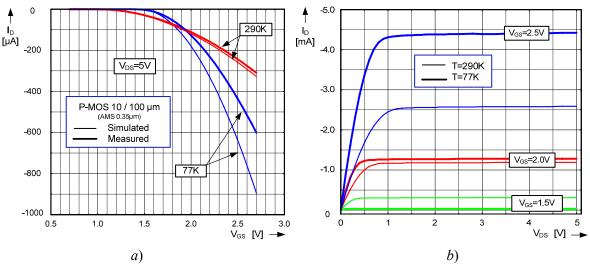

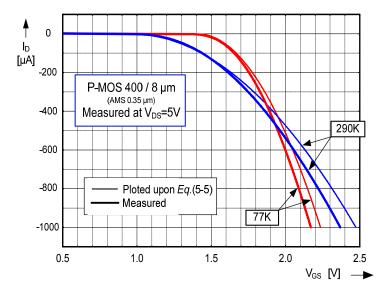

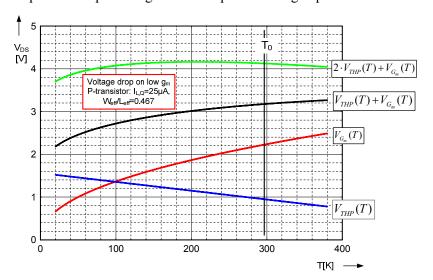

| 5.2 Temperature Modelling of the MOS Transistor                       | 65  |

| 5.2.1 Thermal Behaviour of the MOS Transistor                         |     |

| 5.2.2 Extraction of the Parameters                                    | 67  |

| 5.2.3 LS Model Parameters Fitting                                     | 68  |

| 5.2.4 Verification of the Model                                       |     |

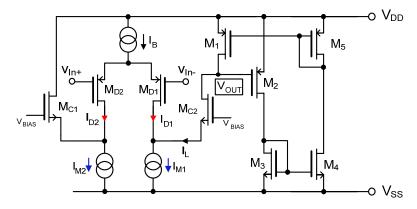

| 5.3 Structures of CMOS Fixed Gain Amplifiers                          | 70  |

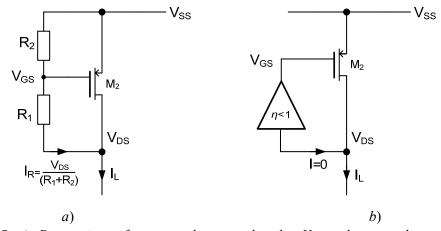

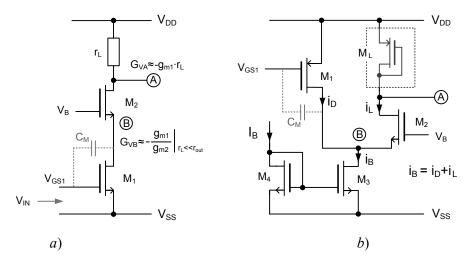

| 5.3.1 Common Source Amplifier                                         |     |

| 5.3.2 Increasing of the Voltage Gain                                  |     |

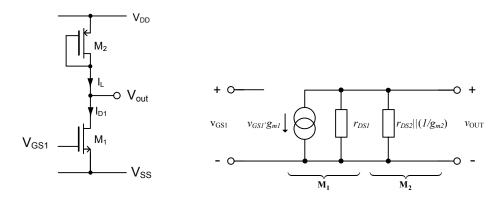

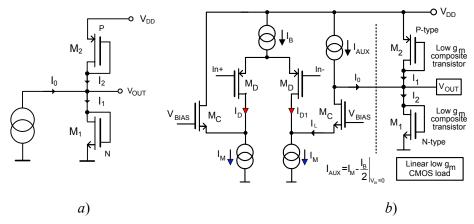

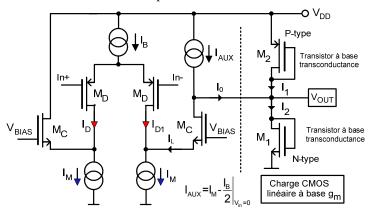

| 5.3.3 Adopted Solution: Low g <sub>m</sub> Active Load                |     |

| 5.3.4 Low g <sub>m</sub> Composite Transistor                         |     |

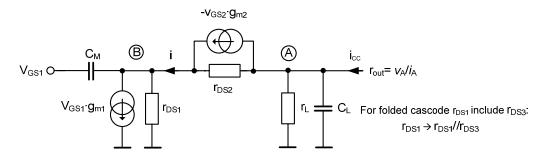

| 5.3.5 Analysis of the Low g <sub>m</sub> Composite Transistor         |     |

| 5.3.7 Common Source Amplifier with Low g <sub>m</sub> Load            |     |

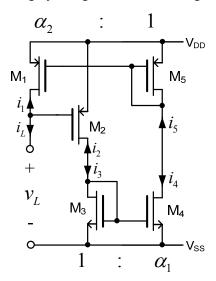

| 5.4 Differential Pair and Cascode Effect                              |     |

| 5.4.1 Cascode and Folded Cascode                                      |     |

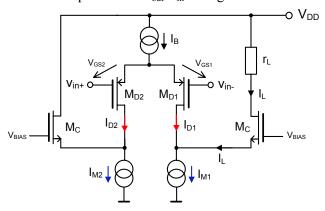

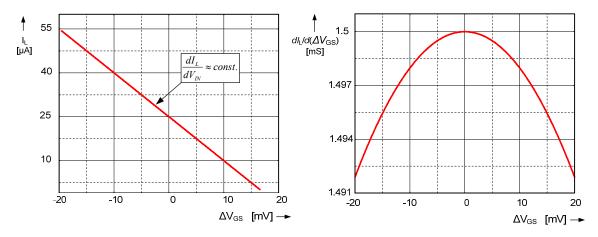

| 5.4.2 MOS Input Differential Pair                                     |     |

| 5.5 Amplifier with Low g <sub>m</sub> Composite Transistor            |     |

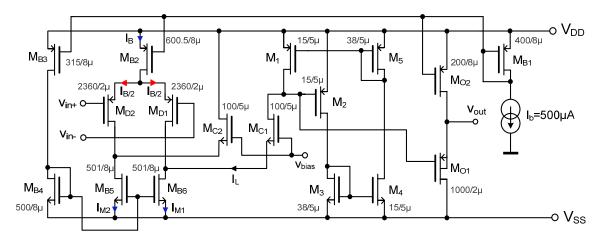

| 5.5.4 Summary of 1 <sup>st</sup> Amplifier Basic Parameters           | 90  |

| 5.6 Linear Temperature Compensated Amplifier                          |     |

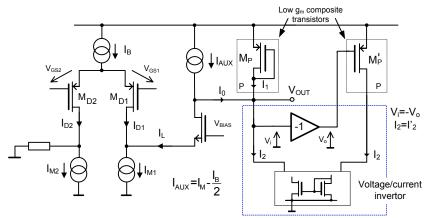

| 5.6.1 Low Transconductance Linear Composite Load                      |     |

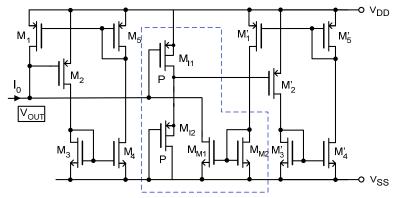

| 5.6.2 Differential Folded Cascode with Linear Load                    |     |

| 5.6.3 Basic Characteristics of the Linear Amplifier                   |     |

| 5.6.4 Analysis of the Temperature Behaviour.                          |     |

| 5.6.5 Design of the Type II Amplifier                                 |     |

| 5.6.6 Performances of the 2 <sup>nd</sup> (Linear) Amplifier: Summary |     |

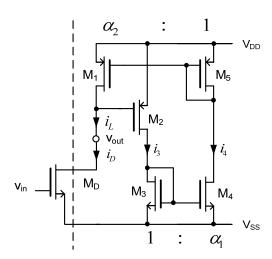

| 5.7 Output Voltage Buffer                                             |     |

| 5.7.1 Common Drain Voltage Follower                                   |     |

| 5.7.2 Linear Low Offset Voltage Buffer                                |     |

| Appendix: Simulated operating points                                  |     |

|                                                                       |     |

| AC and Noise Analysis                                                 | 102 |

| 6.1 AC Analysis of the Amplifier                                      | 102 |

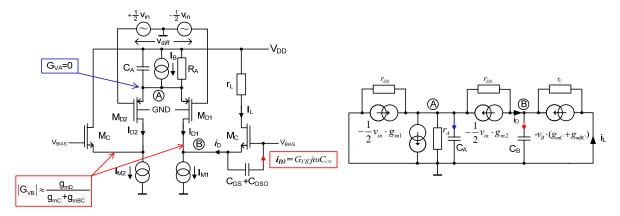

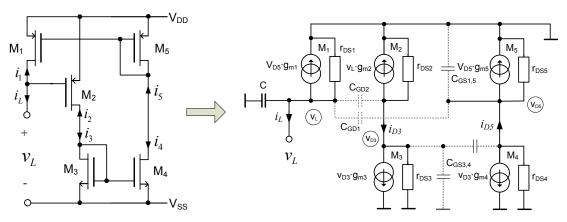

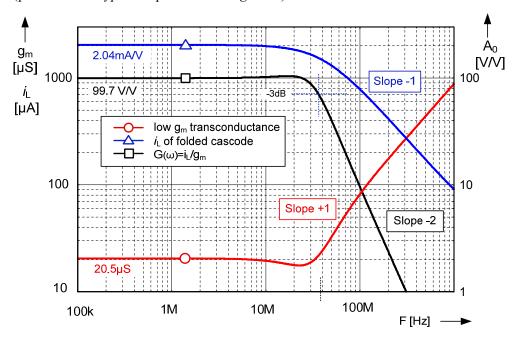

| 6.1.1 AC Response of Folded Cascode Transconductor                    | 102 |

| 6.1.2 Analysis of the Low g <sub>m</sub> Composite Transistor         | 104 |

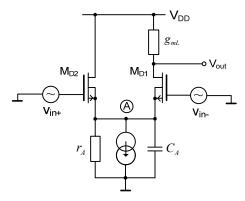

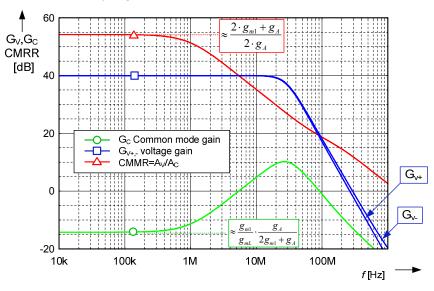

| 6.1.3 CMRRatio and the Gain Symmetry                                  | 105 |

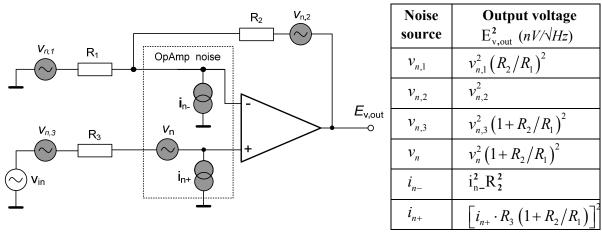

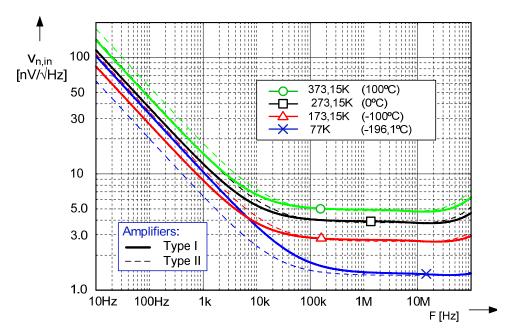

| 6.2 Noise of the Amplifier                                            | 108 |

| 6.2.1 Noise of the MOS Input Differential Pair                        | 108 |

| 6.2.2 Noise of the Low Composite Transistor                           | 110 |

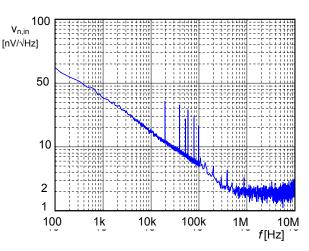

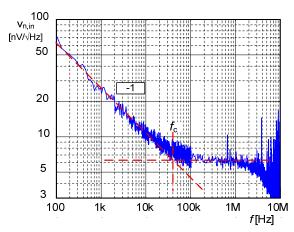

| 6.3.3 Noise Characteristic of the Amplifiers                          |     |

|                                                                       |     |

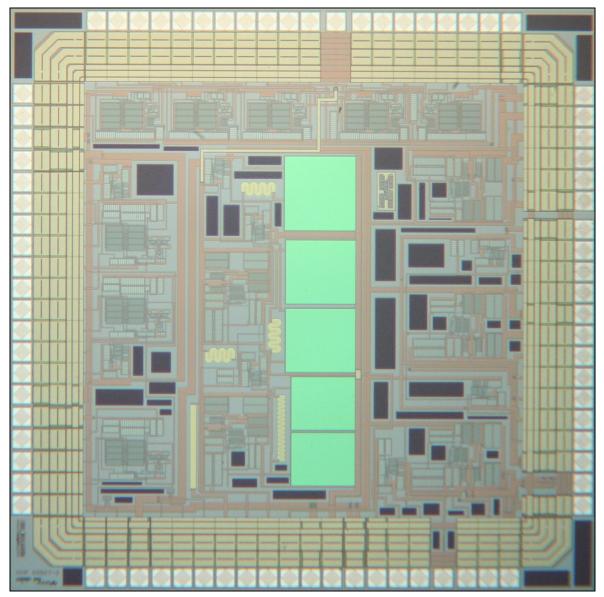

| Integration in CMOS AMS 0.35 μm: Results                              |     |

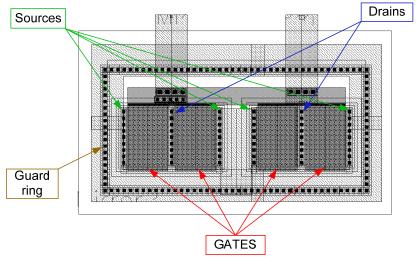

| 7.1 Layout of the Differential Amplifiers                             |     |

| 7.1.1 Matching of the MOS Transistors                                 |     |

| 7.1.2 Symmetric Layout, Common Centroid Structure                     |     |

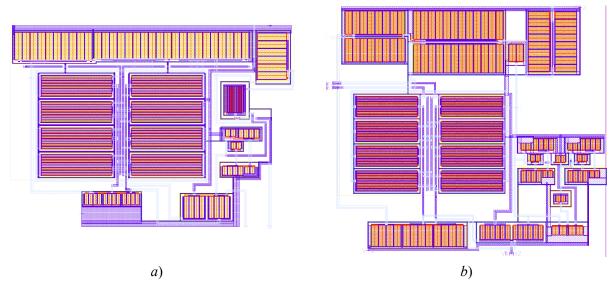

| 7.1.3 Layout of the Amplifiers                                        | 115 |

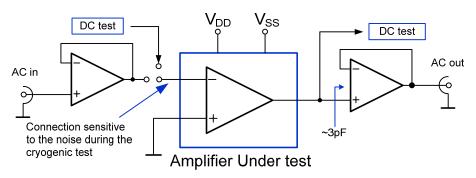

| 7.2 Testing the Amplifiers                               | 115 |

|----------------------------------------------------------|-----|

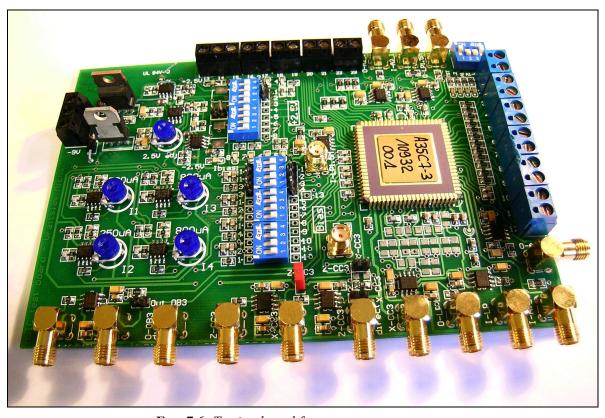

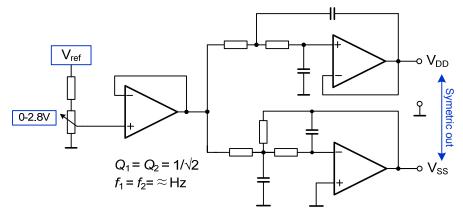

| 7.2.1 Test Facility                                      |     |

| 7.3 Type I Geometry-Fixed Gain Amplifier                 |     |

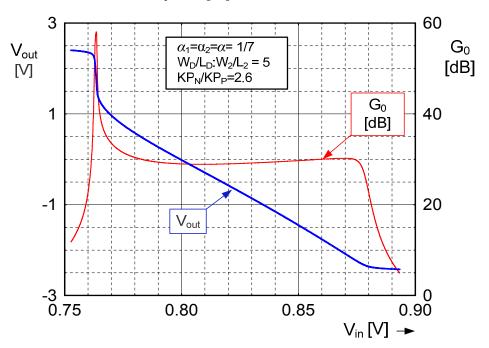

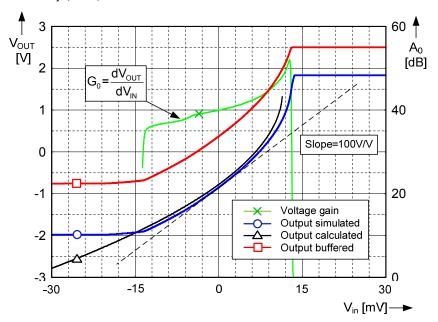

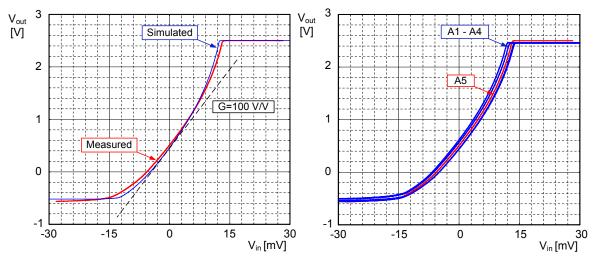

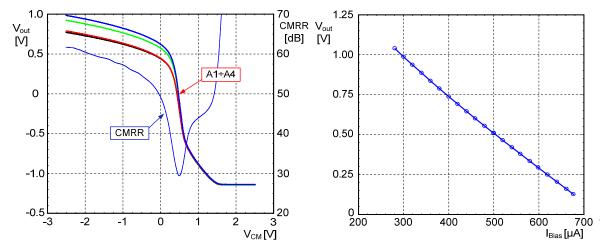

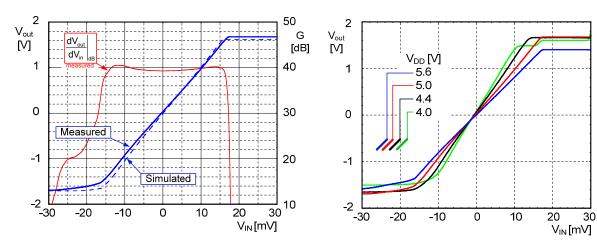

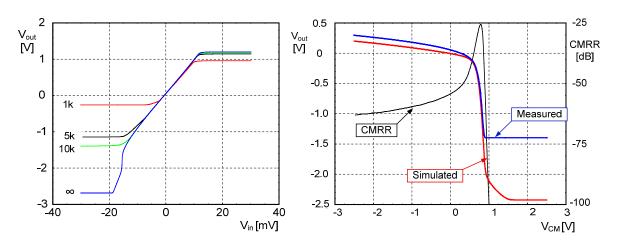

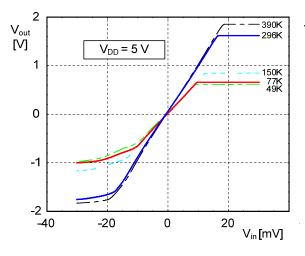

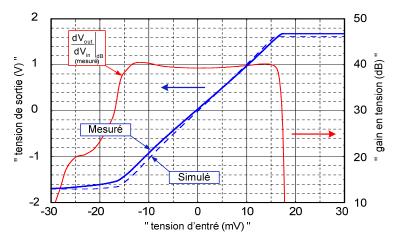

| 7.3.1 DC characteristics                                 |     |

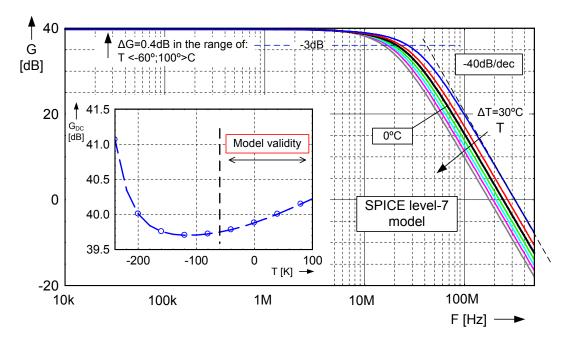

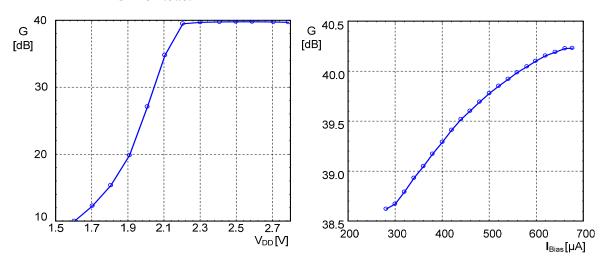

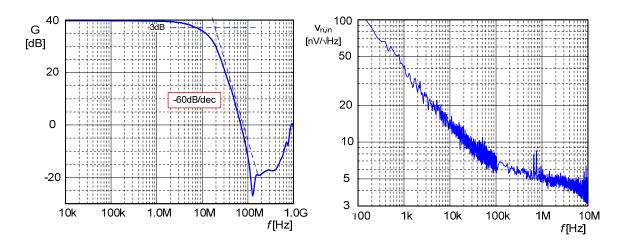

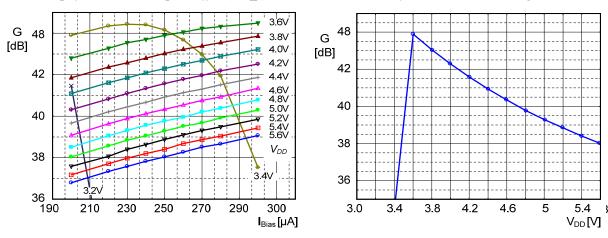

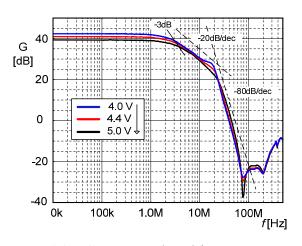

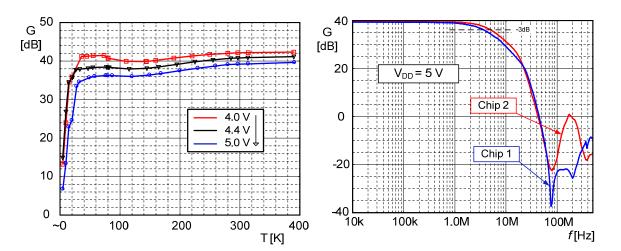

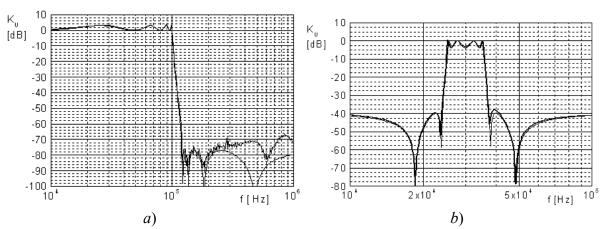

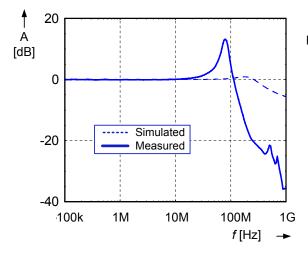

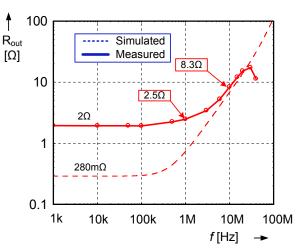

| 7.3.2 AC Performances of the 1 <sup>st</sup> Amplifier   | 120 |

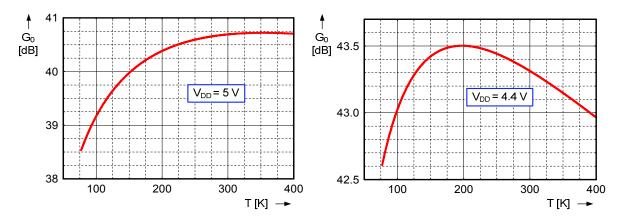

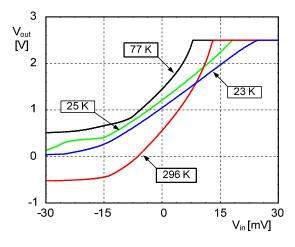

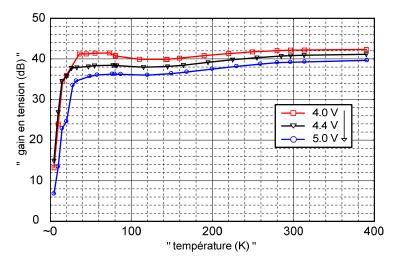

| 7.3.3 Wide Temperature Range Measurements                |     |

| 7.4 Type II Temperature-Compensated Linear Amplifier     | 122 |

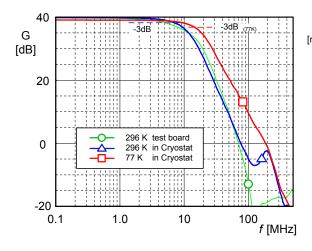

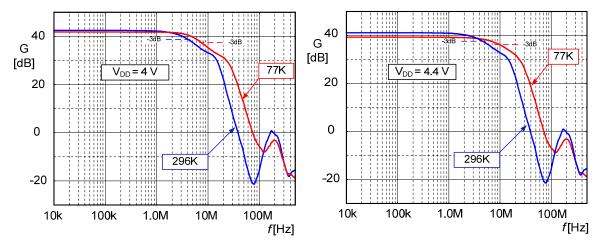

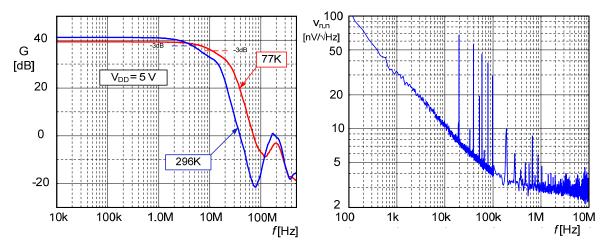

| 7.4.2 AC Performances of 2 <sup>nd</sup> Amplifier       | 124 |

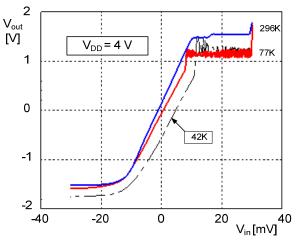

| 7.4.3 Cryogenic measurements of Type II amplifier        | 124 |

| 7.5 Summary of Achieved Results                          | 126 |

| 7.5.1 Comparison with the State-of-the-Art               | 127 |

| Conclusion of part III                                   | 129 |

|                                                          |     |

| IV High performance active frequency filters             |     |

| Design of active frequency filters                       | 131 |

| 8.1 Frequency Filters in the Amplification Chain         |     |

| 8.2 Scope of the Work                                    |     |

| 8.3 Design Approaches to Active Frequency Filters        |     |

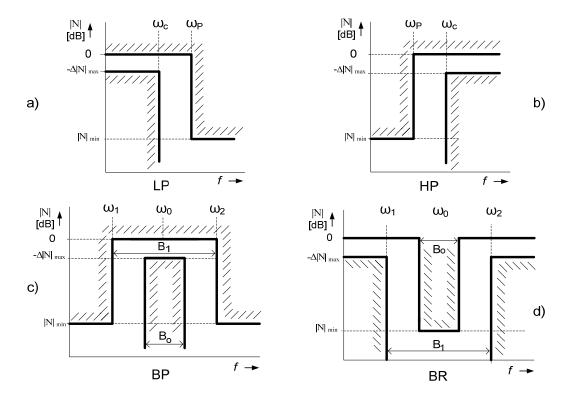

| 8.3.1 Approximation of Transfer Function                 |     |

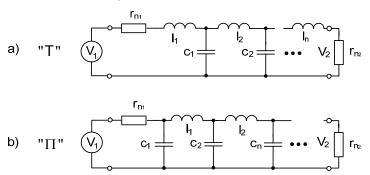

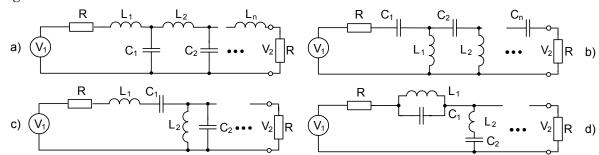

| 8.3.1 Design of Passive RLC Ladder Filters               |     |

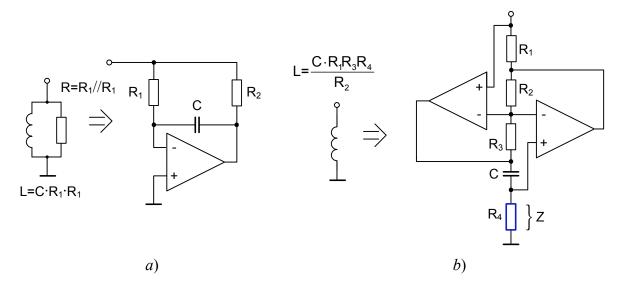

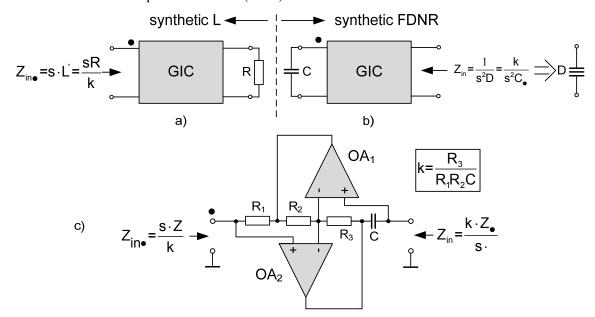

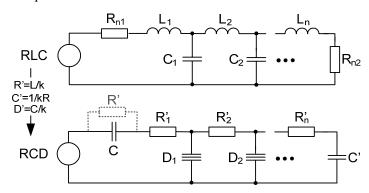

| 8.3.2 Active Simulation of Passive RLC Filters           |     |

| 8.3.3 Cascade Synthesis of Frequency Filters             |     |

| 8.4 Imperfections of Frequency Filters                   |     |

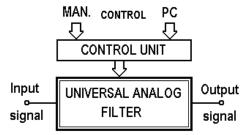

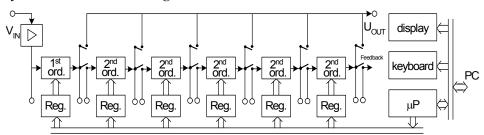

| 8.5 Digitally Controlled Analog Filtering Systems        |     |

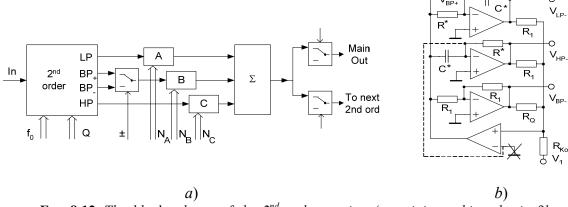

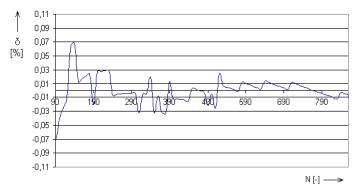

| 8.5.1 Structure of the Universal Analog Frequency Filter |     |

| 8.5.2 Electrical Design of Filter Blocks                 |     |

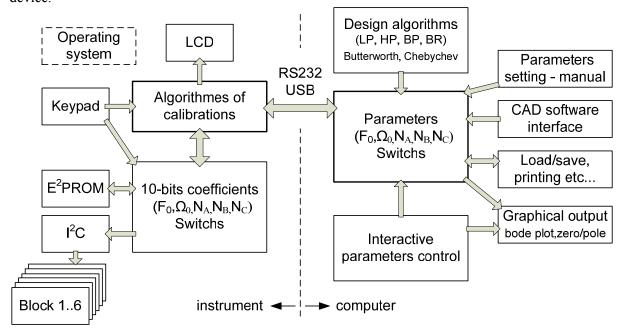

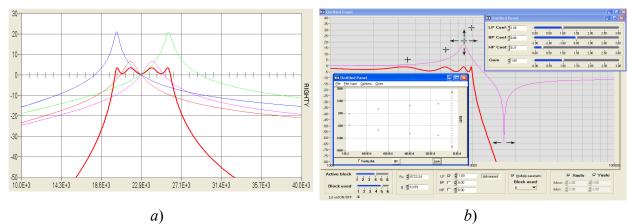

| 8.5.3 Control Software of Frequency Filter               |     |

| 8.5.4 Realisation of the Instrument and Conclusion       | 145 |

| Bigadratic Sections with Increased Attenuation.          |     |

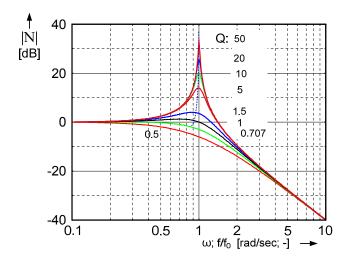

| 9.1 Biquadratic Sections for Cascade Filter Design       |     |

| 9.1.1 The Biquadratic Transfer Function                  |     |

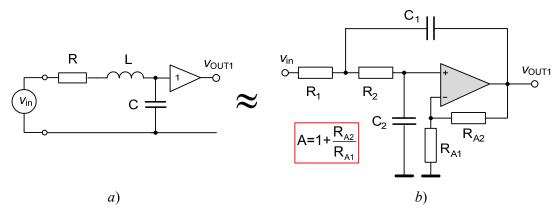

| 9.2 Active Biquadratic Sections                          |     |

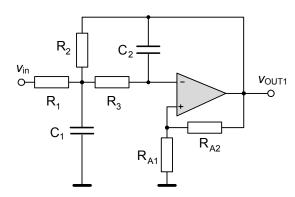

| 9.2.1 Single Amplifier Biquads (SAB)                     |     |

| 9.2.2 Multiple Active Element Biquad: Antonius GIC       |     |

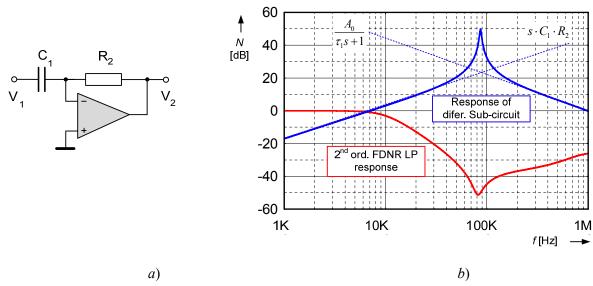

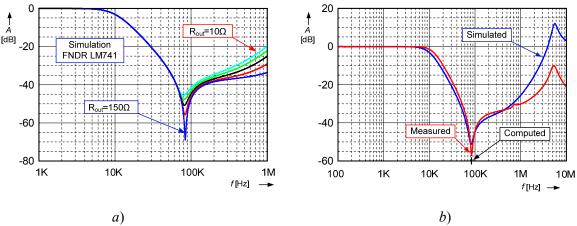

| 9.3 Degradation in the Stopband of LP Filters            |     |

| 9.3.1 Causes of the Parasitic Effect                     |     |

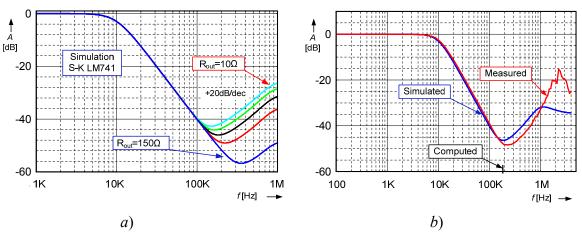

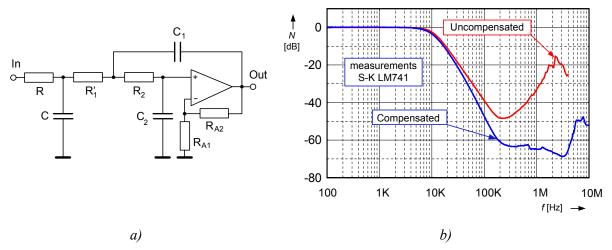

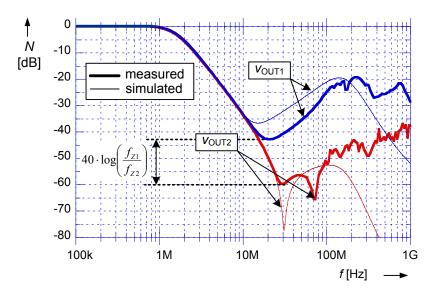

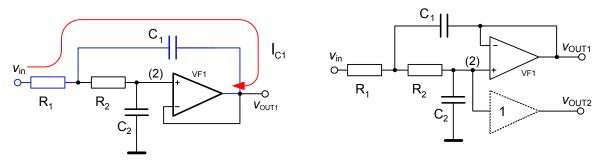

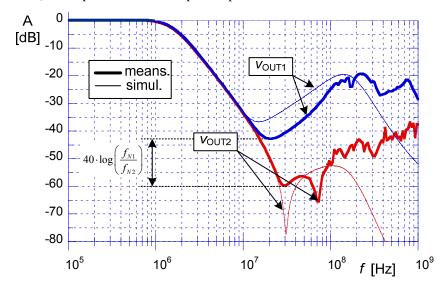

| 9.3.2 attenuation of the Sallen-Key LP Section           |     |

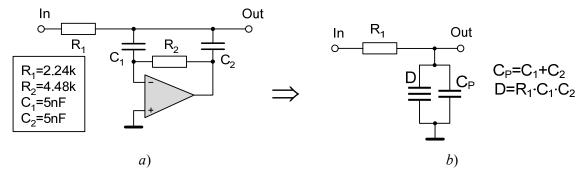

| 9.3.3 The lossy RCD 2 <sup>nd</sup> Order Section        |     |

| 9.3.4 Causes of LP Stopband Degradation                  |     |

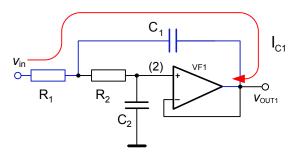

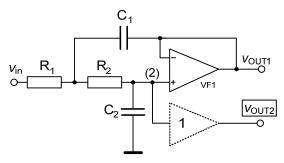

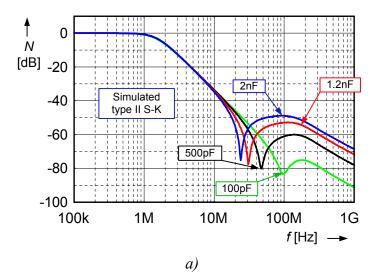

| 9.4 Type II Sallen-Key filter                            |     |

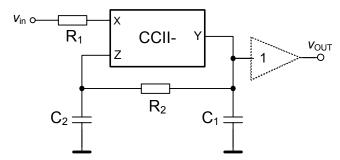

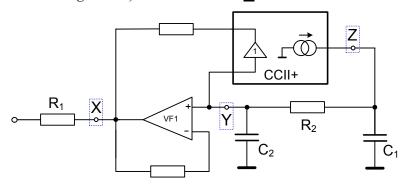

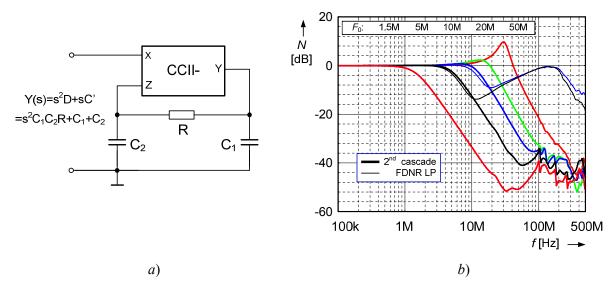

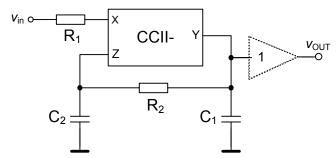

| 9.5 Current Mode CCII cascade Section                    | 162 |

| Design of CMOSSecond Generation Current Conveyor CCII.   |     |

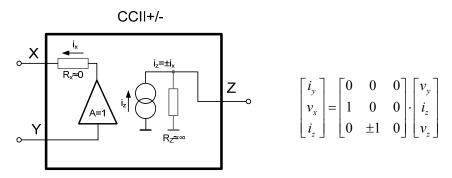

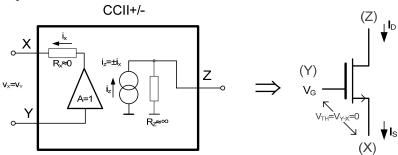

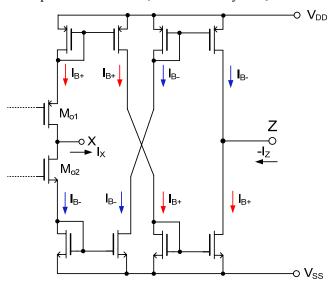

| 10.1 Current Conveyor                                    |     |

| 10.1.1 Second Generation Current Conveyor                |     |

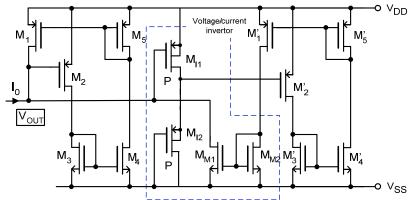

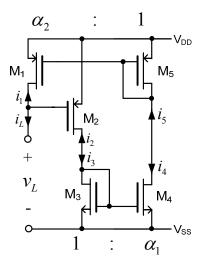

| 10.1.2 Basic Structure of the Current Conveyor           |     |

| 10.1.3 Real Properties of CCII                           | 169 |

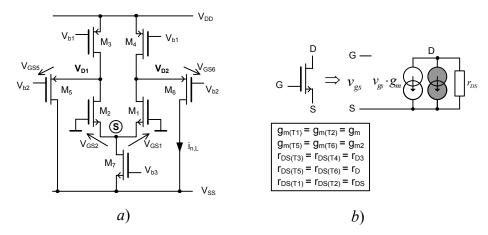

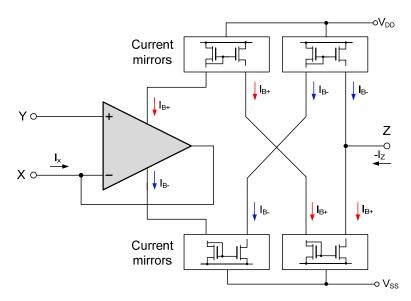

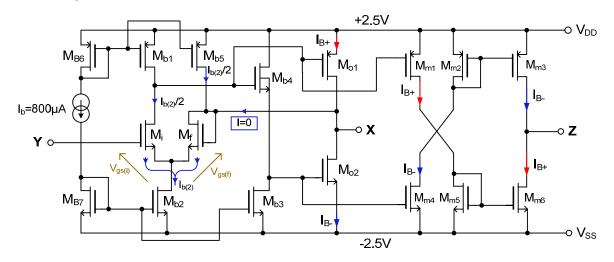

| 10.2 CMOS Realisation of the CCII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 169        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

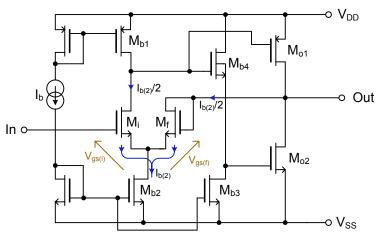

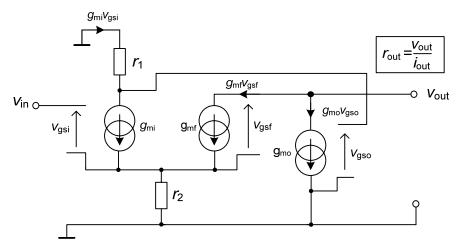

| 10.2.1 Low Impedance Voltage Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 170        |

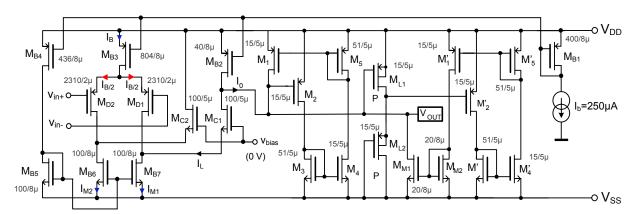

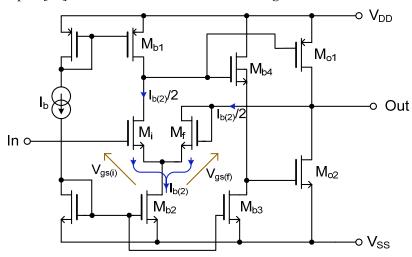

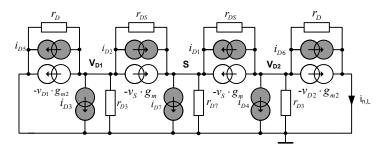

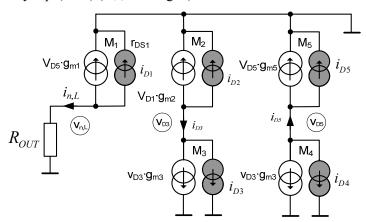

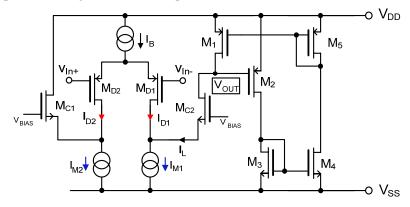

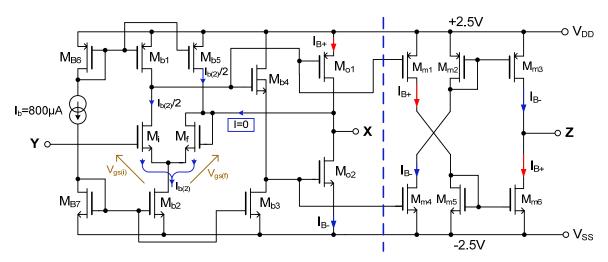

| 10.2.2 CCII- CMOS Current Conveyor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

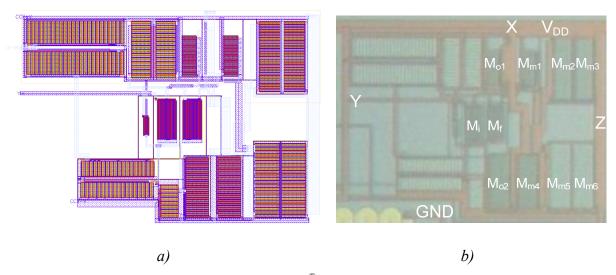

| 10.3 CMOS Integration of CCII-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

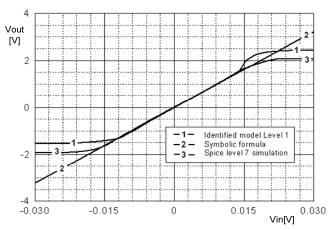

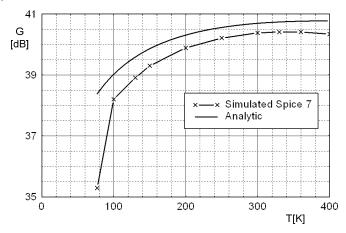

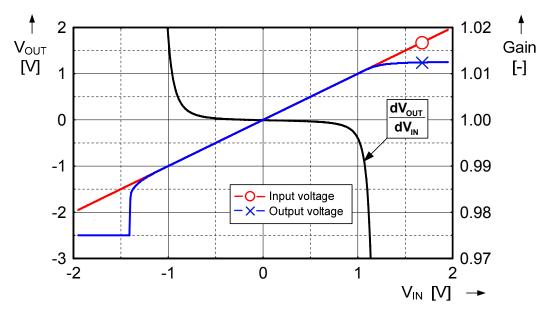

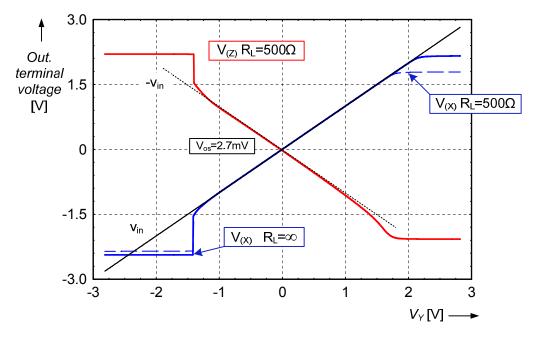

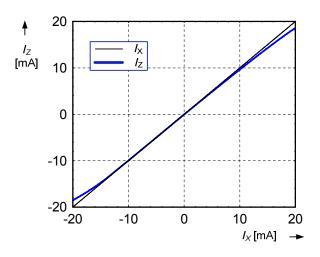

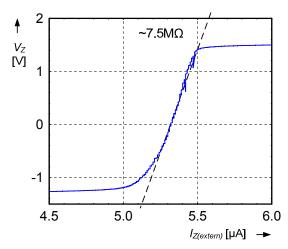

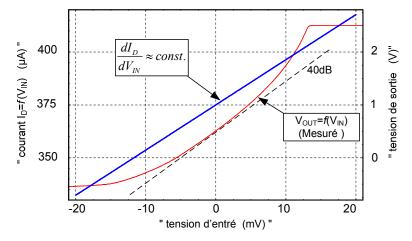

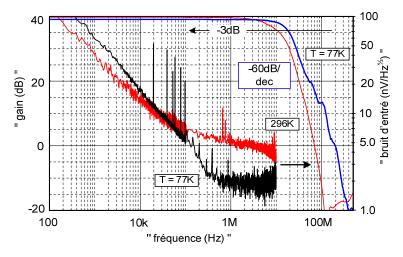

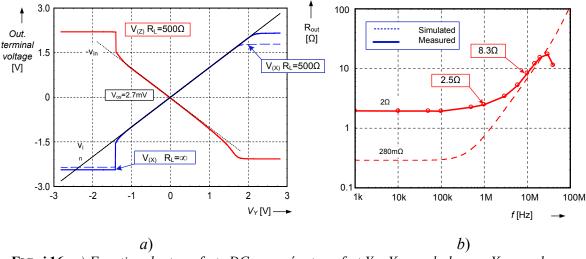

| 10.3.1 AC & DC Characteristic of integrated Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

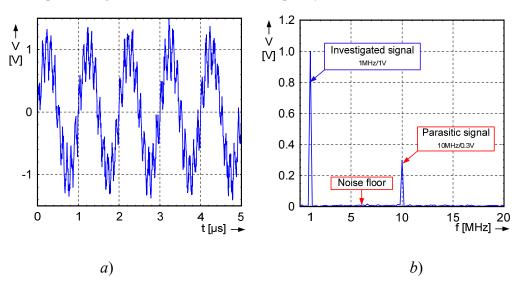

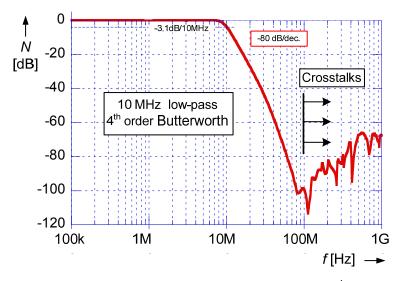

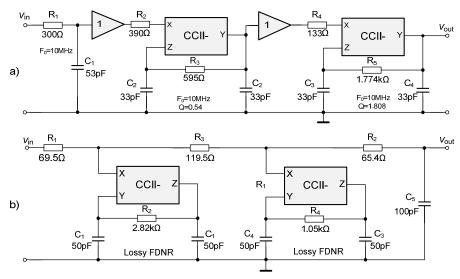

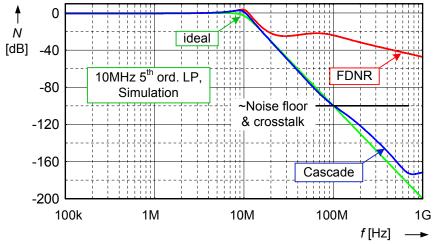

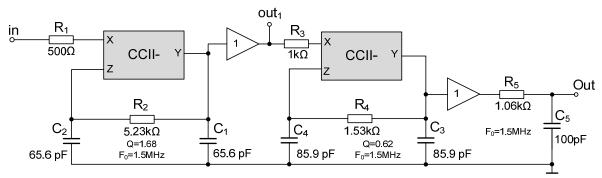

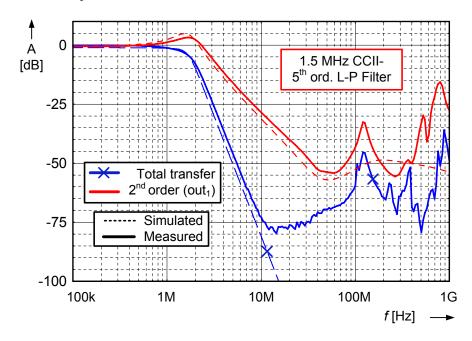

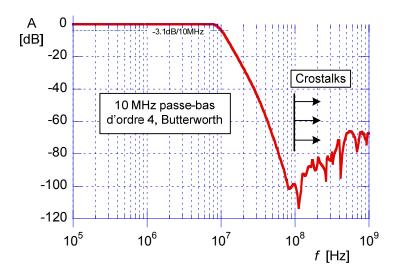

| 10.3.2 1.5MHz 5 <sup>th</sup> order LP filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 177        |

| 10.4 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| 10.7 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 170        |

| Conclusion of Part III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 179        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| Appendix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

| Summary in French                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 180        |

| Présentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 180        |

| I Electronique de lecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 181        |

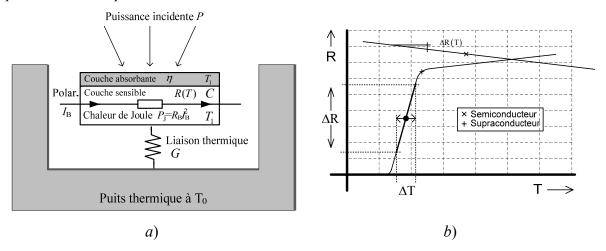

| I.1 Capteur bolométrique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

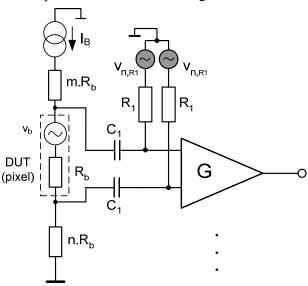

| I.2 Configuration de l'électronique de lecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

| I.3 « Architecture sans contre-réaction »                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 182        |

| II Conception des amplificateurs CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 183        |

| II.1 Comportement thermique d'un transistor MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 183        |

| II.2 Méthode de Conception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 184        |

| II.3 Amplificateur de Type I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 185        |

| II.3 Amplificateur de type II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 186        |

| L'analyse thermique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 188        |

| II.4 Conclusion A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 189        |

| III Filtres de fréquences actifs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 190        |

| III.1 L'atténuation des filtres passe-bas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 190        |