# Conception de systemes robustes de faible puissance pour des applications smarts-cards

Julien Roche

#### ▶ To cite this version:

Julien Roche. Conception de systemes robustes de faible puissance pour des applications smarts-cards. Micro et nanotechnologies/Microélectronique. Université de Provence - Aix-Marseille I, 2009. Français. NNT: . tel-00408730

# HAL Id: tel-00408730 https://theses.hal.science/tel-00408730

Submitted on 2 Aug 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre :XXXX

#### Université d'aix Marseille 1

### Thèse

pour obtenir le grade de :

# DOCTEUR DU L'UNIVERSITÉ D'AIX MARSEILLE 1 Mention PHYSIQUE ET MODÉLISATION DES SYSTÈMES COMPLEXES

présentée et soutenue publiquement par

## Julien ROCHE

Équipe d'accueil : IM2NP-Polytech Marseille

Ecole doctorale : Physique, Modélisation et Sciences pour l'Ingénieur

Titre de la thèse :

# Conception de systèmes robustes de faible puissance pour des applications smarts-cards

Soutenue le XXXX devant la commission d'examen :

# Table des matières

| 1 Introduction |     |                                                                             |       |         |  |  |

|----------------|-----|-----------------------------------------------------------------------------|-------|---------|--|--|

|                | 1.1 | Contexte et motivations                                                     |       | 1       |  |  |

|                | 1.2 | Environnement des cartes à puce sécurisées                                  |       | 6       |  |  |

|                | 1.3 | Historique du choix de la norme USB                                         |       | 8       |  |  |

|                | 1.4 |                                                                             |       |         |  |  |

|                | 1.5 | Réflexions sur la notion de Phase et de Fréquence                           |       | 12      |  |  |

|                |     | 1.5.1 Phase et fréquence dans le cas de signaux périodiques                 |       | 13      |  |  |

|                |     | 1.5.2 Phase et fréquence dans le cas de signaux non périodiques             |       | 14      |  |  |

|                |     | 1.5.3 Définition de la fréquence instantanée par approximation locale du s  | ignal | 14      |  |  |

|                |     | 1.5.4 Application : observation de la phase d'un oscillateur à relaxation . |       | 16      |  |  |

|                |     | 1.5.5 Modélisation du signal carré et définition de sa fréquence instantané | e .   | 18      |  |  |

| 2              |     | at de l'art sur la génération de fréquence<br>écification USB               | e     | t<br>21 |  |  |

|                | 2.1 | Les boucles à verrouillage de phase, BVP                                    |       | 21      |  |  |

|                | 2.2 | Classification des Boucles à verrouillage de Phase                          |       | 23      |  |  |

|                | 2.3 | Boucle à Ligne de Délai, BLD                                                |       | 26      |  |  |

|                | 2.4 | Spécification USB                                                           |       | 29      |  |  |

|                |     | 2.4.1 Généralités sur la transmission USB                                   |       | 30      |  |  |

|                |     | 2.4.2 Protocole USB                                                         |       | 34      |  |  |

|                |     | 2.4.3 Connexion d'un système à un serveur USB                               |       | 42      |  |  |

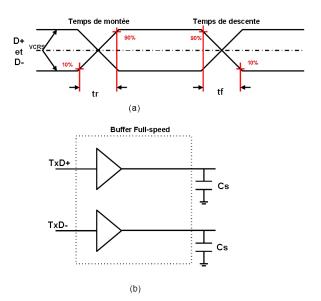

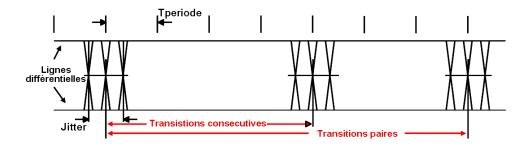

|                |     | 2.4.4 Caractéristiques électriques du signal USB                            |       | 48      |  |  |

|                |     |                                                                             |       |         |  |  |

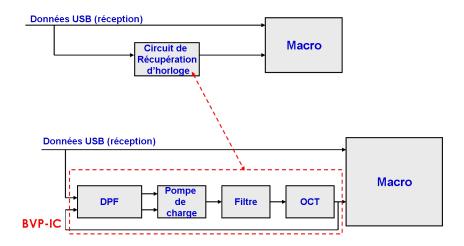

| 3 |                                                                                              | alyse et modelisation du systeme de recuperation<br>orloge               | 55  |  |  |  |

|---|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|--|--|--|

|   |                                                                                              | 3.0.5 Description des blocs                                              | 57  |  |  |  |

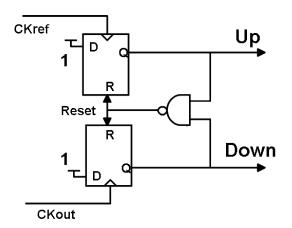

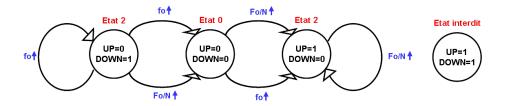

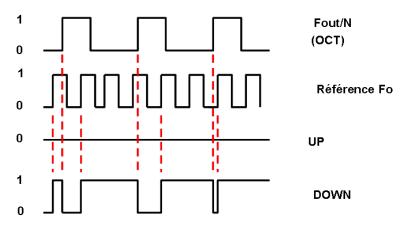

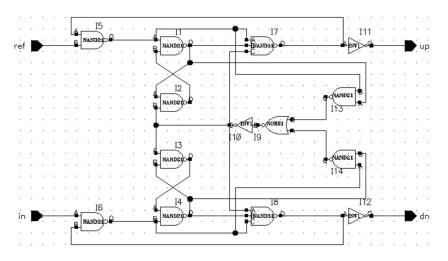

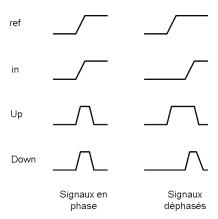

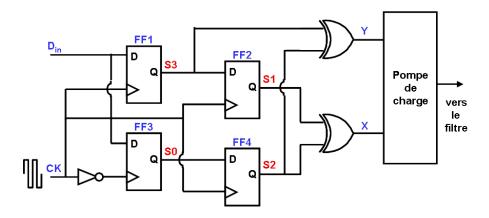

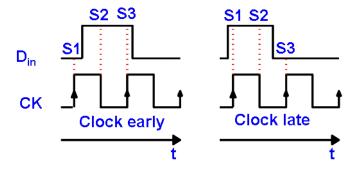

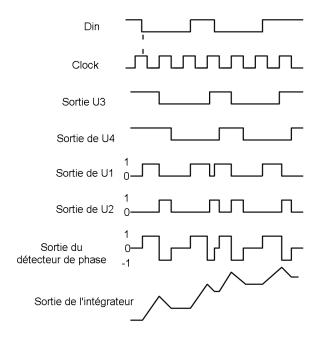

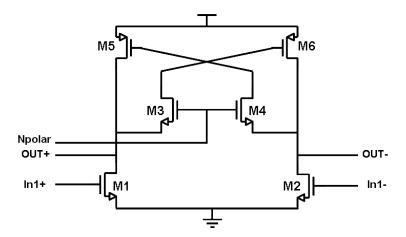

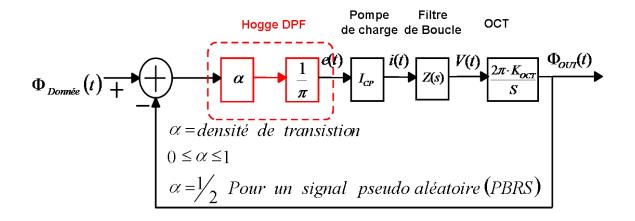

|   |                                                                                              | Détecteur de phase/fréquence                                             | 58  |  |  |  |

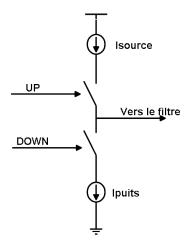

|   |                                                                                              | Pompe de charge                                                          | 69  |  |  |  |

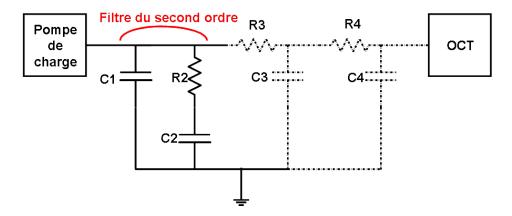

|   |                                                                                              | Le filtre de boucle                                                      | 70  |  |  |  |

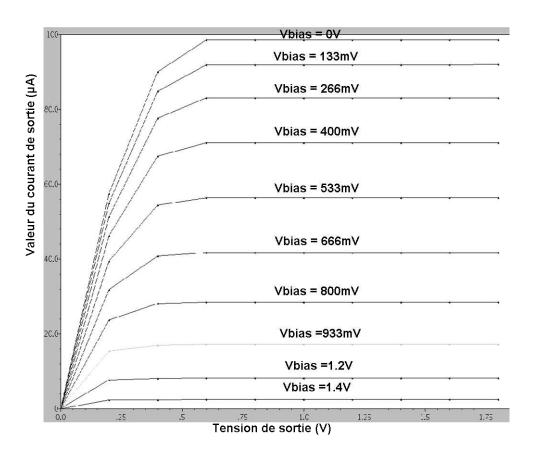

|   |                                                                                              | Oscillateur Contrôlé en Tension                                          | 72  |  |  |  |

|   |                                                                                              | 3.0.6 Spécification de la BVP                                            | 76  |  |  |  |

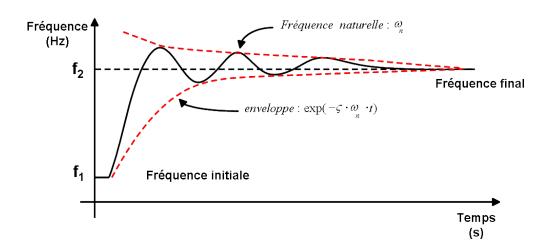

|   |                                                                                              | Temps d'établissement                                                    | 76  |  |  |  |

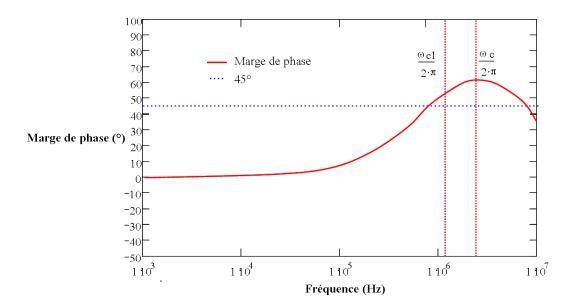

|   |                                                                                              | Stabilité                                                                | 76  |  |  |  |

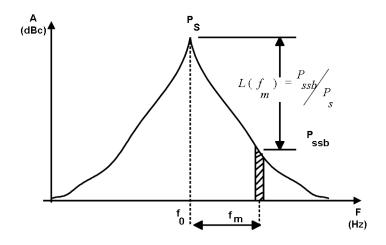

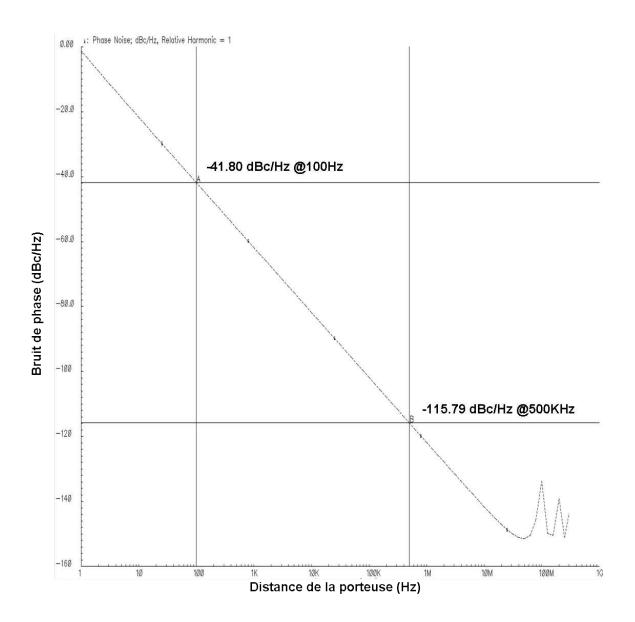

|   |                                                                                              | Bruit de phase                                                           | 76  |  |  |  |

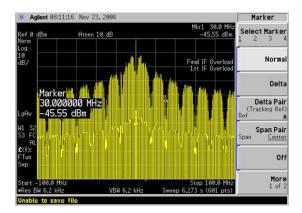

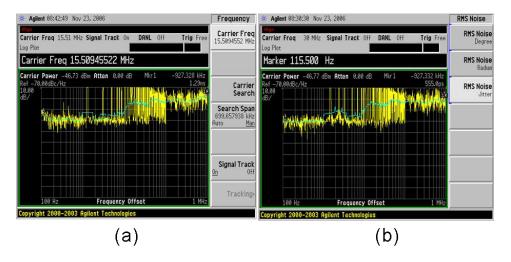

|   |                                                                                              | Pics parasites                                                           | 80  |  |  |  |

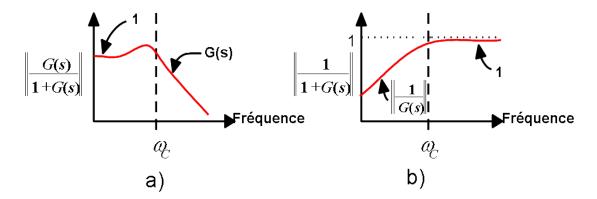

|   |                                                                                              | 3.0.7 Linéarisation et modélisation de la BVP                            | 81  |  |  |  |

|   |                                                                                              | Modélisation du comportement de la boucle                                | 81  |  |  |  |

|   |                                                                                              | Modélisation des différentes sources de bruit                            | 85  |  |  |  |

| 4 | Coi                                                                                          | nception du système                                                      | 89  |  |  |  |

|   | 4.1                                                                                          | Calcul des paramètres de la boucle                                       | 89  |  |  |  |

|   |                                                                                              | 4.1.1 Etude Mathcad du système                                           | 90  |  |  |  |

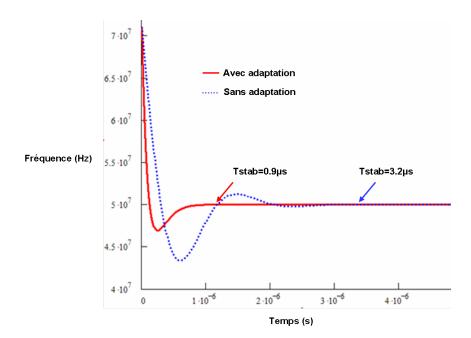

|   | 4.2                                                                                          | Solution d'adaptation de bande passante                                  | 94  |  |  |  |

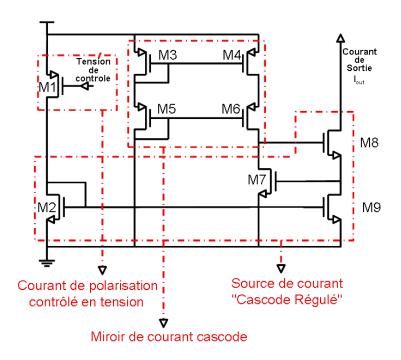

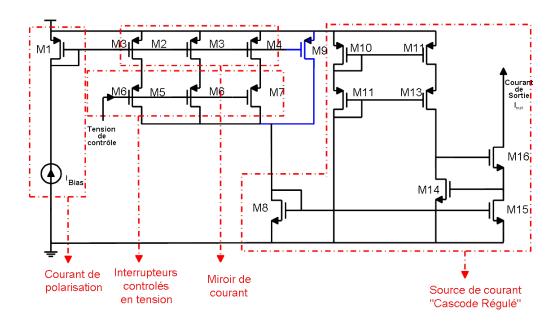

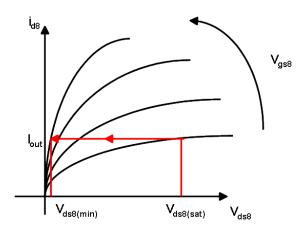

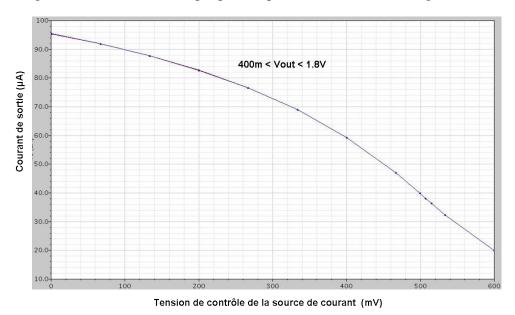

|   |                                                                                              | 4.2.1 Conception de la source de courant contrôlé                        | 94  |  |  |  |

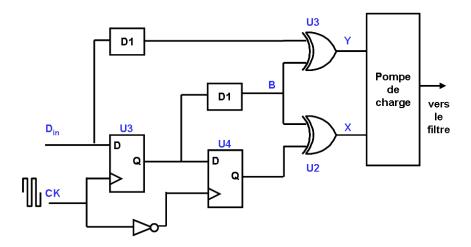

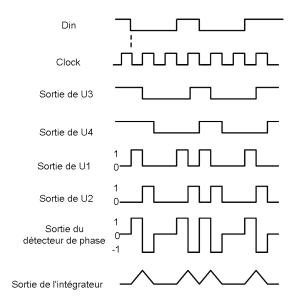

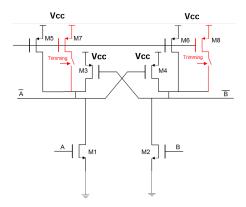

|   | 4.3                                                                                          | Evolution de l'architecture du détecteur de phase                        | 101 |  |  |  |

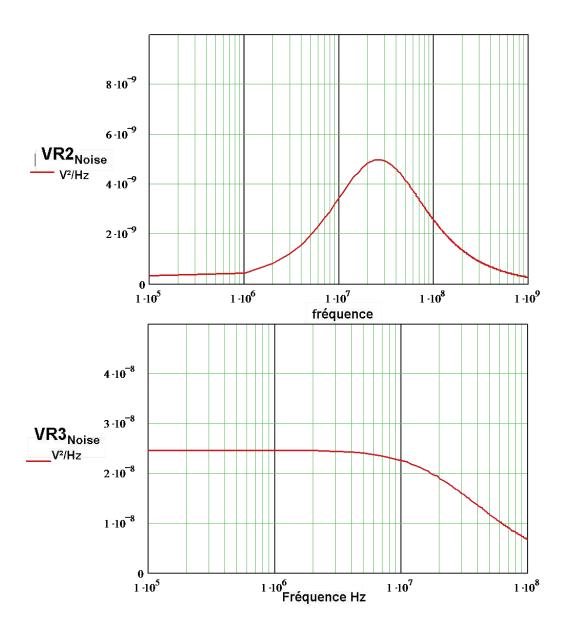

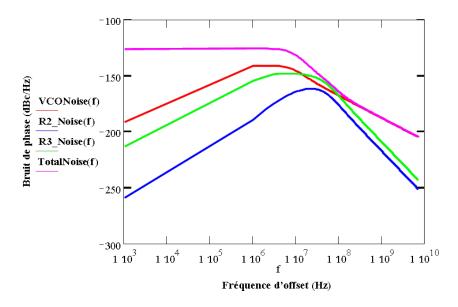

|   | 4.4 Modélisation des différentes sources de bruit et calculs du bruit total dans la boucle 1 |                                                                          |     |  |  |  |

|   |                                                                                              | 4.4.1 Bruit dans les résistances                                         | 105 |  |  |  |

|   |                                                                                              | 4.4.2 Bruit dans les capacitées                                          | 105 |  |  |  |

|   |                                                                                              | 4.4.3 Bruit dans les transistors MOS                                     | 107 |  |  |  |

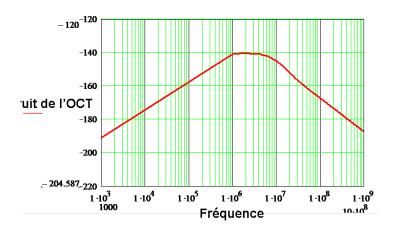

|   |                                                                                              | 4.4.4 Bruit dans l'OCT                                                   | 108 |  |  |  |

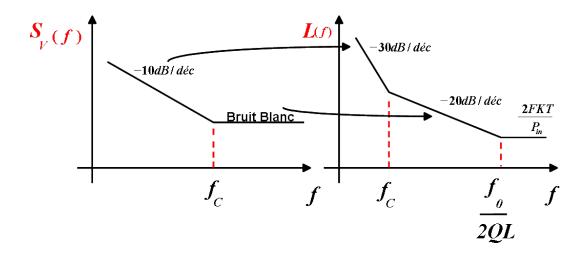

|   |                                                                                              | Le modèle de Leeson (Théorie Linéaire et Stationnaire, LTI : Linear Time |     |  |  |  |

|   |                                                                                              | Invariant)                                                               | 108 |  |  |  |

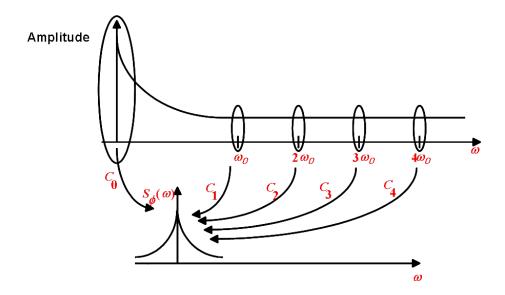

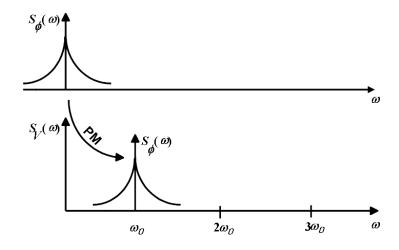

|   |                                                                                              | Le modèle d'Hajimiri (Théorie Linéaire et variant temporellement LTV :   |     |  |  |  |

|   |                                                                                              | Linear Time Variant)                                                     | 110 |  |  |  |

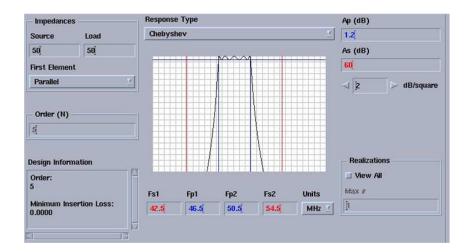

|   |                                                                                              | 4.4.5 Pics parasites et choix du filtre de boucle                        | 113 |  |  |  |

|   |                                                                                              | Gain des pics parasites                                                  | 113 |  |  |  |

|   |                                                                                              | Pics dûs aux fuites de courant                                           | 113 |  |  |  |

|   |                                                                                              | Pics dûs aux différences physiques de la pompe de charge                 | 114 |  |  |  |

|   |                                                                                              | Modélisation de l'influence du filtre sur les pics parasites             | 115 |  |  |  |

|   |                                                                                              | Conception du Filtre de boucle                                           | 116 |  |  |  |

|   |                                                                                              | 4.4.6 Estimation du Bruit dans la PLL                                    | 116 |  |  |  |

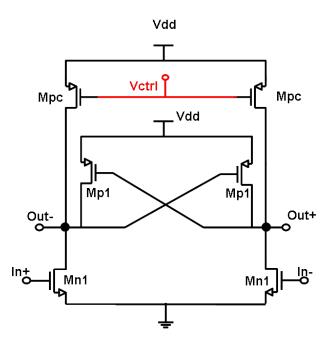

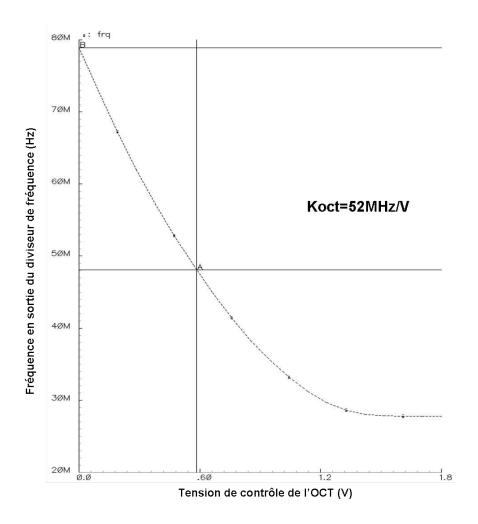

| 4.5                      | Conception de l'OCT                                                            | 119        |

|--------------------------|--------------------------------------------------------------------------------|------------|

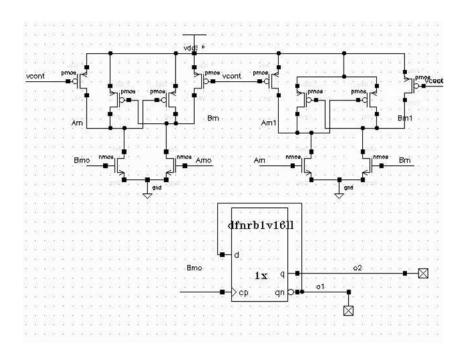

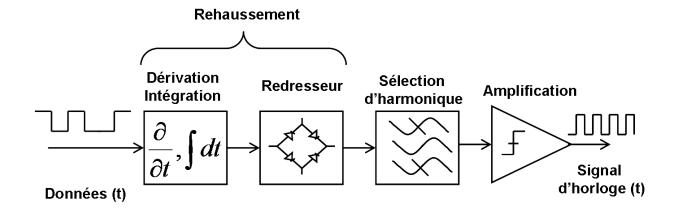

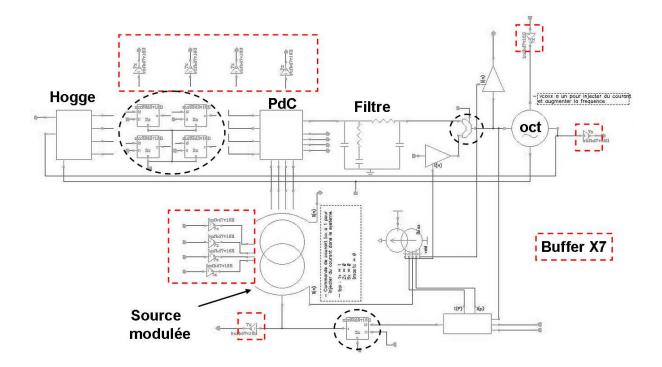

| 4.6                      | Conception du multiplicateur de fréquence faible bruit                         | 125        |

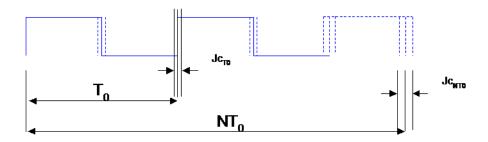

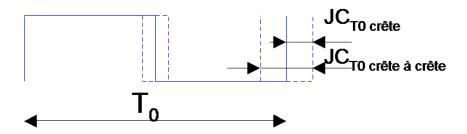

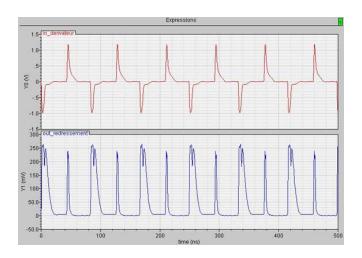

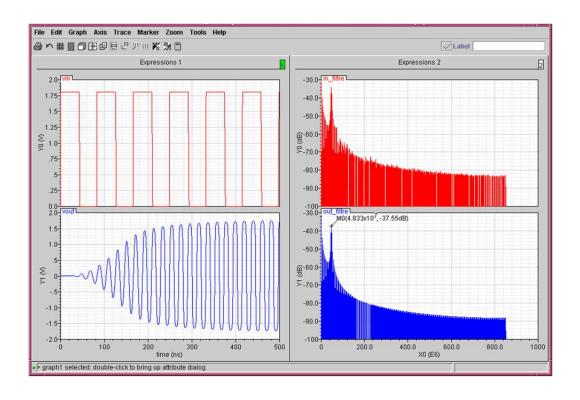

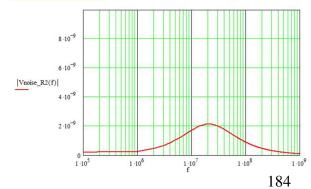

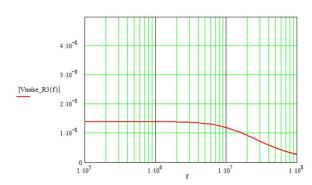

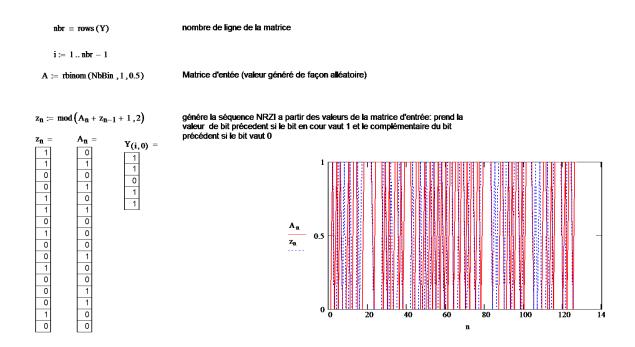

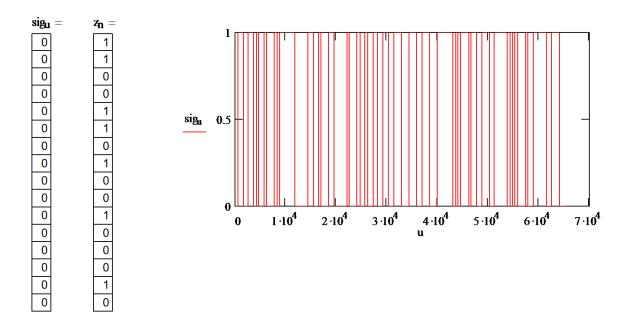

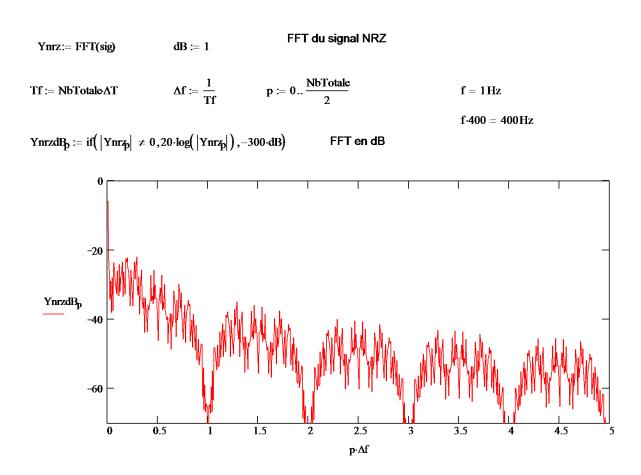

|                          | 4.6.1 Caractéristique d'un signal de type NRZI                                 | 128        |

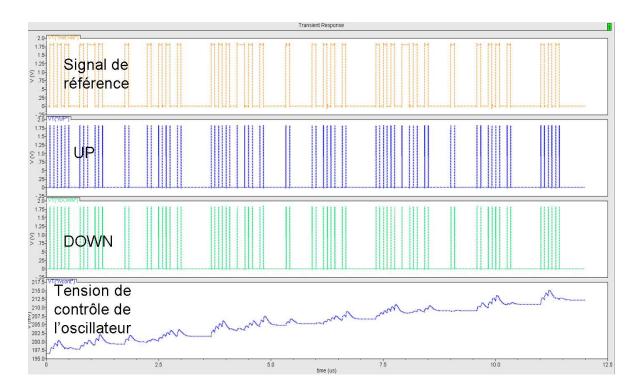

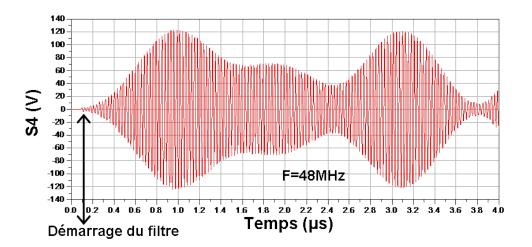

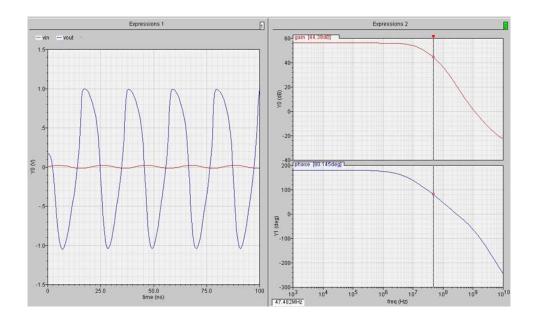

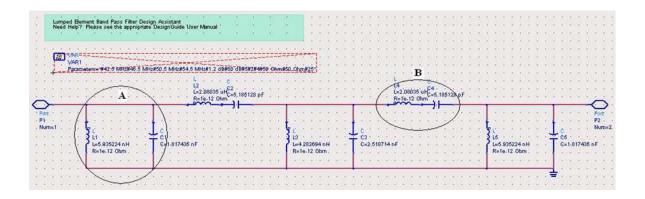

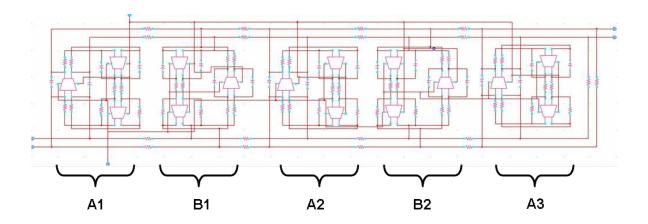

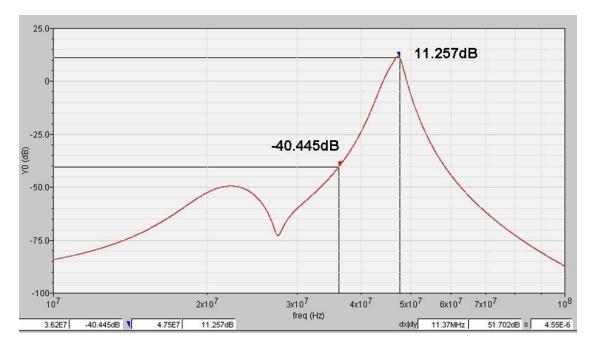

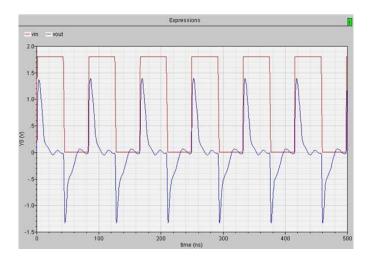

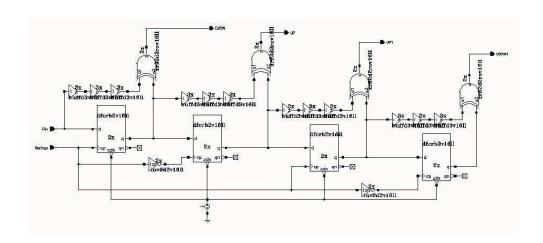

|                          | 4.6.2 Etude et validation du système de multiplication de fréquence sous ADS 1 | 133        |

|                          | 4.6.3 Impact de la multiplication sur le bruit de phase                        | 138        |

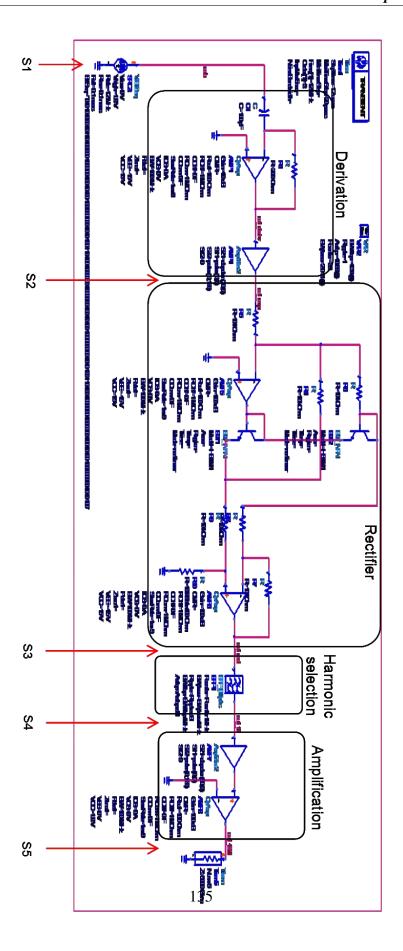

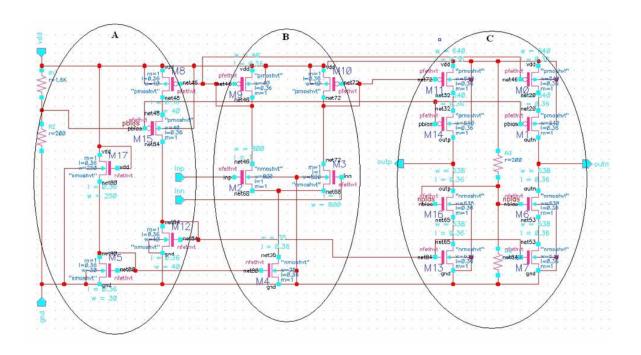

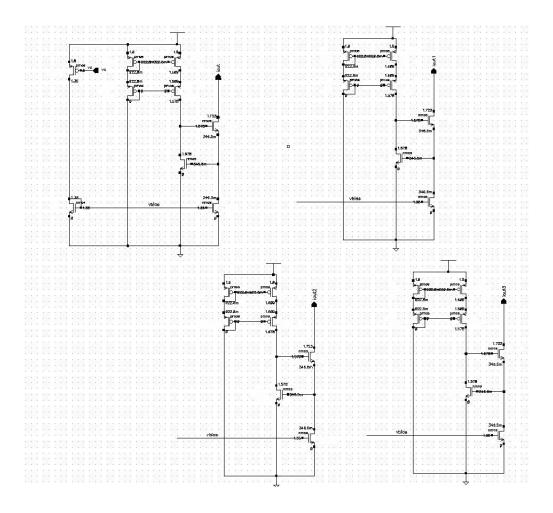

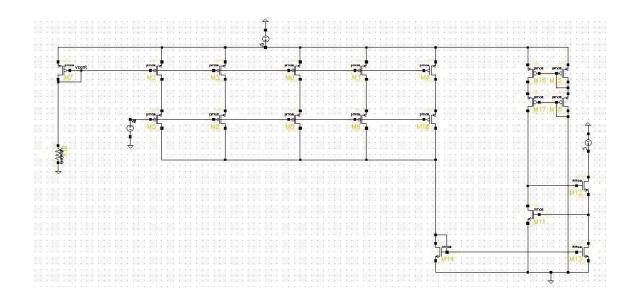

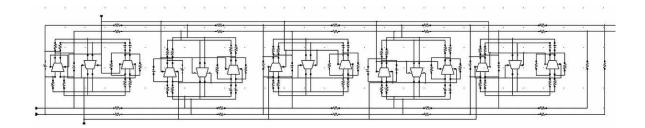

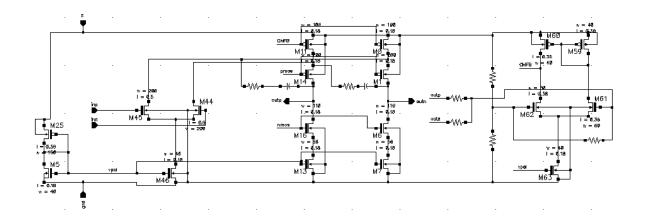

|                          | 4.6.4 conception des blocs du multiplicateur sous cadence                      | 139        |

| 5 Validations du système |                                                                                | 49         |

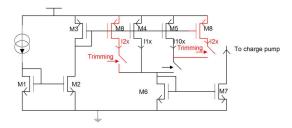

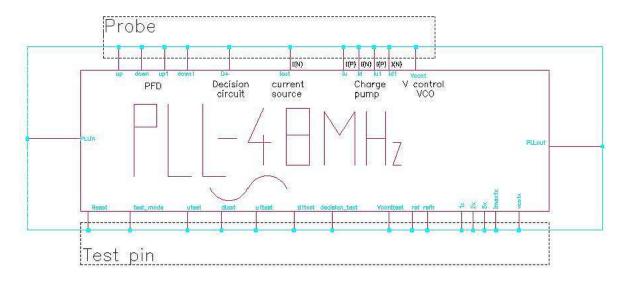

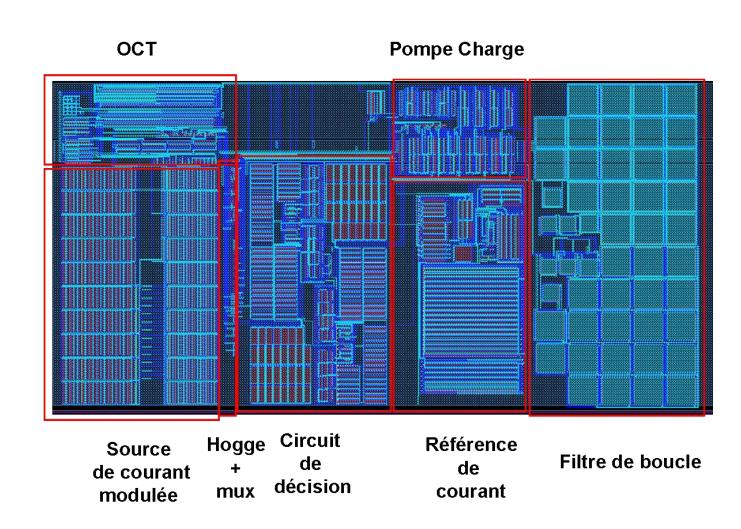

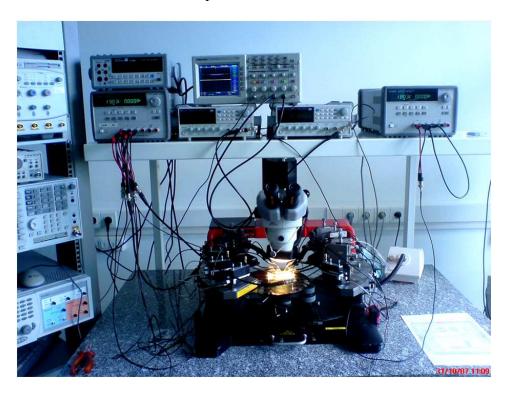

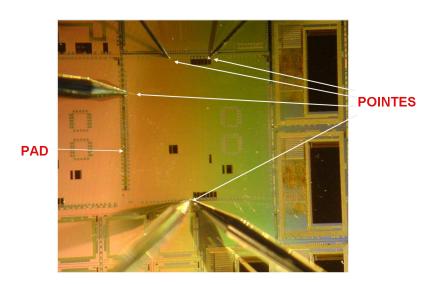

| 5.1                      | Conception de la structure de test                                             | 150        |

|                          | 5.1.1 module de 'trimming'                                                     | 150        |

|                          | 5.1.2 Mise en place du mode de test                                            | 151        |

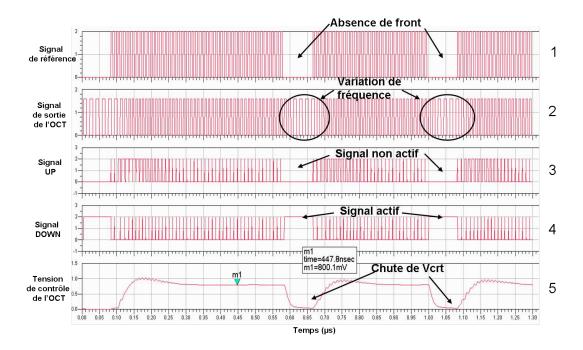

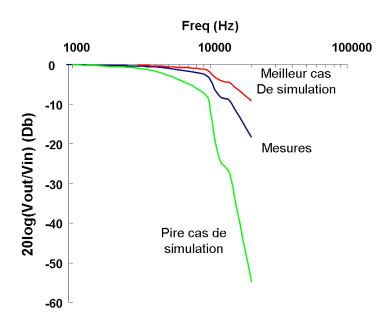

| 5.2                      | Simulation                                                                     | 154        |

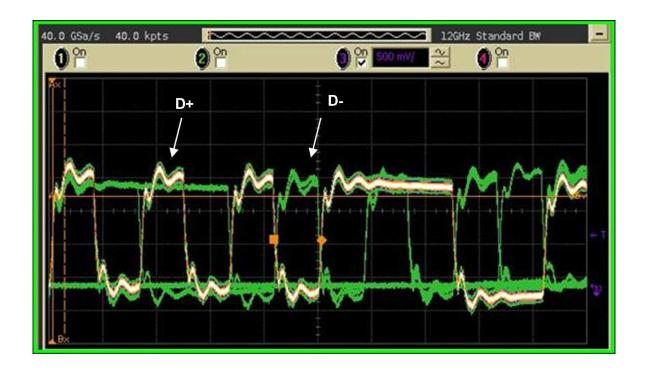

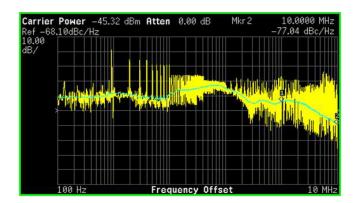

| 5.3                      | Mesures                                                                        | 161        |

| 6 Co                     | 6 Conclusions                                                                  |            |

| A AN                     | NNEXE 17                                                                       | 73         |

|                          |                                                                                |            |

| A.1                      | Liste des Acronymes                                                            | 173        |

|                          | •                                                                              | 173<br>175 |

| A.1                      | Spécification USB                                                              |            |

| A.1<br>A.2               | Spécification USB                                                              | 175        |

| A.1<br>A.2<br>A.3        | Spécification USB                                                              | 175<br>180 |

#### **REMERCIMENTS**

Je tiens à remercier tout particulièrement mes tuteurs de thèse Annie Perez, Gaëtan Bracmard, Wenceslas Rahajandraibe et Lakhdar Zaïd pour leurs conseils et surtout leur soutien pendant ces 4 ans

Ces travaux n'auraient pu aboutir sans le soutien d'*Atmel* à Rousset, et du IM2NP à Marseille, qui m'ont mis dans les meilleures conditions pour l'étude, la conception et les tests des circuits présentés dans ce mémoire.

Je remercie par ailleurs tous les membres du groupe *Design analogique SMS* (Secure Microcontroleur Solution) que je n'ai pas encore cités et qui ont tous contribué à ce que les travaux se passent dans de bonnes conditions.

Je remercie aussi l'ensemble du personnel d'*Atmel* pour leur accueil, (Daniele Fronte, Samuel Charbouillot, Jean-Pascal Maraninchi . . .)

Ces trois années n'auraient pas été particulièrement réussies sans les thésards et stagiaires qui ont contribué à créer une ambiance de travail plus que sympathique : Vincent Cheynet de Beaupré, Emmanuel bergeret, Amir Fanaei, Arnaud regnier, Bertrand Saillet, Jérémy Postel-Pellerin, Julien Mercier, Marc Battista, Matthieu Fillaud, Olivier Mercier, Valéry Bouquet, Yannick Bachelet.

Je retiendrai particulièrement les fous rires et les moments de soutien que nous avons partagés.

Je remercie aussi mes amis : Vinz, Polo, Etienne, Martin, Tank, Axel, Kaesar, Toto pour m'être resté fidèles malgré mes longues absences.

Je voudrais aussi remercier mes parents, mon frère et ma famille en France, aux États-Unis, à Tahiti, parce qu'ils me sont particulièrement chers.

Enfin, je finirai par remercier ma femme qui a dû supporter mes sautes d'humeur et que j'aime plus que tout.

#### Résumé

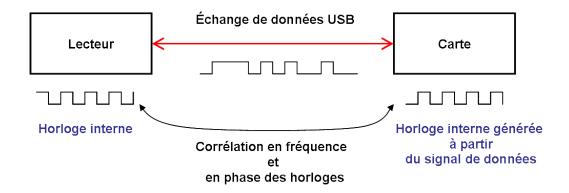

Le besoin sécuritaire lié au développement des cartes à puce intelligentes impose de fortes contraintes quant à la robustesse de fonctionnement de ces dispositifs afin de garantir des performances optimales dans un environnement sans cesse perturbé. Depuis Trois ans, des effets d'annonces, suivies de prudentes introductions commerciales, se sont multipliés pour promouvoir auprès des opérateurs télécoms un nouveau concept de carte SIM : une carte, Mega, Very Large ou SuperSIM, offrant des capacités mémoires étendues aptes à supporter de nouveaux services de gestion de contenus et, surtout, disposant d'un protocole de communication bien plus rapide que celui spécifié par l'ISO7816-3 (9, 6kbits/s en standard). L'augmentation de ce taux de transfert est donc un enjeu important pour ce marché. Une des solutions envisagées serait d'utiliser la performance de la norme USB (Universal Serial Bus) qui est une interface rapide, bidirectionnelle, isochrone et de faible coût, dont les connections sont gérées dynamiquement. En dépit de sa simplicité, cette solution a un coût. En effet, l'isochronisme n'est pas assuré par le transfert d'une base de temps au travers de la connexion. Ainsi le lecteur et l'élément connecté (host et device) doivent générer leurs propre référence. Cependant, celles-ci doivent avoir une précision compatible, aussi bien au niveau des taux de transfert que du nombre d'éléments faisant partie de la chaine de communication. L'objectif de cette thèse est d'une part, la recherche de solutions innovantes et de faible coût permettant la récupération d'horloge lors de la transmition de données entre la carte à puce et son lecteur en se servant du protocole USB, et d'autre part, de démontrer la faisabilité de la solution par l'implémentation d'une structure robuste, à faible puissance, pour les applications Smart-Card.

1

# Introduction

#### 1.1 Contexte et motivations

La production de cartes à puce en 2007 (avec 4,175 milliards) est en progrès de 17% par rapport à 2006. Dans cette production, on distingue les cartes à mémoire (24%) et les cartes à microprocesseurs (76%). Les cartes sont utilisées principalement pour les usages téléphoniques (la carte SIM représente 2,14 milliards d'unités, soit près de la moitié du marché global), les services bancaires (0,5 milliard de cartes à microprocesseur, dont 40 millions pour les paiements sans contact) et les cartes d'identité pour les services de santé et de transport. Selon Frost and Sullivan, les principaux fournisseurs sont cette année l'Allemand Infinéon (29% de parts de marché en valeur), Samsumg (15,5%), NXP (14,3%), Atmel (13%), Renesas (12,5%), etc.

Cependant, le lancement de la carte à puce fût difficile, personne n'y croyait. La première puce SPOM fabriquée en 1980 par Bull et Motorola resta en effet assez ignorée. Ce climat de méfiance explique qu'en 1983, France Télécom eut beaucoup de mal à trouver un industriel qui accepte de produire ses puces. Après avoir prospecté sans succès les Etats-Unis et le Japon, France Télécom trouve enfin une entreprise pour fabriquer ses premières télécartes.

Ce sera Eurotechnique, qui fut ensuite absorbée par STMicroelectronics. L'accélération eut lieu en 1987, lorsque les quantités produites pour France Télécom et Deutsch Telekom commencèrent à être importantes, d'autres acteurs entraient aussi en jeu, comme Siemens avec Infinéon, ou encore au Japon OKI, Hitachi et NEC. Mais, après le pic de consommation annuelle mondiale, atteint en 2002 avec 1,3 milliards de cartes, la concurrence des téléphones portables affecte fortement l'utilisation des cabines téléphoniques. C'est ainsi que la consommation de télécartes est passée au-dessous du milliard en 2004.

Cependant, l'explosion du marché du GSM entre 1995 et 2000 a été une véritable aubaine pour les fabricants de cartes. Le développement continu de la capacité des composants a permi de multiplier les fonctions de la carte SIM (SIM = Subscriber Identity Module) : téléchargement par l'opérateur, dialogue avec le réseau, nouvelles applications. Aujourd'hui une carte SIM haut de gamme dispose de 128 ko de mémoire EEPROM et 4 ko de mémoire vive pour moins de 3 dollars.

Après avoir fait ses preuves dans le secteur bancaire puis dans la téléphonie mobile, la carte à puce s'impose progressivement comme le support universel de l'identité. Une fois personnalisé, ce système sur puce portable et sécurisé permet, entre autres, d'identifier et d'authentifier son porteur légitime, de stocker ses données confidentielles et de signer électroniquement des documents officiels. Ainsi, la carte à puce s'impose dans un nombre grandissant de domaines d'application :

- cartes de santé,

- cartes d'abonnement,

- sécurité sociale

- réseaux de télévision payants (Canal+, BSkyB vecBskyB, SkyTV),

- cartes de sécurité sur Internet,

- transports,

- cartes d'accès (physique ou logique),

#### - cartes d'identité électroniques et passeports biométriques

Ce sont les nouveaux vecteurs de 'l'intelligence ambiante'. Pourtant, la carte à puce est un support contraignant. En particulier, les contraintes mécaniques fixées par les normes limitent la surface silicium à seulement 30 mm2. De fait, les premières cartes commercialisées comportaient uniquement une mémoire pilotée par un circuit logique simple. Par la suite, l'évolution des technologies MOS a permis de décupler les ressources matérielles embarquées; les plus sophistiqués des microcontrôleurs actuels renferment un microprocesseur RISC 32 bits, plusieurs centaines de kilo de mémoire et une multitude de périphériques sécuritaires et de communication (avec ou sans contacts). L'exploitation de cette puissance via des plates-formes de développement ouvertes (Java, .Net, etc.) autorise la mise en oeuvre d'applications de haut niveau alliant performance et interoperabilité.

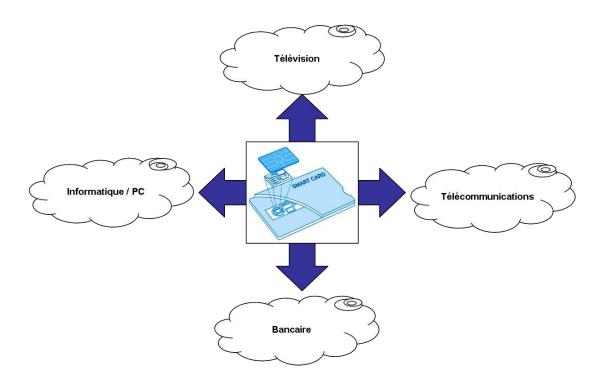

Le besoin sécuritaire lié au développement des cartes à puce intelligentes impose de fortes contraintes quant à la robustesse de fonctionnement de ces dispositifs afin de garantir des performances optimales dans un environnement sans cesse perturbé. Cela impose des spécifications contraignantes pour les circuits dédiés à ces applications afin d'avoir une marge de sécurité de fonctionnement suffisante de ces cartes à puce vis à vis des dispositifs auxquels elles sont connectées. Leur développement demande de plus en plus de ressources tant au niveau de la puissance de calcul que du taux de transfert avec le monde extérieur. Par ailleurs, la tendance se porte vers des cartes à puce multiplateformes, Fig. 1.1, de sorte qu'elles soient reconnues par des mondes totalement différents à l'instar des dernières générations des téléphones portables qui peuvent être connectés à un ordinateur. Depuis Trois ans, des effets d'annonces, suivies de prudentes introductions commerciales, se sont multipliés pour promouvoir auprès des opérateurs télécoms un nouveau concept de carte SIM : une carte, Mega, Very Large ou SuperSIM, offrant des capacités mémoires étendues aptes à supporter de nouveaux services de gestion de contenus et, surtout, disposant d'un protocole de communication bien plus rapide que celui spécifié par l'ISO7816-3 (9,6kbits/s en standard).

FIG. 1.1 – Carte à puce Multiplateformes.

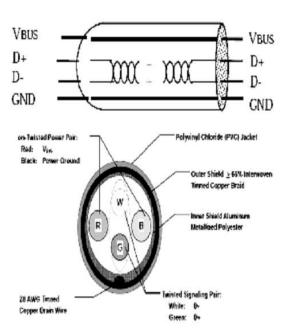

L'augmentation de ce taux de transfert est donc un enjeu important pour ce marché. Une des solutions envisagées serait d'utiliser la performance de la norme USB (Universal Serial Bus) qui est une interface rapide, bidirectionnelle, isochrone et de faible coût, dont les connections sont gérées dynamiquement. Cette norme est bien sûr intéressante pour ces performances en termes de vitesse, mais a aussi un attrait indéniable par le faible coût du lecteur associé. En effet, toutes les informations sont émises au travers d'un simple connecteur relié à quatre fils conducteurs dont l'alimentation positive (V+) et négative (V-), plus les données transmises en complémentaire (D+ et D-) A.1.

Axalto (devenu Gemalto) a été le premier à anticiper les évolutions que le mobile et la carte SIM allaient connaître en termes de capacités mémoires, mais aussi de fonction-nalités liées aux applications sans contact. La société a notamment travaillé très tôt sur le protocole USB, un standard du monde du PC, pour l'adapter au monde de la carte à puce

(avec une spécification baptisée USB Interchip), de façon à répondre en termes de débit, jusqu'à 480Mbits/s, à la montée en puissance en capacités mémoires de la future carte SIM. Mais pas seulement : l'USB - cela a été la vision constante d'Axalto - offre aussi des capacités multiservices intéressantes (communication TCP-IP, stockage, audio, vidéo, etc.) pour le développement de nouveaux services Web en particulier. Ces travaux se sont d'ailleurs inscrits dans le droit fil de ceux menés à l'ISO qui ont abouti fin 2005 à l'adoption de l'ISO7816-12 qui spécifie la façon dont les APDU (Application Protocol Data Units), un format d'échange de données spécifique au monde de la carte, pouvaient être transportées dans des trames USB.

En dépit de sa simplicité, cette solution a un coût. En effet, contrairement à ce que décrit la Fig. 1.2 l'isochronisme n'est pas assuré par le transfert d'une base de temps au travers de la connexion. Ainsi le lecteur et l'élément connecté (host et device) doivent générer leurs propres références. Cependant, celles-ci doivent avoir une précision compatible, aussi bien au niveau des taux de transfert que du nombre d'éléments faisant partie de la chaine de communication figure ,Fig.1.3.

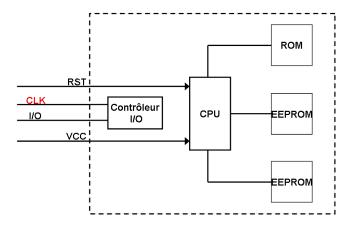

FIG. 1.2 – Structure et interface typique d'une carte à puce

Pour effectuer des opérations synchrones sur un flot de données aléatoires, le récepteur doit générer une horloge. Dans le cas de notre étude, l'environnement d'application des cartes à puces limite l'utilisation d'un Crystal de quartz comme base de temps. Les seuls

informations disponibles proviennent des signaux apériodiques envoyés par l'hôte à travers les signaux D+ et D-.

FIG. 1.3 – Principe de la communication USB entre un lecteur et une carte.

Les données échangées par ces dispositifs sont asynchrones et bruitées. Elle nécessitent donc, pour permettre une utilisation synchrone, l'extraction d'un signal d'horloge à partir du signal de données envoyé par le lecteur. Des blocs de récupération d'horloge se trouvent dans les 'émetteurs-récepteurs' qui servent dans de nombreuses applications comme, les communications optiques, les interconnexions entre puces, les communications radio et hyper fréquence...

# 1.2 Environnement des cartes à puce sécurisées

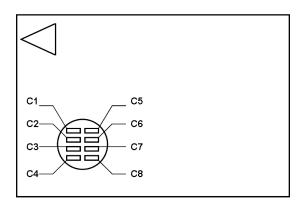

Le terme 'carte à puce' ('smart card' dans la littérature anglaise) désigne tout support fin de petite dimension embarquant un circuit intégré, [1]. Les caractéristiques des cartes à puce sont standardisées par des normes internationales. Les standards ISO/IEC7810 [2] et ISO/IEC7816-1 [3] définissent, entre autres, les caractéristiques physiques et mécaniques du support. Ce dernier se présente généralement sous la forme d'une petite carte en PVC de 0.76mm d'épaisseur. Les deux formats les plus répandus sont le ID-1 (carte bancaire) et le ID-000 (carte SIM). Ils sont tous deux représentés sur le schéma de la Fig. 1.4.

**FIG. 1.4** – Format ID - 1 et ID - 000 selon ISO/IEC7810

En terme d'interface de communication, les cartes à puce se divisent en deux catégories : les cartes à contact et les cartes sans contact. Dans le cas des cartes à contact, l'accès au composant électronique se fait par l'intermédiaire de plots métalliques. Sauf exception [4], une carte à puce n'embarque pas de batterie, elle est alimentée par le lecteur. L'alimentation asymétrique délivrée par ce dernier est appliquée à la puce par l'intermédiaire des contacts Vcc (potentiel électrique le plus élevé) et GND (potentiel électrique le plus faible). Le signal d'horloge est également fourni par le lecteur. Il est transmis à la puce via CLK. L'entrée numérique RST permet de réinitialiser le circuit. Le port de communication série I/O est de type bidirectionnel semi-duplex. Le protocole de communication associé est décrit par le standard ISO7816-3 [3]. La programmation des mémoires de type EEPROM nécessite des tensions généralement supérieures à celle supportée par le reste du circuit. Jusqu'à la fin des années 1990, le contact Vpp était utilisé à cet effet. Il ne l'est plus depuis l'intégration des pompes de charge, structures permettant de générer ces niveaux de tension en interne. Enfin, les contacts AUX1 et AUX2 n'ont pas de fonction attitrée. Leur présence, même physique, reste optionnelle. Les caractéristiques des paramètres électriques (fréquence du signal d'horloge, tension d'alimentation, etc.) dépendent de la norme considérée.

La carte à puce est un support contraignant : sa faible épaisseur lui interdit la majorité

des composants discrets, tandis que le procédé d'encartage et les contraintes mécaniques d'utilisation limitent la surface silicium à  $30mm^2$ . Cependant, l'évolution de la technologie CMOS a permis d'augmenter considérablement la complexité et les performances des circuits électroniques embarqués. En effet, depuis son introduction en 1963, la technologie CMOS a vu sa densité d'intégration doublée tous les 18 mois. En 1970, un transistor MOS occupait une surface de  $1mm^2$  ( $L=10\mu m$  et  $tox=1.2\mu m$ ). A surface égale, les procédés de fabrication actuels permettent d'intégrer jusqu'à 3 millions de transistors (L=45nm et tox=1.3nm), portant à plus d'un milliard le nombre de transistors par puce. Dans le même temps, la fréquence de transition d'un transistor MOS est passée de quelques mégahertz à plus de 100GHz, tandis que le coût de fabrication en volume a chuté de 1dollar par transistor à moins de 0.1dollar par transistor. Qu'elles soient technologiques ou financières, ces évolutions exponentielles ont favorisé la percée commerciale de la technologie CMOS. A l'heure actuelle, la majorité des circuits pour cartes à puce reposent entièrement sur cette technologie.

L'apparition de nouvelles fonctionnalités a scindé la classification des cartes à puce en deux catégories : les cartes à mémoire (carte téléphonique, carte de stationnement, etc.) et les cartes à microprocesseur (carte bancaire, carte GSM, carte de santé, passeport biométrique, etc.). Les cartes à mémoire comportent généralement une mémoire non-volatile et un bloc logique sécuritaire. Plus sophistiquées, les cartes à microprocesseurs sont de véritables microordinateurs de poche. Ces nouveaux types de cartes nécéssitent, avec l'augmentation de la taille des mémoires et de la multiplication des applications intégrées, des taux de transfert de plus en plus importants.

# 1.3 Historique du choix de la norme USB

Le débat sur l'avenir de la carte SIM s'est cristallisé et même crispé autour de la question du protocole. USB ou MMC (La MultiMediaCard (MMC) standard a été introduit en no-

vembre 1997 par SanDisk et Siemens AG / Infeneon Technologies AG). Il s'est soldé, après près d'un an de débats difficiles, voire houleux, au sein du SCP (Smart card platform) de l'ETSI, en charge de la spécification d'un protocole rapide pour la carte SIM, par des conclusions en demi-teintes. Axalto soutenait la proposition USB, Gemplus, la proposition MMC, Gemalto a choisi... USB et MMC. L'ETSI a dû donc officiellement voter pour spécifier un double « standard » ainsi que des mécanismes de sélection de tel ou tel « standard » (car certains téléphones ne peuvent supporter qu'un des deux protocoles).

La complexité engendrée par cette situation, qui paraît plus diplomatique que fondée techniquement, a-t-elle un avenir ? Il semble que non. Car, outre des capacités mémoires accrues, assorties d'un protocole rapide pour charger et échanger des contenus (voire gérer des flux Mpeg-4 de TV), la carte SIM de nouvelle génération doit aussi supporter une interface pour piloter des transactions sans contact de type NFC. Or, les ressources en contacts sur la carte restent limitées Fig. 1.5.

Le choix s'est donc porté sur le protocole USB pour le protocole rapide et du Single-wire protocol (SWP) pour celui de l'interface sans contact, un protocole full duplex conçu sur un seul fil, codéveloppé par Axalto (Gemalto) et Inside Contactless. Ces deux options sont en effet les seules qui offrent une compatibilité avec la carte SIM existante et les exigences de l'ETSI: celles, entre autres, de faire coexister le protocole ISO (pour des raisons de compatibilité avec l'existant), le protocole USB et une interface vers un circuit sans contact de type NFC, et ce sans modifier ni les allocations des contacts de la carte SIM, ni leur nombre (huit contacts, Fig. 1.5). L'interface ISO utilise en effet les contacts C2, C3, C7, l'USB, les contacts C4 et C8, et le SWP, un seul contact, le C6. Les contacts C1 et C5 sont utilisés dans tous les cas pour l'alimentation (Vcc) et la masse (GND).

FIG. 1.5 – Contacts d'une carte à puce ISO

## 1.4 Historique de l'asservissement de phase

Outre les asservissements de phase réalisés par la Nature, l'Homme a créé ses propres asservissements de phase à des fins multiples. La réalisation électronique d'un asservissement de phase par rétroaction est appelée boucle à verrouillage de phase. L'utilisation des boucles à verrouillage de phase, que l'on notera BVP par la suite, est tellement répandue de nos jours qu'un foyer occidental moyen comporte au moins une dizaine d'exemplaires de ce circuit (au moins 2 exemplaires dans un téléviseur, 4 dans un ordinateur, 1 dans une radio, 1 dans un téléphone, 1 dans une télécommande, etc.). Une des premières observations scientifiques du phénomène de synchronisation a été celle de Huygens en 1673 qui a observé la synchronisation de deux horloges à balancier. Les premières études systématiques avec une réalisation électronique d'un asservissement de phase semblent être celle d'Appleton en 1922 [5], et de Van der Pol en 1927 [6], qui ont montré que l'on pouvait asservir la phase d'un oscillateur à triodes au moyen d'un signal de fréquence légèrement différente. La première description connue d'une BVP (en anglais PLL pour Phase Locked Loop) par rétroaction est publiée par l'ingénieur français De Bellescize en 1932 [7] à propos de la réception synchrone de signaux radio.

**De Bellescize** proposait un asservissement de phase dans le but de reconstruire la porteuse d'un signal modulé en amplitude. Ce principe de réception dit hétérodyne a été dans un

premier temps délaissé, car trop complexe, au profit de la réception synchrone. La réception hétérodyne est ensuite devenue incontournable avec le besoin d'accroître les performances et avec la réduction des coûts apportée par l'électronique intégrée.

[8] La première utilisation intensive de la PLL a été la synchronisation horizontale et verticale des balayages des postes de télévision. Le départ du balayage de chaque ligne et celui de chaque demi- trame d'une image télévisée est donné par une impulsion dans le signal vidéo. Une méthode directe pour construire le balayage du tube de télévision consiste à faire partir une trame de balayage des l'apparition d'une impulsion. Mais cette méthode étant très sensible à l'absence d'impulsion et aux bruits, l'utilisation de deux oscillateurs libres synchronisés sur les impulsions du signal vidéo à été mise en oeuvre en utilisant le verrouillage de phase. Ceci permet d'obtenir un balayage en l'absence d'impulsion et surtout de rejeter l'effet du bruit sur le déclenchement des trames provoquant des tremblements de l'image et une mauvaise résolution. Avec le dévelopement des technologies et de leurs domaines d'applications, de nouvelles contraintes sont apparues. La conquête de l'espace et les vols spatiaux notamment, ont apporté de fortes contraintes sur les circuits de télécommunication :

- Faible puissance des signaux porteurs (10mW) et donc fort rapport signal sur bruit, mais aussi un déplacement de la fréquence porteuse dû à la dérive en température des oscillateurs embarqués et à l'effet Doppler lié au déplacement des satellites.

Ces exigences ont inspiré d'énormes progrès dans la maitrise des BVP et ont étendu les domaines d'application [9] :

- les transpondeurs qui localisent et identifient le véhicule dans lequel ils sont embarqués en renvoyant le signal d'un radar en multipliant sa fréquence par un rapport n/m identifiant l'appareil;

- les modulateurs et démodulateurs de fréquence utilisés principalement dans les télécommunications;

- les onduleurs générant la commande des machines asynchrones, et la synchronisation

d'un alternateur sur le réseau électrique;

- les multiplicateurs et diviseurs de fréquence;

- la synchronisation des transmissions digitales utilisées notamment dans les transmissions NRZ (Codage en Non Retour à Zéro), les réseaux Ethernet, le stockage sur support magnétique ou optique, les télécommandes, etc.;

- les générateurs de fréquence dans les téléphones à fréquence vocale, les synthétiseurs musicaux :

- les générateurs d'horloge pour les microprocesseurs et leurs périphériques ;

- les convertisseurs tension-frequence et fréquence-tension ; etc.

De toutes ces applications se sont dégagées un nombre important de solutions, donnant naissance à des types de BVP qui différent selon les signaux traités et la réalisation de chacune des parties qui les composent.

# 1.5 Réflexions sur la notion de Phase et de Fréquence

La phase et la fréquence instantanée sont des notions communément admises qui sont, la plupart du temps, utilisées sans être précisément définies. Dans l'étude d'un asservissement de phase, il est important de définir cette notion avec précision car elle intervient dans la modélisation des signaux. Ce problème de la représentation mathématique des signaux et de leur analyse est l'objet de **la théorie du signal** [10], [11], [12]. La définition de fréquence et de spectre instantanés est une difficulté de cette théorie faisant appel à la relation d'incertitude entre la précision temporelle et la précision fréquentielle de la mesure d'un signal. L'étude de la stabilité d'un asservissement de phase ne nécessite pas, en général, une analyse des signaux très poussée comme par exemple l'analyse par ondelettes. La transformée de Fourier est un outil suffisant pour ce genre d'étude. Par contre, l'étude fait appel à une représentation mathématique temporelle des signaux qui doit être adaptée aux signaux ren-

contrés, et qui permet une modélisation aisée du système. La modélisation des signaux d'un asservissement de phase se fait en calculant l'évolution de leur phase instantanée ou de leur fréquence instantanée, la fréquence étant définie comme la dérivée temporelle de la phase. Une modélisation rigoureuse doit définir ces deux notions et établir leur lien avec l'amplitude du signal. Nous envisageons, pour cela, une définition de la fréquence instantanée établie par approximation locale du signal. Une réflexion sur l'observabilité de la phase d'un signal carré, qui est la forme des signaux rencontrés dans ce mémoire, montre les limites de la définition. On définit alors la notion de phase instantanée à partir des variables d'état d'un oscillateur à relaxation. Cette définition permet de représenter le signal par un signal analytique de même phase et d'amplitude telle que le signal réel soit de forme carrée. On obtient ainsi une représentation mathématique du signal faisant apparaître sa phase et sa fréquence instantanée qui, de plus, admet une représentation physique aisée de ces notions.

#### 1.5.1 Phase et fréquence dans le cas de signaux périodiques

La phase et la fréquence sont des caractéristiques constantes du signal établies pour des signaux périodiques. La phase est une constante angulaire définie par rapport à une référence temporelle, généralement l'instant initial, ou par rapport à la phase d'un signal de référence. La fréquence est définie par rapport à une durée d'observation pendant laquelle le nombre d'occurrences de cycles identiques est compté. Dans le cas d'un simple signal sinusoïdal, l'amplitude A, la phase  $\varphi$ , et la pulsation  $\omega$ , apparaissent explicitement dans l'écriture du signal e(t):

$$e(t) = A\sin(\omega t + \phi) \tag{1.1}$$

La phase étant exprimée en radians, la pulsation est exprimée en radians par seconde. Un simple changement d'unité permet de lier la pulsation  $\omega$  et la fréquence f par

$$\omega = 2\pi f \tag{1.2}$$

Cette définition de la phase n'est plus valable lorsque les caractéristiques des signaux varient dans le temps. C'est le cas des signaux quasi-périodiques, comme les signaux modulés en phase et/ou en fréquence ou ayant subit un encodage (NRZ, NRZI, MANCHESTER, MILLER ...). La phase et la fréquence ne sont plus, dans ce cas là, des caractéristiques constantes du signal et leur mesure dépend alors de la période d'observation. Par extension, une observation de durée infinitésimale permet de définir la notion de phase instantanée, de fréquence instantanée et de phase initiale.

#### 1.5.2 Phase et fréquence dans le cas de signaux non périodiques

Une extension rigoureuse de la notion de fréquence instantanée des signaux quasi périodiques est difficile car elle demande d'exprimer mathématiquement une notion extrapolée intuitivement du cas périodique. La phase instantanée est alors vue comme une information sur l'état d'avancement du cycle à un instant t, ayant pour valeur  $2\pi$  à la fin du cycle, 0 à son début, et de croissance monotone. La fréquence instantanée est liée à la vitesse d'exécution d'un cycle prise à un instant t. Dans le cas d'un signal sinusoïdal quasi périodique  $Asin(\phi(t))$  d'amplitude constante, on assimile la valeur  $\phi(t)$ , à la phase instantanée du signal puisque celle-ci est une valeur en radian égale à  $2\pi$  à la fin d'un cycle et nulle au début. La phase initiale  $\phi(t0)$  est la valeur de la phase instantanée à l'instant initial. Par contre la définition de la fréquence instantanée n'est pas immédiate, car elle nécessite une observation du signal pendant au moins un cycle complet.

# 1.5.3 Définition de la fréquence instantanée par approximation locale du signal

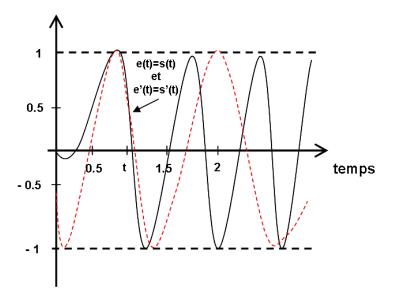

Une première proposition de définition, illustrée par la Fig. 1.6, consiste à approcher le signal quasi-périodique de forme quelconque s(t) à l'instant t par une sinusoïde e(t) de fréquence constante : cette fréquence définit la fréquence instantanée du signal à l'instant t.

On dit que les fonctions s(t) et e(t) sont semblables à l'instant t si leurs amplitudes sont

**FIG. 1.6** – La fréquence instantanée du signal, en trait plein, modulée par un message m(t) = t, est déduite de celle d'une sinusoïde e(t), en pointillés semblable à s(t) à l'instant t

égales et si le premier terme de leurs développements en série de Taylor sont égaux [11], [12]:

$$s(t + \Delta t) = s(t) + \Delta t \cdots s'(t) + \dots e(t + \Delta t) = e(t) + \Delta t \cdots e'(t) + \dots$$

(1.3)

La fréquence instantanée du signal s(t) est alors celle du signal sinusoïdal e(t) de même amplitude vérifiant e(t) = s(t) et e'(t) = s'(t). On obtient ainsi les relations suivantes :

$$e(t) = A \cdot \sin(\omega_i t) = s(t)e'(t) = A \cdot \omega_i \cdot \cos(\omega_i t) = s'(t)$$

(1.4)

A partir de ces égalités, l'expression de la fréquence instantanée, en fonction de la mesure s(t) du signal et de sa dérivée  $\dot{s}(t)$ , est unique :

Remarque 1 Ce résultat est obtenu en remplaçant le terme  $cos(\omega_i(t))$  dans l'expression  $\dot{e}(t) = \dot{s}(t)$  par sa valeur en fonction du sinus :  $\pm \sqrt{1 - \sin(\omega_i(t))^2}$ . La fréquence instantanée étant par définition positive, l'inversion du carré du cosinus se fait sans ambiguïté de

signe.

Remarque 2 Dans le cas d'un signal sinusoïdal quasi périodique à amplitude constante  $Asin(\phi(t))$ , cette définition devient la relation bien connue entre phase et pulsation :  $\omega_i = \frac{\delta(\phi(t))}{\delta t}$ .

**Remarque 3** Cette définition de la fréquence instantanée est dans une certaine mesure arbitraire. En imposant dans la définition l'égalité entre les seconds termes du développement de **Taylor**  $\ddot{s}(t) = \ddot{e}(t)$ , on obtient une fréquence instantanée qui peut être complexe ou multiple. Une telle définition n'aurait pas de sens physique.

Remarquons que la formule 1.4 est indéterminée au niveau des extremas de la courbe, lorsque  $\dot{s}(t)=0$  et s(t)=A: le résultat dépend alors des seconds membres du développement de **Taylor**. Cette singularité apparaît car, au niveau des extremas, la phase n'influence plus le signal et rend la mesure de ses variations impossibles en ces points isolés. Si le signal n'est pas lié à la phase à chaque instant, comme dans un signal carré, cette définition ne donne plus de résultats physiquement cohérents. Un signal carré est constant partout sauf en quelques points où il commute entre deux valeurs constantes. L'observation de la fréquence instantanée d'un tel signal conduirait à une fréquence nulle partout et infinie aux points de discontinuités. La définition n'est donc pas valable lorsque la phase du signal n'est pas observable partout à l'aide de la mesure du signal et de sa dérivée. Nous proposons de définir la phase d'un tel signal en observant les variables d'état du système générant ce signal. Dans cette étude, nous nous intéressons exclusivement aux signaux quasi-périodiques générés par un oscillateur à relaxation.

### 1.5.4 Application : observation de la phase d'un oscillateur à relaxation

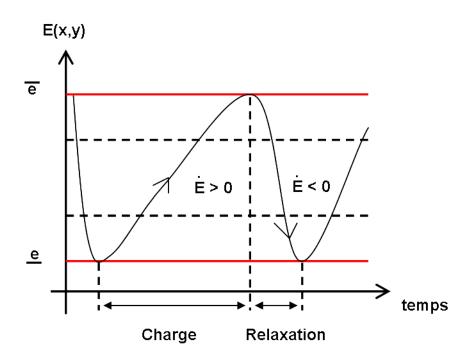

Le principe de l'oscillateur à relaxation est d'emmagasiner de l'énergie tant qu'une limite supérieure n'est pas atteinte –période de charge– le système change alors de comportement et libère l'énergie tant qu'une limite inférieure n'est pas atteinte –période de relaxation–.

Le système retrouve alors son comportement initial et commence une nouvelle période de charge : il oscille ainsi entre les deux limites. Ce montage, consistant à charger et décharger une capacité avec un courant dont on contrôle la valeur, est très utilisé en électronique, car il permet de générer directement un signal carré dont on peut contrôler la fréquence d'oscillation.

Nous pouvons établir un modèle hybride [13], [14], [15], des oscillateurs à relaxation. En effet, l'oscillateur à relaxation possède deux comportements : la charge pendant laquelle l'énergie du système augmente vers une valeur; et la relaxation, pendant laquelle cette énergie décroît vers une valeur e. En choisissant un vecteur d'état X, on peut établir un modèle différentiel continu pour chaque comportement :

Le champ différentiel f0 correspondant au comportement de relaxation et le champ f1 à celui de charge. L'énergie est alors une fonction du vecteur d'état E(X) de l'oscillateur.

FIG. 1.7 – Evolution de l'énergie d'un oscillateur à relaxation dans le plan de phase.

La Fig. 1.7, montre un exemple d'évolution de cette énergie dans un plan de phase de

dimension deux. Dans l'état de charge, le système commute lorsque l'énergie E(X) atteint la valeur  $\overline{e}$ . La relation  $E(X) = \overline{e}$  définit une frontière de commutation dans le plan de phase du système f1. De même,  $E(X) = \underline{e}$ , définit une frontière de commutation du système f0. Il existe des conditions nécessaires à l'apparition d'oscillations [15] dans un tel système, telle que la décroissance (resp. croissance) de l'énergie le long d'une trajectoire de f0 (resp. f1) lorsque,  $E(X) \ge \underline{e}$  (resp.  $E(X) \le \overline{e}$ ). Ces conditions, utiles à la conception de l'oscillateur, ne sont pas discutées dans ce mémoire.

#### Définition de la phase instantanée d'un oscillateur à relaxation

Lorsque l'oscillateur est bien conçu, l'énergie E(X) oscille entre les deux limites en décrivant une trajectoire cyclique dans le plan de phase (voir la fig.1.7) défini par deux arcs : un arc correspondant à la charge où E(X) est croissante E(X)>0 et un arc correspondant à la relaxation avec une énergie décroissante E(X)<0. La valeur de cette énergie et le signe de sa variation donnent toute l'information nécessaire sur l'état d'avancement du mouvement cyclique : la phase. Nous pouvons donc proposer la définition suivante [13] de la phase instantanée d'un signal généré par un oscillateur à relaxation.

**Définition 3** - Phase instantanée du signal d'un oscillateur à relaxation : - Toute variable d'état à croissance monotone liée à l'énergie emmagasinée par l'oscillateur, et au signe de sa variation, prenant une valeur nulle en un point du mouvement cyclique - point de référence, - une valeur égale à  $2\pi$  à la fin du premier cycle débuté en ce point de référence et  $k2\pi$  à la fin du kème cycle.

### 1.5.5 Modélisation du signal carré et définition de sa fréquence instantanée

Le signal carré s(t) est défini, sans perte de généralité, en fonction de la phase instantanée  $\varphi(t)$

$$s(t) = \begin{cases} 0 & \text{si } 0 \le \varphi(t), \mod 2\pi \le \pi, \\ 1 & \text{sinon} \end{cases}$$

(1.5)

L'utilisation du concept de signal analytique, décrit dans [16] et [17], permet de définir le signal carré et d'obtenir une définition de la fréquence instantanée. On peut représenter le signal carré sous la forme d'un signal analytique complexe

$Z_s(t)=a(t)\exp(i\varphi(t)-\frac{\pi}{2})$  ayant pour phase instantanée la phase de l'oscillateur à relaxation  $\varphi(t)$  définie plus haut. Le module a(t), donnant une forme carrée au signal, est défini par :

$$a(t) = \begin{cases} 0 & \text{si } 0 \le \varphi(t), \, \text{mod } 2\pi \le \pi, \\ \frac{1}{\cos(\varphi(t) - \frac{\pi}{2})} & \text{sinon} \end{cases}$$

(1.6)

Ce signal analytique définit ainsi un signal de forme carrée observant un front descendant lorsque :

$$\varphi(t) = k * 2\pi \tag{1.7}$$

Avec

$$k \in N \tag{1.8}$$

Pour simplifier les écritures nous omettrons volontairement le décalage de phase de  $\frac{-\pi}{2}$  utilisé dans cette définition, il faudra donc lire  $\varphi(t)-\frac{\pi}{2}$  à la place de  $\varphi(t)$  dans la suite. On hérite ainsi de la définition 4 de la fréquence instantanée d'un signal analytique [15].

**Définition 4** - Fréquence instantanée d'un signal analytique : - La dérivée temporelle de l'argument  $\varphi(t)$  du signal analytique  $Z_s(t) = a(t) \exp(i\varphi(t))$ , défini comme sa phase instantanée, divisée par  $2\pi$ :

$$f_i(t) = \frac{1}{2\pi} \cdot \frac{\delta(\varphi_s(t))}{\delta t} \tag{1.9}$$

On obtient une modélisation du circuit dont les variables d'état ont un sens physique, et une notion de phase et de fréquence instantanée rigoureusement définies 'en phase' avec la conception intuitive que l'on lie à ces grandeurs.

Aprés avoir placé l'étude dans le contexte de l'environnement 'Smart-Card', puis fait état des différentes notions essentielles pour la bonne compréhension de la suite de l'étude :

- Phase et fréquence de signaux périodiques et non périodiques,

- Fréquence instantannée,

nous ferons un état de l'art sur la génération de fréquence et nous entrerons plus en détail dans la spécification de la norme USB.

# Etat de l'art sur la génération de fréquence et spécification USB

# 2.1 Les boucles à verrouillage de phase, BVP

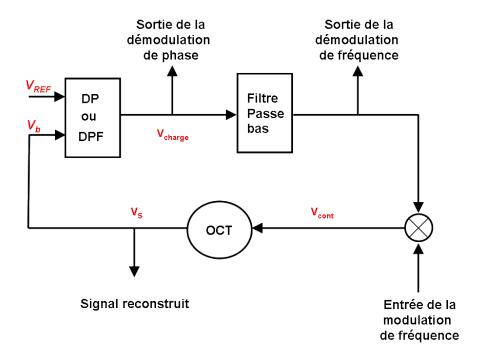

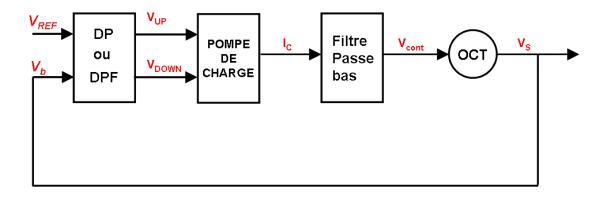

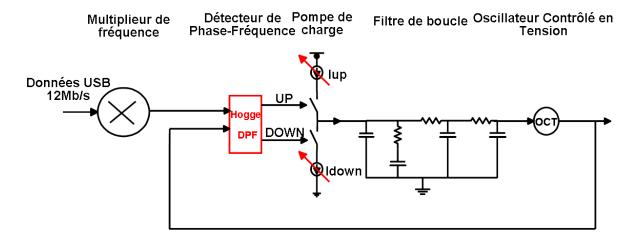

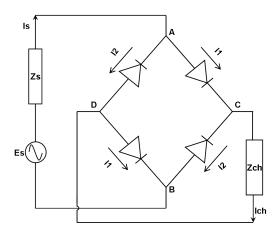

Bien qu'il y ait de nombreuses manières de réaliser une BVP, sa structure globale, présentée dans la Fig 2.1, n'évolue pas. Une BVP est constituée des trois blocs suivants :

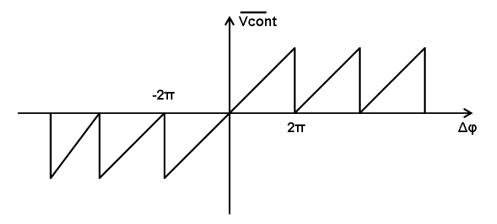

- un Détecteur de Phase ou d'un Détecteur de Phase Fréquence (PD ou PFD pour Phase Detector et Phase Frequency Detector en anglais) fournissant une information sur l'erreur de phase entre le signal d'entrée  $V_{REF}$  et le signal boucle vb, cette information dépend aussi de l'erreur de fréquence dans le cas du DPF;

- un Filtre Passe-bas chargé de filtrer les perturbations, stabiliser la boucle, et lisser la tension V cont transmise à l'oscillateur contrôlé en tension;

- un Oscillateur Contrôlé en Tension ou un Oscillateur Contrôlé Numériquement OCT ou OCN (VCO pour Voltage Controled Oscillator en anglais) qui délivre un signal de fréquence instantanée directement proportionnelle à la tension d'entrée.

La BVP effectue un asservissement sur la phase du signal bouclé  $V_b$ . Lorsque le signal de sortie  $V_s$  est en retard sur le signal d'entrée  $V_{REF}$ , le DP, à travers le filtre et l'OCT, augmente la fréquence du signal de sortie, ce qui a pour effet de réduire ce retard. Inversement, une diminution de la fréquence de l'OCT réduit l'écart de phase lorsque la sortie est en avance.

FIG. 2.1 – Applications de la Boucle à vérouillage de phase

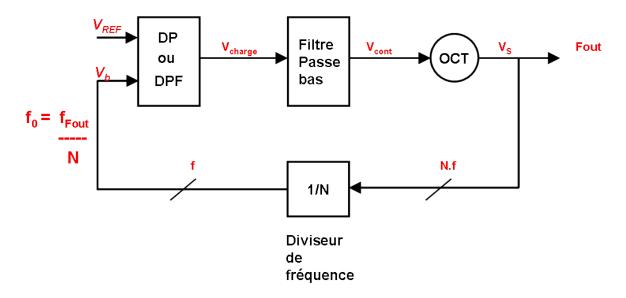

La notion d'entrée et de sortie d'une BVP est relative au type d'application qui lui est destinée, la Fig. 2.1 montre les points d'entrée/sortie de quelques applications. Dans le cas d'une modulation de fréquence, le signal de modulation est additionné à l'entrée de l'OCT et le signal modulé est récupéré à sa sortie, l'entrée du DP étant cadencée par la fréquence porteuse. Dans le cas d'une démodulation de fréquence, le signal à démoduler entre sur le DP, et le signal démodulé est récupéré à la sortie du filtre. Le bouclage de la BVP permet de réaliser une fonction directement mais aussi indirectement par asservissement du signal issu de la fonction inverse. Cela est utile lorsqu'une opération est techniquement difficile à réaliser directement. C'est le cas de la multiplication de la fréquence d'un signal par un nombre rationnel N/P. Il est facile de diviser la fréquence d'un signal binaire en utilisant

par exemple des compteurs, par contre sa multiplication est beaucoup plus difficile. Pour multiplier la fréquence f d'un signal par N, on peut introduire un Diviseur de Fréquence, comme dans la Fig.2.2, pour boucler le signal de sortie  $V_s$  vers le DP. Le signal bouclé  $V_b$  est alors de fréquence  $(f_0)$  N fois inferieure à celle du signal de sortie  $(F_{out})$ .

FIG. 2.2 – Boucle à vérrouillage de phase utilisée comme multiplieur de fréquence

L'asservissement de phase assure alors une fréquence f identique entre le signal bouclé  $V_b$  et le signal d'entrée  $V_{REF}$  ce qui permet d'obtenir un signal de sortie de fréquence N\*f. Il suffit alors de diviser la fréquence de sortie par P pour finalement obtenir le rapport de fréquence N/P.

La fréquence de sortie ainsi obtenue est :

$$F_{out} = \frac{N}{P} F_0 \tag{2.1}$$

# 2.2 Classification des Boucles à verrouillage de Phase

De la littérature concernant les BVP se dégage un grand nombre d'appellations ne désignant parfois pas le même système. On peut remarquer par exemple l'appellation de

DPLL désignant tantôt une BVP comportant un détecteur de phase logique, tantôt une BVP comportant un OCN. Globalement, une classification est utilisée implicitement distinguant les différents types de BVP selon [8]:

- le type de DP, pouvant être un détecteur échantillonneur, multiplieur, séquentiel ou logique;

- le type d'oscillateur, contrôlé par une commande numérique ou analogique.

Le type de filtre utilisé pouvant être déduit de la nature du DP et de l'oscillateur, celui-ci n'influence pas en général l'appellation de la BVP. Le tableau 2.1, liste les différents types de BVP les plus courantes ainsi que l'appellation issue de l'anglais.

| Type de détecteur de phase | Type d'oscillateur |                      |  |

|----------------------------|--------------------|----------------------|--|

|                            | Analogique (VCO)   | Numérique (NCO)      |  |

| Echantillonneur            | S-PLL              | DS-PLL               |  |

|                            | Sample PLL         | Digital Sample PLL   |  |

| Multiplieur                | A-PLL              | D-PLL                |  |

|                            | Analog PLL         | Digital PLL          |  |

| Logique                    | Xor-PLL            | Xor-DPLL             |  |

| Séquentiel                 | CP-PLL             | CUD-PLL              |  |

|                            | Charge Pump PLL    | Counting Up/Down PLL |  |

| Logiciel                   |                    | Soft-PLL             |  |

|                            |                    | Software PLL         |  |

TAB. 2.1 – Nomenclature des BVP

Selon le détecteur de phase on distingue les BVP analogiques —dont le détecteur de phase et l'oscillateur sont analogiques— des BVP semi numérique —dont le détecteur de phase est numérique et l'oscillateur analogique. Le choix du détecteur de phase dépend principalement des signaux qu'il reçoit. Lorsque le signal en entrée et le signal bouclé sont de type sinusoïdaux ou de manière plus générale à phase observable, les détecteurs de phases analo-

giques (multiplieurs, échantillonneurs, etc.) sont préférés aux détecteurs numériques car ces derniers sont très sensibles au bruit. Lorsque les signaux sont mixtes, dans les conversions de signaux carrés en signaux sinusoïdaux par exemple, l'utilisation de détecteurs de phase analogiques demeure avantageuse, notamment celle d'un détecteur par échantillonnage qui se trouve particulièrement adapté à cette situation. Lorsque les signaux sont tous deux de forme carrée, dont la phase n'est pas observable à tout instant, les détecteurs numériques s'imposent car ils peuvent détecter les transitions successives du signal. Lorsque la BVP est intégrée sur une puce, celle-ci se trouve souvent être la seule partie analogique du circuit, c'est le cas dans les circuits purement numériques comme les microprocesseurs, les DSP, les microcontrôleurs et leurs périphériques. Cette partie analogique devient coûteuse car elle empêche l'utilisation de certaines technologies à très basse tension utilisées en numérique et demande des efforts de conception qui doivent être renouvelés à chaque changement de technologie. C'est pourquoi des BVP entièrement numériques ont été réalisées en utilisant des détecteurs de phase numériques et en remplaçant le filtre et l'OCT par leurs équivalents numériques. Elles sont alors conçues et intégrées avec les outils de conception numériques, fondues avec les mêmes technologies et peuvent être directement réutilisées lors de changement de technologies. La conception de l'OCN est faite à partir d'une horloge externe de haute fréquence dont on compte le nombre de cycles. Cependant il existe des OCN n'exploitant pas d'horloges externes,[18] [19]. Dans certaines applications où un processeur est disponible, on peut remplacer les circuits numériques par un microprogramme exécuté par le processeur. Celui-ci mesure le signal d'entrée par un de ses périphériques, simule le fonctionnement du détecteur de phase, du filtre et de l'OCN -en utilisant l'horloge du processeur comme horloge de haute fréquence- calcule le signal de sortie et le transmet via un périphérique. Ces types de BVP sont qualifiés de BVP logicielles, ou Software PLL en anglais. Beaucoup de microcontrôleurs comportent une implémentation des éléments d'une BVP, et permettent de les contrôler par le microprogramme. Il ne faut pas confondre ces BVP dites programmables avec une BVP logicielle dont au moins une des parties de la BVP doit être implémentée par le microprogramme.

## 2.3 Boucle à Ligne de Délai, BLD

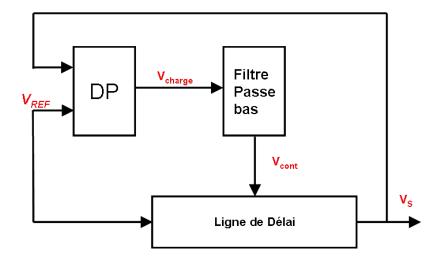

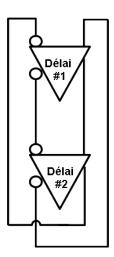

Un grand nombre d'applications utilisent des BVP comme nous l'avons vu précédemment. Les BLD sont apparues comme des alternatives séduisantes aux BVP. En effet de nombreux systèmes nécessitent une mise en phase précise des signaux d'horloge ou de données. Parfois un simple retard du signal permet ce décalage de phase, cependant cette méthode n'est pas robuste face aux variations de processus, de température et d'alimentations. Pour un réglage plus précis, les concepteurs incorporent souvent cet élément de retard dans une boucle de rétroaction qui synchronise la phase du signal de sortie avec celle d'un signal de référence. Dans le principe cette boucle est identique à celle des BVP décrites plus haut mis à part le fait que la phase est le seul paramètre pris en compte et que l'oscillateur est remplacé par une chaine de délai. Ce type de boucle est généralement référencé comme Boucle à Verrouillage de Phase à Ligne de Délai ou boucle à Ligne de Délai (Delay Line Loop en anglais). L'objectif de ces boucles est donc d'obtenir un positionnement en phase précis avec un bruit de phase faible (nous définirons ce terme au cours des prochains chapitres). La Fig.2.3 montre le principe de ce type de boucle.

Les blocs principaux sont identiques à ceux d'une BVP. Un détecteur de phase qui compare la phase du signal de référence à celle du signal de sortie de la ligne de délai et qui fourni un signal proportionnel à l'erreur de phase, un filtre passe bas pour filtrer ce signal et pour avoir en entrée de la ligne de délai un signal de contrôle adéquat permettant de moduler le retard de la ligne. L'entrée de la ligne de délai peut être le signal de référence ou bien un autre signal d'horloge interne.

La BLD a des caractéristiques de boucle plus simples que celles d'une BVP car comme nous le verrons plus tard, un zéro supplémentaire est nécessaire pour maintenir la stabilité d'une BVP. Avec un pôle unique la BLD est moins contraignante. Quand on compare les ca-

FIG. 2.3 – Boucle a Ligne De Délai

ractéristiques de ces deux systèmes sur leur capacitée à réduire le bruit de phase, on se rend compte que les BLD engendrent moins d'erreur de phase que les BVP et ce grâce à l'ordre moins élevé de leur boucle. Sur une BVP, lors d'une réponse à une perturbation du signal d'entrée, la boucle accumule de l'erreur de phase avant de corriger [20]. De plus les systèmes à base de BLD sont plus rapides que leur équivalent à base de BVP, car les contraintes de stabilité sont moins importantes (elles ne dépendent que du délai interne de la boucle) et permettent une caractérisation du système plus en adéquations avec les spécifications demandées.

Cependant comme les BLD ne comportent pas d'éléments de contrôle permettant des variations de fréquence, elles ont historiquement moins d'applications que les BVP. Bazes dans [21] exposa un exemple d'utilisation de ces boucles en générant de façon précise les signaux d'accès aux lignes et aux colonnes de DRAM. Une autre application est la génération d'une horloge ayant la même phase que l'horloge d'entrée d'un système dont le 'fan out' (nombre maximal de circuit logique élémentaires que l'on peut connecter en parralèle sur une sortie) est faible [22] permettant ainsi de régénérer les signaux de données dans le système. On trouve, ces dernières années, de plus en plus d'articles, [23] [24], qui introduisent des architectures qui permettent de multiplier des fréquences en utilisant des BLD et ainsi de pouvoir

réaliser des fonctions de génération d'horloge.

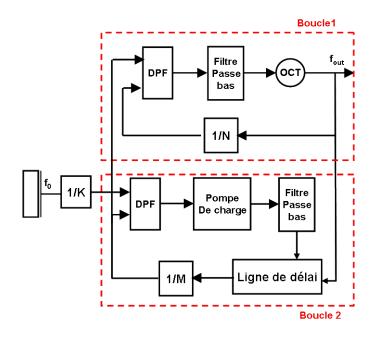

Le principal inconvénient de ces structures est qu'elles nécessitent l'utilisation de circuits complémentaires, comme l'utilisation de plusieurs boucles (Fig.2.4 [25] pour la régénération de donnée et d'horloges, ou de système correcteur de rapport cyclique [26] pour les synthétiseurs de fréquence.

FIG. 2.4 – Schéma fonctionnel de la synthèse de fréquence double boucle

Le précédent chapitre présentait les définitions des deux notions importantes de la récupération d'horloge : la phase et la fréquence de signaux périodiques et non périodiques, ainsi qu'une vue d'ensembles des deux éléments principaux utilisés dans les systèmes de récupération d'horloge, les BVP et les BLD. La Spécification USB et ses contraintes doivent être analysées pour connaître les signaux et les données sur lesquels on peut se synchroniser ainsi que les contraintes temporelles et fréquentielles (temps maximum d'accrochage de la fréquence, erreur autorisée sur la période du signal de sortie, encodage du signal de référence...). Cette étude nous amènera à faire un choix structurel pour le système de récupération d'horloge. Le système doit être innovant, robuste aux variations de température,

d'alimentation et de processus, de faible coût et occuper un espace minimum. Toutes ces spécifications ajoutent des contraintes sur le choix et la conception des divers blocs. Une fois la structure choisie, le chapitre 3 présentera une étude complète de ce système. Au fil de ce mémoire les problèmes de conception rencontrés seront évoqués ainsi que les solutions mises en oeuvre. Pour une meilleure compréhension, un chapitre sera consacré à la définition du bruit de phase ainsi qu'à son impact sur les différents blocs. Dans ce chapitre l'étude mathématique sera complétée par des résultats de simulations ainsi que des résultats de mesures sur silicium.

Enfin les résultats complets de ce travaille de thèse seront éxposés en comparant les mesures siliciums avec les résultats de simulation et les modèles mathématiques.

# 2.4 Spécification USB

L'objectif premier de la norme USB (acronyme d'Universal Serial Bus) était de répondre à trois impératifs [27] :

Permettre la connexion entre un téléphone portable et un PC: "It is well understood that the merge of computing and communication will be the basis for the next generation of productivity applications. The movement of machine-oriented and human-oriented data types from one location or environment to another depends on ubiquitous and cheap connectivity. Unfortunately, the computing and communication industries have evolved independently. The USB provides a ubiquitous link that can be used across a wide range of PC-to-telephone interconnects."

Etre Facile d'utilisation: "The lack of flexibility in reconfiguring the PC has been acknowledged as the Achilles' heel to its further deployment. The combination of user-friendly graphical interfaces and the hardware and software mechanisms associ-ated with new-generation bus architectures have made computers less confrontational and easier to

reconfigure. However, from the end user's point of view, the PC's I/O interfaces, such as serial/parallel ports, keyboard/mouse/joystick interfaces, etc., do not have the attributes of plug-and-play."

Une capacité de connexion importante: "The addition of external peripherals continues to be constrained by port availability. The lack of a bidirectional, low-cost, low-to-mid speed peripheral bus has held back the creative proliferation of peripherals such as telephone/fax/modem adapters, answering machines, scanners, PDA's, key-boards, mice, etc. Existing interconnects are optimized for one or two point products. As each new function or capability is added to the PC, a new interface has been defined to address this need."

Ces trois Impératifs sont tirés de l'Introduction de la spécification de la norme USB version 0.7 datant de novembre 1994. En effet, comme l'avaient bien compris les concepteurs de la norme USB (Compaq, Hewlett-Packard, Intel, Lucent, Microsoft, NEC, Philips), avec l'avènement de la téléphonie mobile et la recrudescence de l'équipement informatique des ménages, une convergence de ces deux mondes était devenue inévitable. Un mode de transfert de données normalisé a été nécessaire pour faciliter les échanges. La démocratisation de cette norme et son utilisation par le grand public, passe par un coût raisonnable, une facilité d'utilisation et une capacité de connexion importante. Depuis la version 2.0 d'avril 2000 un troisième taux de transfert High-speed de 480Mb/s, a été ajouté aux deux premiers taux initiaux, Full-speed et Low-speed, respectivement de 12Mb/s et 1.5Mb/s. Cette mise à jour reste dans la lignée des précédentes versions qui définissent les performances de la norme USB qui est une interface rapide, bidirectionnelle, isochrone et de faible coût, dont les connexions sont gérées dynamiquement.

#### 2.4.1 Généralités sur la transmission USB

Le protocole USB possède les caractéristiques suivantes :

- Protocole de communication série entre entités.

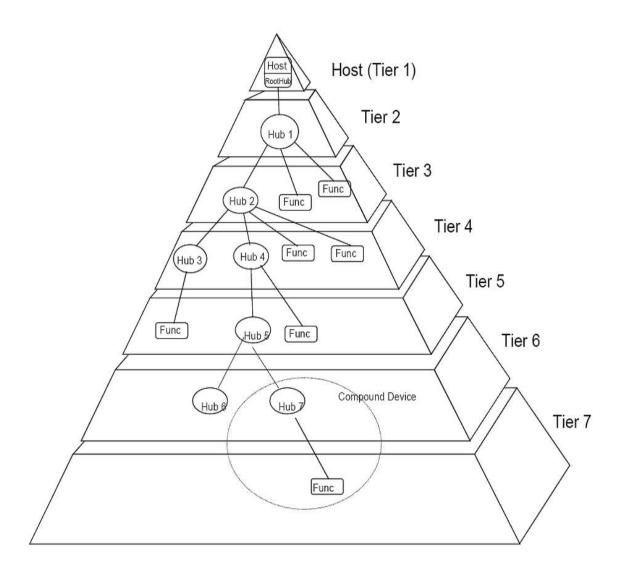

- Architecture étoilée et pyramidale, Fig.A.2.

- Échanges de données à vitesse prédéfinie dans la spécification USB.

- Possibilité de connecter un grand nombre de périphériques.

- facilité d'utilisation : "plug'n play"

- Largeur de bande passante garantie et basses latences

En effet, l'hôte se trouve au centre du réseau, et les périphériques à l'extérieur. L'Hôte USB a la charge de mener à bien toute les transactions et de programmer la bande passante et le taux de transfert, 1,5Mbits/s ou 12Mbits/s ou 480Mbits/s selon la tolérance du périphérique concerné. Typiquement, les modes High-speed et Full-speed peuvent être isochroniques (Largeur de bande passante garantie et basses latences, appropriées pour la téléphonie, l'acoustique, la vidéo, etc.), alors que les données Low-speed viennent des dispositifs interactifs.

Dans la suite de l'étude nous nous concentrerons sur le mode de transfert Full-speed.

L'hôte doit être capable de supporter jusqu'à 127 dispositifs physiques. Le branchement à chaud avec des pilotes qui sont directement chargeables et déchargeables rend facile et accessible son utilisation. L'utilisateur branche simplement l'appareil sur le Bus, l'Hôte détectera cet ajout, interrogera l'appareil nouvellement inséré et chargera le pilote approprié pendant le temps qu'il faut au sablier pour clignoter sur l'écran assurant qu'un pilote est installé pour l'appareil sélectionné. L'utilisateur final n'a pas besoin de se soucier des terminaisons, de termes tels qu'IRQs, adresses de ports, ou de la réinitialisation de l'ordinateur. Une fois que l'utilisateur a terminé, il lui suffit de retirer le câble, l'Hôte détectera cette absence et déchargera automatiquement le pilote. On dit que les périphériques sont auto définis.

De plus ce protocole prend en charge l'ajout de dispositifs composés, c'est à dire de périphériques comportant plusieurs fonctions telles que les imprimantes multifonctions (scanner, photocopieuses, fax...)

L'hôte est au sommet de la pyramide de communication Fig.A.2. Les transactions USB

se font grâce à l'émission de plusieurs paquets dont le format obéit à un standard. Chaque transaction consiste en la succession des paquets suivants :

- Un paquet Jeton (en anglais Token)

- Un paquet de données (en anglais DATA)

- Un paquet d'état (en anglais HandShake poignet de main)

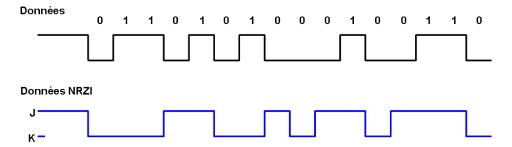

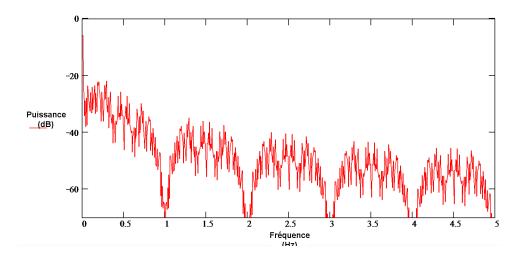

Il faut aussi mentionner que les données du flux de communication USB sont encodées en NZRI (Non Zéro Return Inverse). Le signal NRZI possède deux propriétés qui influence directement la conception d'un circuit de récupération d'horloge. En NRZI, encoder "1" revient à ne pas changer le niveau du signal alors qu'un "0" correspond à un changement d'état. La Fig.2.5 montre une série de données et son équivalent NRZI. L'état *J* représente le niveau haut sur la ligne de signal et *K* le niveau bas. Une suite de "0" fait donc commuter le signal NRZI entre niveau haut et bas tandis qu'une suite de "1" crée une longue période sans changement d'état du signal NRZI.

FIG. 2.5 - Données encodées en NRZI

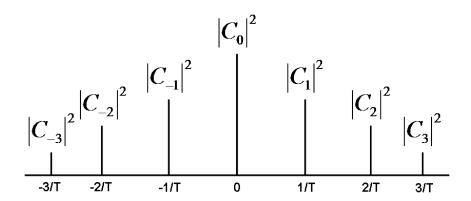

Pour une séquence binaire aléatoire, de fréquence,  $r_b$ , et une probalité égale de '1' et de '0', la densité spectrale de puissance vaut, [28] :

$$P_x(\omega) = T_b \left[ \frac{\sin[(\omega \cdot t_B)/2]}{(\omega \cdot t_B)/2} \right]^2 et T_b = \frac{1}{r_b}$$

(2.2)

On peut observer que cette fonction présente une valeur nulle aux multiples entiers de  $r_b$ . Nous regarderons ce point plus en detail dans  $\bf S$  4.6.

Une autre propriété importante est que le signal peut comporter de longues séquences

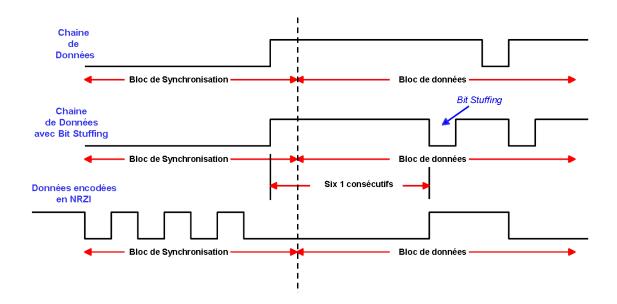

sans transition. Pour assurer un nombre de transitions suffisantes et ainsi permettre la synchronisation d'horloge, le protocole USB utilise une méthode dite de 'Bit Stuffing' Fig.2.6. Un zéro est inséré après une séquence de six '1' consécutifs dans la chaîne de données pour forcer une transition sur le signal encodé. Cela donne au recepteur un signal avec au moins une transition tous les sept temps bit, pour lui permettre de se synchroniser et ainsi de pouvoir décoder correctement les signaux de données. Le 'Bit Stuffing' commence avec le bloc de synchronisation envoyé au début de chaque paquet Fig.2.6. En effet le système compte le nombre de '1' à partir du dernier '1' du champ de synchronisation. Le bloc de réception doit être capable de décoder le signal NZRI, détecter le bit inséré par le 'Bit stuffing' et le rejeter.

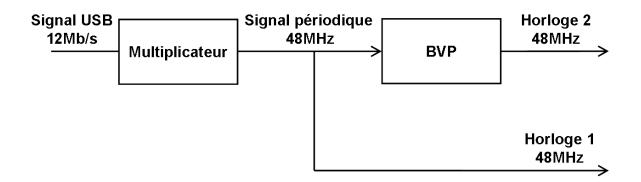

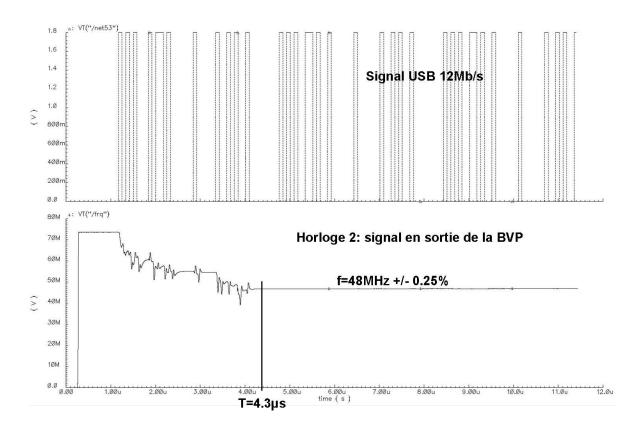

Le signal de donnée, reçu par les divers éléments connectés à l'hôte, est un signal nonpériodique et dans le cas (Full-Speed), ayant un taux de transfert de 12Mb/s, soit un temps bit de 83.33ns. De plus la spécification demande, à tout système désirant émettre un signal répondant à la certification USB, une précision de 2500ppm sur la fréquence du signal, soit 0.25%.

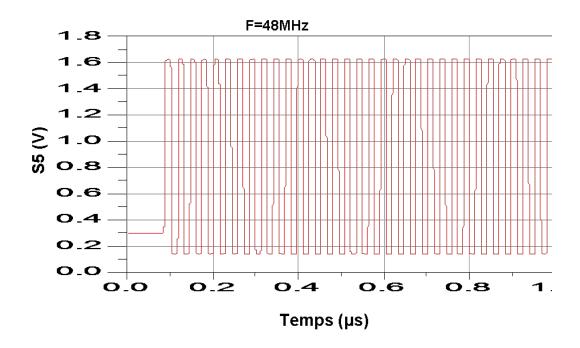

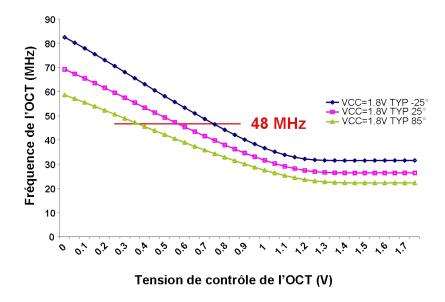

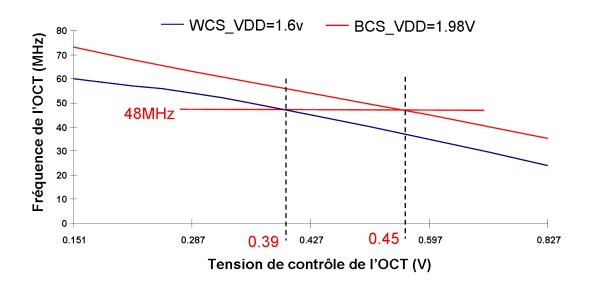

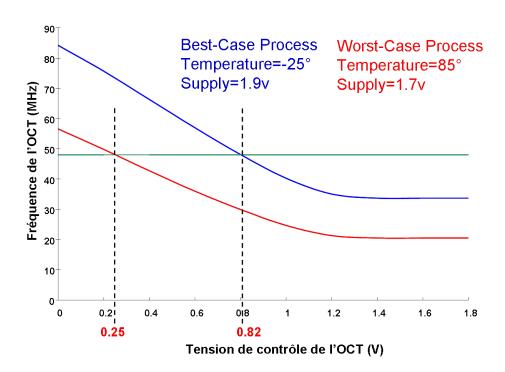

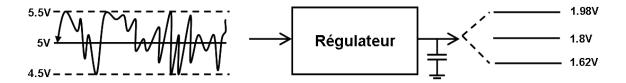

**FIG. 2.6** – Bit Stuffing

Le système doit être capable d'émmettre un signal cadencé à  $12Mb/s \pm 0.25\%$  et avoir un signal d'horloge suffisamment précis pour le faire. Le choix de réalisation a été, en accord avec Atmel Rousset, partenaire industriel de cette étude, un signal d'horloge de 48MHz (période 20.833ns) ce qui permet en réception de suréchantillonner le signal reçu pour un meilleur décodage. Cela permet d'avoir 4 fronts d'horloge par temps bit du signal NRZI. Pour assurer un décodage efficace, en réception, une horloge moins précise que pour l'émission est suffisante. En effet pour décoder correctement l'information du signal NRZI on peut admettre entre trois et cinq fronts d'horloge par Bit, ce qui nous permet de certifier la valeur du signal avant de le décoder. Le problème étant de pouvoir certifier que pour l'émission on aura une horloge permettant d'envoyer un signal à  $12Mb/s \pm 0.25\%$ .

Il faut donc, soit générer une horloge précise dès la réception, soit trouver un moyen d'en affiner sa précision entre la réception des informations envoyées par l'hôte et l'émission de la réponse.

Nous allons maintenant nous intéresser plus en détail au protocole d'échange de données USB afin de determiner quel seront les possibilitées de synchronisations.

#### 2.4.2 Protocole USB

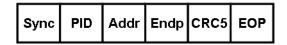

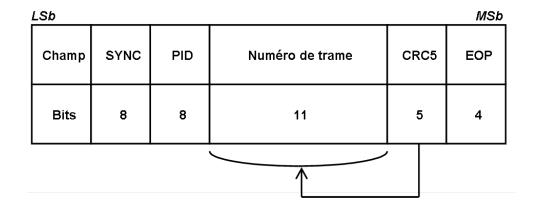

Le bus est géré par l'hôte, ce qui signifie que c'est lui qui initie toutes les transactions en envoyant un paquet Jeton (TOKEN) dans lequel figure le type de transaction (lecture ou écriture), l'adresse du périphérique de destination, et la terminaison désignée (nous reviendrons sur ce terme plus loin). Ensuite le paquet de données (DATA) qui contient les informations réellement utiles dans la transaction, puis le paquet d'état qui indique si l'échange s'est correctement déroulé. Les paquets USB se composent des champs suivants :

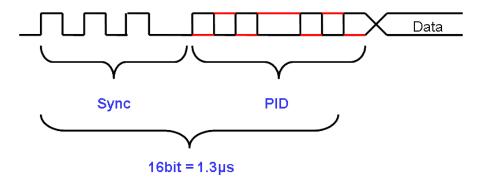

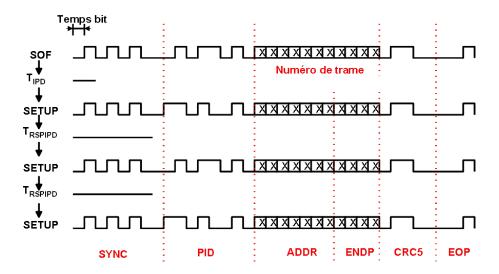

#### - SYNC

Tous les paquets doivent commencer avec un champ Sync, de 8 bits de long en Low-speed et full-speed Fig.2.7 ou 32 bits en High-speed. Il est utilisé pour synchroniser l'horloge du

récepteur avec celle de l'émetteur. Il est composé de trois transitions entre niveau Bas et Haut (KJ) et les 2 derniers bits (2K) indiquent l'endroit où le champ PID commence.

FIG. 2.7 – Champ SYNC

#### - PID

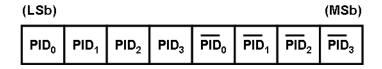

Composé de 4 bits, il est utilisé pour identifier le type de paquet qui est envoyé (TableA.3), ainsi que la direction du paquet de données, sachant que l'hôte est toujours pris comme repère pour les directions de communication. Pour s'assurer qu'il a été reçu correctement, les 4 bits sont complémentés, ce qui permettra de vérifier la validité de ce paquet. On obtient alors un PID de 8 bits au total Fig.2.8

FIG. 2.8 – Format des paquets PID

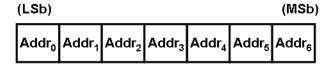

#### - ADDR

Composé de 7 bits de long, Fig.2.9, pour supporter 128 appareils, il détermine, par son adresse, la fonction qui émet ou reçoit les données. Par définition chaque adresse ne peut définir qu'une seule fonction

FIG. 2.9 – Champ d'adresse

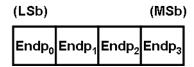

#### - ENDP

Le champ de terminaison composé de 4 bits, Fig.2.10, autorisant seize terminaisons possibles, il est ajouté pour rendre l'adressage des fonctions plus flexible.

FIG. 2.10 – Champ ENDP

#### - CRC

Les Contrôles à Redondance Cyclique sont exécutés sur les données à l'intérieur du paquet de charge utile. Ils servent à protéger l'intégrité de tous les champs, excepté les PID, dans les paquets de jetons et de données. Un mauvais champ CRC indique que l'un des champs du paquet est corrompu. Le système qui reçoit ce paquet sait alors qu'il doit l'ignorer.

- les paquets jetons ont un CRC de 5 bits

- les paquets de données ont un CRC de 16 bits

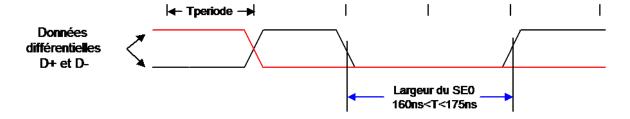

#### - EOP

Signalé par une sortie unique zéro (SE0), Fig. 2.11, pendant une durée de 2 bits suivie par un 'J' d'une durée de 1 bit, ce champ indique la fin d'un paquet.

FIG. 2.11 – EOP avec sa sortie unique à zéro

Jusqu'à présent, parmi tous les champs composant les différents paquets transmis entre un hôte et sa fonction raccordée, seule la partie de synchronisation, est déterministe. En effet c'est la seule que l'on retrouve au début de chaque paquet; quelque en soit sa nature :

JETON, DONNEE ou ETAT, et dont on peut prévoir la structure. De plus elle présente une densité de transition assurée, ce qui est un point important pour la récupération du signal d'horloge.

On retrouve ces champs dans les paquets de communication :

**JETON** (**TOKEN**) : *In* - Informe l'appareil USB que l'hôte veut lire des informations.

Out - : Informe l'appareil USB que l'hôte veut envoyer des informations.

Setup - Utilisé pour commencer les transferts de commande.

Les paquets de Jeton doivent se conformer au format suivant Fig.2.12 :

FIG. 2.12 – paquet de Jeton

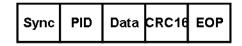

**DONNEES (DATA) :** Il y a 2 sortes de paquets de données :

- Data0

- Data1

La taille maximale de données 'charge utile 'est :

- De 8 octets pour les appareils Low-speed

- De 1023 octets pour les appareils Full-speed

- De 1024 octets pour les appareils High-speed

Les paquets de données doivent se conformer au format suivant Fig.2.13 :

FIG. 2.13 – Paquet de données

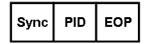

#### Paquet POIGNET DE MAIN (HANDSHAKE): Il y a 3 sortes de poignet de main:

- ACK - validant que le paquet a été reçu correctement

- NAK rapporte que temporairement l'appareil ne peut ni envoyer ou recevoir des données, il est aussi utilisé pendant les transactions d'interruptions pour avertir l'hôte qu'il n'a pas de donnée à envoyer.

- STALL (Bloqué) L'appareil se retrouve dans un état qui va exiger l'intervention de l'hôte.

Les paquets Poignet de main doivent se conformer au format suivant Fig.2.14

FIG. 2.14 – Paquet poignet de main

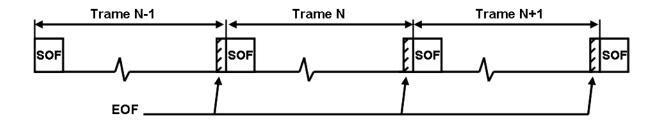

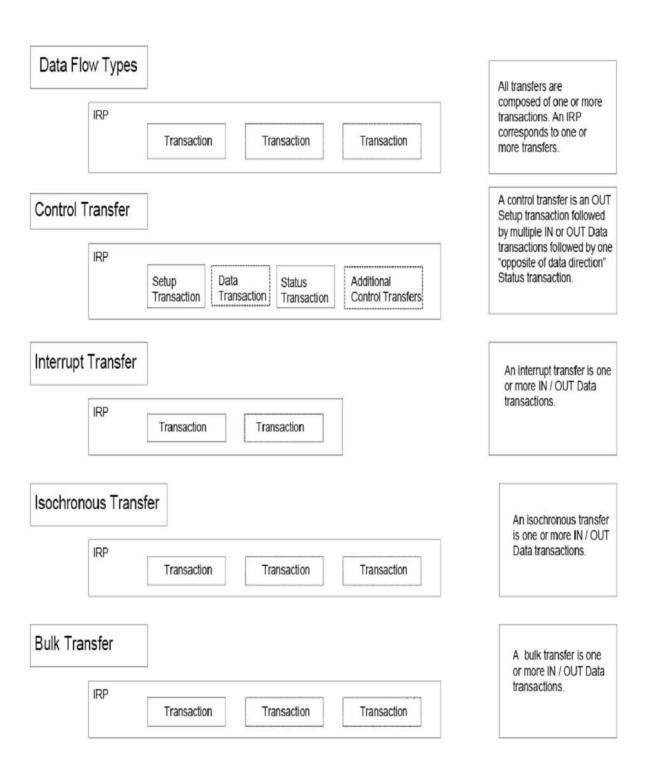

La norme USB définit une base temporelle, appelée trame (frame en anglais) d'une milliseconde plus ou moins 500ns pour les modes Full-speed et Low-speed et de 125us plus ou moins 65ns pour le High-speed. Une trame peut contenir plusieurs transactions entre l'hôte et la fonction qui lui est attachée. Cinq types de transactions sont possibles :

- Transfert de DONNEES

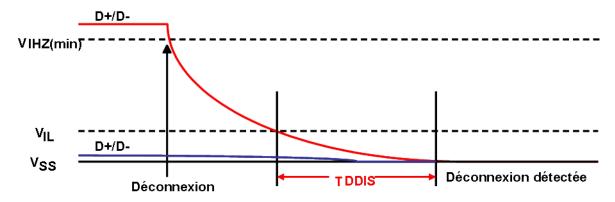

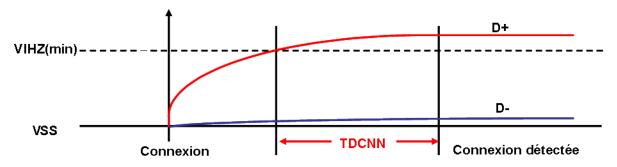

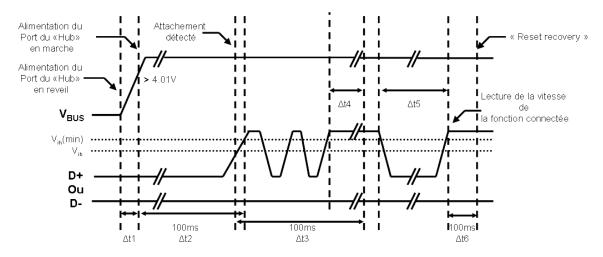

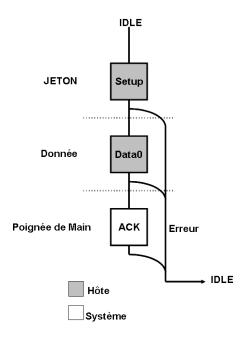

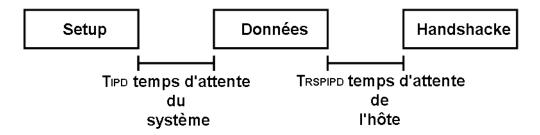

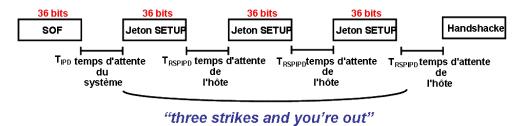

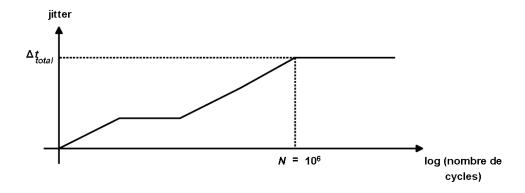

- Transfert de CONTROLE