# ANALYSE DU COMPORTEMENT PETIT SIGNAL DU TRANSISTOR MOS :

# CONTRIBUTION A UNE NOUVELLE APPROCHE D'EXTRACTION ET DE MODELISATION POUR DES APPLICATIONS RF

#### E. BOUHANA

STMICROELECTRONICS, 850 RUE J. MONNET, 38926 CROLLES CEDEX, FRANCE IEMN, AVENUE POINCARÉ, BP 69, 59652 VILLENEUVE D'ASCQ CEDEX, FRANCE

# ANALYSE DU COMPORTEMENT PETIT SIGNAL DU TRANSISTOR MOS:

# CONTRIBUTION A UNE NOUVELLE APPROCHE D'EXTRACTION ET DE MODELISATION POUR DES APPLICATIONS RF

#### F. BOUHANA

STMICROELECTRONICS, 850 RUE J. MONNET, 38926 CROLLES CEDEX, FRANCE IEMN, AVENUE POINCARÉ, BP 69, 59652 VILLENEUVE D'ASCQ CEDEX, FRANCE

# TROIS ELEMENTS IMPORTANTS

#### ☐ Transistor MOS:

OComposant à semiconducteur massivement utilisé dans l'industrie microélectronique

#### TROIS ELEMENTS IMPORTANTS

- ☐ Transistor MOS:

- OComposant à semiconducteur massivement utilisé dans l'industrie microélectronique

- Modélisation

- OConsiste à faire des modèles

- O Reproduction & prédiction du comportement électrique d'un composant

- OEssentiel pour la conception de circuits

#### TROIS ELEMENTS IMPORTANTS

- ☐ Transistor MOS :

- OComposant à semiconducteur massivement utilisé dans l'industrie microélectronique

- Modélisation

- OConsiste à faire des modèles

- Reproduction & prédiction du comportement électrique d'un composant

- OEssentiel pour la conception de circuits

- □ Applications RF

- ○GPS, GSM, Bluetooth, Wifi, Wimax

- OFréquence : 1-10GHz

$\square$  RF  $\Leftrightarrow$  Bip & III-V

□ RF ⇔ Bip & III-V

☐ Mais:

○ Réduction des dimensions en technologie MOS : augmentation de la rapidité des transistors

|                        | 1995    |         |         |         |       |         | 2007  |

|------------------------|---------|---------|---------|---------|-------|---------|-------|

| Nœud technologique     | 0.35 μm | 0.25 μm | 0.18 μm | 0.13 μm | 90 nm | 65 nm   | 45 nm |

| F <sub>t</sub> (GHz)   | 25      | 35      | 50      | 85      | 120   | 165-200 | > 250 |

| F <sub>max</sub> (GHz) | ~ 40    | ~ 60    | ~ 80    | > 120   | > 200 | > 300   | > 400 |

□ RF ⇔ Bip & III-V

☐ Mais:

O Réduction des dimensions en technologie MOS : augmentation de la rapidité des transistors

|                        | 1995    |         |         |         |       |         | 2007  |

|------------------------|---------|---------|---------|---------|-------|---------|-------|

| Nœud technologique     | 0.35 μm | 0.25 μm | 0.18 μm | 0.13 μm | 90 nm | 65 nm   | 45 nm |

| F <sub>t</sub> (GHz)   | 25      | 35      | 50      | 85      | 120   | 165-200 | > 250 |

| F <sub>max</sub> (GHz) | ~ 40    | ~ 60    | ~ 80    | > 120   | > 200 | > 300   | > 400 |

O Avantages: Prix, consommation & intégration avec des fonctions numériques

- $\square$  RF  $\Leftrightarrow$  Bip & III-V

- ☐ Mais:

- ORéduction des dimensions en technologie MOS : augmentation de la rapidité des transistors

|                        | 1995 — 20 |         |         |         |       |         | <b>2</b> 007 |

|------------------------|-----------|---------|---------|---------|-------|---------|--------------|

| Nœud technologique     | 0.35 μm   | 0.25 μm | 0.18 μm | 0.13 μm | 90 nm | 65 nm   | 45 nm        |

| F <sub>t</sub> (GHz)   | 25        | 35      | 50      | 85      | 120   | 165-200 | > 250        |

| F <sub>max</sub> (GHz) | ~ 40      | ~ 60    | ~ 80    | > 120   | > 200 | > 300   | > 400        |

- O Avantages : Prix, consommation & intégration avec des fonctions numériques

- □ De plus en plus d'applications analogiques & RF sont conçues en technologie MOS

- ☐ Mais : les modèles disponibles ont des lacunes.

- OBesoin d'améliorer la modélisation RF du transistor MOS

- ☐ Mais : les modèles disponibles ont des lacunes.

- OBesoin d'améliorer la modélisation RF du transistor MOS

- ☐ Ces travaux de thèse :

- O Nouvelles approches pour la modélisation linéaire du MOS

- ➤ Applications : 1<f<10GHz

- > Validation des modèles : domaine millimétrique

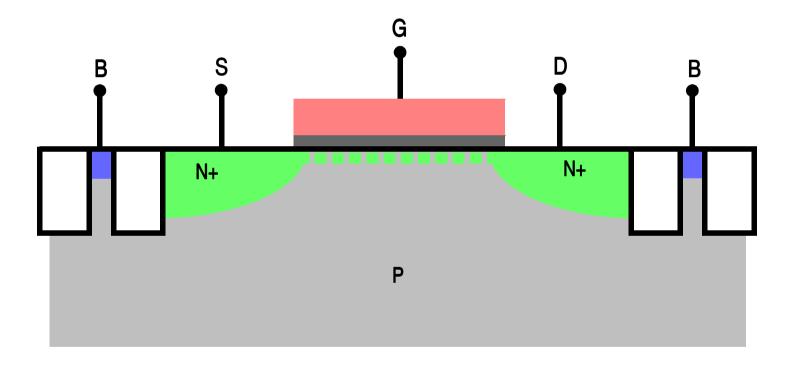

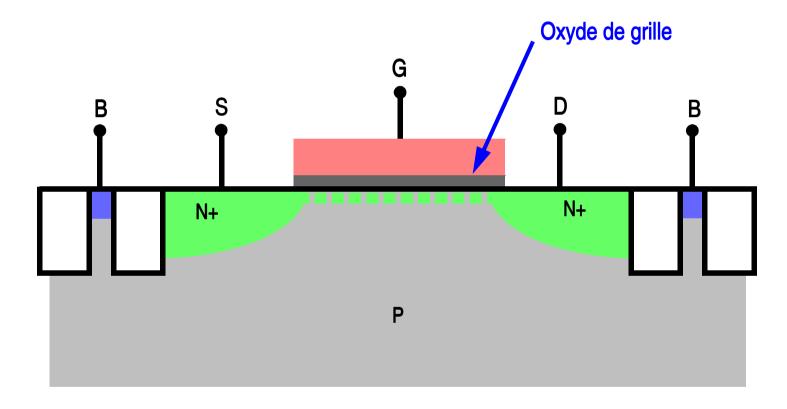

#### Introduction

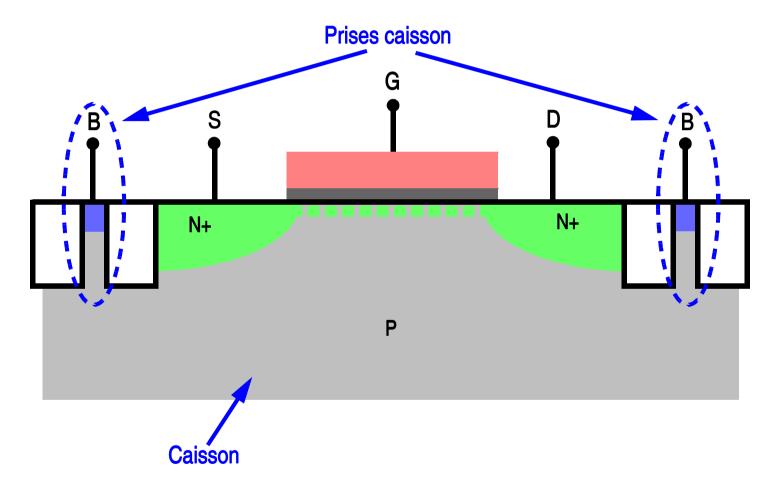

- O Description succincte du MOSFET

- O Problématique de la modélisation en RF

Introduction

Etude des éléments extrinsèques "connus"

- O Capacités parasites

- O Résistance de grille

- O Impact et évolution

Introduction

Etude des éléments extrinsèques "connus"

#### Etude du réseau substrat

- O Particularités

- O Méthodologie d'accès au réseau substrat

- O Analyse du réseau en technologies 130nm et 65nm

Introduction

Etude des éléments extrinsèques "connus"

Etude du réseau substrat

Conclusion & perspectives

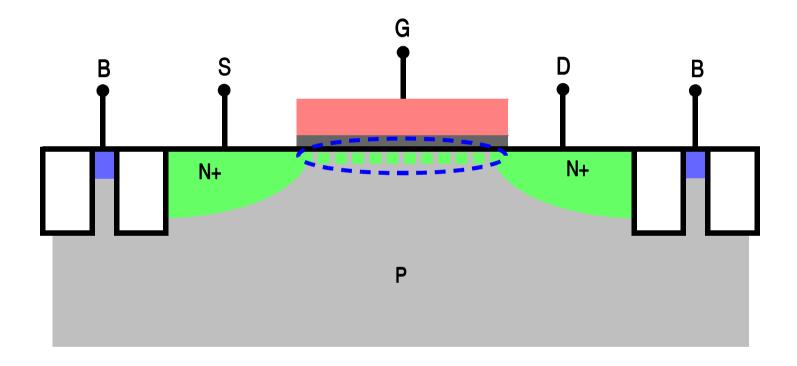

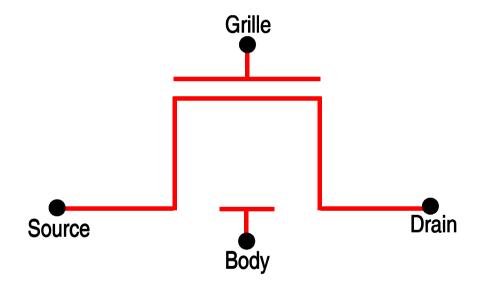

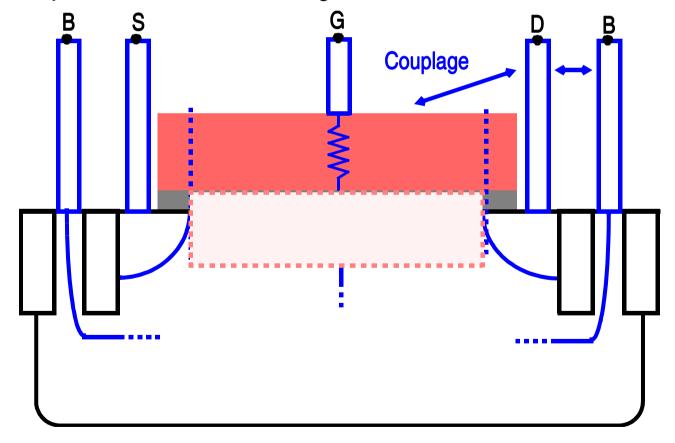

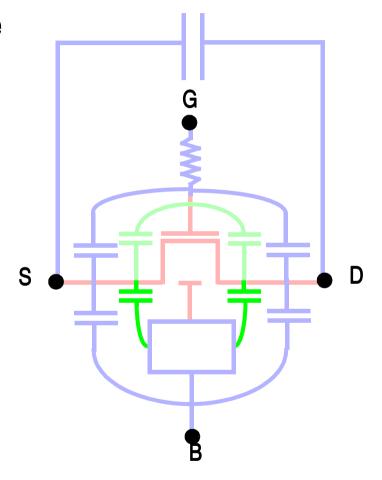

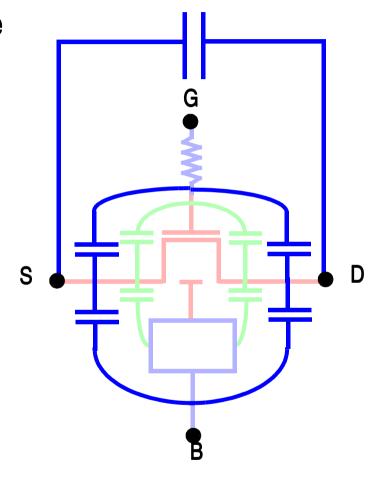

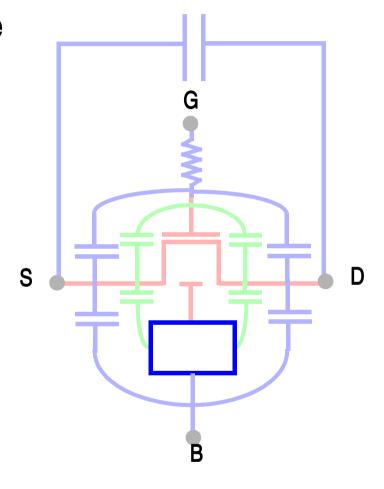

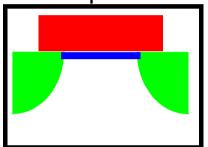

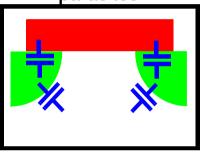

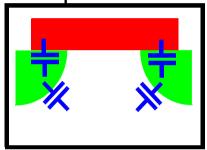

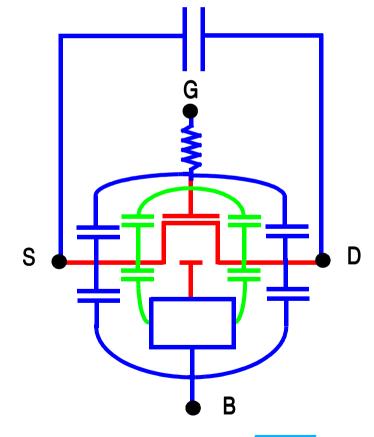

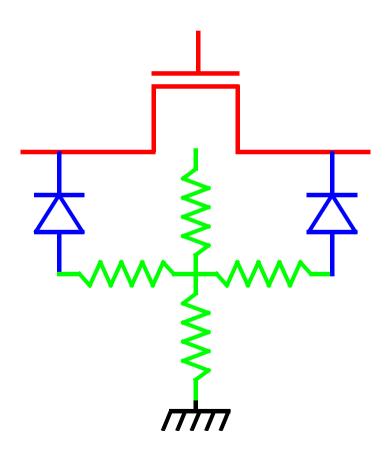

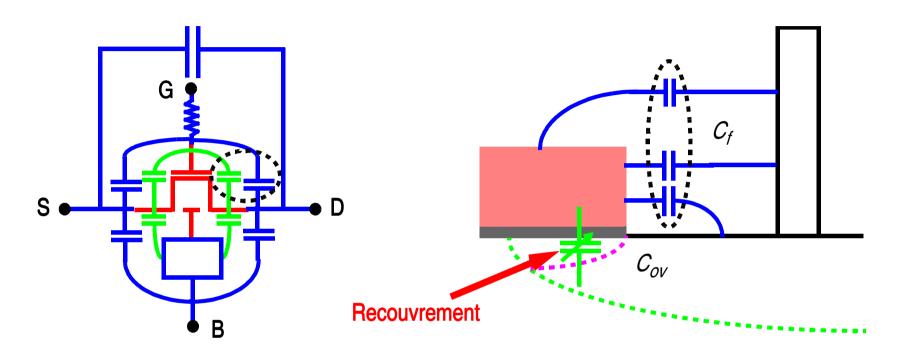

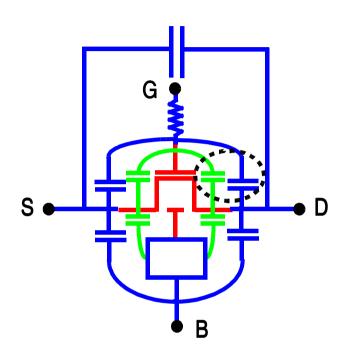

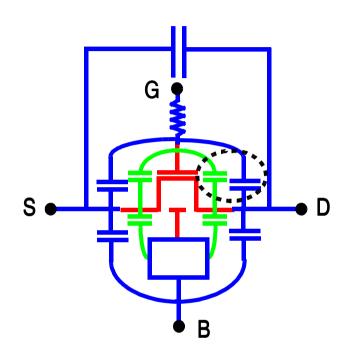

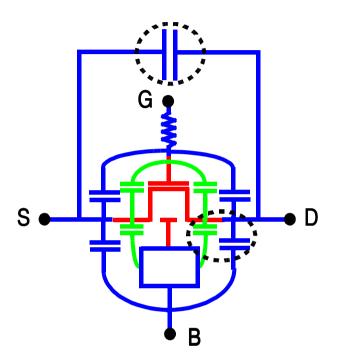

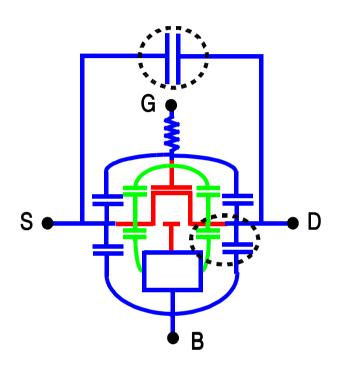

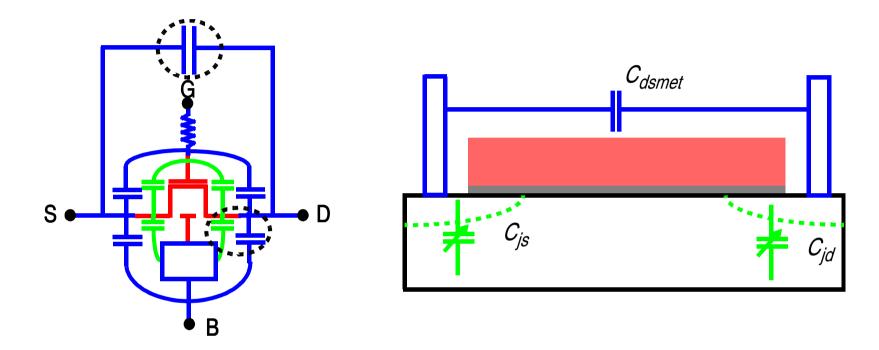

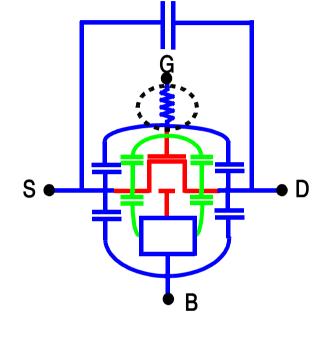

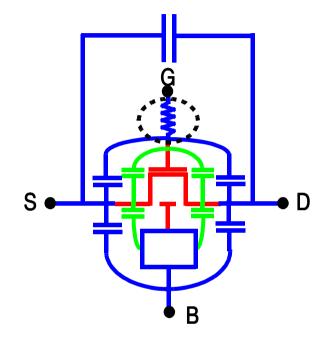

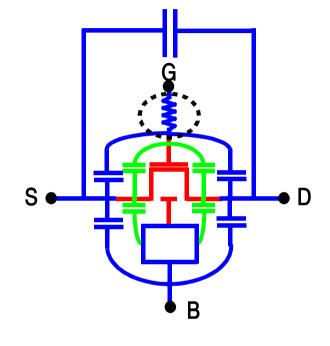

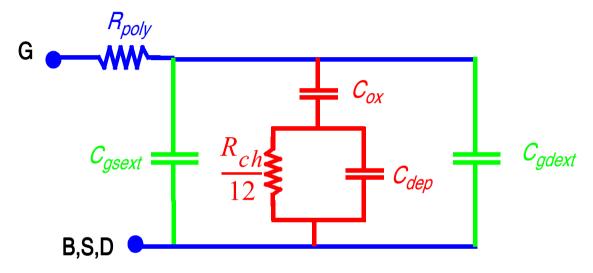

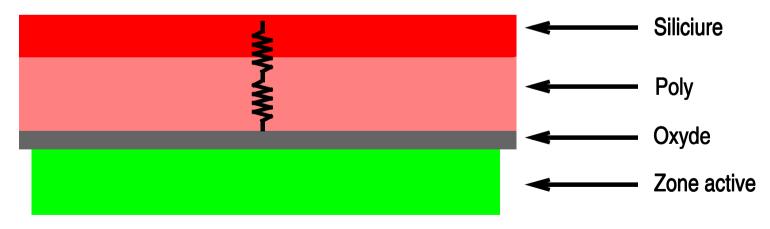

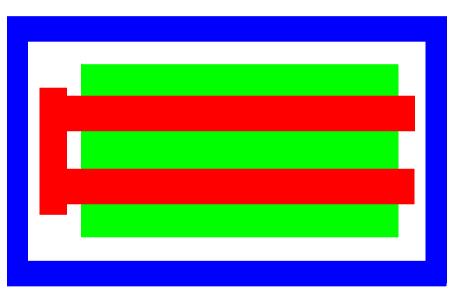

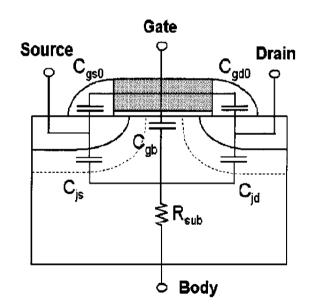

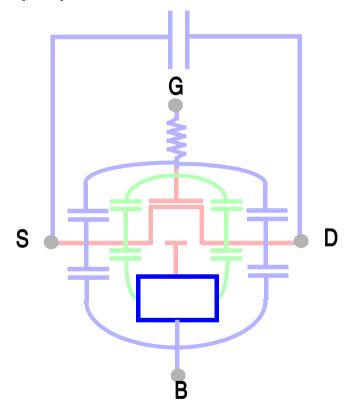

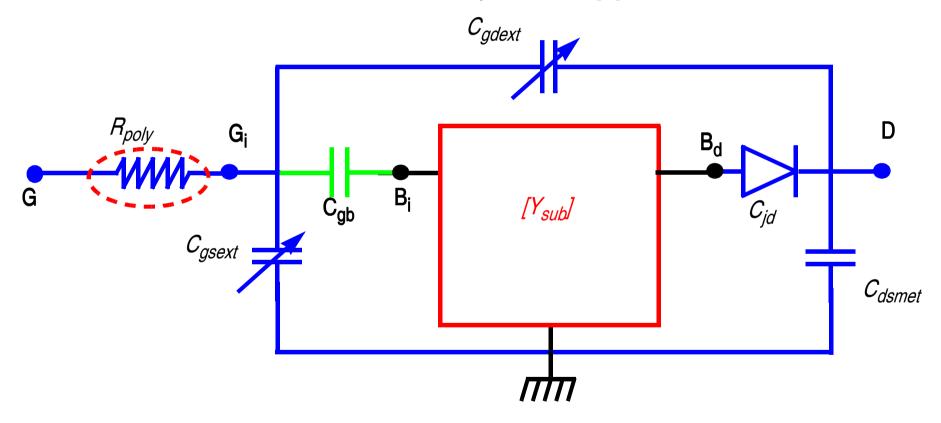

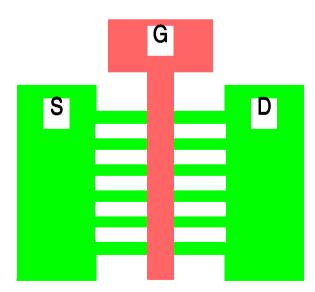

☐ Intrinsèque ⇔ effet transistor

- ☐ Intrinsèque ⇔ effet transistor

- ☐ Extrinsèque ⇔ lié à la technologie et à l'accès aux terminaux du transistor

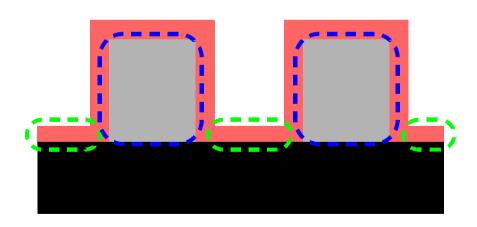

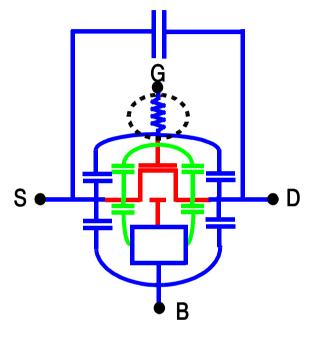

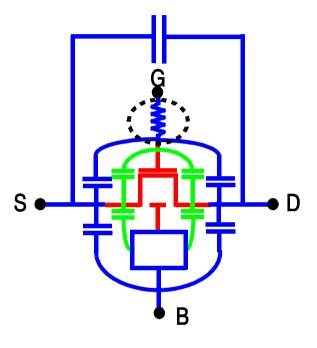

- ☐ Intrinsèque ⇔ effet transistor

- ☐ Extrinsèque ⇔ lié à la technologie et à l'accès aux terminaux du transistor

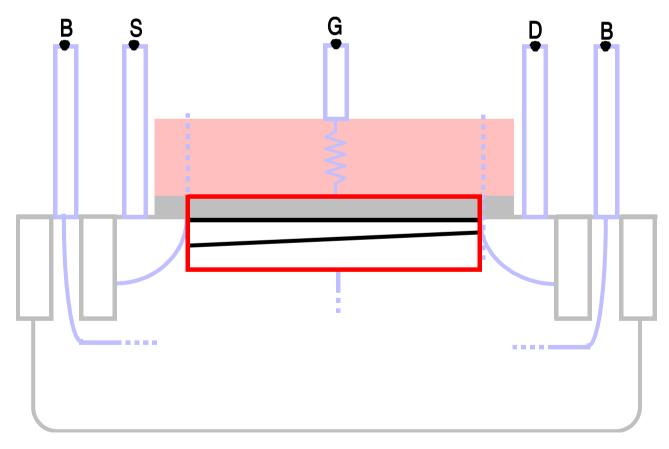

- ☐ Les éléments extrinsèques entourent le dispositif

- OChemins non-idéaux pour le signal

- OInfluence en RF

- ☐ Les éléments extrinsèques entourent le dispositif

- OChemins non-idéaux pour le signal

- OInfluence en RF

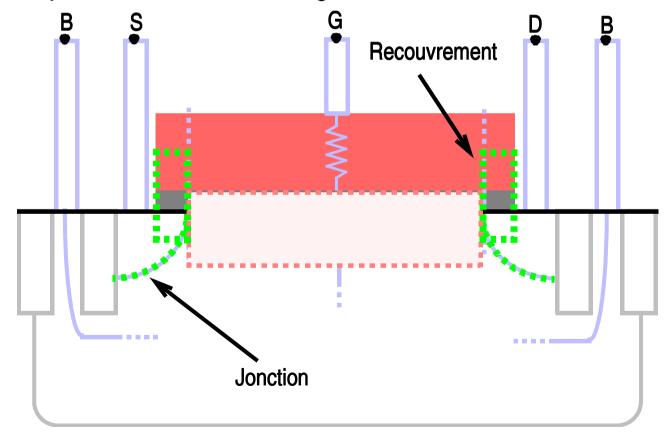

- ☐ Eléments parasites

- ORésistance de grille ;

- ☐ Les éléments extrinsèques entourent le dispositif

- OChemins non-idéaux pour le signal

- OInfluence en RF

- ☐ Eléments parasites

- O Résistance de grille ;

- OCapacités de recouvrement;

- ☐ Les éléments extrinsèques entourent le dispositif

- OChemins non-idéaux pour le signal

- OInfluence en RF

- ☐ Eléments parasites

- O Résistance de grille ;

- OCapacités de recouvrement;

- OCapacités de jonction;

- ☐ Les éléments extrinsèques entourent le dispositif

- OChemins non-idéaux pour le signal

- OInfluence en RF

- ☐ Eléments parasites

- O Résistance de grille ;

- OCapacités de recouvrement;

- OCapacités de jonction;

- OCapacités métalliques ;

- ☐ Les éléments extrinsèques entourent le dispositif

- OChemins non-idéaux pour le signal

- OInfluence en RF

- ☐ Eléments parasites

- O Résistance de grille ;

- OCapacités de recouvrement;

- OCapacités de jonction;

- OCapacités métalliques ;

- O Réseau substrat.

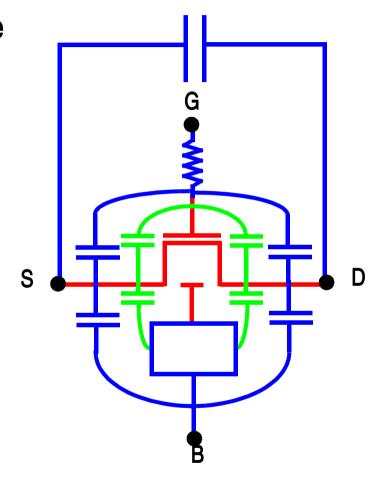

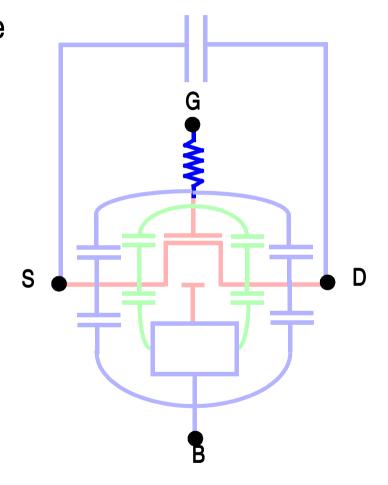

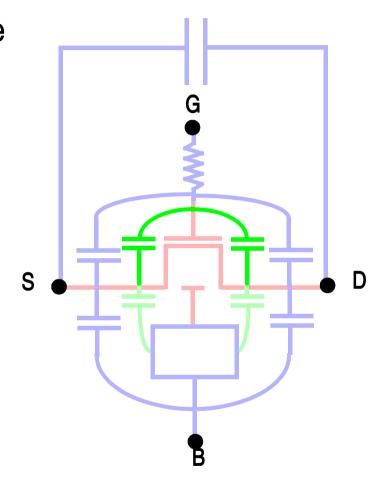

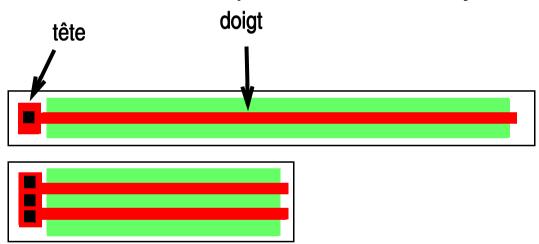

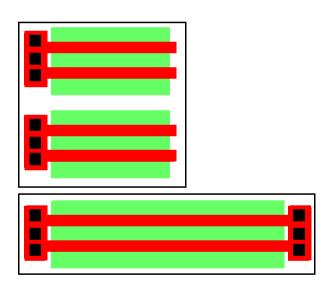

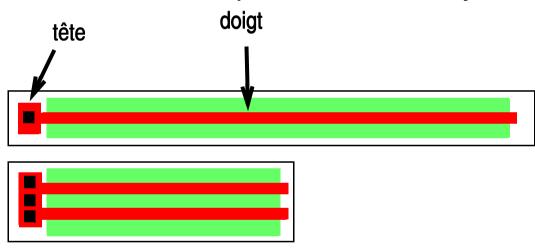

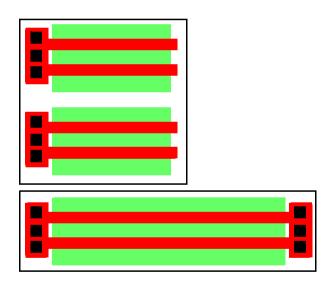

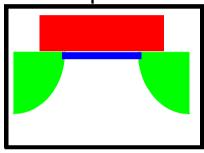

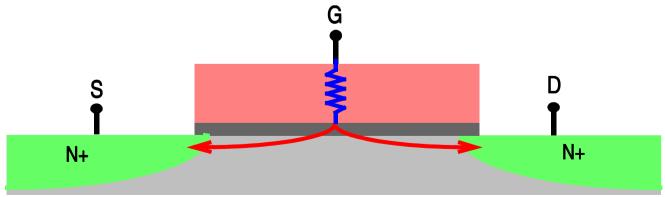

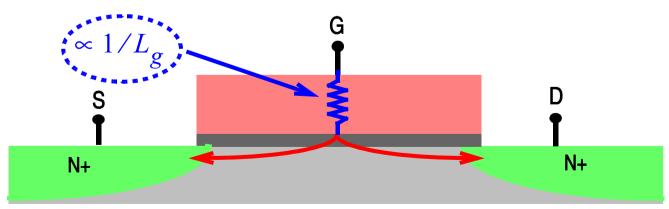

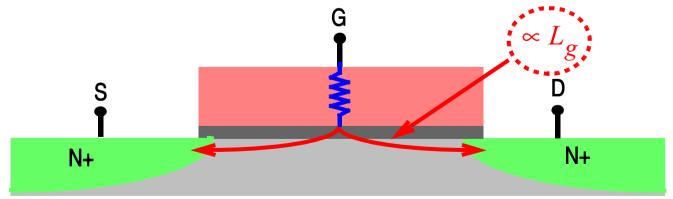

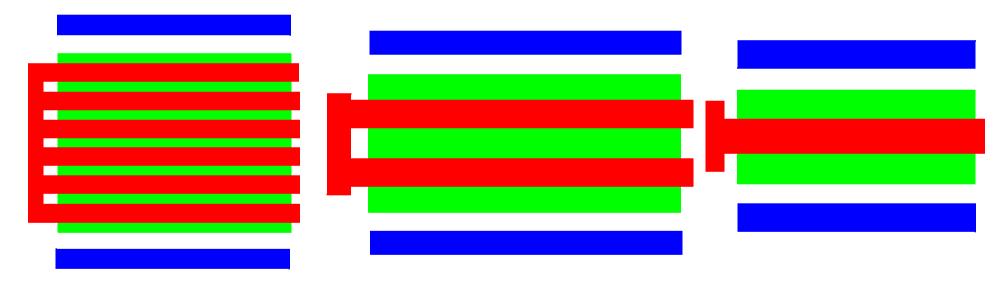

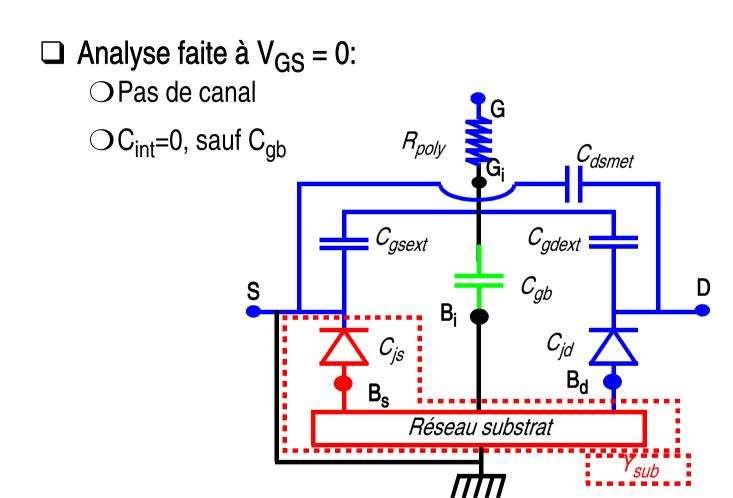

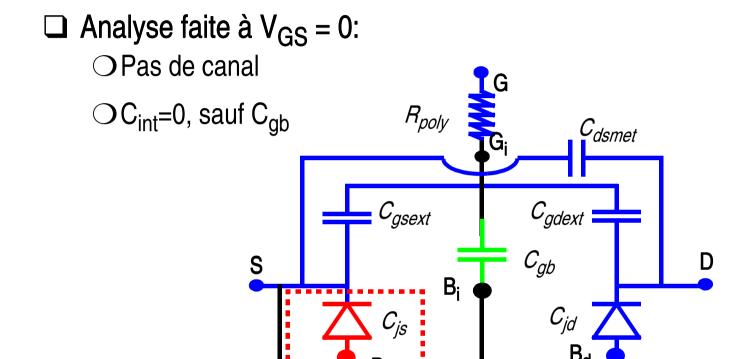

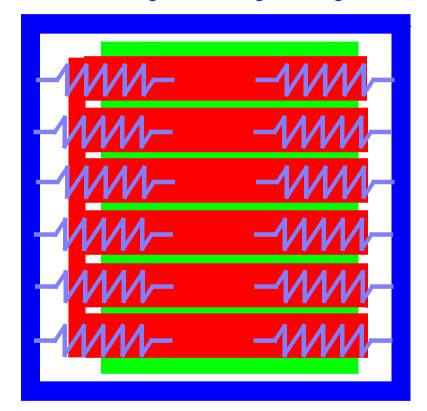

$\square$  Partie intrinsèque  $\Leftrightarrow$  (W,L)

- $\square$  Partie intrinsèque  $\Leftrightarrow$  (W,L)

- ☐ Partie extrinsèque : influence du layout

- $\square$  Partie intrinsèque  $\Leftrightarrow$  (W,L)

- ☐ Partie extrinsèque : influence du layout

- O Influence sur la résistance de grille

- OInfluence sur le réseau substrat

- OInfluence sur les couplages entre les contacts

# MODELISATION DU TRANSISTOR MOS

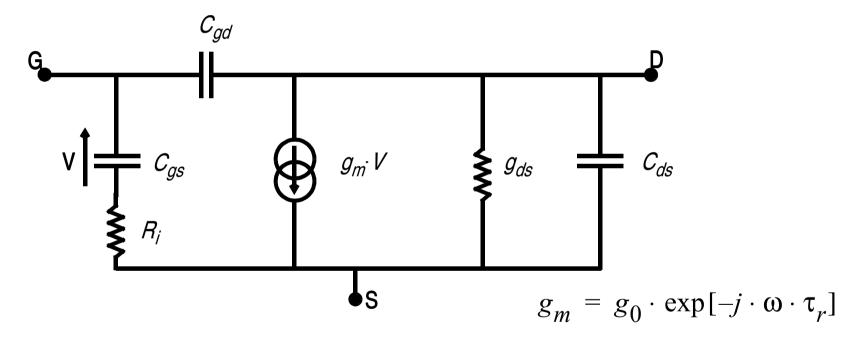

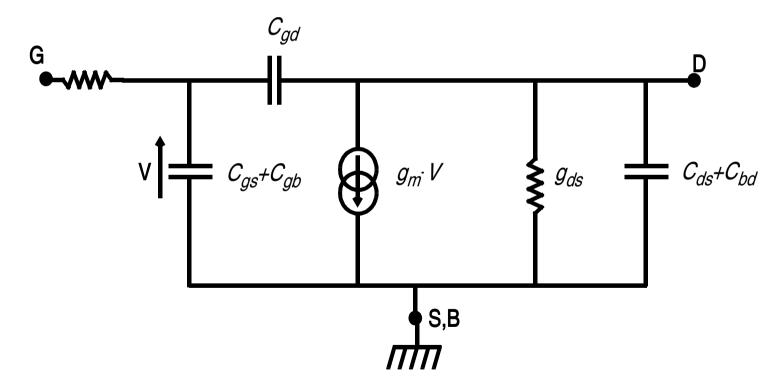

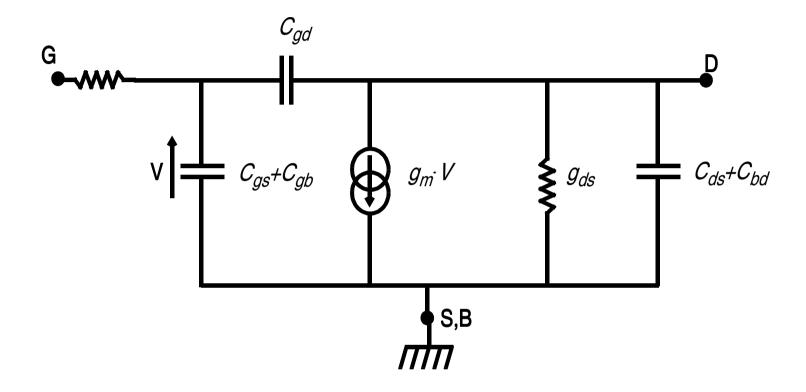

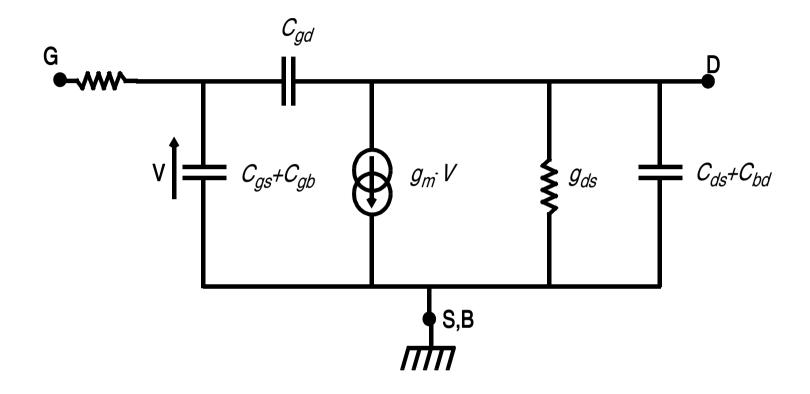

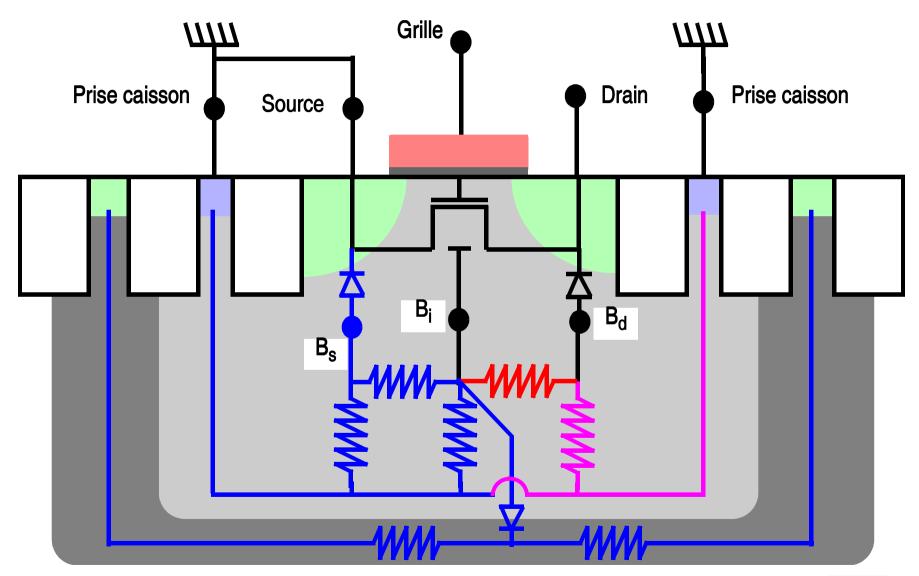

#### MODELISATION RF DU FET

- ☐ Modèle "historique" : schéma équivalent petit signal

- OTransistor à Effet de Champ en source commune

#### MODELISATION DU MOSFET DANS L'INDUSTRIE

- ☐ Plusieurs familles de composants (compromis vitesse/consommation)

- Applications numériques

- Applications embarquées

- Applications analogiques/RF

## MODELISATION DU MOSFET DANS L'INDUSTRIE

| Plusieurs familles de composants (compromis vitesse/consommatio  |

|------------------------------------------------------------------|

| O Applications numériques                                        |

| O Applications embarquées                                        |

| OApplications analogiques/RF                                     |

| Différentes utilisations ⇒ différents domaines de fonctionnement |

| OCircuits analogiques/RF: LNA, VCO, mélangeur,                   |

| OCircuits numériques                                             |

# MODELISATION DU MOSFET DANS L'INDUSTRIE

| Plusieurs familles de composants (compromis vitesse/consommatio                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| OApplications numériques                                                                                                                  |

| O Applications embarquées                                                                                                                 |

| OApplications analogiques/RF                                                                                                              |

| Différentes utilisations ⇒ différents domaines de fonctionnement  ○ Circuits analogiques/RF : LNA, VCO, mélangeur,  ○ Circuits numériques |

| Différentes géométries possibles                                                                                                          |

# MODELISATION DU MOSFET DANS L'INDUSTRIE

| Plusieurs familles de composants (compromis vitesse/consommation                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| O Applications numériques                                                                                                                 |

| O Applications embarquées                                                                                                                 |

| OApplications analogiques/RF                                                                                                              |

| Différentes utilisations ⇒ différents domaines de fonctionnement  O Circuits analogiques/RF : LNA, VCO, mélangeur,  O Circuits numériques |

| Différentes géométries possibles                                                                                                          |

| → Besoin d'un modèle complet et prédictif                                                                                                 |

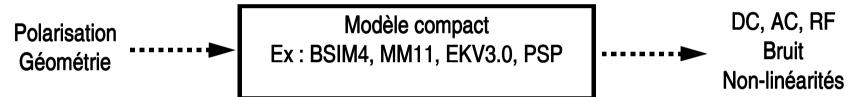

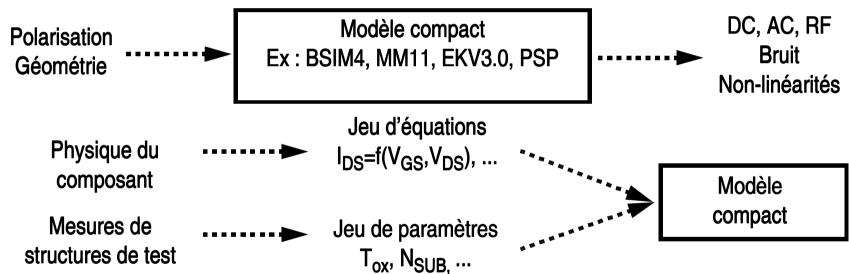

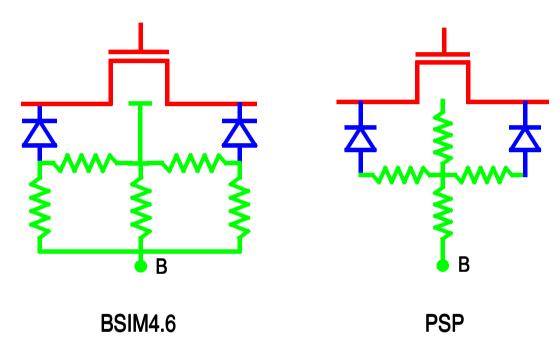

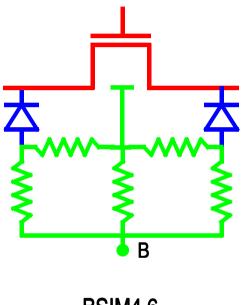

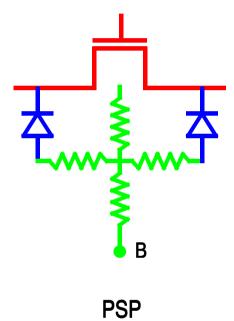

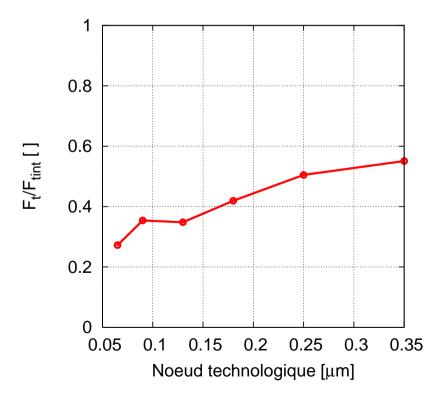

☐ Structure du modèle compact

☐ Structure du modèle compact

#### ☐ Evolution des modèles :

Description "canal long" du dispositif

Prise en compte des effets canaux courts

Prise en compte des éléments parasites

☐ Evolution des modèles :

Description "canal long" du dispositif

Prise en compte des effets canaux courts

Prise en compte des éléments parasites

- ☐ Aujourd'hui:

- ○BSIM4.6 (Berkeley)

- ○EKV3.0 (EPFL)

- OPSP102.1 (Philips/PSU puis NXP/ASU)

☐ Partie intrinsèque :

OThéorie du MOSFET idéal

Tsividis, "Operation and Modeling of the MOS Transistor", Oxford University Press, 1999.

- ☐ Partie intrinsèque :

- OThéorie du MOSFET idéal

Tsividis, "Operation and Modeling of the MOS Transistor", Oxford University Press, 1999.

- ☐ Partie extrinsèque :

- Sous-circuits R-C autour de la partie intrinsèque

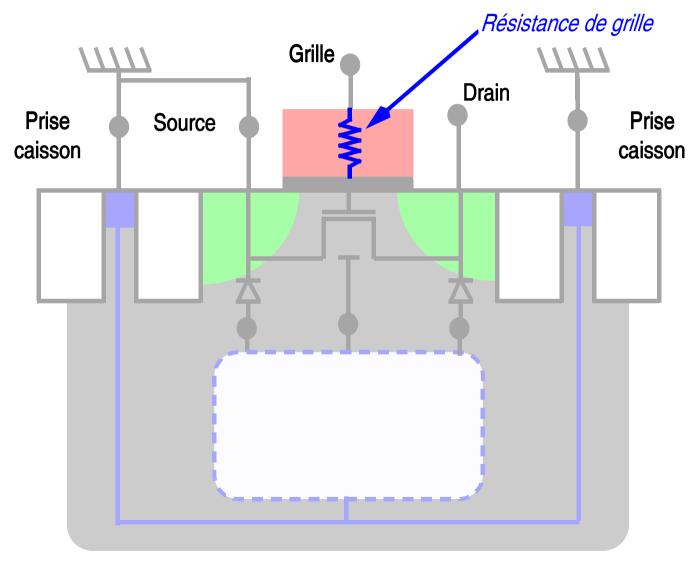

# EFFET DE LA RESISTANCE DE GRILLE

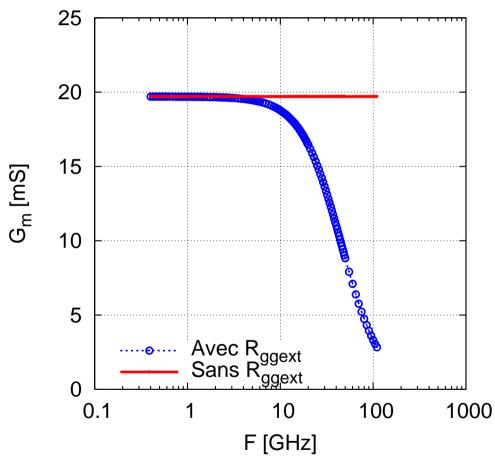

### EFFET DE LA RESISTANCE DE GRILLE

#### ☐ Transconductance de grille ⇒ Fréquence de coupure

nMOSFET, techno 130nm,  $V_{GS}=V_{DS}=1.2V$ ,  $L_g=1.0\mu m$ ;  $N_c\times N_f\times W_f=4\times 2\times 10\mu m$

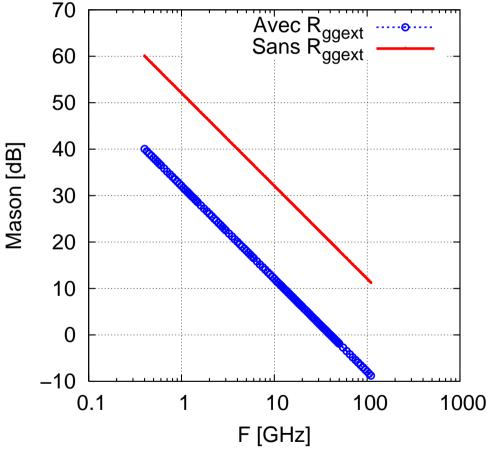

## EFFET DE LA RESISTANCE DE GRILLE

#### ☐ Limitation du gain en puissance du transistor

nMOSFET, techno 130nm,  $V_{GS} = V_{DS} = 1.2V$ ,  $L_q = 1.0 \mu m$ ;  $N_c \times N_f \times W_f = 4 \times 2 \times 10 \mu m$

# LA RESISTANCE DE GRILLE DANS LES MODELES COMPACTS

- □ BSIM4.6

- OUn élément localisé

- OLoi géométrique mais incomplète

### LA RESISTANCE DE GRILLE DANS LES MODELES COMPACTS

- □ BSIM4.6

- OUn élément localisé

- OLoi géométrique mais incomplète

- □ EKV3.0

- OUn élément localisé

- OPas de loi géométrique

- □ PSP102.1

- OUn élément localisé

- OPas de loi géométrique

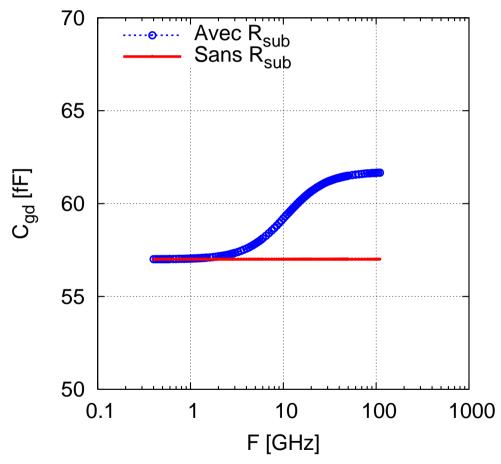

### **EFFETS DU SUBSTRAT**

### **EFFETS DU SUBSTRAT**

#### ☐ Effet sur la capacité de contre-réaction

nMOSFET, techno 130nm,  $V_{GS}=V_{DS}=1.2V$ ,  $L_g=1.0\mu m$ ;  $N_c\times N_f\times W_f=4\times 2\times 10\mu m$

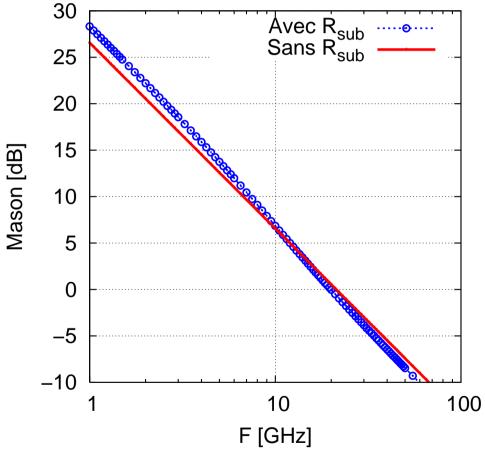

### **EFFETS DU SUBSTRAT**

#### ☐ Effet sur le gain de Mason

nMOSFET, techno 130nm,  $V_{GS} = V_{DS} = 1.2V$ ,  $L_g = 1.0 \mu m$ ;  $N_c \times N_f \times W_f = 4 \times 2 \times 10 \mu m$

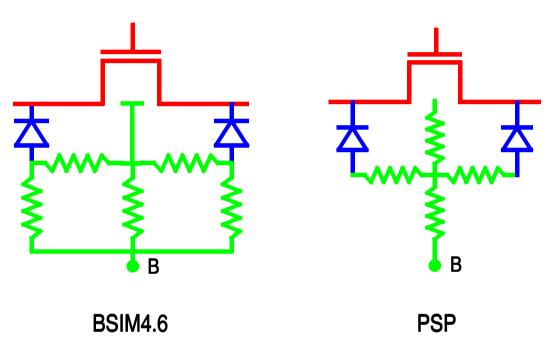

#### LES EFFETS SUBSTRAT DANS LES MODELES COMPACTS

- □ BSIM4.6

- O Réseau de résistances

- OLois géométriques avec une base empirique

#### LES EFFETS SUBSTRAT DANS LES MODELES COMPACTS

□ BSIM4.6

□ EKV3.0

O Sous-circuit externe défini par l'utilisateur

#### LES EFFETS SUBSTRAT DANS LES MODELES COMPACTS

- □ BSIM4.6

- □ EKV3.0

- □ PSP102.1

- O Réseau de résistances

- O Pas de lois géométriques

#### BILAN:

#### LA PARTIE EXTRINSEQUE ET LES MODELES COMPACTS

- ☐ Prise en compte par les modèles compacts : insuffisante

- O Résistance de grille : modèles incomplets

- ORéseau substrat : modèles existants, mais...

#### BILAN:

#### LA PARTIE EXTRINSEQUE ET LES MODELES COMPACTS

- ☐ Prise en compte par les modèles compacts : insuffisante

- O Résistance de grille : modèles incomplets

- ORéseau substrat : modèles existants, mais...

- $\Rightarrow$  Dans la suite :

- ☐ Extraction & modélisation de la partie extrinsèque

- □ Approche : Mesure ⇒ épluchage du MOSFET

#### PLAN

Introduction

Etude des éléments extrinsèques "connus"

Etude du réseau substrat

Conclusion & perspectives

# EXTRACTION DES ELEMENTS PARASITES "CONNUS"

- □ Pourquoi "connus" ?

- OEffets du premier ordre sur les performances RF du MOSFET

- O Effets modélisés avec un élément localisé

- OLois géométriques simples

# EXTRACTION DES ELEMENTS PARASITES "CONNUS"

- □ Pourquoi "connus" ?

- OEffets du premier ordre sur les performances RF du MOSFET

- O Effets modélisés avec un élément localisé

- OLois géométriques simples

- ☐ Intérêt :

- OVoir les effets de ces éléments

- 1ère étape vers le substrat

### PRINCIPE DE L'EXTRACTION DES PARASITES

- ☐ On dispose :

- Ode mesures 2 ports  $(G,D) \Rightarrow$  paramètres [Y] mesurés ;

- Od'un schéma équivalent simplifié ⇒ paramètres [Y] = expressions analytiques

# PRINCIPE DE L'EXTRACTION DES PARASITES

☐ On "lit" la mesure ⇒ identification des éléments du schéma équivalent

### PRINCIPE DE L'EXTRACTION DES PARASITES

- ☐ On "lit" la mesure ⇒ identification des éléments du schéma équivalent

- O Impossible de mesurer séparément les différentes parties du MOS

- ⇒ Analyse basée sur une connaissance du comportement intrinsèque.

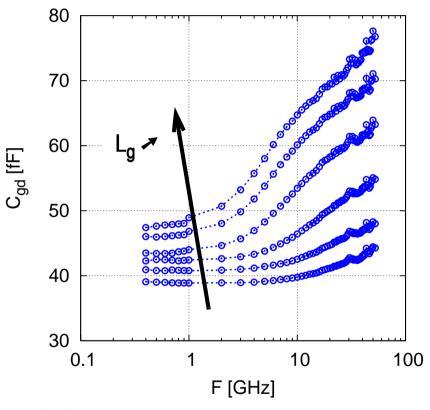

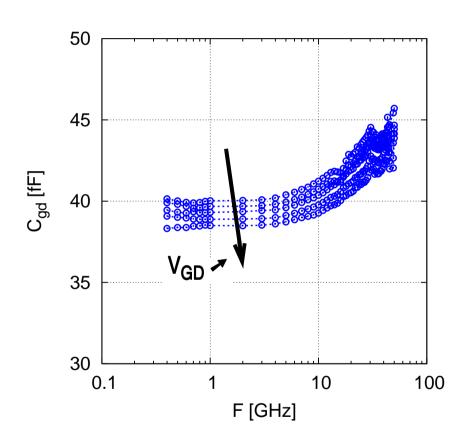

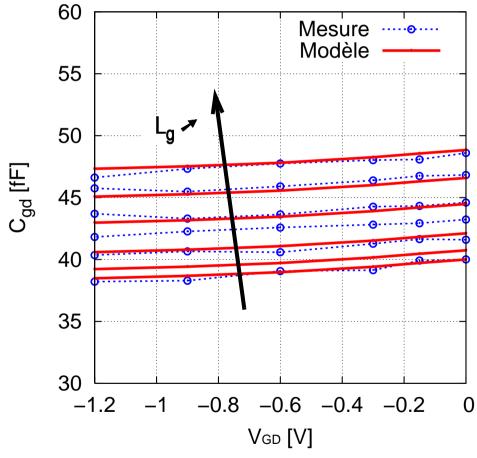

# Extraction de $C_{\text{GD}}$ parasite

# Extraction de $C_{\mathsf{GD}}$ parasite

# Extraction de $C_{GD}$ parasite

- $\square$  Extraction :  $(Im[(Y_{12})^{-1}])^{-1}/\omega$

- $\bigcirc$  V<sub>GS</sub>=0  $\Longrightarrow$  C<sub>gdint</sub>=0

- $\bigcirc$  V<sub>GD</sub> variable  $\Rightarrow$  dépendance en polarisation

- $\bigcirc$ BF  $\Rightarrow$  on évite les effets de couplage par le substrat.

# Extraction de $C_{\text{GD}}$ parasite

#### ■ Mesures

#### Technologie 65nm

- $\begin{array}{ll} \bullet & L_g: 65 nm \rightarrow 2.0 \mu m, \ V_{GS} = 0, \ V_{DS} = 0.6 V \\ \bullet & V_{DS}: -1.2 V \rightarrow 0 V, \ V_{GS} = 0, \ L_g \ nominal \end{array}$

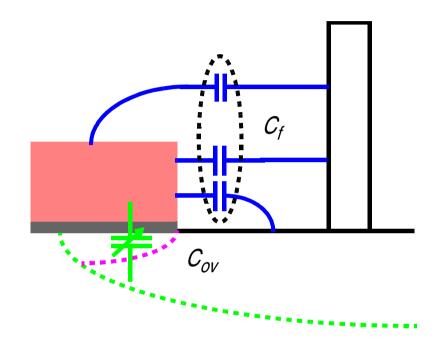

# Modelisation de $C_{\text{GD}}$ parasite : $C_{\text{GDEXT}}$

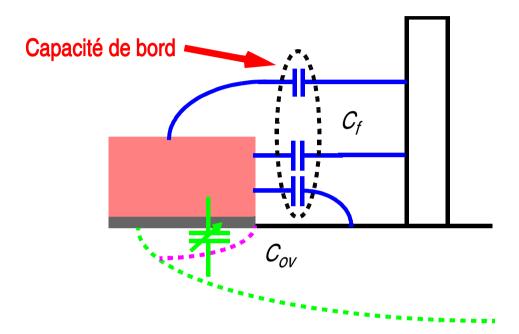

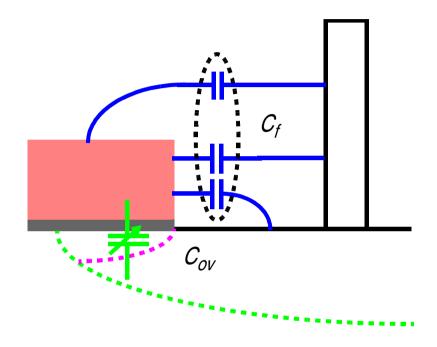

- ☐ Modélisation : C<sub>gdext</sub>=C<sub>ov</sub>+C<sub>f</sub>

- $\bigcirc C_{ov} = f(V_{GD}) \Rightarrow Modèle de BSIM4.6$ ;

- $\bigcirc C_f = f(L_g)$

- ○C<sub>gsext</sub> : même modèle, mêmes paramètres (dispositif symétrique)

# Modelisation de $C_{\text{GD}}$ parasite : $C_{\text{GDEXT}}$

#### ■ Validation du modèle

Technologie 65nm,  $L_g$ : 65nm  $\rightarrow$  2.0 $\mu$ m,  $V_{GS}$ =0

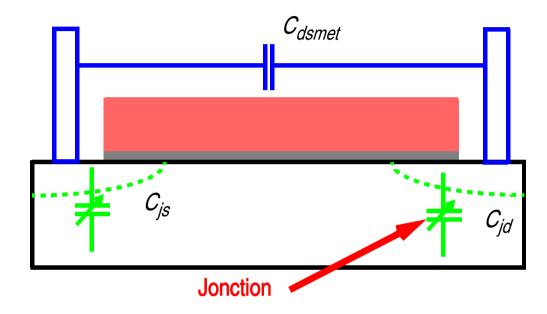

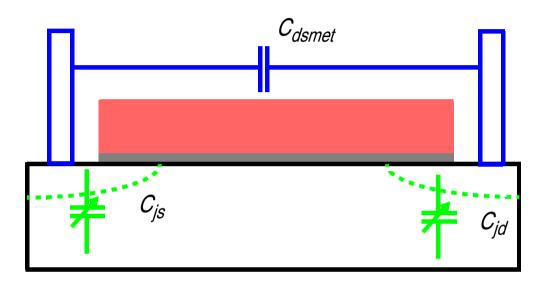

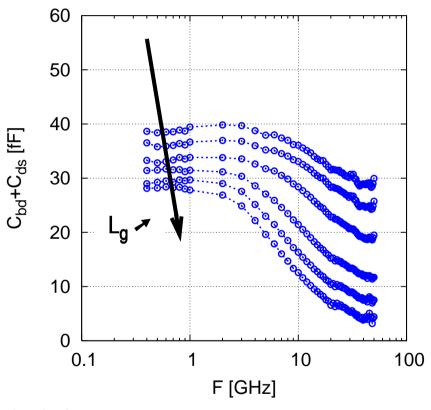

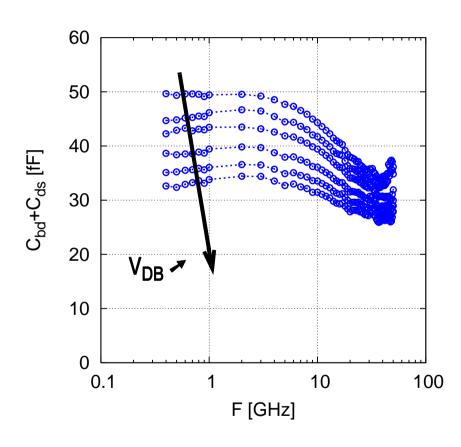

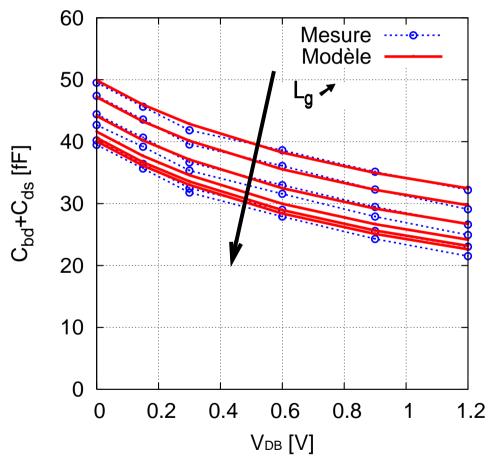

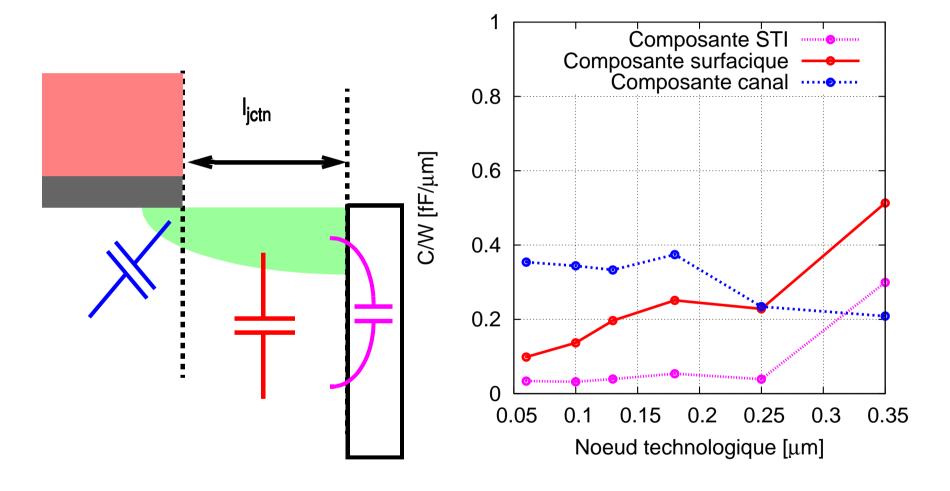

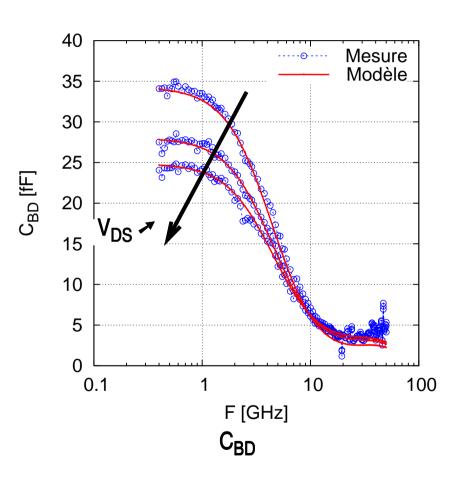

# EXTRACTION DE $C_{BD}+C_{DS}$ PARASITE

# Extraction de $C_{\text{BD}} + C_{\text{DS}}$ parasite

# EXTRACTION DE $C_{BD}+C_{DS}$ PARASITE

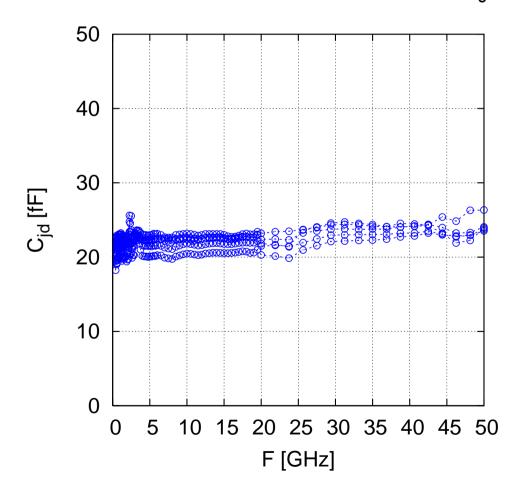

- $\square$  Extraction :  $Im[Y_{22} + Y_{12}]/\omega$

- $\bigcirc$  V<sub>GS</sub>=0  $\Rightarrow$  C<sub>bdint</sub>=0

- $\bigcirc$  V<sub>DB</sub> variable  $\Rightarrow$  dépendance en polarisation

- $\bigcirc$ BF  $\Rightarrow$  on évite l'influence du substrat.

# EXTRACTION DE C<sub>BD</sub>+C<sub>DS</sub> PARASITE

#### ■ Mesures

#### Technologie 65nm

•  $L_g$ : 65nm  $\rightarrow$  2.0 $\mu$ m,  $V_{DS}$ =0.6V•  $V_{DB}$ : 0V  $\rightarrow$  1.2V,  $L_g$  nominal

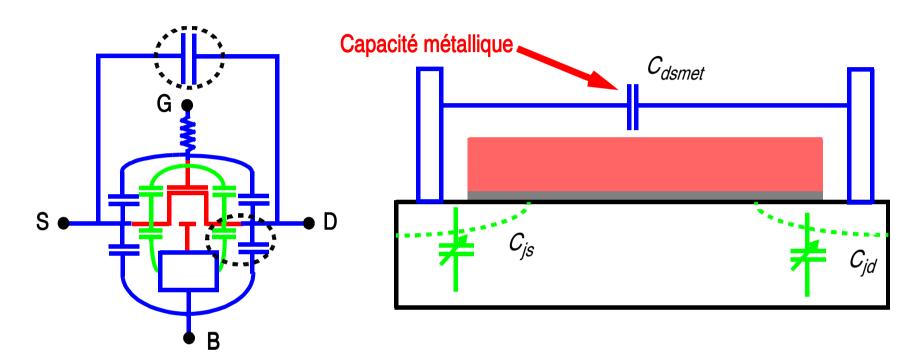

# Modelisation de $C_{\text{BD}} + C_{\text{DS}}$ parasite : $C_{\text{BDEXT}} + C_{\text{DSEXT}}$

- $\square$  Modélisation :  $C_{bdext} + C_{dsext} = C_{jd} + C_{dsmet}$

- $\bigcirc C_{id} = f(V_{DB}) \Longrightarrow Capacité de jonction ;$

- $\bigcirc C_{dsmet} = f(L_g)$

# Modelisation de $C_{\text{BD}} + C_{\text{DS}}$ parasite : $C_{\text{BDEXT}} + C_{\text{DSEXT}}$

#### □ Validation du modèle

Technologie 65nm,  $L_g$ : 65nm  $\rightarrow$  2.0 $\mu$ m,  $V_{GS}$ =0

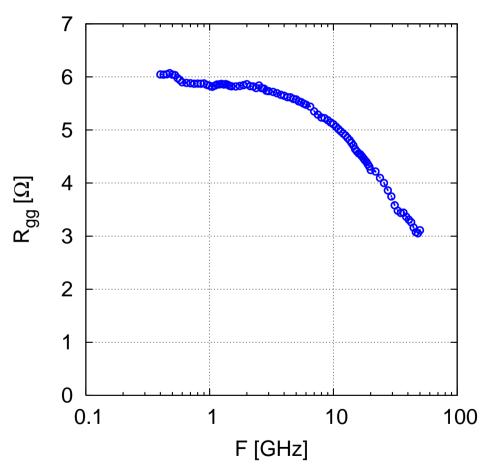

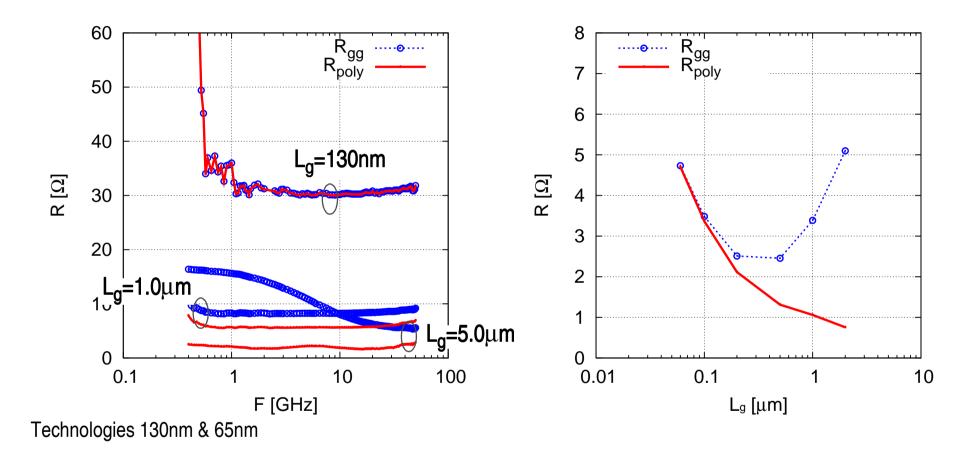

□ R<sub>gg</sub> : résistance série vue de la grille

$$R_{gg} = Re[1/Y_{11}]$$

☐ R<sub>qq</sub> : résistance série vue de la grille

$$R_{gg} = Re[1/Y_{11}]$$

- ☐ Extraction :

- O Inversion forte : substrat écranté par le canal

- $OV_{DS}=0$

☐ R<sub>qq</sub> : résistance série vue de la grille

$$R_{gg} = Re[1/Y_{11}]$$

- ☐ Extraction :

- O Inversion forte : substrat écranté par le canal

- $OV_{DS}=0$

- □ Deux contributions

☐ R<sub>qq</sub> : résistance série vue de la grille

$$R_{gg} = Re[1/Y_{11}]$$

- ☐ Extraction :

- O Inversion forte : substrat écranté par le canal

- $OV_{DS}=0$

■ Deux contributions

☐ R<sub>qq</sub> : résistance série vue de la grille

$$R_{gg} = Re[1/Y_{11}]$$

- ☐ Extraction :

- O Inversion forte : substrat écranté par le canal

- $OV_{DS}=0$

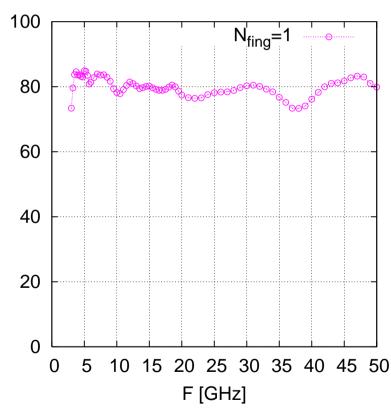

#### ☐ Dispositif long

Technologie 65nm,  $L_g$ =2.0 $\mu$ m,  $V_{GS}$ =1.2V,  $V_{DS}$ =0V

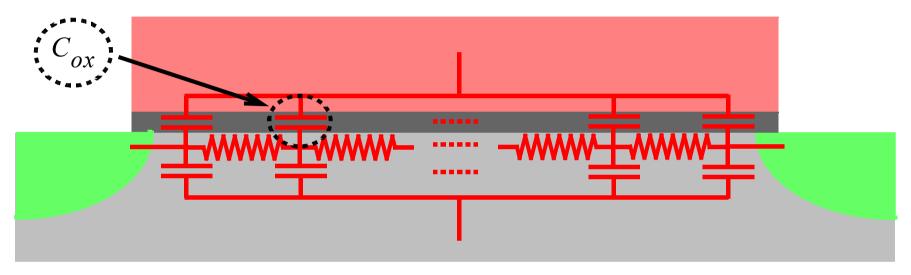

#### ☐ Structure distribuée en inversion forte

☐ Structure distribuée en inversion forte

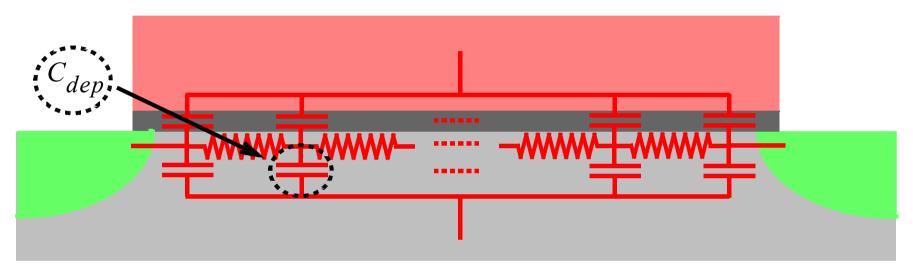

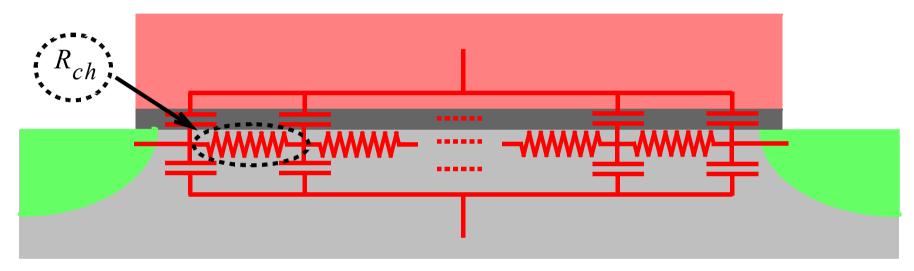

☐ Structure distribuée en inversion forte

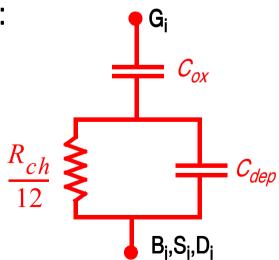

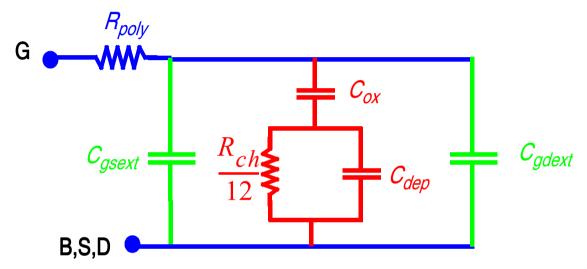

- ☐ Contribution intrinsèque due au canal :

- Inversion forte, V<sub>DS</sub>=0

$$Y_{11} = \frac{C_{ox}}{C_{ox} + C_{dep}} \cdot \left[ j \cdot \omega \cdot C_{dep} + j \cdot \omega \cdot C_{ox} \cdot \frac{\tanh[(\gamma \cdot L)/2]}{(\gamma \cdot L)/2} \right]$$

$$\gamma \cdot L = \sqrt{R_{ch} \cdot j \cdot \omega \cdot (C_{dep} + C_{ox})}$$

- ☐ Contribution intrinsèque due au canal :

- O Inversion forte, V<sub>DS</sub>=0

$$Y_{11} = \frac{C_{ox}}{C_{ox} + C_{dep}} \cdot \left[ j \cdot \omega \cdot C_{dep} + j \cdot \omega \cdot C_{ox} \cdot \frac{\tanh[(\gamma \cdot L)/2]}{(\gamma \cdot L)/2} \right]$$

$$\gamma \cdot L = \sqrt{R_{ch} \cdot j \cdot \omega \cdot (C_{dep} + C_{ox})}$$

☐ Approximation à l'ordre 2 :

#### ☐ Approximation à l'ordre 2 :

☐ Approximation à l'ordre 2 :

☐ Mesure de R<sub>poly</sub> :

$$R_{poly} = R_{gg} - \left(12 \cdot Re \left[Y_{22} + \frac{2}{3} \cdot Y_{12}\right]\right)^{-1} \cdot \left(\frac{C_{gg} - 2 \cdot C_{gdext}}{C_{gg}}\right)^{2}$$

Mesure

Contribution canal estimée

Mesure directe de  $R_{poly} \Rightarrow$  construction de  $R_{ggext}$

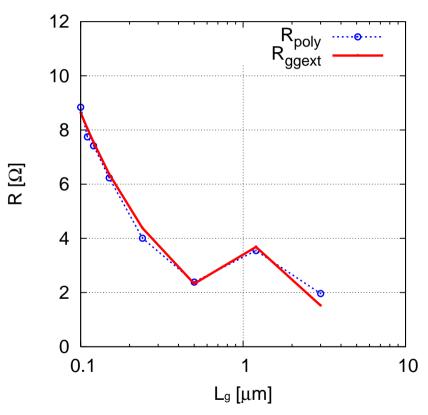

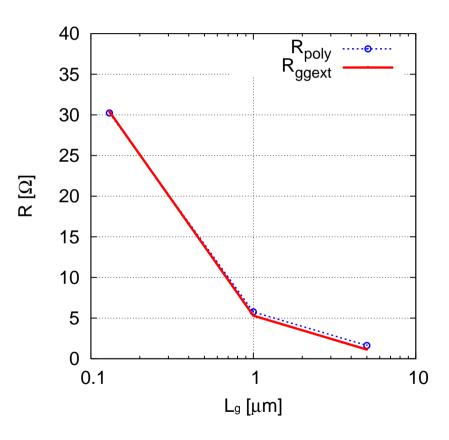

☐ Contribution de la tête de grille

O Dépend du nombre de contacts

- ☐ Contribution de la tête de grille

- O Dépend du nombre de contacts

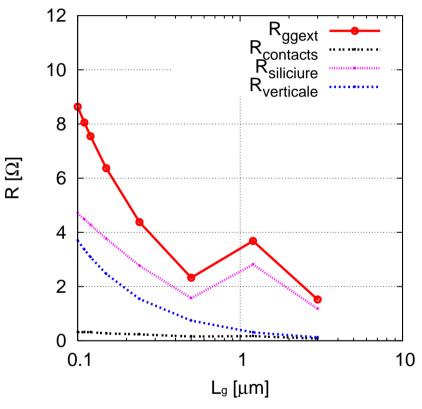

- ☐ Contribution du siliciure de grille

O Dépend de W<sub>f</sub>/L<sub>g</sub>

- ☐ Contribution de la tête de grille

- O Dépend du nombre de contacts

- ☐ Contribution du siliciure de grille

- O Dépend de W<sub>f</sub>/L<sub>g</sub>

- ☐ Contribution verticale

○ Dépend de 1/(W<sub>f</sub>×L<sub>q</sub>)

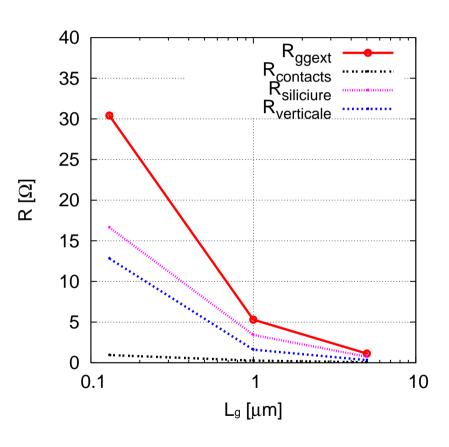

#### ☐ Comparaison Mesure/Modèle

Technologies 90nm & 130nm

#### ☐ Poids des différentes contributions

Technologies 90nm & 130nm

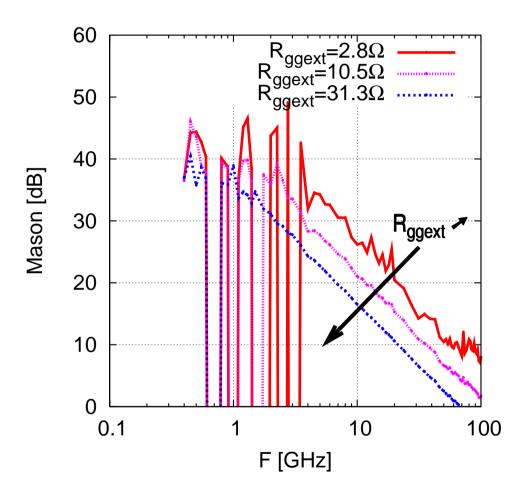

## IMPACT DE LA RESISTANCE DE GRILLE

#### Technologie 65nm

- L<sub>g</sub> nominale, V<sub>DS</sub>=V<sub>GS</sub>=1.2V

F<sub>max</sub>=67, 113 & 200GHz

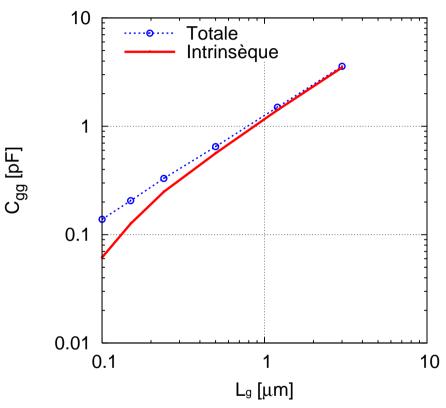

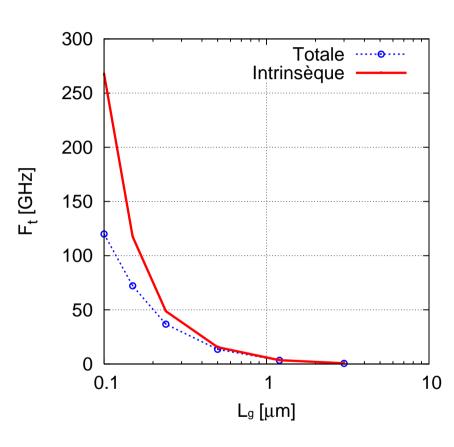

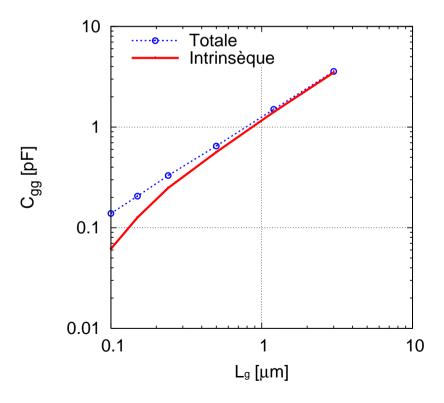

#### IMPACT DES CAPACITES PARASITES

#### Technologie 90nm

•  $L_g$  : nominale  $\rightarrow$  3.0 $\mu$ m,  $V_{DS}$ = $V_{GS}$ =1.25V

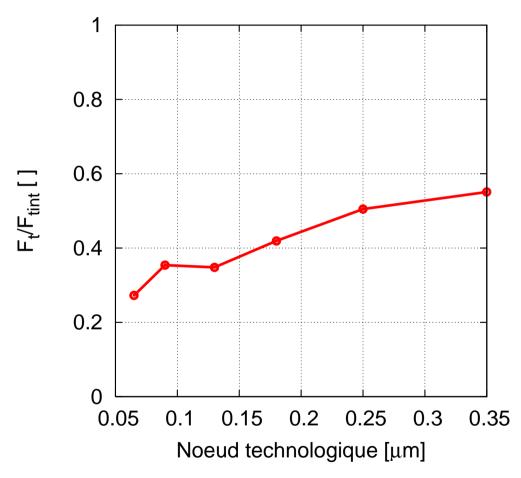

## **EVOLUTION DES CAPACITES PARASITES**

•  $V_{GS}=V_{DS}=V_{DD}$ ,  $L_g$  nominale

## **EVOLUTION DES CAPACITES PARASITES**

# EXTRACTION ET MODELISATION DES ELEMENTS EXTRINSEQUES "CONNUS"

- ☐ Méthodologie basée sur la connaissance du MOS

- OExtraction de R<sub>poly</sub>

- ⇒ Résistance de la grille uniquement

- Applicable à toutes les géométries

- ⇒ Mise en évidence et extraction de 3 contributions

# EXTRACTION ET MODELISATION DES ELEMENTS EXTRINSEQUES "CONNUS"

- ☐ Méthodologie basée sur la connaissance du MOS

- OExtraction de R<sub>poly</sub>

- ⇒ Résistance de la grille uniquement

- O Applicable à toutes les géométries

- ⇒ Mise en évidence et extraction de 3 contributions

- ☐ Impact de la partie extrinsèque

- O Evolution croissante

- O Performances de plus en plus conditionnées par l'extrinsèque

- E. Bouhana et al., JNM2005.

#### PLAN

Introduction

Etude des éléments extrinsèques "connus"

Etude du réseau substrat

Conclusion & perspectives

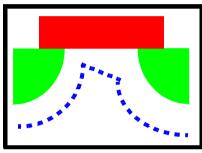

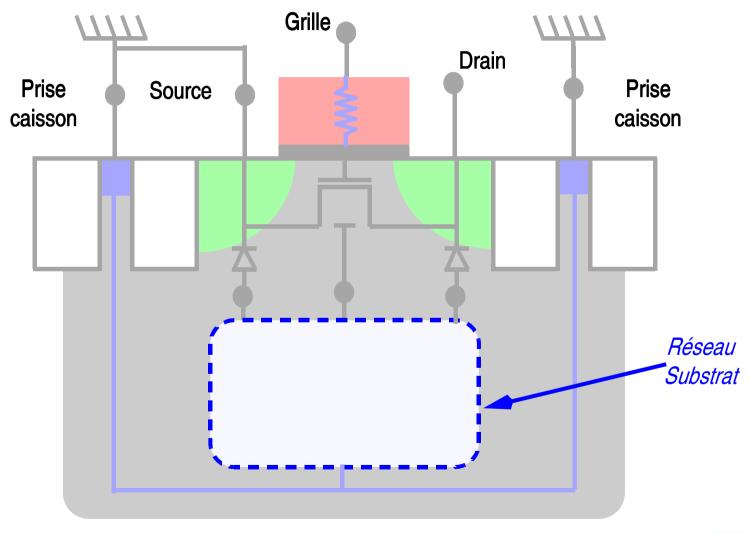

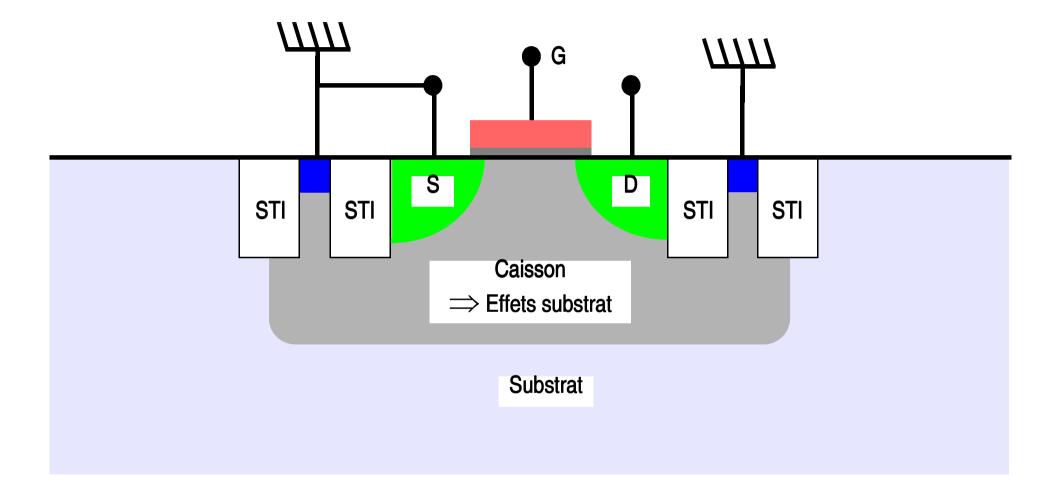

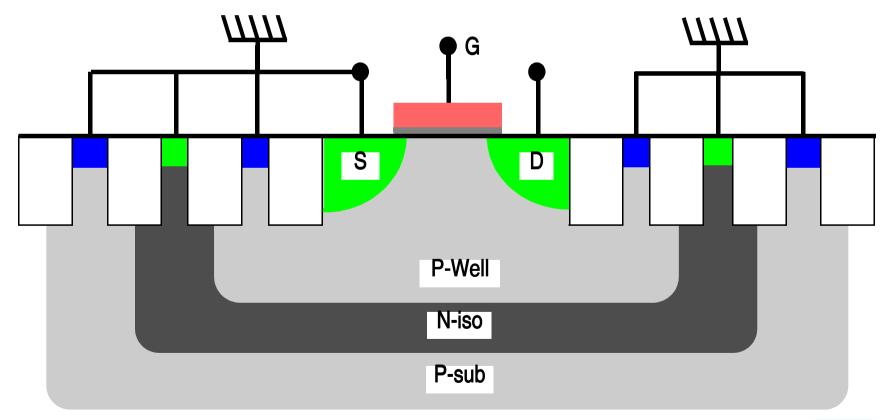

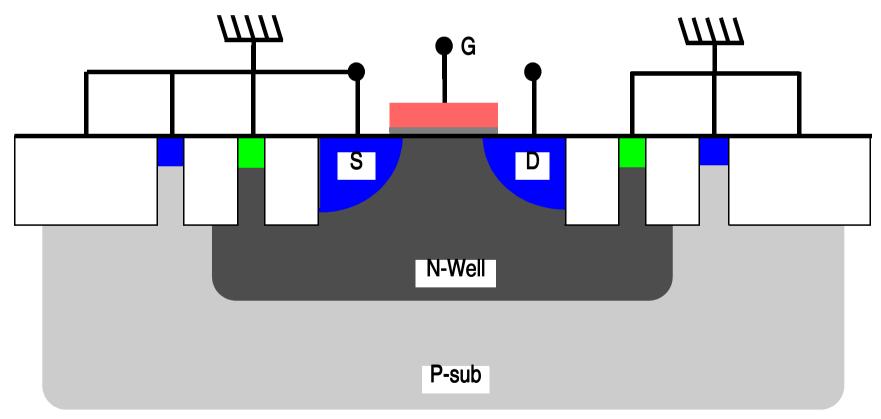

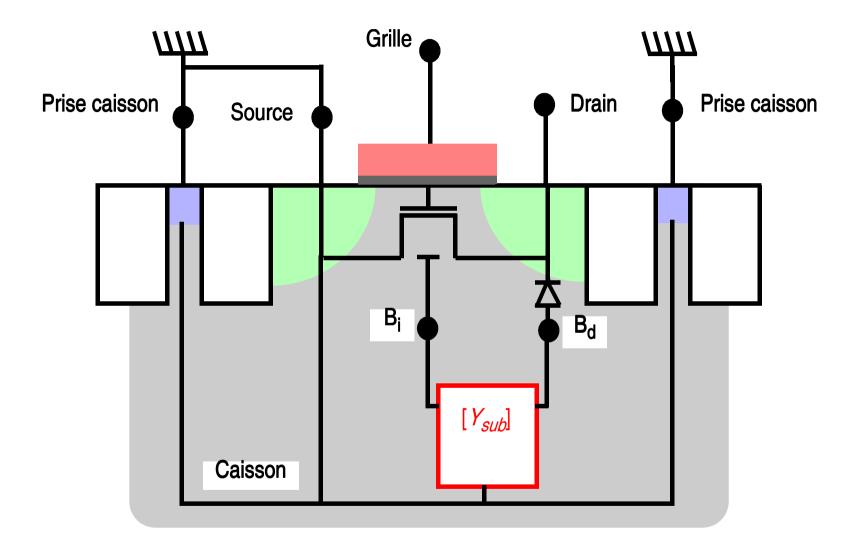

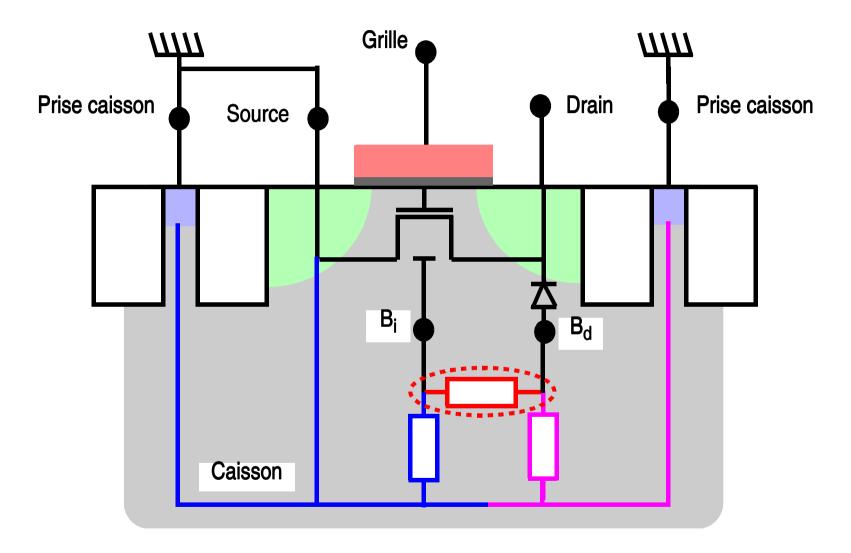

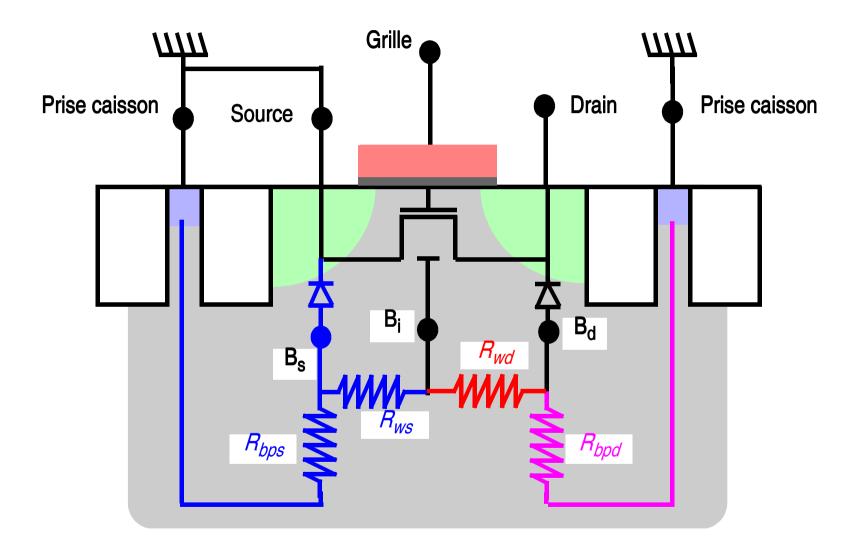

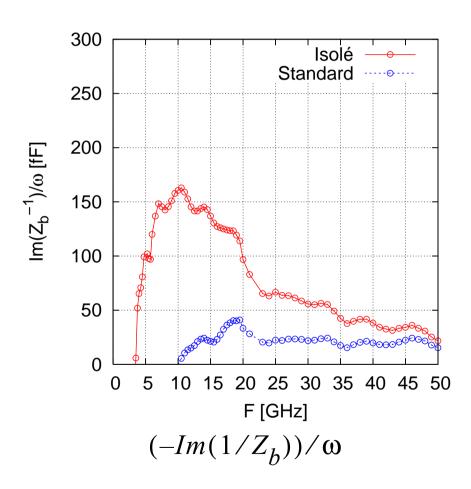

#### LE RESEAU SUBSTRAT

☐ Le réseau substrat dépend du layout et de la technologie

- ☐ Le réseau substrat dépend du layout et de la technologie

- OTypes de prises caisson

- ☐ Le réseau substrat dépend du layout et de la technologie

- OTypes de prises caisson

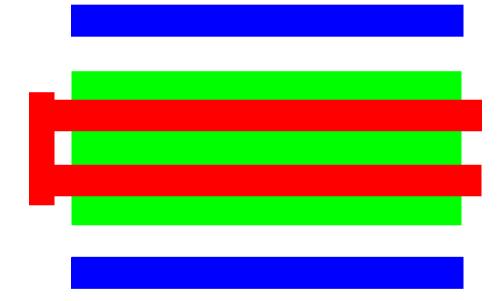

- OStructures interdigitées

- ☐ Le réseau substrat dépend du layout et de la technologie

- OTypes de prises caisson & structures interdigitées

- O Dispositifs isolés : nMOSFET

- ☐ Le réseau substrat dépend du layout et de la technologie

- OTypes de prises caisson & structures interdigitées

- O Dispositifs isolés : pMOSFET

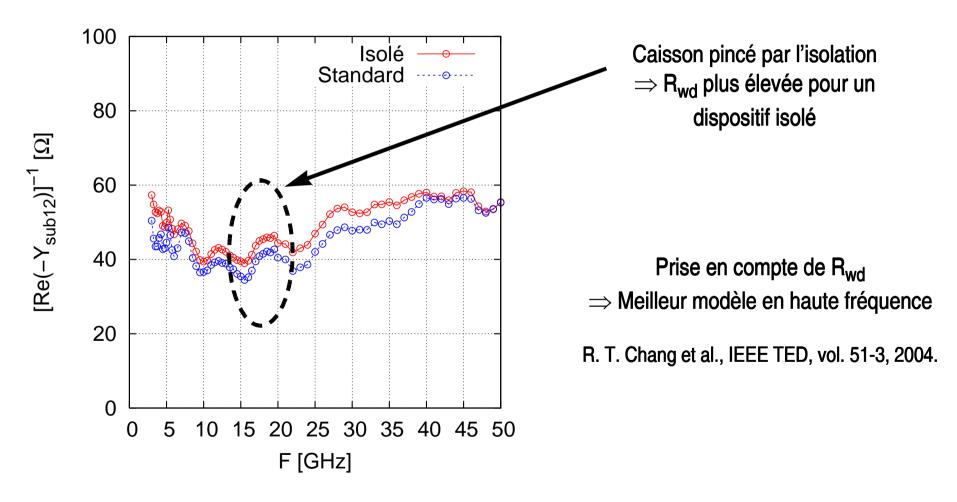

### ANALYSE DU RESEAU SUBSTRAT (2)

- ☐ Dans la littérature : plusieurs modèles

- OPrise en compte de la dépendance vis-à-vis du layout :

- J. Han and H. Shin, IEEE MTT Symposium, vol. 3, 2003.

- R. T. Chang et al., IEEE TED, vol. 51, no. 3, 2004.

### ANALYSE DU RESEAU SUBSTRAT (2)

- ☐ Dans la littérature : plusieurs modèles

- OPrise en compte de la dépendance vis-à-vis du layout :

- J. Han and H. Shin, IEEE MTT Symposium, vol. 3, 2003.

- R. T. Chang et al., IEEE TED, vol. 51, no. 3, 2004.

- OPas de prise en compte des effets de la couche d'isolation.

### ANALYSE DU RESEAU SUBSTRAT (2)

- ☐ Dans la littérature : plusieurs modèles

- OPrise en compte de la dépendance vis-à-vis du layout :

- J. Han and H. Shin, IEEE MTT Symposium, vol. 3, 2003.

- R. T. Chang et al., IEEE TED, vol. 51, no. 3, 2004.

- OPas de prise en compte des effets de la couche d'isolation.

- ☐ La plupart de ces modèles sont basés sur un schéma équivalent présupposé

- La valeur des éléments est extraite de la mesure de Y<sub>22</sub>

J. Han, M. Je and H. Shin, IEEE EDL, vol. 23, no. 7, 2002.

### ANALYSE DU RESEAU SUBSTRAT (3)

☐ Approche différente proposée :

- ○Analyse des mesures ⇒ on accède au réseau substrat progressivement ;

- On identifie la topologie du modèle : pas de schéma équivalent présupposé.

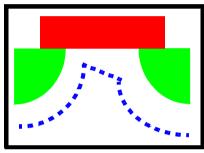

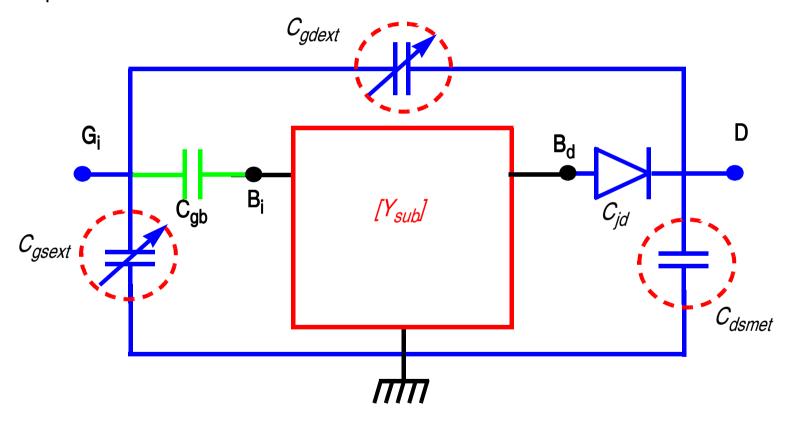

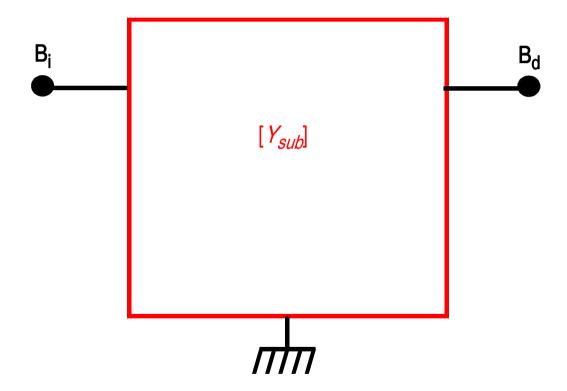

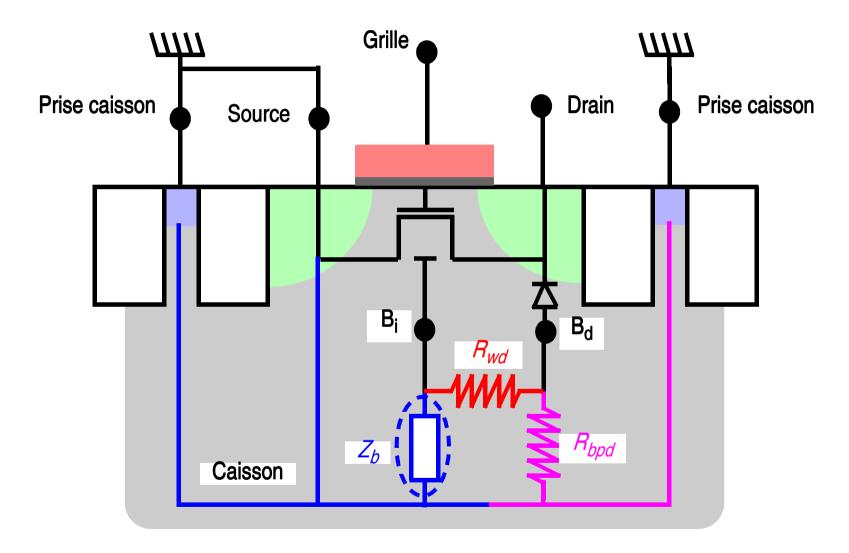

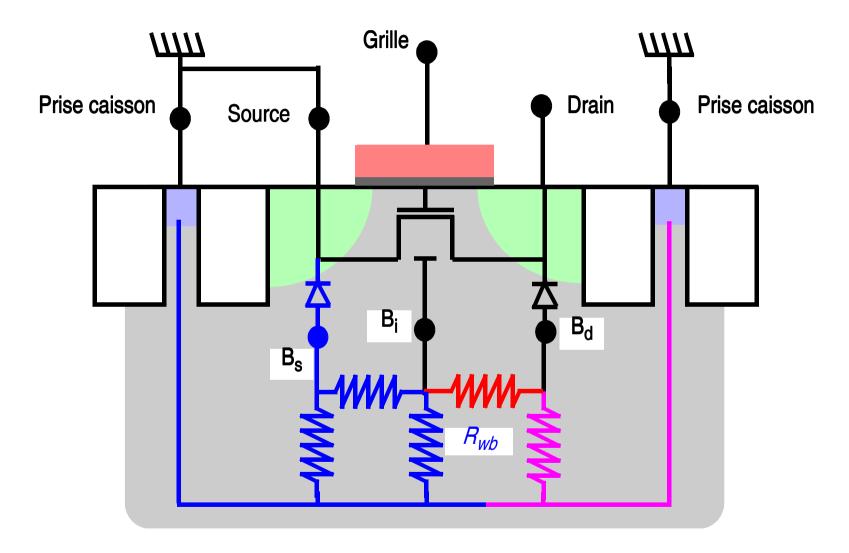

### ACCES AU RESEAU SUBSTRAT

#### ACCES AU RESEAU SUBSTRAT

Réseau substrat

☐ On retire les éléments parasites puis C<sub>gb</sub> et C<sub>jd</sub>

#### ☐ Résistance de grille

➤ Les mesures sont converties en paramètres [Z]

#### ☐ Capacités parasites

ightharpoonup Représentation en  $\Pi$

#### ☐ Dernière étape

> Représentation en T

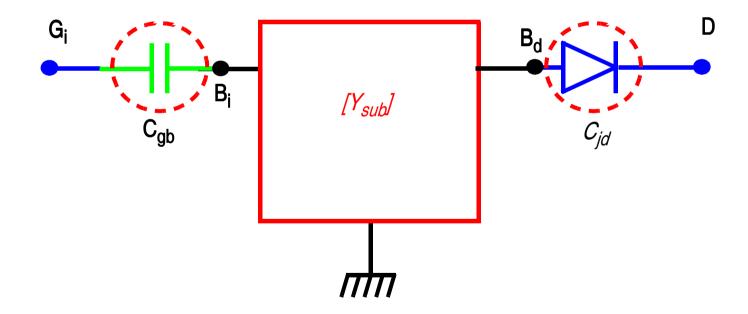

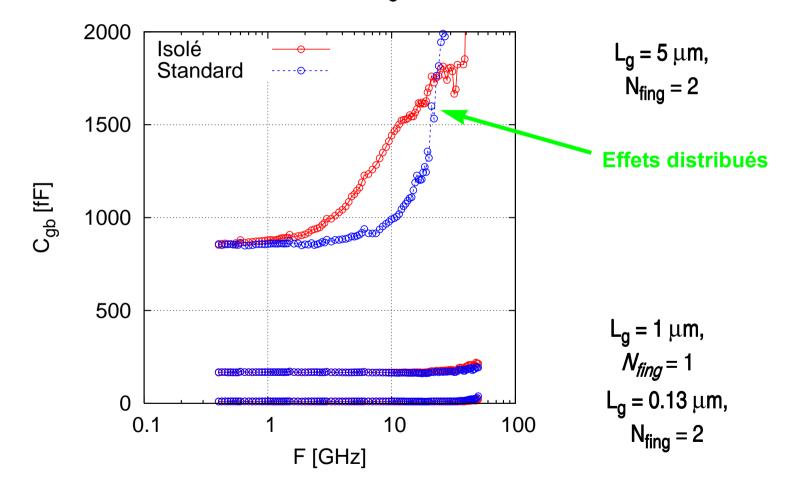

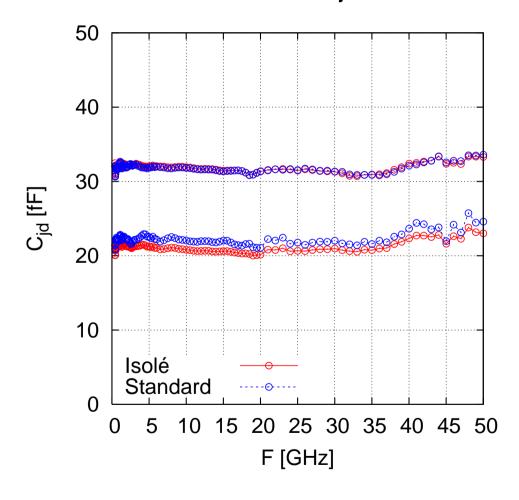

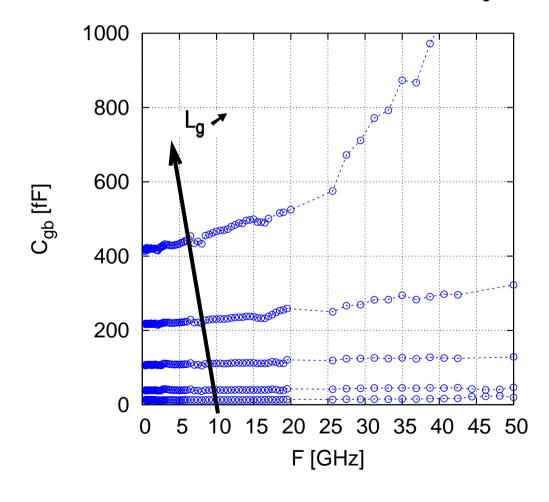

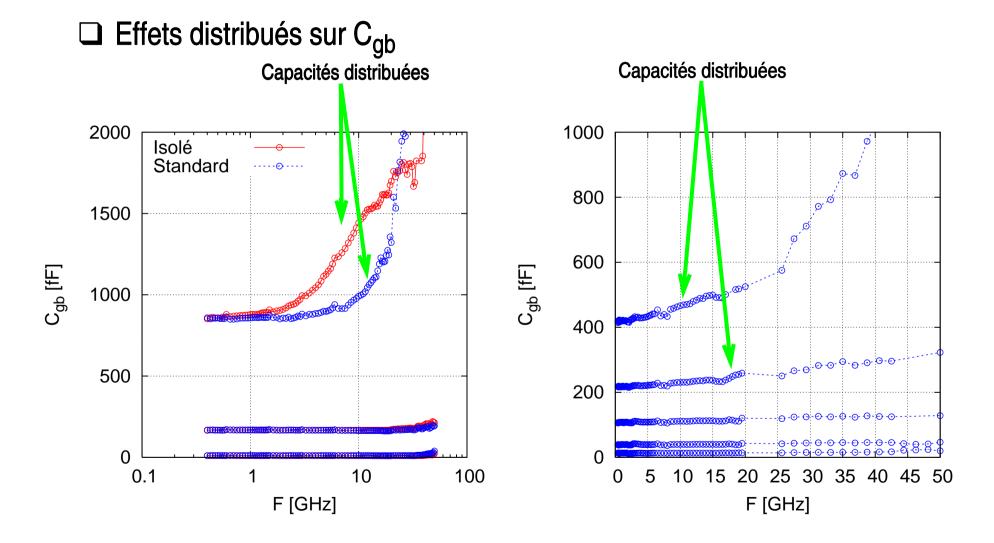

#### ☐ Technologie 130nm - Capacité C<sub>qb</sub>

#### ☐ Technologie 130nm - Capacité C<sub>jd</sub>

$$L_g = 1 \mu m$$

,  $N_{fing} = 1$

$$L_g = 5 \mu \text{m},$$

$N_{fing} = 2$

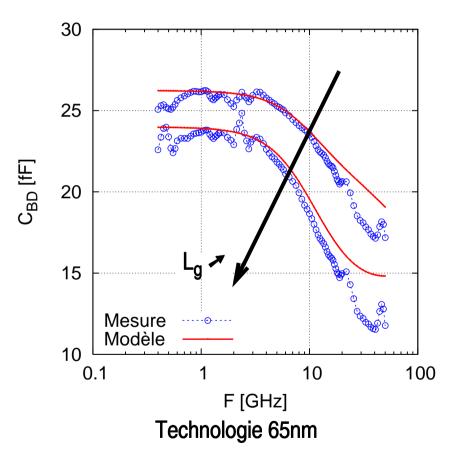

### ☐ Technologie 65nm - Capacité C<sub>gb</sub>

➤ Dispositifs isolés - prises caissons entourantes, N<sub>fing</sub> = 8

### ☐ Technologie 65nm - Capacité C<sub>id</sub>

➤ Dispositifs isolés - prises caissons entourantes, N<sub>fing</sub> = 8

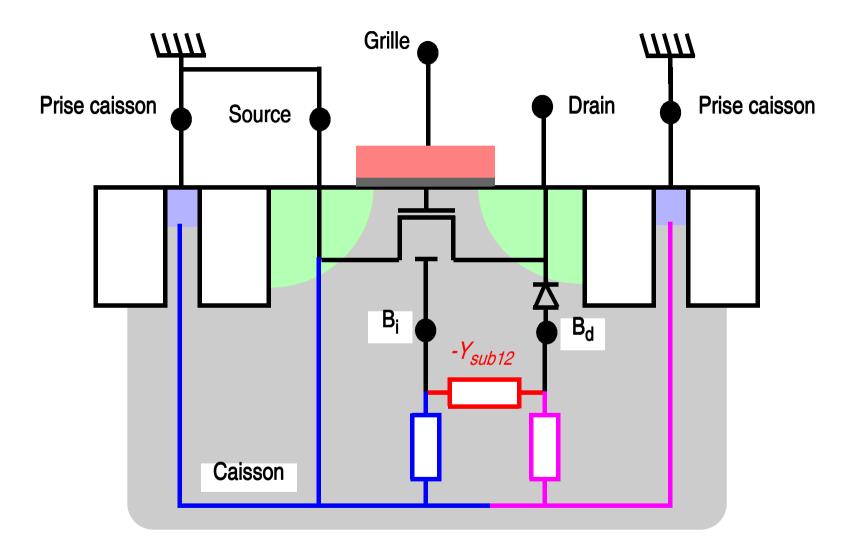

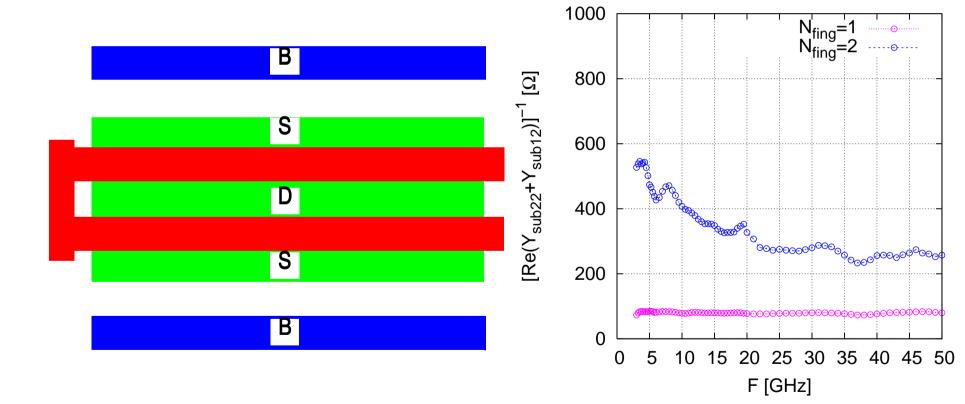

# ANALYSE DE [Y<sub>SUB</sub>]: -Y<sub>SUB12</sub>

## ANALYSE DE [Y<sub>SUB</sub>]: -Y<sub>SUB12</sub> (2)

#### □ -Y<sub>sub12</sub> ⇔ Chemin sous le canal entre source et drain=R<sub>wd</sub>

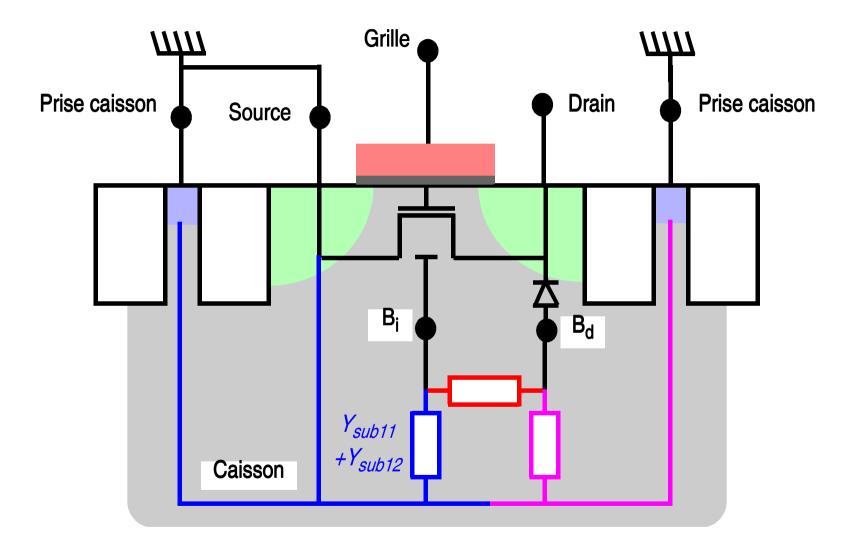

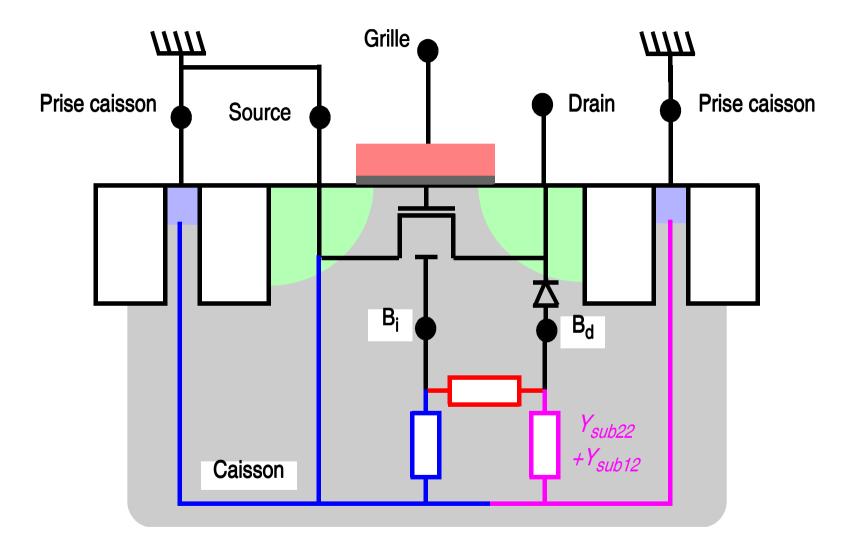

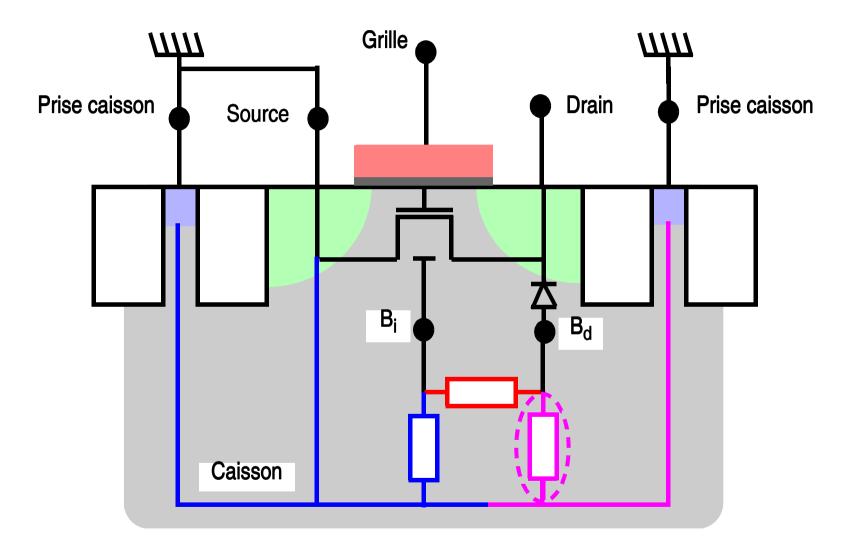

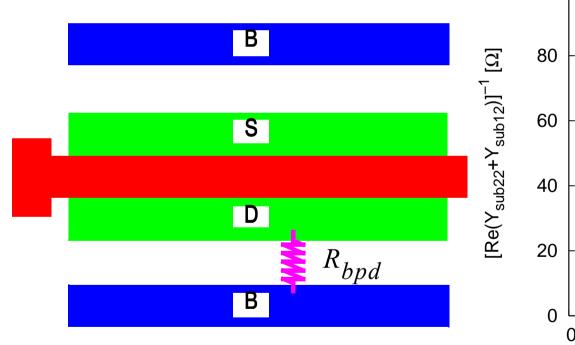

## ANALYSE DE $[Y_{SUB}]$ : $Y_{SUB22} + Y_{SUB12}$ (2)

$\Box$   $Y_{sub22} + Y_{sub12} =$  Chemin entre la jonction drain et la prise caisson

$$\bigcirc N_{fing}=1$$

## ANALYSE DE $[Y_{SUB}]$ : $Y_{SUB22} + Y_{SUB12}$ (2)

$\Box$   $Y_{sub22} + Y_{sub12} =$  Chemin entre la jonction drain et la prise caisson

$$\bigcirc N_{fing}=2$$

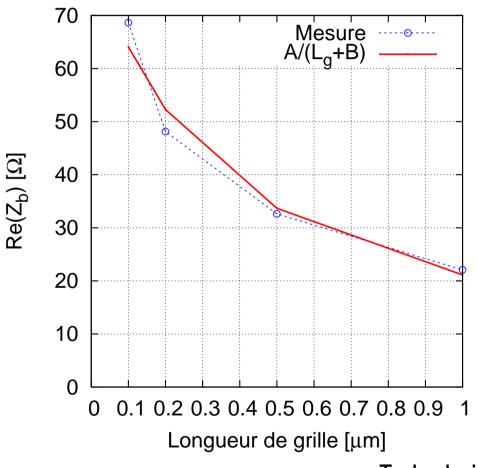

## ANALYSE DE $[Y_{SUB}]$ : $Y_{SUB11} + Y_{SUB12}$ (2)

#### ☐ Effet d'une prise caisson entourante : chemin le long des doigts de grille

A = 28.3  $\Omega.\mu\text{m}$  ; B = 0.34  $\mu\text{m}$

Technologie 65 nm

## ANALYSE DE $[Y_{SUB}]$ : $Y_{SUB11} + Y_{SUB12}$ (2)

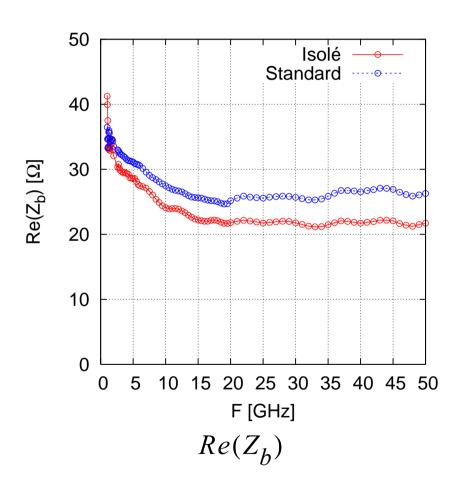

#### ☐ Effet d'une couche d'isolation

Technologie 130 nm,  $V_{GS} = 0$ ,  $V_{DS} = 0.6 \text{ V}$

### SIMULATION AVEC LE MODELE EXTRAIT

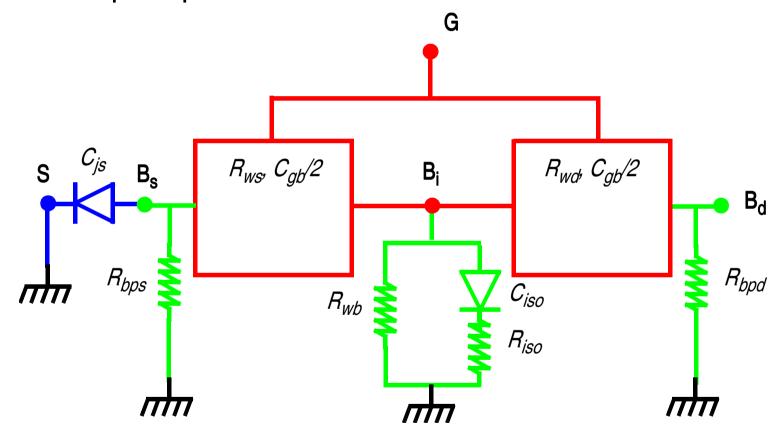

□ C<sub>gb</sub>, C<sub>jd</sub> et les parasites sont rajoutés autour du modèle de [Y<sub>SUB</sub>]

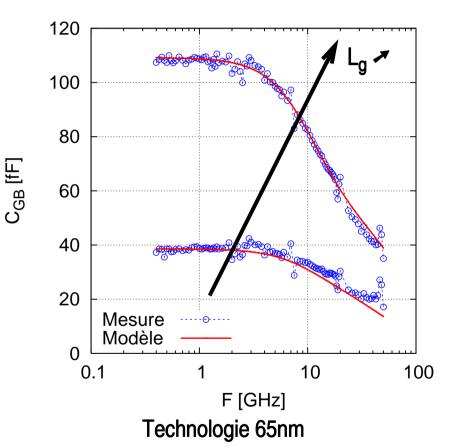

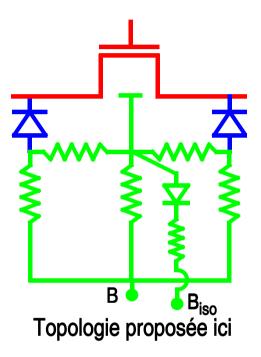

- ☐ Mesures observées : capacités totales

- O Incluent un chemin à travers le réseau substrat

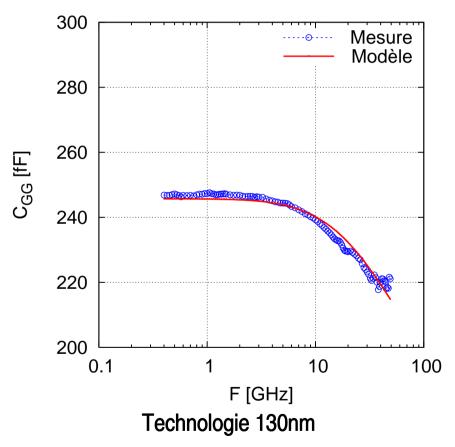

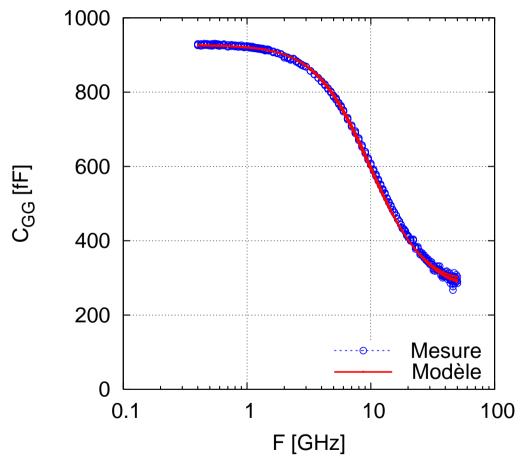

## RESULTATS SUR C<sub>GG</sub>

130nm :  $L_g$ =1.0 $\mu$ m,  $N_f$ =1, isolé,  $V_{GS}$ = $V_{DS}$ =0 65nm :  $L_g$ =0.2 $\mu$ m&0.5 $\mu$ m,  $N_f$ =8, isolé,  $V_{GS}$ =0,  $V_{DS}$ =0.6

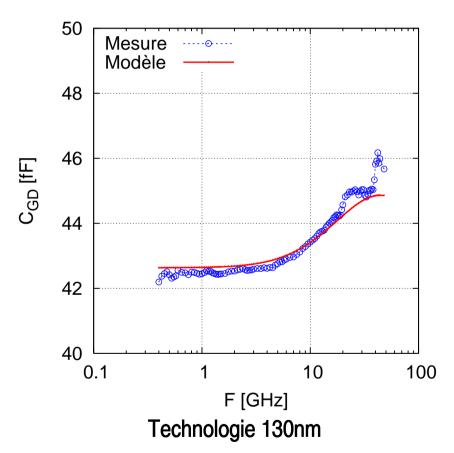

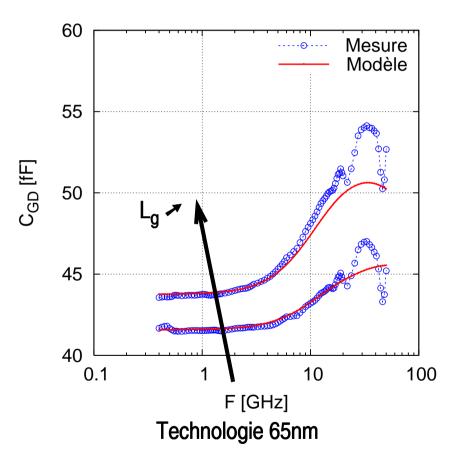

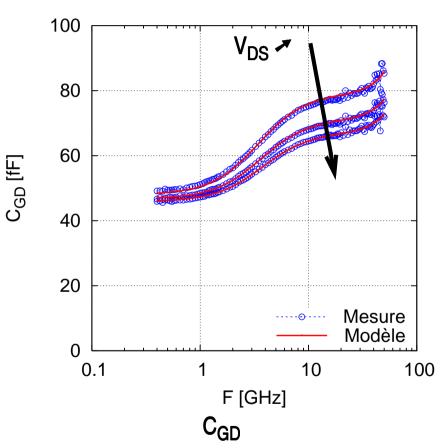

## RESULTATS SUR C<sub>GD</sub>

130nm :  $L_g$ =1.0 $\mu$ m,  $N_f$ =1, isolé,  $V_{GS}$ = $V_{DS}$ =0 65nm :  $L_g$ =0.2 $\mu$ m&0.5 $\mu$ m,  $N_f$ =8, isolé,  $V_{GS}$ =0,  $V_{DS}$ =0.6

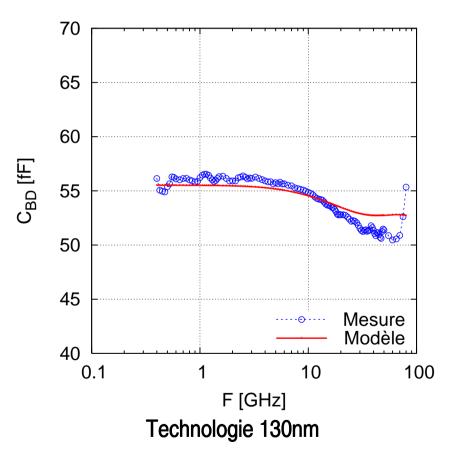

## RESULTATS SUR CBD

130nm :  $L_g$ =1.0 $\mu$ m,  $N_f$ =1, isolé,  $V_{GS}$ = $V_{DS}$ =0 65nm :  $L_g$ =0.2 $\mu$ m&0.5 $\mu$ m,  $N_f$ =8, isolé,  $V_{GS}$ =0,  $V_{DS}$ =0.6

### CAS DES DISPOSITIFS TRES LONGS

### Cas des dispositifs tres longs

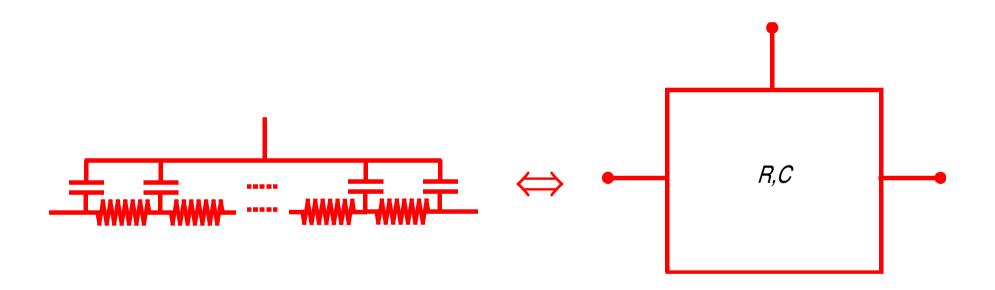

☐ Modèle spécifique

# Cas des dispositifs tres longs

### ☐ Modèle spécifique

# CAS DES DISPOSITIFS TRES LONGS

□ C<sub>GG</sub>

Technologie 130nm,  $L_g$ =5 $\mu$ m,  $V_{GS}$ =0,  $V_{DS}$ =0;0.6;1.2V

## CAS DES DISPOSITIFS TRES LONGS

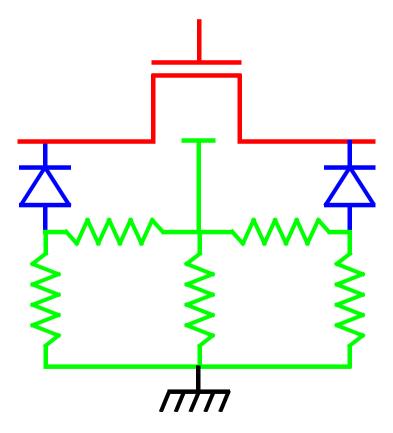

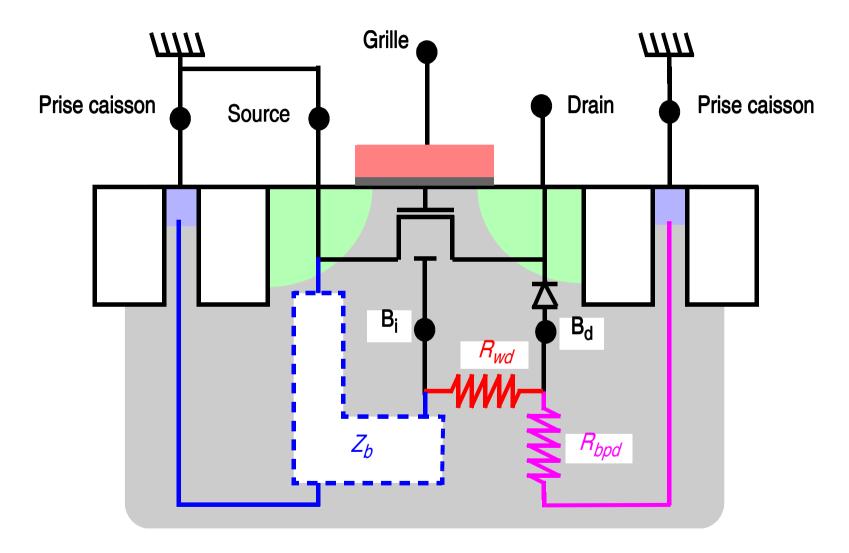

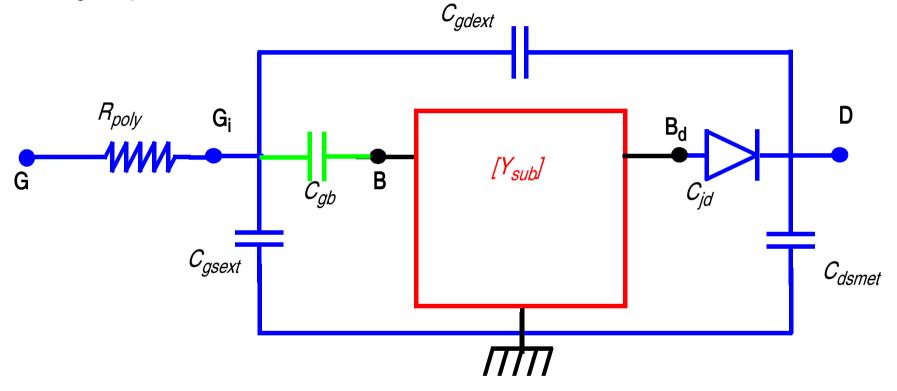

# ETUDE DU RESEAU SUBSTRAT

#### ☐ Modèles de réseau substrat :

# ETUDE DU RESEAU SUBSTRAT

#### ☐ Modèles de réseau substrat :

B B<sub>iso</sub> Topologie proposée ici

# ETUDE DU RESEAU SUBSTRAT

#### ☐ Trois modèles :

- OTopologie proposée ici :

- ➤ Prise en compte de l'isolation

- ➤ Méthodologie d'extraction

Bouhana et al., ICMTS2006.

### PLAN

Introduction

Etude des éléments extrinsèques "connus"

Etude du réseau substrat

Conclusion & perspectives

### CONCLUSION GENERALE

- ☐ Mise au point d'une méthodologie d'analyse du MOSFET à partir de la mesure

- O Résistance de grille

- ➤ Mesure directe, méthode originale

- ➤ Mise en évidence de 3 contributions

- > Modèle équivalent à celui approuvé par le Compact Model Council

### **CONCLUSION GENERALE**

- ☐ Mise au point d'une méthodologie d'analyse du MOSFET à partir de la mesure

- O Résistance de grille

- ➤ Mesure directe, méthode originale

- ➤ Mise en évidence de 3 contributions

- > Modèle équivalent à celui approuvé par le Compact Model Council

- O Réseau substrat

- > Applicable nMOSFET (isolé/standard)/pMOSFET,

- > Topologie reliée au layout

- ➤ Mise au point d'une méthodologie d'extraction

- > Mise en évidence d'effets ignorés jusque là

- ☐ Augmentation de la part de l'extrinsèque

- OBesoin d'une meilleure prise en compte

- > Modélisation

- > Lois géométriques

- > Extraction

- ☐ Augmentation de la part de l'extrinsèque

- OBesoin d'une meilleure prise en compte

- OQuel gain d'une technologie à la suivante?

- ☐ Augmentation de la part de l'extrinsèque

- OBesoin d'une meilleure prise en compte

- OQuel gain d'une technologie à la suivante?

- ☐ Augmentation de la part de l'extrinsèque

- OBesoin d'une meilleure prise en compte

- OQuel gain d'une technologie à la suivante?

- ☐ Technologies alternatives : quelles performances RF ?

- O Exemple: FinFET

- O Impact de la résistance de grille

- ☐ Augmentation de la part de l'extrinsèque

- OBesoin d'une meilleure prise en compte

- OQuel gain d'une technologie à la suivante?

- □ Technologies alternatives : quelles performances RF ?

- O Exemple: FinFET

- O Impact de la résistance de grille