# Le test des PLAs optimisés topologiquement

A.-O. Fernandes

### ▶ To cite this version:

A.-O. Fernandes. Le test des PLAs optimisés topologiquement. Modélisation et simulation. Institut National Polytechnique de Grenoble - INPG, 1988. Français. NNT: . tel-00330517

# HAL Id: tel-00330517 https://theses.hal.science/tel-00330517

Submitted on 14 Oct 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THESE

# présentée par

## **Antonio Otavio FERNANDES**

# pour obtenir le titre de **DOCTEUR**

# de l'INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

(arrêté ministériel du 5 Juillet 1984)

Spécialité: **Microélectronique**

# LE TEST DES PLAS OPTIMISES TOPOLOGIQUEMENT

Date de soutenance: 9 septembre 1988

Composition du jury:

Messieurs

G.MAZARE

Président

G.CAMBON

Rapporteur

**B.COURTOIS**

J.FREHEL

Rapporteur

# INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

Président : Georges LESPINARD Année 1988

# Professeurs des Universités

| BARIBAUD Michel         | ENSERG  | JOUBERT Jean-Claude      | <b>ENSPG</b>   |

|-------------------------|---------|--------------------------|----------------|

| BARRAUD Alain           | ENSIEG  | JOURDAIN Geneviève       | <b>ENSIEG</b>  |

| BAUDELET Bernard        | ENSPG   | LACOUME Jean-Louis       | <b>ENSIEG</b>  |

| BEAUFILS Jean-Pierre    | ENSEEG  | LESIEUR Marcel           | <b>ENSHMG</b>  |

| BLIMAN Samuel           | ENSERG  | LESPINARD Georges        | <b>ENSHMG</b>  |

| BLOCH Daniel            | ENSPG   | LONGEQUEUE Jean-Pierre   | <b>ENSPG</b>   |

| BOIS Philippe           | ENSHMG  | LOUCHET François         | <b>ENSIEG</b>  |

| BONNETAIN Lucien        | ENSEEG  | MASSE Philippe           | <b>ENSIEG</b>  |

| BOUVARD Maurice         | ENSHMG  | MASSELOT Christian       | <b>ENSIEG</b>  |

| BRISSONNEAU Pierre      | ENSIEG  | MAZARE Guy               | <b>ENSIMAG</b> |

| BRUNET Yves             | IUFA    | MOREAU René              | <b>ENSHMG</b>  |

| CAILLERIE Denis         | ENSHMG  | MORET Roger              | <b>ENSIEG</b>  |

| CAVAIGNAC Jean-François | ENSPG   | MOSSIERE Jacques         | <b>ENSIMAG</b> |

| CHARTIER Germain        | ENSPG   | OBLED Charles            | <b>ENSHMG</b>  |

| CHENEVIER Pierre        | ENSERG  | OZIL Patrick             | <b>ENSEEG</b>  |

| CHERADAME Hervé         | UFR PGP | PARIAUD Jean-Charles     | <b>ENSEEG</b>  |

| CHOVET Alain            | ENSERG  | PERRET René              | <b>ENSIEG</b>  |

| COHEN Joseph            | ENSERG  | PERRET Robert            | <b>ENSIEG</b>  |

| COUMES André            | ENSERG  | PIAU Jean-Michel         | <b>ENSHMG</b>  |

| DARVE Félix             | ENSHMG  | POUPOT Christian         | <b>ENSERG</b>  |

| DELLA-DORA Jean         | ENSIMAG | RAMEAU Jean-Jacques      | <b>ENSEEG</b>  |

| DEPORTES Jacques        | ENSPG   | RENAUD Maurice           | UFR PGP        |

| DOLMAZON Jean-Marc      | ENSERG  | ROBERT André             | UFR PGP        |

| DURAND Francis          | ENSEEG  | ROBERT François          | <b>ENSIMAG</b> |

| DURAND Jean-Louis       | ENSIEG  | SABONNADIERE Jean-Claude | <b>ENSIEG</b>  |

| FOGGIA Albert           | ENSIEG  | SAUCIER Gabrielle        | <b>ENSIMAG</b> |

| FONLUPTJean             | ENSIMAG | SCHLENKER Claire         | <b>ENSPG</b>   |

| FOULARD Claude          | ENSIEG  | SCHLENKER Michel         | ENSPG          |

| GANDINI Alessandro      | UFR PGP | SILVY Jacques            | UFR PGP        |

| GAUBERT Claude          | ENSPG   | SIRIEYS Pierre           | <b>ENSHMG</b>  |

| GENTIL Pierre           | ENSERG  | SOHM Jean-Claude         | <b>ENSEEG</b>  |

| GREVEN Hélène           | IUFA    | SOLER Jean-Louis         | <b>ENSIMAG</b> |

| GUERIN Bernard          | ENSERG  | SOUQUET Jean-Louis       | <b>ENSEEG</b>  |

| GUYOT Pierre            | ENSEEG  | TROMPETTE Philippe       | <b>ENSHMG</b>  |

| IVANES Marcel           | ENSIEG  | VEILLON Gérard           | <b>ENSIMAG</b> |

| JAUSSAUD Pierre         | ENSIEG  | ZADWORNY François        | <b>ENSERG</b>  |

|                         |         |                          | -              |

# Professeur Université des Sciences Sociales (Grenoble II)

**BOLLIET Louis**

# Personnes ayant obtenu le diplôme d'HABILITATION A DIRIGER DES RECHERCHES

**BECKER Monique BINDER Zdenek** CHASSERY Jean-Marc CHOLLET Jean-Pierre **COEY John COLINET** Catherine **COMMAULT** Christian CORNUEJOLS Gérard COULOMB Jean-Louis **DALARD Francis DANES Florin DEROO** Daniel DIARD Jean-Paul DION Jean-Michel **DUGARD Luc DURAND Madcleine DURAND** Robert **GALERIE Alain GAUTHIER Jean-Paul GENTIL Sylviane** GHIBAUDO Gérard **HAMAR Sylvaine HAMAR Roger** LADET Pierre **LATOMBE** Claudine LE GORREC Bernard **MADAR Roland MULLER** Jean NGUYEN TRONG Bernadette **PASTUREL Alain PLA Fernand** ROUGER Jean **TCHUENTE Maurice**

### Chercheurs du C.N.R.S Directeurs de recherche 1ère Classe

CARRE René FRUCHART Robert HOPFINGER Emile JORRAND Philippe LANDAU Ioan VACHAUD Georges VERJUS Jean-Pierre

**VINCENT Henri**

#### Directeurs de recherche 2ème Classe

ALEMANY Antoine

ALLIBERT Colette

ALLIBERT Michel

ANSARA Ibrahim

ARMAND Michel

BERNARD Claude

BINDER Gilbert

BONNET Roland

BORNARD Guy

CAILLET Marcel

CALMET Jacques

COURTOIS Bernard

DAVID René

**DRIOLE Jean ESCUDIER Pierre EUSTATHOPOULOS Nicolas GUELIN Pierre** JOUD Jean-Charles **KLEITZ Michel KOFMAN Walter** KAMARINOS Georges LEJEUNE Gérard LE PROVOST Christian MADAR Roland MERMET Jean MICHEL Jean-Marie **MUNIER Jacques** PIAU Monique SENATEUR Jean-Pierre SIFAKIS Joseph SIMON Jean-Paul **SUERY Michel TEODOSIU Christian VAUCLIN Michel** WACK Bernard

### Personnalités agrées à titre permanent à diriger des travaux de recherche (décision du conseil scientifique)

E.N.S.E.E.G

CHATILLON Christian

HAMMOU Abdelkader

MARTIN GARIN Régina

SARRAZIN Pierre

SIMON Jean-Paul

E.N.S.E.R.G

**BOREL Joseph**

E.N.S.I.E.G

DESCHIZEAUX Pierre GLANGEAUD François PERARD Jacques REINISCH Raymond

E.N.S.H.G

**ROWE Alain**

E.N.S.J.M.A.G

**COURTIN Jacques**

E.F.P.

**CHARUEL Robert**

C.E.N.G

CADET Jean

COEURE Philippe

DELHAYE Jean-Marc

DUPUY Michel

JOUVE Hubert

NICOLAU Yvan

NIFENECKER Hervé

PERROUD Paul

PEUZIN Jean-Claude

TAIB Maurice

VINCENDON Marc

Laboratoires extérieurs C.N.E.T

DEVINE Rodericq GERBER Roland MERCKEL Gérard PAULEAU Yves

# **UNIVERSITE Joseph FOURIER (GRENOBLE I)**

## Président de l'Université : M. PAYAN Jean Jacques

#### Année Universitaire 1987 - 1988

## MEMBRES DU CORPS ENSEIGNANT DE SCIENCES ET DE GEOGRAPHIE

#### PROFESSEURS DE 1ère Classe

ARNAUD Paul ARVIEU ROBERT AUBERT Guy

**AURIAULT Jean-Louis**

**AYANT** Yves

BARBIER Marie-Jeanne BARJON Robert

BARNOUD Fernand BARRA Jean-René BECKER Pierre BEGUIN Claude BELORISKY Elie

BENZAKEN Claude BERARD Pierre BERNARD Alain

BERTRANDIAS Françoise BERTRANDIAS Jean-Paul

**BILLET Jean**

BOELHER Jean-Paul BONNIER Jane Marie BOUCHEZ Robert BRAVARD Yves CARLIER Georges CAUQUIS Georges CHARDON Michel CHIBON Pierre

COHEN ADDAD Jean-Pierre COLIN DE VERDIERE Yves

CYROT Michel

DEBELMAS Jacques

DEGRANGE Charles

DEMAILLY Jean-Pierre

DENEUVILLE Alain

DEPORTES Charles

DOLIQUE Jean-Michel

DOUCE Roland

DUCROS Pierre

FONTAINE Jean-Marc

GAGNAIRE Didier

GERMAIN Jean-Pierre

GIRAUD Pierre HICTER Pierre IDELMAN Simon JANIN Bernard JOLY Jean-René

KAHANE André, détaché KAHANE Josette KRAKOWIAK Sacha Chimie Organique

Physique Nucléaire I.S.N.

Physique C.N.R.S

Mécanique

Physique Approfondie

Electrochimie

Physique Nucléaire ISN

Biochimie Macromoléculaire Végétale Statistiques-Mathématiques Appliquées

Physique

Chimie Organique

Physique

Mathématiques Pures Mathématiques Pures Mathématiques Pures Mathématiques Pures Mathématiques Pures

Géographie Mécanique Chimie Générale Physique Nucléaire ISN

Géographie

Biologie Végétale

Chimie Organique

Géographie

Biologie Animale

Physique

Mathématiques Pures Physique du Solide Géologie Générale

Zoologie

Mathématiques Pures

Physique

Chimie Minérale

Physique des Plasmas

Physiologie Végétale

Cristallographie

Mathématiques Pures

Chimie Physique

Mécanique,

Géologie

Chimie

Physiologie Animale

Géographie

Mathématiques Pures

Physique Physique

Mathématiques Appliquées

LAJZEROWICZ Jeanine Physique LAJZEROWICZ Joseph Physique

LAURENT Pierre-Jean Mathématiques Appliquées

LEBRETON Alain Mathématiques Appliquées

DE LEIRIS Joël Biologic

LHOMME Jean Chimie

LLIBOUTRY Louis Géophysique

LOISEAUX Jean-Marie Sciences Nucléaires I.S.N.

LUNA Domingo Mathématiques Pures

MACHE Régis Physiologie Végétale

MASCLE Georges Géologie

MAYNARD Roger Physique du Solide OMONT Alain Astrophysique

OZENDA Paul Botanique (Biologie Végétale)

PAYAN Jean-Jacques Mathématiques Pures

PEBAY-PEYROULA Jean-Claude Physique Géophysique

PIERRARD Jean-Marie Mécanique

PIERRE Jean-Louis Chimie Organique

RENARD Michel Thermodynamique

RINAUDO Marguerite CERMAV

ROSSI André Biologic

SAXOD Raymond Biologie Animale

SENGEL Philippe Biologie Animale

SERGERAERT Francis Mathématiques Pures

SOUCHIER Bernard Biologic

SOUTIF Michel Physique

STUTZ Pierre Mécanique

TRILLING Laurent Mathématiques Appliquées

VALENTIN Jacques Physique Nucléaire I.S.N.

VAN CUTSEM Bernard Mathématiques Appliquées

VIALON Picrre Géologie

#### PROFESSEURS de 2<sup>ème</sup> Classe

ADIBA Michel Mathématiques Pures

ANTOINE Pierre Géologie

ARMAND Gilbert Géographie

BARET Paul Chimie

BLANCHI J.Pierre STAPS

BLUM Jacques Mathématiques Appliquées

BOITET Christian Mathématiques Appliquées

BORNAREL Jean Physique

BRUANDET J.François Physique

BRUGAL Gérard Biologie

BRUN Gilbert Biologie

CASTAING Bernard Physique

CERFF Rudiger Biologie

CHIARAMELLA Yves Mathématiques Appliquées

COURT Jean Chimic

DUFRESNOY Alain Mathématiques Pures

GASPARD François

GAUTRON René

GENIES Eugène

GIDON Maurice

Chimic

Géologic

GIGNOUX Claude Sciences Nucléaires

GILLARD Roland Mathématiques Pures

GIORNI Alain Sciences Nucléaires

GONZALEZ SPRINBERG Gérardo Mathématiques Pures

GUIGO Maryse Géographie

GUMUCHAIN Hervé Géographie

GUITTON Jacques Chimie

**HACOUES Gérard HERBIN Jacky HERAULT Jeanny JARDON Pierre JOSELEAU Jean-Paul KERCKHOVE Claude**

LONGEOUEUE Nicole

**LUCAS Robert** MANDARON Paul **MARTINEZ Francis**

**NEMOZ Alain**

**OUDET Bruno PECHER Arnaud PELMONT Jean PERRIN Claude**

**PFISTER Jean-Claude** PIBOULE Michel

**RAYNAUD Hervé**

**RICHARD Jean-Marc RIEDTMANN Christine**

**ROBERT Gilles ROBERT Jean-Bernard** SARROT-REYNAULD Jean

**SAYETAT Françoise SERVE Denis** STOECKEL Frédéric **SCHOLL Pierre-Claude**

**SUBRA Robert** VALLADE Marcel VIDAL Michel

**VIVIAN Robert VOTTERO Philippe**  Mathématiques Appliquées

Géographie **Physique** Chimie **Biochimie** Géologie

Sciences Nucléaires I.S.N.

**Physique** Biologie

Mathématiques Appliquées

Thermodymamique CNRS - CRTBT

Mathématiques Appliquées

Géologie **Biochimie**

Sciences Nucléaires I.S.N.

Physique du Solide

Géologie

Mathématiques Appliquées

Physique

Mathématiques Pures Mathématiques Pures Chimie Physique

Géologie **Physique** Chimie **Physique**

Mathématiques Appliquées

Chimie **Physique**

Chimie Organique Géographie Chimie

#### MEMBRES DU CORPS ENSEIGNANT DE L'IUT 1

#### PROFESSEURS de 1ère Classe

**BUISSON Roger DODU Jacques NEGRE Robert NOUGARET Marcel**

**PERARD Jacques**

Physique IUT 1

Mécanique Appliquée IUT 1

Génie Civil IUT 1 Automatique IUT 1 EEA. IUT 1

#### PROFESSEURS de 2 ème classe

**BOUTHINON Michel CHAMBON René**

**CHEHIKIAN Alain CHENAVAS Jean CHOUTEAU Gérard CONTE René GOSSE Jean-Pierre**

**GROS Yves** KUHN Gérard, (Détaché)

**MAZUER Jean** MICHOULIER Jean MONLLOR Christian PEFFEN René PERRAUD Robert PIERRE Gérard

TERRIEZ Jean-Michel **TOUZAIN Philippe**

**VINCENDON Marc**

EEA. IUT 1

Génie Mécanique IUT 1

EEA. IUT 1 Physique IUT 1 Physique IUT 1 Physique IUT 1 **EEA.IUT 1** Physique IUT 1 Physique IUT 1 Physique IUT 1 Physique IUT 1 EEA.IUT 1 Métallurgie IUT 1

Chimie IUT 1 Chimie IUT 1

Génie Mécanique IUT 1

Chimie IUT 1 Chimie IUT 1

# PROFESSEURS DE PHARMACIE

| AGNIUS-DELORD Claudine   | Physique                     | Faculté La Tronche |

|--------------------------|------------------------------|--------------------|

| ALARY Josette            | Chimie Analytique            | Faculté La Tronche |

| BERIEL Hélène            | Physiologie et Pharmacologie | Faculté La Tronche |

| CUSSAC Max               | Chimie Therapcutique         | Faculté La Tronche |

| DEMENGE Pierre           | Pharmacodynamie              | Faculté La Tronche |

| FAVIER Alain             | Biochimie                    | C.H.R.G.           |

| JEANNIN Charles          | Pharmacie Galénique          | Faculté Meylan     |

| LATURAZE Jean            | Biochimie                    | Faculté La Tronche |

| LUU DUC Cuong            | Chimie Générale              | Faculté La Tronche |

| MARIOTTE Anne-Marie      | Pharmacognosie               | Faculté La Tronche |

| MARZIN Daniel            | Toxicologie                  | Faculté Meylan     |

| RENAUDET Jacqueline      | Bactériologie                | Faculté La Tronche |

| ROCHAT Jacques           | Hygiéne et Hydrologie        | Faculté La Tronche |

| SEIGLE-MURANDI Françoise | Botanique et Cryptogamie     | Faculté Meylan     |

| VERAIN Alice             | Pharmacie Galénique          | Faculté Meylan     |

## MEMBRES DU CORPS ENSEIGNANT DE MEDECINE

## PROFESSEURS CLASSE EXEPTIONNELLE ET 1ère CLASSE

| AMBLARD Pierre         | Dermatologie                    | C.H.R.G.         |

|------------------------|---------------------------------|------------------|

| AMBROISE-THOMAS Pierre | Parasitologie                   | C.H.R.G.         |

| BEAUDOING André        | Pédiatrie-Puericulture          | C.H.R.G.         |

| BEZEZ Henri            | Orthopédie-Traumatologie        | Hopital SUD      |

| BONNET Jean-Louis      | Ophtalmologie                   | C.Ĥ.R.G.         |

| BOUCHET Yves           | Anatomie                        | Faculté La Merci |

|                        | Chirurgie Générale et Digestive | C.H.R.G.         |

| BUTEL Jean             | Orthopédie-Traumatologie        | C.H.R.G.         |

| CHAMBAZ Edmond         | Biochimie                       | C.H.R.G.         |

| CHAMPETIER Jean        | Anatomie-Topographique          |                  |

| •                      | et Appliquée                    | C.H.R.G.         |

| CHARACHON Robert       | O.R.L.                          | C.H.R.G.         |

| COLOMB Maurice         | Immunologie                     | Hopital sud      |

| COUDERC Pierre         | Anatomie-Pathologique           | C.H.R.G.         |

| DELORMAS Pierre        | Pneumophtisiologie              | C.H.R.G.         |

| DENIS Bernard          | Cardiologie                     | C.H.R.G.         |

| GAVEND Michel          | Pharmacologie                   | Faculté La Merci |

| HOLLARD Daniel         | Hématologie                     | C.H.R.G.         |

| LATREILLE René         | Chirurgie Thoracique et         |                  |

|                        | Cardiovasculaire                | C.H.R.G.         |

| LE NOC Pierre          | Bactériologie-Virologie         | C.H.R.G.         |

| MALINAS Yves           | Gynécologie et Obstétrique      | C.H.R.G.         |

| MALLION Jean-Michel    | Médecine du Travail             | C.H.R.G.         |

| MICOUD Max             | Clinique Médicale et Maladies   |                  |

|                        | Infectieuses                    | C.H.R.G.         |

| MOURIQUAND Claude      | Histologie                      | Faculté La Merci |

| PARAMELLE Bernard      | Pneumologie                     | C.H.R.G.         |

| PERRET Jean            | Neurologie                      | C.H.R.G.         |

| RACHAIL Michel         | Hépato-Gastro-Entérologie       | C.H.R.G.         |

| DE ROUGEMONT Jacques   | Neurochirurgie                  | C.H.R.G.         |

| SARRAZIN Roger         | Clinique Chirurgicale           | C.H.R.G.         |

| STIEGLITZ Paul         | Anestésiologie                  | C.H.R.G.         |

| TANCHE Maurice         | Physiologie                     | Faculté La Merci |

| VIGNAIS Pierre         | Biochimie                       | Faculté La Merci |

# PROFESSEURS 2ème CLASSE

|                           |                                  | OHD C            |

|---------------------------|----------------------------------|------------------|

| BACHELOT Yvan             | Endocrinologie                   | C.H.R.G.         |

| BARGE Michel              | Neurochirurgie                   | C.H.R.G.         |

| BENABID Alim Louis        | Biophysique                      | Faculté La Merci |

| BENSA Jean-Claude         | Immunologie                      | Hopital Sud      |

| BERNARD Pierre            | Gynécologie-Obstétrique          | C.H.R.G.         |

| BESSARD Germain           | Pharmacologie                    | ABIDJAN          |

| BOLLA Michel              | Radiothérapie                    | C.H.R.G.         |

| BOST Michel               | Pédiatrie                        | C.H.R.G.         |

| BOUCHARLAT Jacques        | Psychiatrie Adultes              | Hopital Sud      |

| BRAMBILLA Christian       | Pneumologie                      | C.H.R.G.         |

| CHIROSSEL Jean-Paul       | Anatomie-Neurochirurgie          | C.H.R.G.         |

| COMET Michel              | Biophysique                      | Faculté La Merci |

| CONTAMIN Charles          | Chirurgie Thoracique et          |                  |

|                           | Cardiovasculaire                 | C.H.R.G.         |

| CORDONNIER Daniel         | Néphrologie                      | C.H.R.G.         |

| COULOMB Max               | Radiologie                       | C.H.R.G.         |

| CROUZET Guy               | Radiologie                       | C.H.R.G.         |

| DEBRU Jean-Luc            | Médecine Interne et Toxicologie  | C.H.R.G.         |

| DEMONGEOT Jacques         | Biostatistiques et Informatique  | Faculté La Merci |

| -                         | Médicale                         |                  |

| DUPRE Alain               | Chirurgie Générale               | C.H.R.G.         |

| DYON Jean-François        | Chirurgie Infantile              | C.H.R.G.         |

| ETERRADOSSI Jacqueline    | Physiologie                      | Faculté La Merci |

| FAURE Claude              | Anatomie et Organogénèse         | C.H.R.G.         |

| FAURE Gilbert             | Urologie                         | C.H.R.G.         |

| FOURNET Jacques           | Hépato-Gastro-Entérologie        | C.H.R.G.         |

| FRANCO Alain              | Médecine Interne                 | C.H.R.G.         |

| GIRARDET Pierre           | Anesthésiologie                  | C.H.R.G.         |

| GUIDICELLI Henri          | Chirurgie Générale et Vasculaire | C.H.R.G.         |

| GUIGNIER Michel           | Thérapeutique et Réanimation     |                  |

|                           | Médicale                         | C.H.R.G.         |

| HADJIAN Arthur            | Biochimie                        | Faculté La Merci |

| HALIMI Serge              | Endocrinologie et Maladies       |                  |

|                           | Métaboliques                     | C.H.R.G.         |

| HOSTEIN Jean              | Hépato-Gastro-Entérologie        | C.H.R.G.         |

| HUGONOT Robert            | Médecine Interne                 | C.H.R.G.         |

| JALBERT Pierre            | Histologie-Cytogénétique         | C.H.R.G.         |

| JUNIEN-LAVILLAUROY Claude | O.R.L.                           | C.H.R.G.         |

| KOLODIE Lucien            | Hématologie Biologique           | C.H.R.G.         |

| LETOUBLON Christian       | Chirurgie Générale               | C.H.R.G.         |

| MACHECOURT Jacques        | Cardiologie et Maladies          |                  |

| •                         | Vasculaires                      | C.H.R.G.         |

| MAGNIN Robert             | Hygiène                          | C.H.R.G.         |

| MASSOT Christian          | Médecine Interne                 | C.H.R.G.         |

| MOUILLON Michel           | Ophtalmologie                    | C.H.R.G.         |

| PELLAT Jacques            | Neurologie                       | C.H.R.G.         |

| PHELIP Xavicr             | Rhumatologie                     | C.H.R.G.         |

| RACINET Claude            | Gynécologie-Obstétrique          | Hopital Sud      |

| RAMBAUD Pierre            | Pédiatrie                        | C.H.R.G.         |

| RAPHAEL Bernard           | Stomatologie                     | C.H.R.G.         |

| SCHAERER René             | Cancérologie                     | C.H.R.G.         |

| SEIGNEURIN Jean-Marie     | Bactériologie-Virologie          | Faculté La Merci |

| SELE Bernard              | Cytogénétique                    | Faculté La Merci |

| SOTTO Jean-Jacques        | Hématologie                      | C.H.R.G.         |

| STOEBNER Pierre           | Anatomie Pathologique            | C.H.R.G.         |

| VROUSOS Constantin        | Radiothérapie                    | C.H.R.G.         |

| 1100000 Collomium         |                                  | •                |

#### **AVANT PROPOS**

Tout d'abord, qu'il me soit permis d'adresser ma reconnaissance à Monsieur **B.Courtois** pour la confiance qu'il m'a témoignée en m'accueillant dans son laboratoire et pour avoir dirigé avec compétence tout ce travail.

Que monsieur **G.Mazare** Professeur à l'ENSIMAG, trouve ici l'expression de ma gratitude pour l'intérêt qu'il a porté à ce travail en me faisant l'honneur de présider le jury de cette thèse.

Monsteur **G.Chambon**, Professeur à l' Université des science et technique du languedoc et Monsteur **J.Frehel**, Directeur de recherche à SGS-Thompson ont bien voulu mobiliser leur temps et leurs compétences pour juger ce travail; je tiens à les assurer de mes sincères remerciements.

Que tous mes collègues de laboratoire trouvent ici ma gratitude pour l'ambiance sympathique et amicale de travail. Un grand merci à **M.Nicolaidis et K.Torki** pour les fructueuses discussions que nous avons tenues pendant toutes ces années.

Enfin, je ne saurais oublier les amis Armand, Habiba, Bassan, Denis, Dominique, Chiên, Mohamad, Meryem, Jean Pierre, Isabelle, Fernando, Jayne, Aarão, Ana, Afonso, Renata, Vladimir et Lilian. Je vous suis infiniment reconnaissant.

à Rosana et Nicolas

•

#### RESUME.

Dans ce travail, nous avons effectué une étude complète de la testabilité des PLAs. Pour les trois classes de test (hors ligne, en ligne et unifié) nous avons proposé des schémas de test dont la compatibilité avec les PLAs optimisés a été étudiée.

En ce qui concerne le test hors ligne, le schéma de test proposé apporte une amélioration vis-a-vis des schémas publiés dans la littérature tout en gardant la compatibilité avec les PLAs optimisés.

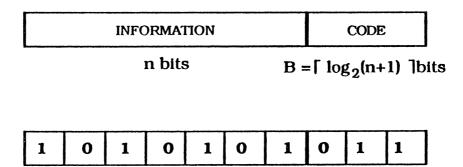

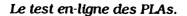

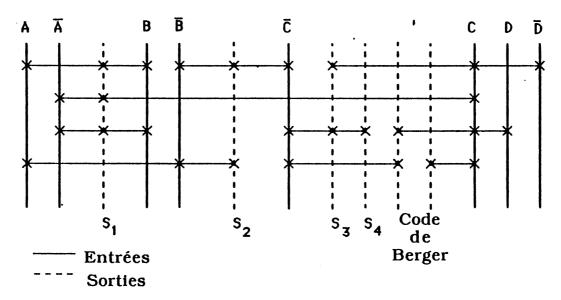

En ce qui concerne le test en ligne, l'application de deux schémas de test aux PLAs optimisés a été analysée: le schéma utilisant des codes non ordonnés et le schéma utilisant des codes détectant des erreurs simples. Un nouvel algorithme pour la génération des codes non ordonnés a été proposé.

En ce qui concerne le test unifié, le test en ligne est assuré par la méthode utilisant des codes non ordonnés. Deux méthodes sont proposées pour la génération des vecteurs d'entrée pendant le test hors ligne: le test exhaustif et le test déterministe.

#### **MOTS-CLES:**

PLA, Circuits autotestables, Circuits autocontrôlables, Test en ligne, Test hors ligne, Test unifié, Test, Test integré.

## **ABSTRACT**

This Thesis deals with testability of the folded PLAs. We propose a testing scheme for each class of the test (off-line, on-line and unified BIST). Their application on the topological optimization cases are discussed in detail. The constraints inherent to these applications are given.

In the off-line testing, the proposed testing scheme is an improvement over other existing schemes and it is convenient for topologically optimized PLAs.

In the on-line testing, two testing schemes are examined: the testing scheme using the unordered code and the testing scheme using the single error detecting code. A new algorithm is proposed to generate the unordered code.

In the UBIST (Unified Built-In Self-Test) the on-line testing is ensured by the method using the unordered code. The input pattern generation in the off-line phase can be ensured by two methods: determinist testing and exhaustive testing.

## **Keywords:**

PLAs, folding, self-checking systems, UBIST.

#### **SOMMAIRE**

| 1 - INTRODUCTION.                                    |      |

|------------------------------------------------------|------|

| 1.1 - GENERALITES                                    | 3    |

| 1.2 - LES HYPOTHESES DE PANNES:                      | 6    |

|                                                      |      |

| 2 - TECHNIQUES D'OPTIMISATION DES PLAS.              |      |

| 2.1 - GENERALITES                                    | , 11 |

| 2.1.1 - Representation des PLAs au niveau structurel | 12   |

| 2.2 - OPTIMISATION EN SURFACE DES PLAS               | 15   |

| 2.2.1 - Le pliage simple                             | 17   |

| 2.2.2 - Le pliage multiple                           | 20   |

| 2.2.3 - La technique "PAOLA"                         | 22   |

|                                                      |      |

| 3 - LE TEST HORS LIGNE DES PLAS.                     |      |

| 3.1 - GENERALITES                                    | 29   |

| 3.1.1 - Les PLAs facilement testables                | 30   |

| 3.1.2 - Les PLAs fonctionnellement testables         | 32   |

| 3.1.3 - Les PLAs autotestables (première classe)     | 34   |

| 3.1.4 - Les PLAs autotestables (deuxième classe)     | 35   |

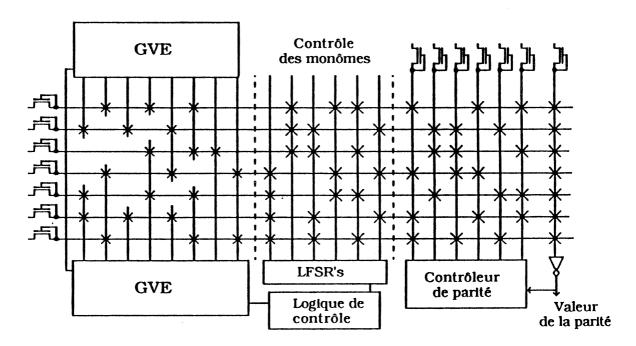

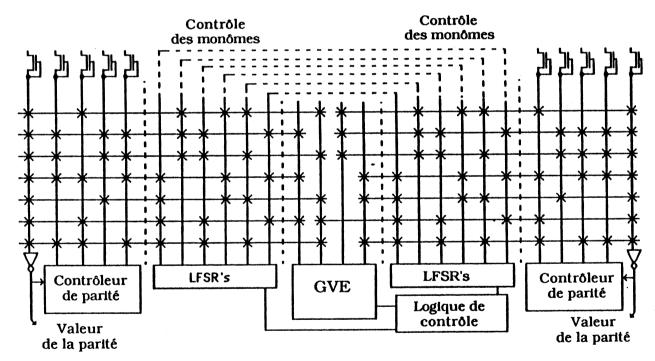

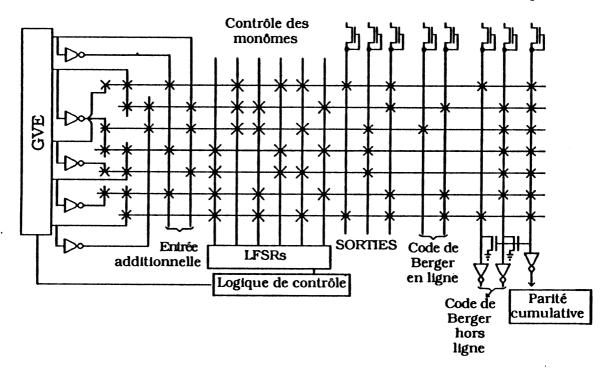

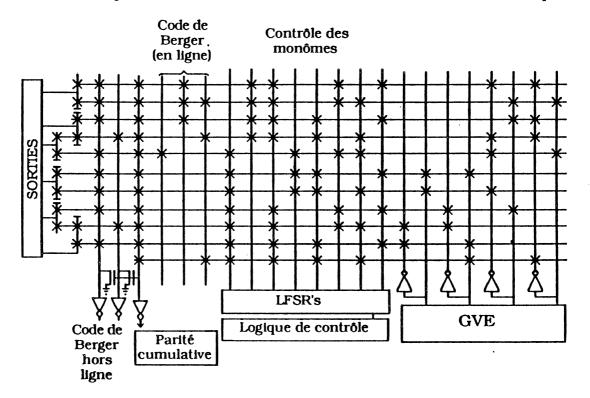

| 3.2 - SCHEMA DE TEST PROPOSE                         | 39   |

| 3.2.1 - Générateur des vecteurs d'entrée             | 40   |

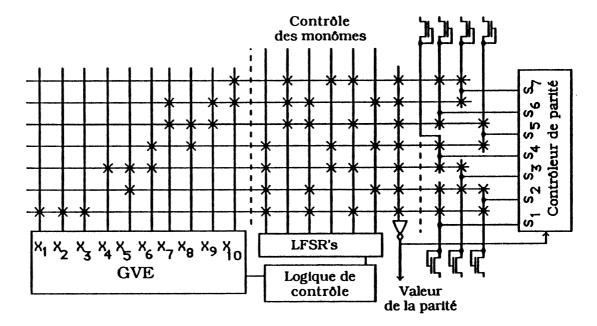

| 3.2.2 - Contrôle des monômes                         | 42   |

| 3.2.3 - Compression des vecteurs de sortie           | 43   |

| 3.2.4 - Logique de contrôle                          | 46   |

| 3.3 - COMPARAISON DES DIFFERENTES METHODES                 | 47         |

|------------------------------------------------------------|------------|

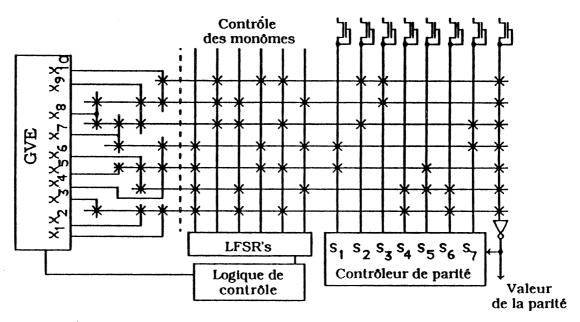

| 3.4 - APPLICATION AUX PLAS OPTIMISES TOPOLOGIQUEMENT       | 49         |

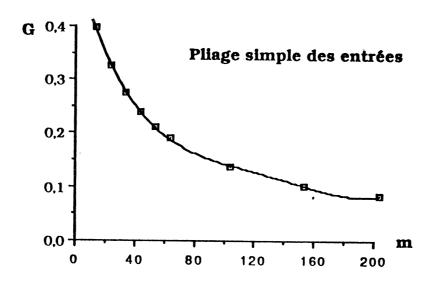

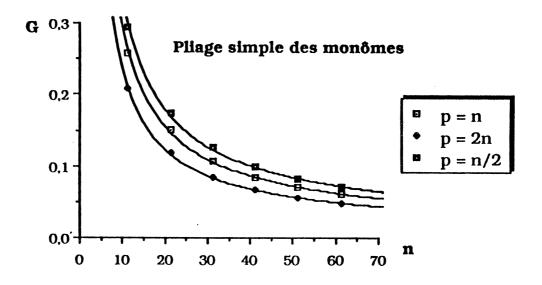

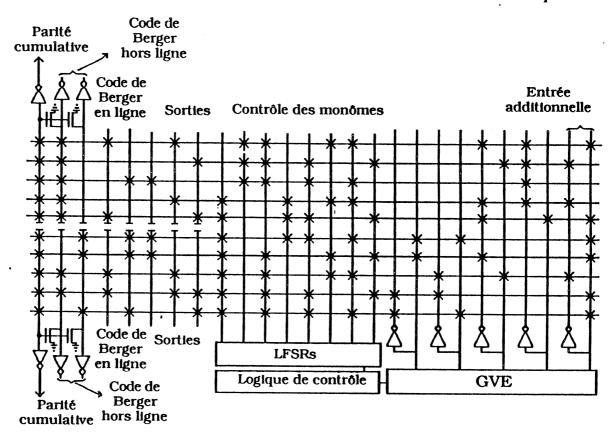

| 3.4.1 - Le pliage simple des entrées                       | 50         |

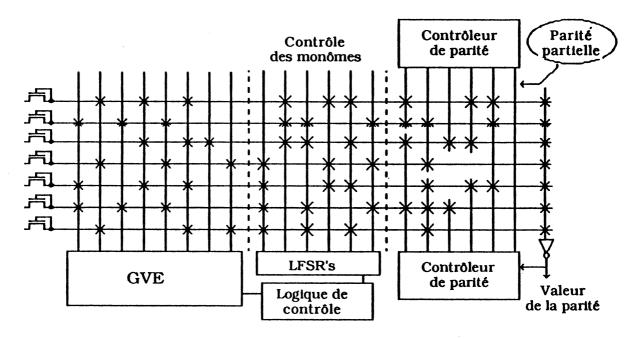

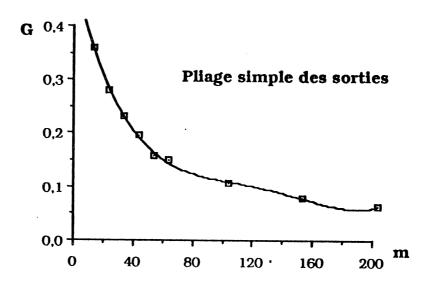

| 3.4.2 - Le pliage simple des sorties                       | 52         |

| 3.4.3 - Le pliage simple des monômes                       | 54         |

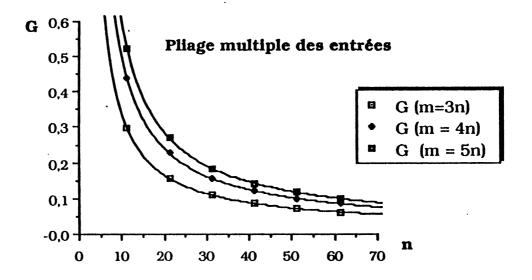

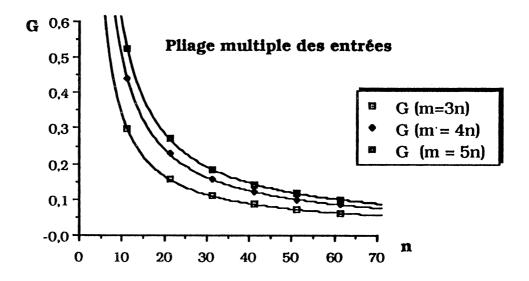

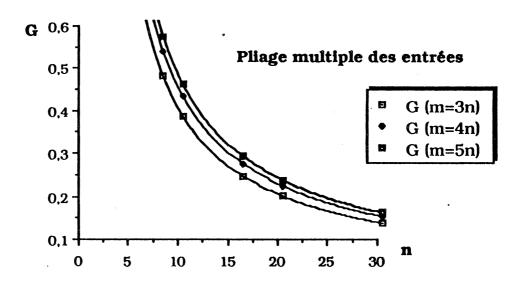

| 3.4.4 - Le pliage multiple des entrées                     | 56         |

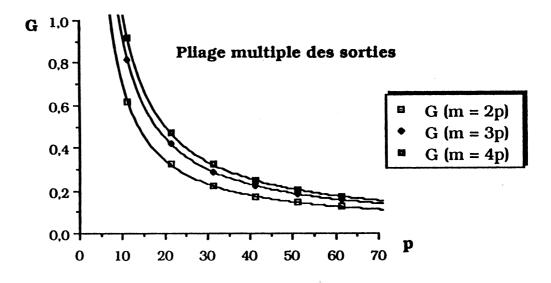

| 3.4.5 - Le pliage multiple des sorties                     | 58         |

| 3.5 - CONCLUSION                                           | 60         |

|                                                            |            |

| 4 - LE TEST EN LIGNE DES PLAS.                             |            |

| 4.1 - GENERALITES                                          | 65         |

| 4.2 - CODES                                                | 7]         |

| 4.2.1 - Code de parité                                     | 7]         |

| 4.2.2 - Code de Berger.                                    | 72         |

| 4.2.3 - Codes k parmi n                                    | 73         |

| 4.2.4 - Codes à duplication                                | <b>7</b> 3 |

| 4.3 - PLAs SFS                                             | 74         |

| 4.3.1 - PLAs SFS utilisant des codes non ordonnés          | 75         |

| 4.3.2 - PLAs SFS utilisant des codes détectant des erreurs |            |

| simples                                                    | 76         |

| 4.4 - GENERATION DES CODES NON ORDONNES                    | 78         |

| 4.5 - APPLICATION AUX PLAS OPTIMISES TOPOLOGIQUEMENT       | 82         |

| 4.5.1 - Le pliage simple des entrées                       | 82         |

| 4.5.2 - Le pliage simple des monômes                       | 83         |

| 4.5.3 - Le pliage simple des sorties                       | 85         |

| 4 5 4 - Le pliage multiple des entrées                     | 88         |

| 4.5.5 - Le pliage multiple des monômes                | 88   |

|-------------------------------------------------------|------|

| 4.5.6 - Le pliage multiple des sorties                | 89   |

| 4.6 - CONCLUSION                                      | 90   |

|                                                       |      |

| 5 - LE TEST UNIFIE DES PLAs.                          |      |

| 5.1 - GENERALITES                                     | 93   |

| 5.2 - SCHEMA A TEST DETERMINISTE                      | 93   |

| 5.3 - SCHEMA A TEST EXHAUSTIF                         | 97   |

| 5.4 - COMPARAISON DES DEUX SCHEMAS                    | 101  |

| 5.5 - APPLICATION AUX PLAS OPTIMISES TOPOLOGIQUEMENT  | 102  |

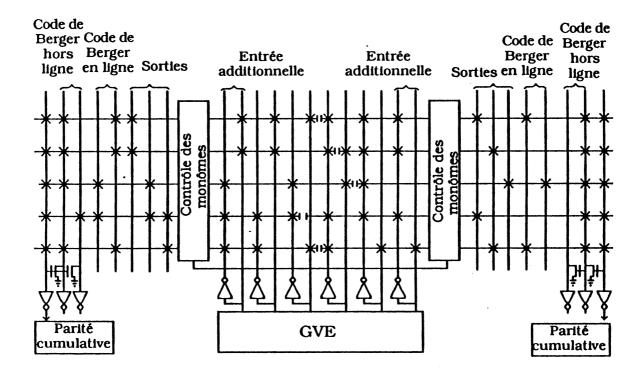

| 5.5.1 - Le pliage simple des entrées                  | .103 |

| 5.5.2 - Le pliage simple des sorties                  | 105  |

| 5.5.3 - Le pliage simple des monômes                  | 106  |

| 5.5.4 - Le pliage multiple des entrées                | 107  |

| 5.5.5 - Le pliage multiple des sorties                | .109 |

| 5.6 - CONCLUSION                                      | 110  |

| 6 - CONCLUSION                                        | 113  |

| 7 - BIBLIOGRAPHIE.                                    | 119  |

| ANNEXE 1: SURFACE DU GENERATEUR DES VECTEURS D'ENTREE | 127  |

| ANNEXE 2: SURFACE DU CONTROLEUR DE PARITE             | 129  |

| ANNEXE 3: COUVERTURE DES PANNES TEST HORS LIGNE       | 131  |

| ANNEXE 4: EXEMPLE DE PLA CODE                         | 137  |

| ANNEXE 5: COUVERTURE DES PANNES TEST UNIFIE           | 147  |

INTRODUCTION

• • •

#### 1 - INTRODUCTION.

#### 1.1 - GENERALITES.

Les circuits VLSI conçus actuellement sont marqués par une très grande complexité due au nombre de transistors qu'ils comportent ainsi qu'aux fonctions qu'ils réalisent. La conception de ces circuits doit impérativement utiliser non seulement des outils de conception assistée par ordinateur (CAO) mais aussi des structures régulières. Les RAMs (Random Acess Memories), ROMs (Read-Only Memories) et PLAs (Programmable Logic Arrays) sont les structures régulières le plus utilisées et tout particulièrement les PLAs qui sont de puissantes structures pour l'implantation de multiples fonctions combinatoires. Leur structure contient seulement deux niveaux logiques, ce qui simplifie les processus de conception et de vérification. En outre, il est relativement simple d'implanter une structure testable. Par contre, la surface qu'ils occupent par rapport à la logique anarchique limite leur utilisation. Pour résoudre ce problème, c'est-à-dire, pour augmenter l'application des PLAs, des techniques d'optimisation ont été développées. L'optimisation logique permet l'élimination des entrées, sorties et monômes redondants ainsi que la réduction du taux de remplissage i.e. du nombre de transistors dans les deux matrices du PLA. L'optimisation topologique réorganise la structure interne des PLAs pour obtenir un gain de surface soit par la technique de brisure (folding) soit par la technique de partitionnement. Ceci permet non seulement de diminuer la surface et la consommation, mais aussi d'augmenter la vitesse des PLAs tout en élargissant leur champ d'utilisation. En effet, les compromis de temps, de surface et de consommation dans les circuits intégrés sont très importants. Par conséquent les structures qui occupent une grande surface, tout en ayant une forte consommation ou dont la vitesse de commutation est faible ont une utilisation assez limitée.

Un autre facteur important dans les circuits actuels est la testabilité. Le test exhaustif (i.e. l'application de 2<sup>n</sup> vecteurs sur un circuit à n entrées) peut être facilement appliqué pour des circuits ayant un faible nombre d'entrées, mais dès que ce nombre augmente il est impossible de tester le circuit de cette manière en un temps raisonnable. Plusieurs solutions sont données pour résoudre ce problème telles que le partitionnement du

circuit en sous circuits ou bien l'emploi d'un test déterministe (i.e. appliquer au circuit un ensemble de vecteurs capables de mettre en évidence une panne modélisée). La première solution suppose que nous ayons accès à ces sous circuits et la deuxième présente des problèmes pour la détermination des vecteurs ce qui entraîne un faible taux de couverture de pannes.

Cela fait apparaître de nouvelles classes de circuits conçus avec des facilités de test (Design For Testability - DFT) ou même des circuits à test intégré (Built-In Self Test - BIST). Ces circuits sont apparus grâce à l'augmentation de la capacité d'intégration.

Plusieurs niveaux de test peuvent être considérés dans les circuits intégrés.

Après la conception, il est nécessaire de s'assurer que les fonctions réalisées par le circuit sont bien les fonctions que nous voulons implanter et que le circuit fonctionne comme nous l'avons prévu. Il s'agit de la validation de la conception, elle est faite en testant des prototypes.

Après la fabrication, il faut éliminer les circuits défectueux et périodiquement effectuer des tests de maintenance pour les circuits assemblés sur des cartes.

Pendant le fonctionnement normal du circuit, il est important de détecter une panne avant sa propagation dans d'autres parties du système.

Ainsi les méthodes de test peut être divisées en deux catégories:

- Le test hors ligne et

- Le test en-ligne.

Le test hors ligne est réalisé hors le fonctionnement normal du circuit. Il peut être divisé en deux catégories:

- Le test paramétrique et

- Le test logique.

Dans le premier cas, les différents paramètres qui caractérisent le circuit, tels que la tension de seuil, le courant. l'impédance, etc. (paramètres statiques) et le temps de commutation, les délais, etc. (paramètres dynamiques) sont mesurés. Dans le deuxième cas, le fonctionnement logique est vérifié. Ce test permet de détecter des fautes permanentes pour

l'acceptation initiale ou pour le test de maintenance du système. Lors du test hors ligne, le fonctionnement normal du circuit est interrompu et une séquence de test est appliquée. Les sorties sont contrôlées pour détecter une possible erreur. Dans notre travail nous étudierons le test logique pour les PLAs.

Le test en ligne est réalisé pendant le fonctionnement normal du circuit. Il peut aussi être divisé en deux catégories:

- Le test en ligne discontinu et

- Le test en ligne continu.

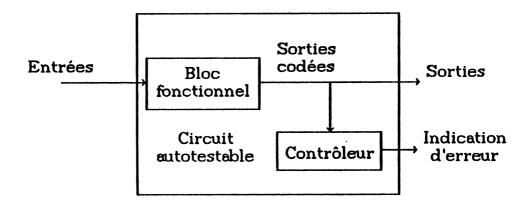

Le test en ligne discontinu exécute des procédures de test spécifiques quand le circuit n'a aucune tâche fonctionnelle à exécuter. Le test en ligne continu assure la détection d'erreurs pendant l'exécution d'une tâche quelconque. Il est utilisé pour surveiller le système pendant son fonctionnement normal. Dans ce cas toutes les fautes, permanentes et intermittentes peuvent être détectées. Les circuits qui assurent la détection d'erreur en ligne sont appelés "self checking". Dans notre travail nous étudierons le test en ligne continu pour les PLAs.

Une nouvelle classe proposée par NICOLAIDIS [NIC 86], appelé UBIST (Unified Built-In Self Test), associe le test hors ligne et le test en ligne. Ainsi tous les tests nécessaire à un système VLSI sont assurés. En effet le test en ligne et le test hors ligne ont été développés indépendament l'un de l'autre. Pour pouvoir exploiter au maximum les avantages que l'un pourrait apporter à l'autre il faut développer des nouvelles méthodes. Il est important de remarquer que généralement les propriétés des "circuits self-checking" sont vérifiées pour des fautes simples mais des fautes multiples peuvent se produirent spécialement après le processus de fabrication. Il est donc nécessaire de s'assurer que les pannes multiples seront détectées avant l'utilisation du circuit, par le test hors ligne. Ainsi le schéma unifié offre une plus haute couverture de fautes et assure un test de très haute qualité.

Dans ce travail le test des PLAs est étudié. Nous avons abouti à des schémas optimisés par rapport aux schémas proposés dans la littérature et ces schémas sont compatibles avec les PLAs optimisés topologiquement.

Le chapitre 2 présente les différentes méthodes d'optimisation des PLAs.

Le test hors ligne des PLAs est exposé dans le chapitre 3. Un bref apperçu des diverses méthodes exposées dans la littérature est fait avant la proposition d'un schéma. Dans ce schéma trois caractéristiques sont prises en compte:

- La compatibilité avec les PLAs optimisés,

- La surface additionnelle et

- La couverture des fautes.

Ce schéma est une amélioration des schémas existants et il reste compatible avec la structure des PLAs optimisés. L'application de ce schéma aux PLAs optimisés est aussi détaillée.

Le test en ligne est exposé dans le chapitre 4. Une revue des schémas de test proposés dans la littérature est faite et son application dans les PLAs optimisés est démontrée. Une nouvelle méthode pour la génération du codage des sorties est proposée et des exemples d'application sont donnés.

Le test unifié est exposé dans le chapitre 5. Les modifications nécessaires à la logique additionnelle sont montrées ainsi que l'application du schéma de test aux PLAs optimisés. Le test exhaustif est utilisé pour les PLAs ayant un faible nombre d'entrées.

La couverture de faute de chaque schéma est donnée dans les annexes.

Les règles de dessin utilisées dans ce travail sont celle proposées par MEAD et CONWAY [MEA 80].

La terminologie utilisée est la suivante:

- n nombre d'entrées,

- m nombre de monômes et

- p nombre de sorties.

#### 1.2 - LES HYPOTHESES DE PANNES.

La conception des circuits autotestables nécessite un modèle de panne qui représente les défaillances réelles. Il est nécessaire de considérer les défauts physiques qui surviennent dans une technologie donnée. Puisque ces défauts physiques sont généralement connus, il est raisonnable de déterminer les effets de ces défauts au niveau logique. Ceci correspond à la modélisation des pannes.

Le collage logique a été longtemps le modèle pris en compte pour le test

des circuits. Ce modèle couvre une partie des pannes physiques mais il n'est pas représentatif [COU 81] et [GAL 80] de toutes les pannes réelles des circuits.

Plusieurs pannes physiques ont un effet plus complexe dans les circuits. Le dosage d'implantation ionique, par exemple, peut provoquer un décalage dans les niveaux d'un transistor et peut amener sur la sortie une tension située entre les tensions assignées au "0" logique et au "1" logique. Ce comportement résulte en un "1" ou "0" faible. En effet le collage à "1" est une dégénérescence d'un "0" faible et le collage à "0" est une dégénérescence d'un "1" faible [TAM 84]. Un court-circuit impose sur les deux lignes une même valeur. Cette valeur doit être comprise entre la valeur logique "1" et la valeur logique "0" (les deux lignes sont supposées avoir des valeurs complémentaires) et donc la ligne supposée avoir la valeur "0" aura un "0" faible et l'autre un "1" faible.

Nous pouvons décrire à présent la modélisation de pannes des PLAs que nous utiliserons.

La structure régulière des PLAs permet de grouper les fautes dans un petit nombre de types. Elle permet aussi de simplifier l'analyse des effets de chaque faute modélisée ainsi que la détermination de la couverture des fautes.

Les fautes permanentes dans la structure des PLAs peuvent être modélisées par les fautes logiques suivantes [CHA 78]:

- Collage d'une entrée, monôme ou sortie à "0" ou à "1",

- Court-circuit entre deux lignes adjacentes ("bridging") et

- "Crosspoint".

Le collage logique ainsi que le court circuit correspondent à des défauts physiques dans les PLAs. Le crosspoint correspond à des fautes dont l'effet équivaut à la présence ou à l'absence anormale de transistors, dans les matrices ET et OU.

Y.TAMIR et C.H.SEQUIN [TAM 84] ont proposé un modèle de panne pour les PLAs représentatif des pannes permanentes et intermittentes. Dans ce modèle, les fautes dues à un "1" ou "0" faible et les coupures des lignes d'entrée, de monôme et de sortie sont ajoutées à l'ensemble des fautes permanentes. Ainsi l'ensemble complet des pannes permanentes et intermittentes peut être modélisé par [TAM 84]:

- 1/0 faible d'une ligne d'entrée,

- Court-circuit entre deux lignes d'entrée adjacentes,

- 1/0 faible d'un monôme,

- Court circuit entre deux monômes adjacents,

- 1/0 faible d'une sortie,

- Court circuit entre deux sorties adjacentes,

- Court circuit entre une ligne d'entrée et un monôme,

- Court circuit entre un monôme et une sortie,

- Transistor supplémentaire dans la matrice ET,

- Transistor supplémentaire dans la matrice OU,

- Coupure d'un monôme et

- Coupure d'une sortie.

Le collage à 1 est une dégénérescence d'un "0" faible tandis que le collage à "0" est une dégénérescence d'un "1" faible. L'absence d'un transistor dans la matrice ET a l'effet d'un "1" faible d'une ligne d'entrée et l'absence d'un transistor dans la matrice OU a l'effet d'un "1" faible d'un monôme. Ceci explique l'exclusion de ces pannes de l'ensemble donné.

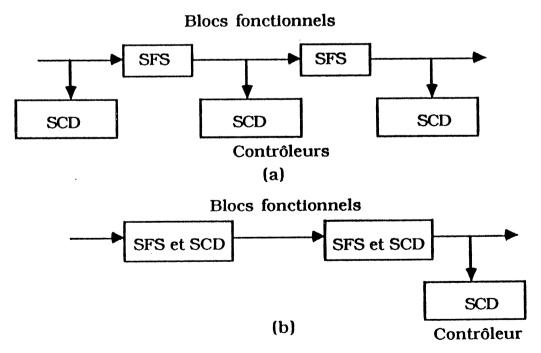

Quand ces fautes sont propagées aux sorties des PLAs elles provoquent des erreurs unidirectionnelles. Cela a été démontré dans [MAK 82] pour les fautes simples dues à un collage, court-circuit et "crosspoint". Le "1" faible se propage de la même manière que le collage à "0". De même le "0" faible se propage de la même manière que le collage à "1". Les coupures ont l'effet soit d'un "1" faible soit d'un collage à "0". Nous pouvons donc conclure que l'ensemble des pannes modélisées provoquent des erreurs unidirectionnelles aux sorties des PLAs.

TECHNIQUES D'OPTIMISATION DES PLAS

## 2 - TECHNIQUES D'OPTIMISATION DES PLAS.

#### 2.1 - GENERALITES.

Les réseaux logiques programmables (PLAs) sont des structures régulières qui permettent la réalisation de circuits logiques de type combinatoire ou séquentiel.

Les circuits combinatoires sont des circuits dont les sorties sont des fonctions booléennes, exprimées en sommes de produits des variables d'entrée. Ainsi les PLAs sont composés de deux matrices indépendantes, la matrice ET et la matrice OU. La matrice ET génère, à partir des variables d'entrée les monômes (qui sont les produits des entrées). La matrice OU génère, à partir des monômes, les sorties (qui sont les sommes des monômes).

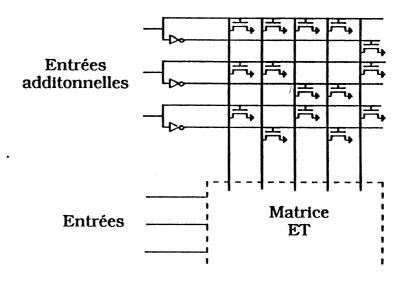

Les circuits séquentiels sont des circuits dont les sorties dépendent non seulement des entrées au même instant (circuit combinatoire) mais aussi des entrées aux instants précédents. Des circuits séquentiels peuvent être réalisés par des PLAs à l'aide d'éléments de mémorisation placés comme des entrées additionnelles de la matrice ET et chargés par les sorties de la matrice OU (PLA statique). Cette connexion constitue le bouclage des circuits séquentiels. Dans le cas des PLAs dynamiques les éléments de mémorisation ne sont plus nécessaires, les sorties sont rebouclées directement aux entrées correspondantes.

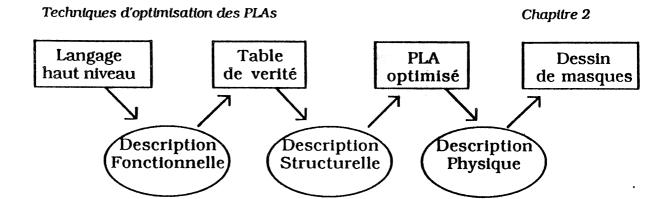

Différentes représentations sont utilisées pour décrire les différents niveaux de conception et de vérification des PLAs. L'ensemble des descriptions utilisées, qui est montré dans la figure 2.1, peut se résumer en trois catégories, qui sont:

- Description fonctionnelle,

- Description structurelle et

- Description physique.

Figure 2.1: Représentation des PLAs.

Dans la description fonctionnelle, le concepteur décompose la réalisation en une série d'algorithmes structurés de complexité décroissante. L'ensemble des sorties sont décrites en fonction de l'ensemble des entrées par une langage de haut niveau ou bien par des équations booléennes. L'implantation du circuit lui même n'est pas défini dans cette phase. Ici on s'occupe principalement de la spécification des conditions qui doivent être testées, de la définition de l'architecture ainsi que des caractéristiques opérationnelles.

La description structurelle permet d'effectuer la traduction entre la description fonctionnelle et la description physique. Dans cette phase, sont effectuées les optimisations logique et topologique. Les PLAs sont décrits par des tables de vérité ou bien une représentation topologique. Dans ce travail, tous les exemples considérés sont des PLAs traités au cours de cette phase. Ceci explique sa description détaillée dans les paragraphes suivants.

Dans la description physique les caractéristiques technologiques sont prises en compte et le dessin des masques est généré.

# 2.1.1 - Représentation des PLAs au niveau structurel.

Les PLAs, comme tous les circuits combinatoires, peuvent être représentés par une table de vérité qui spécifie les valeurs des variables de sortie pour chaque combinaison des valeurs des variables d'entrée. Soit F une fonction de n entrées et p sorties. L'ensemble des variables d'entrée de la fonction F est:

$$X_F = (X_1, X_2, ..., X_n) = X_i$$

, i dans  $(1,...,n)$

L'ensemble des variables de sortie de la fonction F est:

$$Y_F = (Y_1, Y_2, ..., Y_p) = Y_j, j dans (1,...,p)$$

Un cube singulier défini par  $P_k = (R_k, V_k) = R_k/V_k$  est une assignation des valeurs  $R_{ki}$  et  $V_{kj}$  à chacune des variables  $X_i$  et  $Y_j$  respectivement.  $R_k = (R_{k1}, R_{k2}, ..., R_{kn})$  est le cube d'entrée et  $V_k = (V_{k1}, V_{k2}, ..., V_{kp})$  est le cube de sortie. Le terme singulier indique l'existence d'une relation entre le cube d'entrée et le cube de sortie.

La figure 2.2 montre un exemple d'une table de vérité compacte qui est une représentation tabulaire des cubes  $P_{\mathbf{k}}$  de la fonction F.

|        | Cube<br>d'entrée  | Cube<br>de sortie                            |

|--------|-------------------|----------------------------------------------|

| Terme  | $X_1 X_2 X_3 X_4$ | Y <sub>1</sub> Y <sub>2</sub> Y <sub>3</sub> |

| 1      | 1 1 0 0           | 1 0 0                                        |

| 2      | 0 1 0 0           | 101                                          |

| 2<br>3 | 0 1 1 0           | 101                                          |

| 4      | * 1 1 1           | 100                                          |

| 5      | * 0 * 1           | 0 0 0                                        |

| 6      | 1 * 1 0           | 0 0 0                                        |

| 7      | 0000              | 0 1 1                                        |

| 8      | * 1 0 1           | 0 1 0                                        |

| 9      | 0010              | 0 0 0                                        |

| 10     | 1 0 0 0           | 0 0 0                                        |

Figure 2.2: Table de vérité compacte.

Un PLA réalise des fonctions exprimées sous la forme d'une somme des termes produits. Une fonctions Y<sub>1</sub> est décrite par:

$$Y_j = (V_{kj} * t_k, k, t_k \text{ dans PT}_F)$$

$PT_F$  est l'ensemble des termes produits de la fonction F dont l'ensemble  $t_k$  est au moins lié à une variable de sortie  $Y_j$  ayant une valeur "1" ( $V_{kj} = 1$ ).

Dans la figure 2.2, par exemple,  $Y_1 = T_1 + T_2 + T_3 + T_4$  ou bien  $Y_1 = X_1 X_2 \overline{X}_3 \overline{X}_4 + \overline{X}_1 X_2 \overline{X}_3 \overline{X}_4 + \overline{X}_1 X_2 \overline{X}_3 \overline{X}_4 + X_2 X_3 \overline{X}_4 + X_2 X_3 \overline{X}_4$ . Le symbole "\*", dans la table de vérité, représente une valeur indéfinie qui peut être considérée comme étant la valeur "0" ou "1".

Une autre manière de représenter une table de vérité est montrée dans la figure 2.3. Dans ce cas toutes les variables, entrée et entrée complémentaire, sont montrées. Donc une rangée représente un monôme et une colonne représente une entrée ou une entrée complémentaire ou une sortie.

|                            | Cube d'entrée                           |                                           |                                        | Cube<br>de sortie                      |                                                    |

|----------------------------|-----------------------------------------|-------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------------------|

| Terme                      | $x_1 \overline{x}_1$                    | $\overline{x_2}\overline{\overline{x}_2}$ | $x_3\overline{x}_3$                    | $X_4\overline{X}_4$                    | $Y_1Y_2Y_3$                                        |

| 1<br>2<br>3<br>4<br>5<br>6 | 1 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 1 0<br>1 0<br>1 0<br>1 0<br>0 1<br>1 0    | 0 1<br>0 1<br>1 0<br>1 0<br>0 1<br>0 1 | 0 1<br>0 1<br>0 1<br>1 0<br>0 1<br>1 0 | 1 0 0<br>1 0 1<br>1 0 0<br>1 0 0<br>0 1 0<br>0 1 0 |

Figure 2.3: Table de vérité d'implantation.

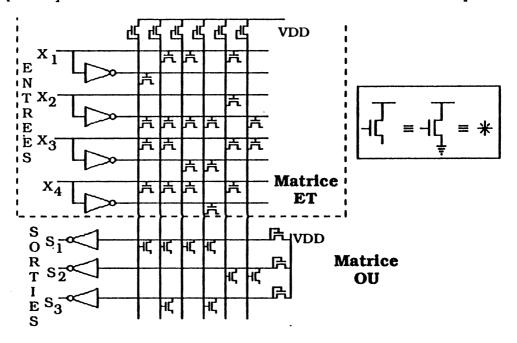

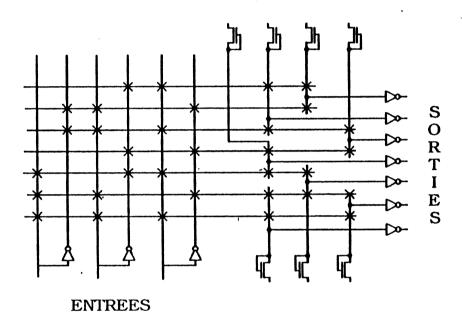

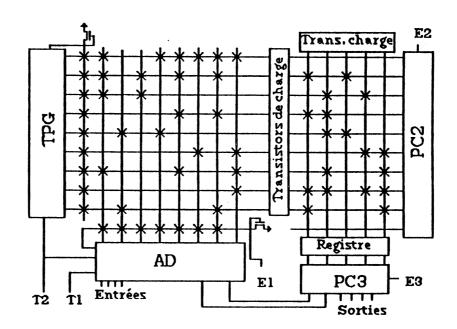

La figure 2.4 montre la représentation topologique du PLA de la figure 2.3. L'utilisation d'une entrée (ou entrée complémentaire) dans la génération d'un monôme correspond au placement d'un transistor entre cette entrée (ou entrée complémentaire) et le monôme. De même, l'utilisation d'un monôme dans la génération d'une fonction de sortie correspond au placement d'un transistor entre ce monôme et la sortie. Ainsi la programmation des PLAs est obtenue par l'insertion des transistors dans les intersections convenables des monômes et des entrées/sorties. Généralement, dans la technologie MOS, ils sont implementés en une structure NOR-NOR. Donc, à partir de la table de vérité de la figure 2.3, les "1" correspondent au placement d'un transistor dans le croisement et le "0" signifie l'absence de transistor. Puisque la structure utilisée est NOR-NOR le cube d'entrée doit être inversé i.e. les transistors sont placés dans le croisement entre le monôme et la variable complémentaire. De même la sortie doit être inversée d'où l'inclusion des inverseurs à la sortie du PLA.

Figure 2.4: Représentation topologique d'un PLA.

### 2.2 - OPTIMISATION EN SURFACE DES PLAS.

La surface d'un PLA classique est proportionnelle au nombre des entrées/sorties et des monômes indépendamment des fonctions que le PLA réalise. Plus précisément, la surface d'un PLA est donnée par l'équation:

$$S_{PLA} = (2*n + p)*m + a n + b m + c p$$

(eq. 1)

Où n, m et p sont, respectivement, le nombre des entrées, monômes et sorties et a, b et c sont des constantes associées directement à la topologie des amplificateurs-décodeurs des entrées, des sorties et des monômes. Cette surface peut être optimisée par deux techniques différentes, mais complémentaires:

- Optimisation logique et

- Optimisation topologique.

L'optimisation logique cherche la simplification des fonctions booléennes. Ainsi elle peut réduire la surface des PLAs par l'élimination des entrées, sorties et monômes redondants. Elle peut aussi réduire le nombre de transistors dans les matrices ET et OU. Cela permet de réduire le taux de remplissage des matrices et en conséquence d'améliorer l'optimisation topologique.

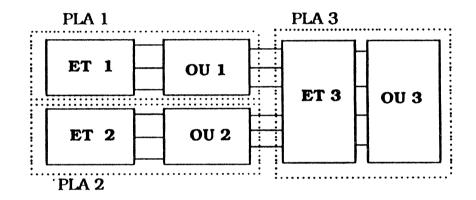

L'optimisation topologique peut être obtenue par deux techniques:

- Partition ou segmentation et

- Pliage (brisure ou "folding").

La technique de partition consiste à diviser de grands PLAs en plusieurs petits PLAs [EGA 84]. La figure 2.5 montre l'exemple d'un PLA partitionné. Dans cette technique la structure du PLA est maintenue.

Figure 2.5: PLA partitionné.

Le pliage consiste à réorganiser les matrices ET et OU de façon à pouvoir placer deux ou plusieurs entrées et/ou sorties sur une même colonne et/ou deux ou plusieurs monômes sur une même rangée. L'optimisation par pliage peut être divisée en deux classes que nous décrirons dans les paragraphes suivants:

- Pliage simple et

- Pliage multiple.

Une ligne peut être partagée par deux monômes si et seulement si les deux monômes sont disjoints (voir définition D 2.1). Une colonne peut être partagée par deux entrées/sorties si et seulement si les deux entrées/sorties sont disjointes (voir définition D 2.2). Mais le fait que deux entrées, sorties ou monômes soient disjoints n'est pas l'unique contrainte d'application de l'optimisation topologique. Chaque paire d'entrée/sortie partageant une ligne, par exemple, introduit des contraintes sur les autres.

Ceci veut dire que deux entrées/sorties partageant une colonne doivent être l'une au dessous de l'autre et que les monômes doivent suivre cet ordonnancement. D'où l'introduction de contraintes pour les autres entrées/sorties. Ainsi un ensemble de pairs entrées/sorties disjoint peut être implanté si ses monômes peuvent être ordonnés.

## **DEFINITION D 2.1**

Deux entrées sont dites disjointes si et seulement si elles excitent des monômes différents.

### **DEFINITION D 2.2**

Deux sorties sont dites disjointes si et seulement si elles n'ont pas de monômes communs.

### **DEFINITION D 2.3**

Deux monômes sont dits disjoints si et seulement si les entrées et les sorties qui leur sont rattachées sont disjointes.

En fonction de ces définitions HACHTEL, NEWTON et SANGIOVANNI-VINCENTELLI [HAC 82] ont formalisé le problème de l'optimisation topologique de la manière suivante:

"Determiner l'ensemble d'entrées, sorties et/ou monômes disjoints pour obtenir une surface minimale dont l'implantation soit possible".

Ce problème ainsi que ses variations est un problème NP-complet [LUB 82] et pour le résoudre plusieurs heuristiques ont été proposées dont la technique PAOLA [PER 80 et 85] [CHU 84] et PLEASURE [MIC 83].

# 2.2.1 - Le pliage simple.

Pour le pliage simple, une colonne au moins est partagée entre deux entrées et/ou sorties et/ou une ligne au moins est partagée entre deux monômes. Dans ce cas, si toutes les lignes sont partagées par deux monômes et si toutes les colonnes sont partagés par deux entrées/sorties, le PLA sera réduit à 25% de la surface originale. Ceci est le gain maximal du pliage simple.

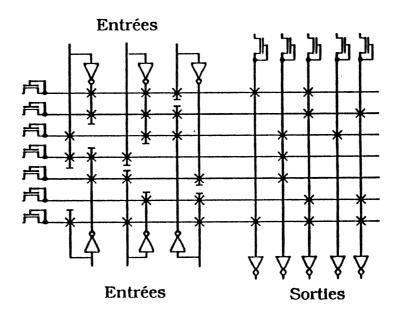

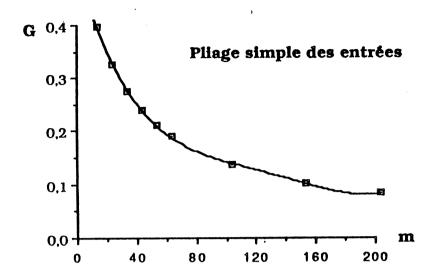

Le pliage simple d'entrées est décrit dans la figure 2.6. La particularité de cette technique est que les entrées sont placées sur deux côtés du PLA. La surface finale de la matrice ET, après l'optimisation topologique, est au maximum égale à 50%. Ce gain maximal est obtenu quand toutes les colonnes sont partagés par deux entrées.

Figure 2.6: Pliage simple d'entrées.

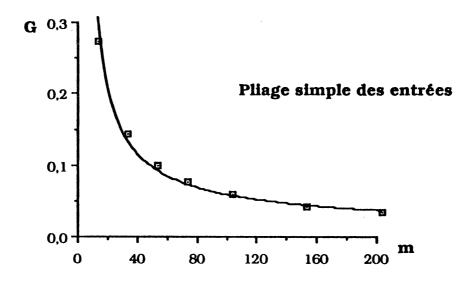

Le pliage simple des sorties est décrit dans la figure 2.7. Dans cette technique les sorties sont placées sur deux côtés du PLA. La surface finale de la matrice OU, après l'optimisation topologique, est au maximum égale à 50%. Ce gain maximal est obtenu quand toutes les colonnes sont partagés par deux sorties. Généralement le taux de remplissage de la matrice OU est beaucoup plus faible que celui de la matrice ET. Par conséquent, l'optimisation topologique de cette matrice est normalement plus facile. Le gain de surface est aussi généralement plus important que celle de la matrice ET.

Figure 2.7: Pliage simple des sorties.

Le pliage simple des monômes présente des lignes du PLA partagées par deux monômes. Deux monômes peuvent partager une ligne si et seulement si les entrées et les sorties qui les attaquent sont différentes. Dans ce cas les sorties sont divisées en deux ensembles qui sont placés sur deux côtés distincts du PLA. Les entrées sont susceptibles d'être réordonnées. Ces contraintes limitent l'utilisation de cette technique. Par contre cette technique optimise les deux matrices. Le gain maximal est égal à 50% de la surface du PLA. La figure 2.8 décrit le pliage simple des monômes.

Figure 2.8: Pliage simple des monômes.

# 2.2.2 - Le pliage multiple.

Pour le pliage multiple, une colonne au moins est partagées entre plusieurs entrées et/ou sorties. Le pliage simple est un cas particulier du pliage multiple. Donc le gain de surface est toujours meilleur dans le cas du pliage multiple (dans le pire des cas le gain sera égal). Le gain de surface maximal est déterminé par la structure du PLA lui même. La principale difficulté pour l'application de cette technique est due au routage interne des matrices ET et OU. Chaque segment doit être relié à son connecteur placé sur le bord de la matrice. Il faut donc trouver un chemin à travers les emplacements vides à l'intérieur des matrices du PLA. Cette recherche est difficile et parfois impossible [CHU 84]. Les colonnes qui utilisent moins de monômes sont placées vers le côté externe de la matrice, où convergent toutes les connexions internes. Ceci permet de libérer la place pour le routage puisque les monômes peuvent être coupés dès que leur utilisation est finie. Dans le cas où la place libérée n'est pas suffisante une bande d'écartement doit être introduite. Cette bande rend le PLA plus haut que prévu et en conséquence l'optimisation est dégradée.

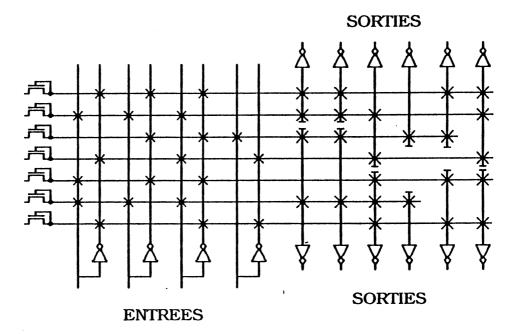

Le pliage multiple d'entrées est illustré par la figure 2.9. La particularité de cette technique est que les entrées sont généralement placées parallèlement aux monômes. Le taux de remplissage de la matrice ET doit être assez faible pour pouvoir libérer la place nécessaire aux connexions. Ceci est un facteur qui restreint l'utilisation de cette technique.

Figure 2.9: Pliage multiple des entrées.

Le pliage multiple des sorties présente les sorties parallèles aux monômes, comme le montre la figure 2.10. Cette technique s'applique aux PLAs ayant un grand nombre de monômes et de sorties où chaque sortie est générée par un petit nombre de monômes. Ceci veut dire que comme dans le cas précédent le taux de remplissage doit être faible. Généralement le taux de remplissage de la matrice OU est plus faible que celui de la matrice ET. Par conséquence l'application du pliage multiple des sorties est relativement plus facile que celle des entrées.

Figure 2.10: Pliage multiple des sorties.

Un autre cas du pliage multiple est le PLA monomatrice [VAR 85]. Il présente des lignes partagées par plusieurs monômes comme indiqué sur la figure 2.11. Ceci est obtenu par une duplication des entrées. Les entrées et les sorties sont placées sur les deux cotés du PLA. Cette technique donne une structure très particulière au PLA. Le gain de surface dans le PLA est faible. Par contre celui obtenu par une meilleure connexion avec les blocs voisins peut être assez important.

Figure 2.11: PLA monomatrice [VAR 85].

# 2.2.3 - La technique "PAOLA".

La technique PAOLA consiste à réduire la surface d'un PLA par un changement de sa topologie interne et par une adaptation de sa forme de manière a augmenter sa connectabilité et sa transparence [CHU 84].

La technique utilisée cherche à réorganiser la structure interne du PLA, en permutant les monômes ainsi que les entrées et les sorties. Après cette réorganisation, un compactage en rangées et en colonnes est essayé. Ainsi l'optimisation du PLA lui même est faite. D'autre part la disposition des connecteurs d'entrée et de sortie définis par le concepteur permet un câblage externe le plus simple possible.

Dans cette technique l'optimisation des PLAs se réalise en trois phases:

- Réordonnancement des monômes,

- Compactage des matrices et

- Duplication des monômes.

Les phases de réordonnancement et de compactage s'appliquent soit à la matrice ET, soit à la matrice OU. La duplication des monômes s'applique à la matrice OU mais avec des répercussions sur la matrice ET.

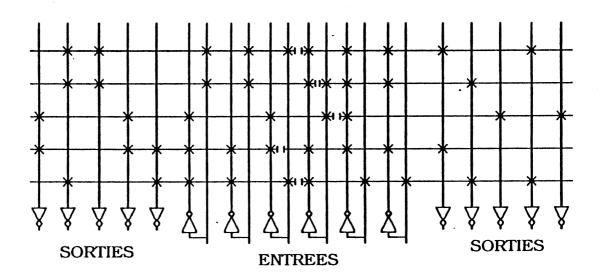

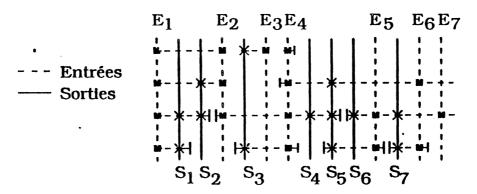

Le but de la première phase est de réordonner les monômes pour obtenir une distribution des transistors qui permettra un meilleur compactage. L'approche utilisée, pour réordonner les monômes, consiste a redistribuer les transistors sur une bande diagonale décrite par M et S comme le montre la figure 2.12. Ceci veut dire que les monômes et les entrées/sorties sont réordonnés de manière que leurs transistors se trouveront le plus près possible d'une bande diagonale. La diagonalisation est obtenue par la minimisation de la couverture géométrique de chaque

segment.

Un segment interne d'une entrée ou sortie est défini par le segment de colonne compris entre le premier et le dernier transistor contrôlés par cette entrée ou contrôlant cette sortie.

La couverture géométrique d'un segment interne est l'ensemble des monômes se trouvant entre le premier et le dernier transistor de l'entrée/sortie considérée, ses monômes intermédiaires étant connectés ou non à cette entrée/sortie.

Figure 2.12: Diagonalisation de la matrice OU.

La couverture géométrique d'un monôme est l'ensemble des entrées et des sorties se trouvant entre le premier et le dernier transistor de la partie ET et OU du monôme.

On obtient la minimisation de la couverture géométrique d'un segment interne par permutation des monômes et celle d'un monôme par permutation des entrées/sorties.

Le réordonnancement des monômes peut s'appliquer soit à la matrice ET soit à la matrice OU, avec des répercussions de l'une sur l'autre bien entendu. Normalement la matrice OU est beaucoup plus creuse que la matrice ET, il est donc normal que l'ordonnancement soit fait sur cette matrice. Ceci entraîne un meilleur compactage sur la matrice OU.

C'est dans cette phase que la position des connecteurs, fixée par le concepteur, est prise en compte.

Le but du compactage des matrices est de placer deux ou plusieurs entrées/sorties sur une même colonne réalisant ainsi l'optimisation topologique des matrices.

Le regroupement des entrées/sorties sur une même colonne se fait en fonction de leur **compatibilité**: deux ou plusieurs entrées/sorties peuvent partager une même colonne si elles sont compatibles.

# **DEFINITION D 2.4**

Deux entrées/sorties sont compatibles si leurs segments ne se recouvrent pas.

Il est important de remarquer que la couverture d'une entrée ou sortie est définie par l'ordre des monômes, d'où l'importance de l'ordonnancement dans l'optimisation.

Le nombre de possibilités pour regrouper les entrées/sorties en groupes de 1 à n/p éléments, sachant que le nombre de groupes peut varier entre 1 et n/p, croît de manière exponentielle avec n/p. Pour résoudre ce problème il faut utiliser des heuristiques, même pour des exemples de taille moyenne.

Une entrée/sortie peut être compatible avec une ou plusieurs entrées/sorties ou n'avoir aucune compatibilité. Le nombre de compatibilité est le nombre qui exprime la quantité d'entrées/sorties qui sont compatibles avec une entrée/sortie donnée. Dans PAOLA l'heuristique utilisée est la suivante:

Les entrées/sorties sont triées par nombre de compatibilité. A partir de l'entrée/sortie qui a le nombre le plus petit de compatiblité on choisit un ensemble de sorties compatibles deux à deux pour les regrouper dans une même colonne. Ces entrées/sorties sont éliminées du groupe de départ. Cette procédure est répétée jusqu'à ne plus avoir d'entrée/sorties.

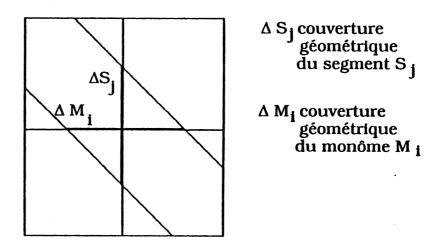

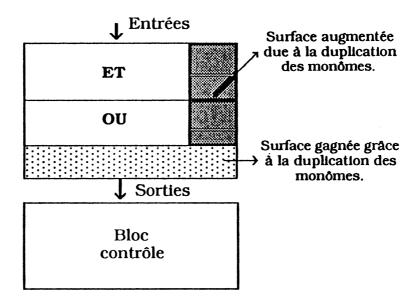

Quand la longueur d'un PLA est plus petite que celle du bloc à commander, il est nécessaire de l'augmenter. Cette opportunité peut être utilisée pour améliorer la diagonalisation de la matrice OU par duplication des monômes comme le montre la figure 2.13. La duplication des monômes ne donne pas un gain de surface dans le PLA. Elle facilite la connexion avec les blocs voisins, ce qui represente des gains importants au niveau du routage.

Figure 2.13: Adaptation de la structure d'un PLA par allongement.

La duplication d'un monôme, dit monôme-père, consiste à le dédoubler en deux monômes-fils distribués sur deux sorties différentes ce qui permettra un éventuel compactage. Donc les deux monômes ont les mêmes variables d'entrée dans la matrice ET. Les sorties qui était attachées à un seule monôme avant la duplication sont distribuées entre les deux monômes.

La difficulté de cette phase consiste à choisir le monôme qui, une fois dupliqué, permettra effectivement de gagner une colonne, ainsi que le point de coupure du monôme ou bien quelles sorties doivent être placées sur chaque monôme. Le choix du monôme à dupliquer est en effet une application d'une fonction heuristique qui prend en compte un des critères suivants [PER85]:

- Le nombre de sorties contrôlées.

- La couverture géométrique du monôme,

- Le facteur d'occupation,

- Le facteur d'utilisation,

- La distance barycentre moyenne,

- La taille de trou et

- Le poids des trous extrêmes de chaque sortie.

La distance barycentre moyenne est la distance entre le barycentre et le point milieu de la couverture d'un monôme. Le point milieu est défini comme le point équidistant du premier et du derniér transistor d'un monôme. Le barycentre est défini en fonction du poids donné à chaque sortie. Ce poids

' est donné en fonction de l'ordre du connecteur sortie. La taille de trou d'un monôme est un ensemble de points vides contigus. Les trous extrêmes de chaque sortie prennent en compte les trous contigus au premier et au dernier transistor de la sortie.

Le point de coupure est fixé par des critères basés principalement sur le barycentre et le point milieu [PER 85]. Etant donné que les résultats sont fonction des caractéristiques des monômes et des sorties, des essais permettent de définir le meilleur critère pour chaque cas.

LE TEST HORS LIGNE DES PLAS

#### 3 - LE TEST HORS LIGNE DES PLAS.

#### 3.1 - GENERALITES.

La régularité des PLAs, qui favorise l'implantation d'une structure testable, présente aussi quelques particularités qui rendent difficile sa contrôlabilité. Premièrement, chaque entrée contrôle deux lignes d'entrée i.e. le changement d'une entrée implique le changement de la ligne d'entrée et de la ligne d'entrée complémentaire. Deuxièmement, chaque vecteur d'entrée sélectionne en général plusieurs monômes. Pour ces raisons la génération des vecteurs de test pour un PLA sans modifications est une tâche difficile.

Pour résoudre ces problèmes plusieurs schémas de test sont proposés dans la littérature, dont les plus importants seront décrits dans cette étude avant la presentation d'une nouvelle proposition. La clé de ces schémas est le contrôle de chaque ligne d'entrée et de chaque monôme individuellement.

Les PLAs testables peuvent être divisés en trois classes:

- Les PLAs facilement testables,

- Les PLAs fonctionnellement testables et

- Les PLAs autotestables.

La première méthode est basée sur de simples modifications dans la structure du PLA. Ces modifications permettent de contrôler soit les lignes d'entrée soit les monômes. Le contrôle des entrées ou des monômes est associé à des vecteurs d'entrée convenablement choisis pour exciter les fautes en propageant les erreurs (si possible) vers une sortie observable. Les vecteurs d'entrée ainsi que les vecteurs de sorties sont dépendants de la programmation du PLA. Les vecteurs d'entrée et les réponses de sortie sont respectivement générés et vérifiés hors circuit. La surface de la logique rajoutée est faible.

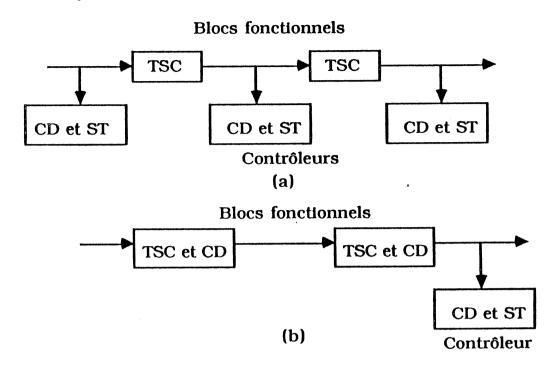

La seconde méthode est basée sur le principe qu'il existe un test universel tel que les vecteurs d'entrée et les réponses de sortie sont indépendants de la fonction que le PLA réalise. Par conséquent le coût de génération de vecteurs de test est éliminé. Les vecteurs d'entrée sont générés hors circuit et la réponse de sortie est normalement comprimée sur des bits de parité. Dans la troisième méthode, le circuit est capable de se tester tout seul. La logique nécessaire à la génération des vecteurs d'entrée, de même que celle necessaire à la compression des vecteurs de sortie est implantée sur la même puce. Les PLAs autotestables peuvent être divisés en deux classes générales:

- Dans la première classe, les vecteurs d'entrée sont générés par des LFSRs (Linear Feedback Shift Register) et les réponses de sortie sont comprimées par des analyseurs de signature.

- Dans la seconde classe, les entrées et les sorties sont contrôlées pour pouvoir tester à chaque cycle un seul croisement dans la matrice ET. Cette classe utilise le même principe que les PLAs fonctionnellement testables mais dans ce cas la logique nécessaire au test est implantée sur la même puce.

Par la suite, nous ferons une brève presentation des schémas de test les plus importants proposés dans la littérature. Cette description est divisée, en trois classes.

#### 3.1.1 - Les PLAs facilement testables.

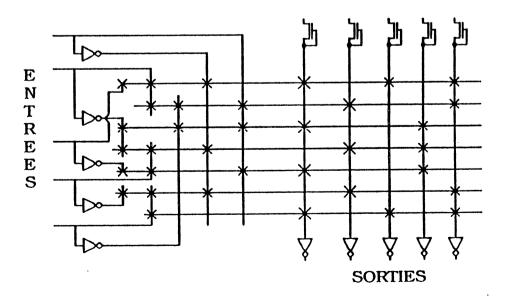

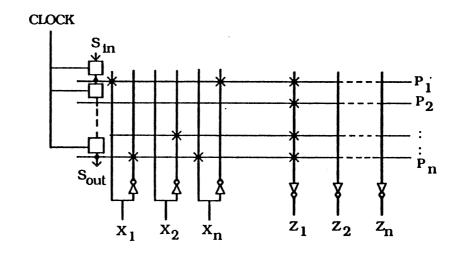

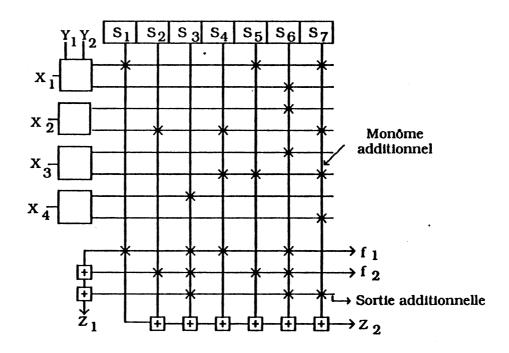

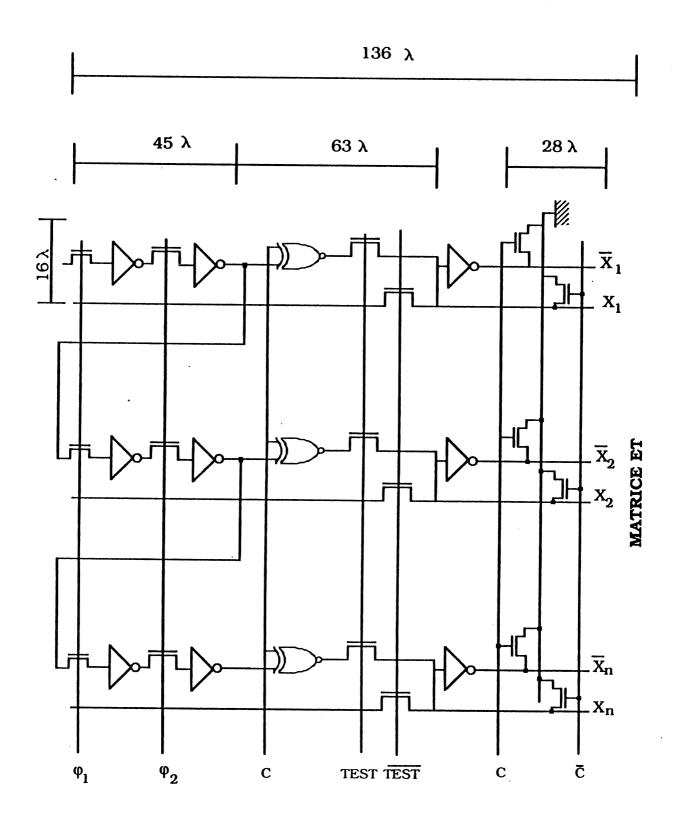

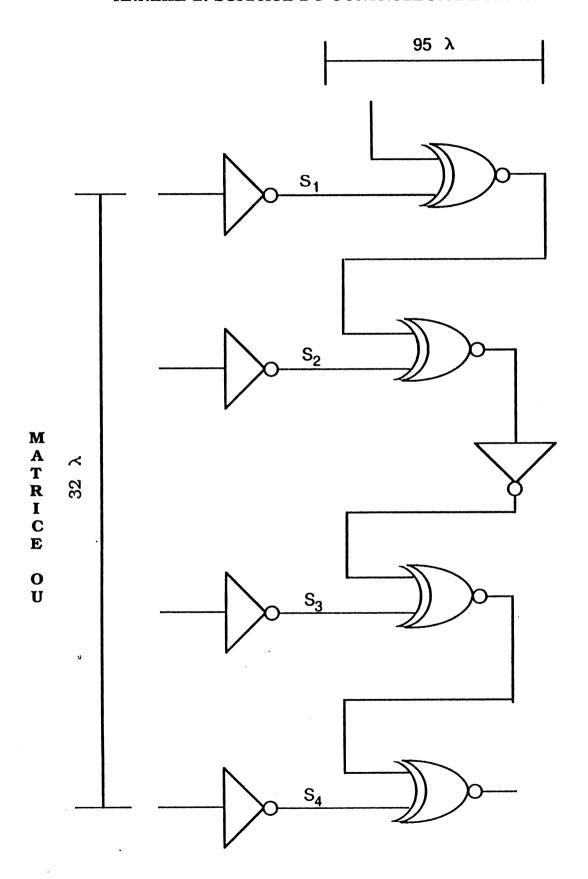

KHAKBAZ [KHA 84] propose un schéma de test basé sur le contrôle individuel des monômes. Ce contrôle est obtenu par des registres à décalage. La procédure de test assigne la valeur "1" à chaque monôme sélectonné (le registre à décalage met à la masse tous les autres monômes). Le vecteur d'entrée, qui maintient ce monôme sélectionné, est appliqué. Puis à chaque cycle une entrée est changée. Le registre à décalage est maintenu dans son état tant que la dernière entrée n'est pas changée. Les monômes sont connectés à une sortie additionnelle  $(Z_1)$  qui sera à "1" si le monôme est aussi à "1" ou si le vecteur d'entrée est une "don't care condition" (i.e. il n'est pas défini pour la fonction de sortie). Sinon, la valeur de  $Z_1$  doit changer, s'il n'y a pas de faute. La figure 3.1 décrit ce schéma.

Figure 3.1: Schéma proposé par KHAKBAZ.

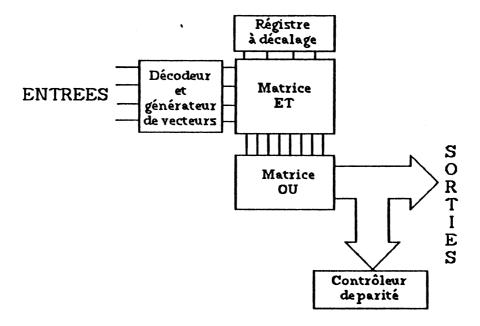

RAJSKI et TYSZER [RAJ84] proposent un schéma de test basé sur le contrôle de chaque ligne d'entrée. La figure 3.2 montre le schéma de test.

Figure 3.2: Schéma proposé par RAJSKI et TYSZER.

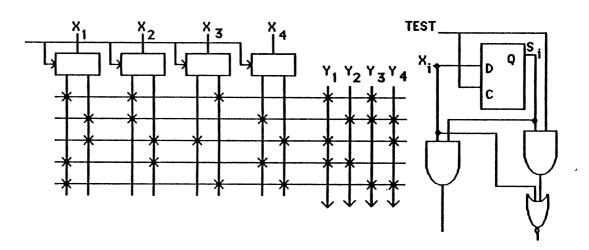

BOZORGUI-NESBAT et McCLUSKEY [BOZ 84] proposent un schéma de test où le contrôle des monômes est obtenu par l'addition des entrées. Ces entrées sont additionnées en vue de rendre le PLA "non concurrent" (i.e. chaque vecteur d'entrée sélectionne seulement un monôme). Dans la phase de test les entrées supplémentaires associées aux entrées normales contrôlent les monômes. Les vecteurs d'entrée sont envoyés de manière semblable à celle du schéma proposé par KHAKBAZ. Les monômes ont une distance minimale entre eux égale à deux (i.e. il existe au moins deux variables d'entrée différentes entre deux monômes). Ainsi le changement

d'une seule entrée n'est pas suffisant pour sélectionner un autre monôme. La figure 3.3 décrit ce schéma.

Figure 3.3: Schéma proposé par BOZORGUI-NESBAT et McCLUSKEY.

## 3.1.2 - Les PLAs fonctionnellement testables.

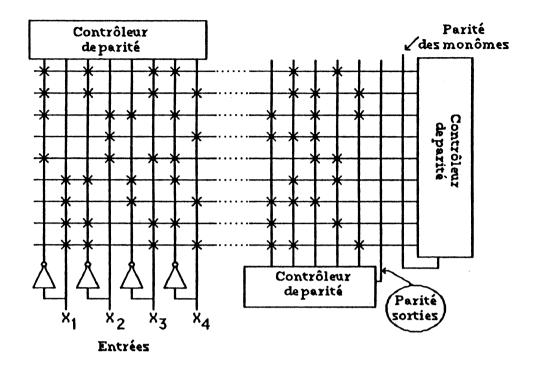

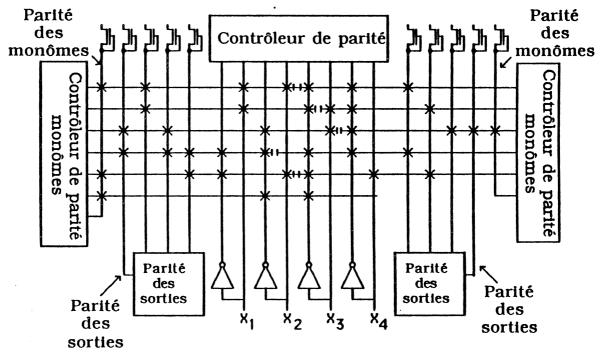

FUJIWARA et KINOSHITA [FUJ 81] proposent un schéma de test universel. Dans les schémas de test universel, les vecteurs d'entrée ainsi que les réponses de sortie sont prédéterminés indépendamment de la fonction que le PLA réalise. La logique additionnelle est composée principalement de:

- Un registre à décalage,

- Deux colonnes  $Y_1$  et  $Y_2$ ,

- Un contrôleur de parité (monômes)

- Un contrôleur de parité (sorties)

- Un monôme et

- Une sortie.

Un monôme est ajouté pour rendre impair le nombre de transistors sur chaque ligne d'entrée. La sortie additionnelle permet d'avoir un nombre impair de transistors, sur chaque monôme, dans la matrice OU. Les deux colonnes Y<sub>1</sub> et Y<sub>2</sub> permettent de sélectionner l'entrée ou l'entrée complémentaire. Ainsi, après la selection d'une ligne d'entrée ou d'une ligne d'entrée complémentaire, le registre à décalage sélectionne un monôme à chaque cycle. La parité des monômes doit être égale à la parité des sorties à

chaque cycle. La figure 3.4 décrit ce schéma.

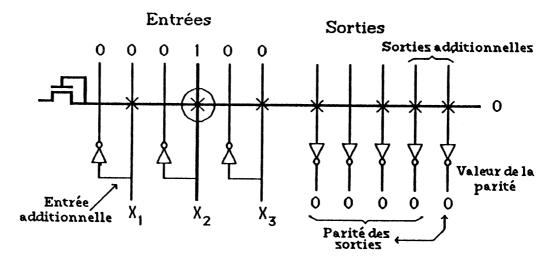

Figure 3.4: Schéma proposé par FUJIWARA et KINOSHITA.

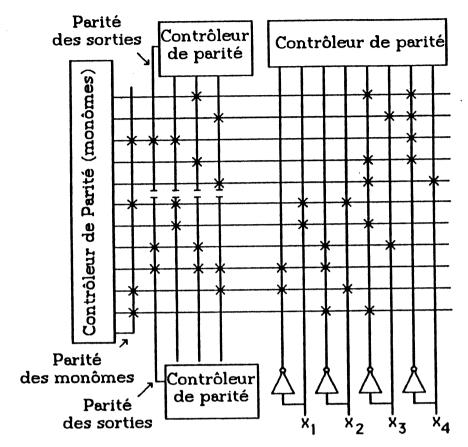

SALUJA [SAL 83] et FUJIWARA [FUJ 84] proposent des améliorations du schéma de [FUJ 81]. Le schéma proposé par FUJIWARA est donné dans la figure 3.5.

Figure 3.5: Schéma proposé par FUJIWARA.

# 3.1.3 - PLA autotestable (première classe).

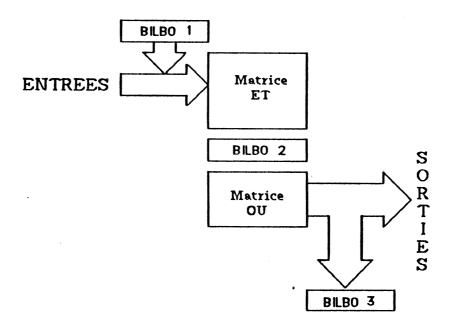

DAEHN et MUCHA [DAE 81] proposent l'utilisation d'un registre non linéaire à rebouclage pour la génération des vecteurs d'entrée. Comme le montre la figure 3.6, les BILBOs (Built-In Logic Block Observers) sont capables de générer les vecteurs d'entrées et de comprimer la réponse de sortie. Chaque matrice est testée séparément et le test est divisé en trois phases. Dans la première phase le BILBO 1 génère les vecteurs d'entrée qui seront comprimés par le BILBO 2. Après la vérification de la valeur de la signature, le BILBO 2 génère les vecteurs d'entrée dont les vecteurs de sortie seront comprimés par le BILBO 3. Finalement, le BILBO 3 génère les vecteurs qui seront comprimés par le BILBO 1. La première phase permet de tester la matrice ET, la seconde, la matrice OU et la troisième les décodeurs d'entrée et de sortie. Les vecteurs d'entrée sont indépendants de la fonction que le PLA réalise par contre les vecteurs de sortie ne le sont pas. La surface de la logique ajoutée limite l'utilisation de ce schéma.

Figure 3.6: Schéma proposé par DAEHN et MUCHA.

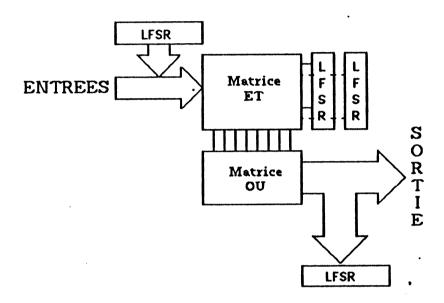

HASSAN et McCLUSKEY [HAS 83] proposent un schéma dans lequel les LFSRs sont utilisés pour générer les vecteurs d'entrée et pour vérifier les vecteurs de sortie. Les deux LFSRs parallèles aux entrées, donnés sur la figure 3.7, compriment la valeur des entrées et des entrées complémentaires. Un autre LFSR comprime la réponse des sorties. Les trois

signatures comprimées sont comparées avec les signatures attendues pour déterminer si le PLA fonctionne correctement. Ce schéma convient aux PLAs ayant un petit nombre d'entrées puisque il est nécessaire d'appliquer  $2^{n-1}$  vecteurs de test. Le PLA doit donc avoir un petit nombre entrées pour que le test soit appliqué dans un temps raisonnable.

Figure 3.7: Schéma proposé par HASSAN et McCLUSKEY.

# 3.1.4 - Le PLA autotestable (seconde classe).

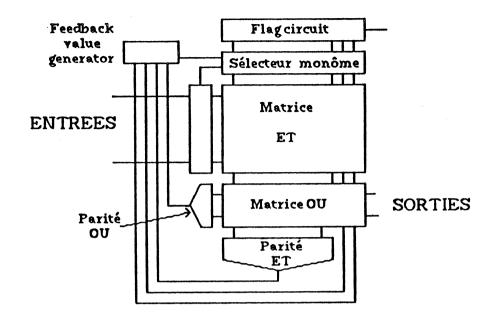

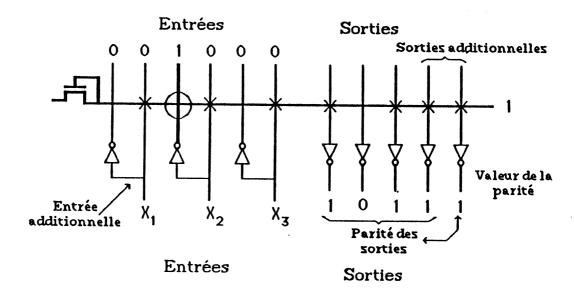

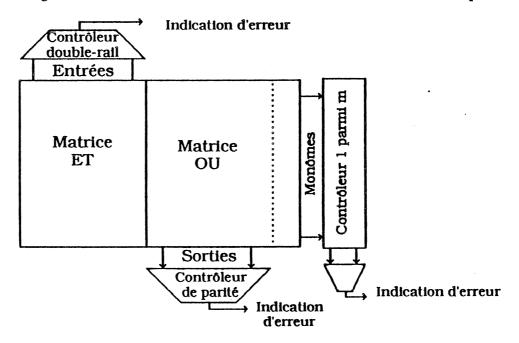

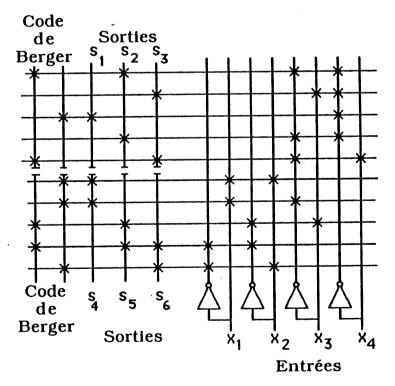

YAJIMA et ARAMAKI [YAJ 82] proposent la structure donnée dans la figure 3.8. La logique additionnelle est composée de quatre monômes, deux sorties, deux contrôleurs de parité (monômes et sorties), un décodeur d'entrée avec un registre à décalage et un contrôle des parités (feedback value generator). Les deux valeurs de parité sont utilisées par le "feedback value generator" pour la génération du vecteur d'entrée suivant. Après l'application de n + 2m + 8 vecteurs d'entrée, la réponse de sortie est comprimée dans un régistre à décalage composé par m + 4 cellules.

Figure 3.8: Schéma proposé par YAJIMA et ARAMAKI.

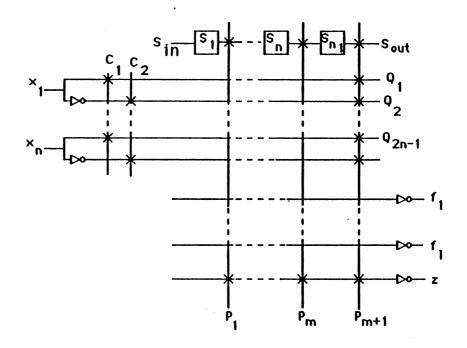

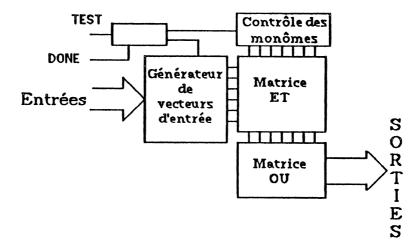

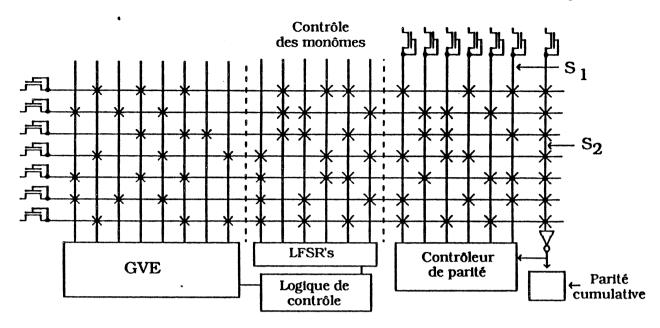

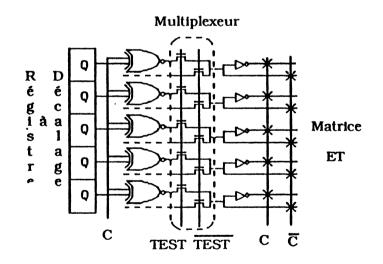

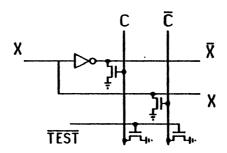

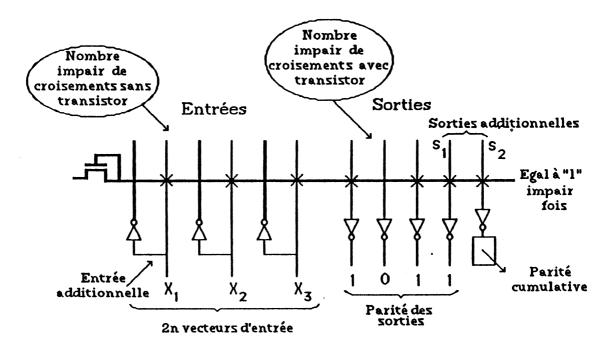

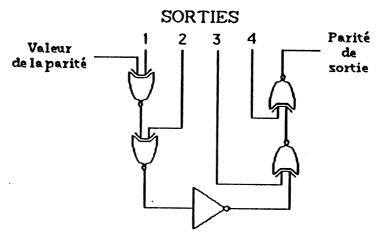

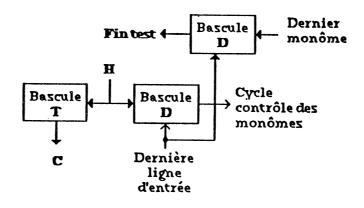

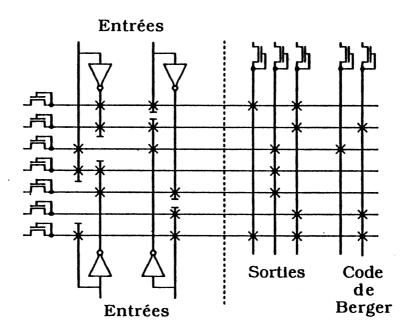

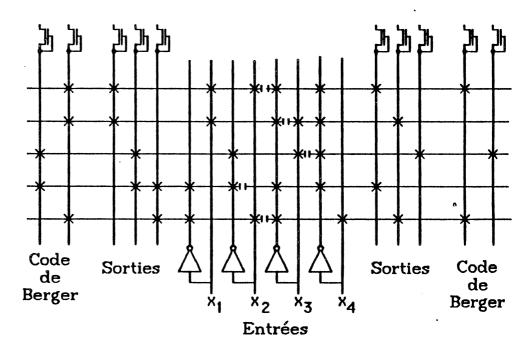

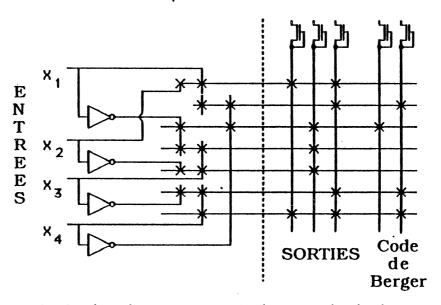

TREUER, FUJIWARA et AGARWAL [TRE 85] proposent un schéma où le contrôle des monômes est obtenu par des registres à décalage (m/2). Un autre registre à décalage est utilisé pour générer les vecteurs d'entrée. Deux lignes additionnelles contrôlent le test des lignes d'entrée ou des lignes d'entrée complémentaire. Un multiplexeur permet de sélectionner les entrées de test pendant la phase de test, ou les entrées normales au cours du fonctionnement normal du circuit. Les vecteurs de sorties sont comprimés sur des bits de parité. Cette compression est obtenue par l'addition des monômes et une sortie. Les monômes permettent d'avoir un nombre impair de croisements avec et sans transistors pour chaque ligne d'entrée dans la matrice ET. La sortie permet d'avoir un nombre impair de croisements avec transistors dans la matrice OU. Donc après l'application de 2nm + 1 vecteurs d'entrée la parité cumulative doit être impaire. Ce schéma est donné dans la figure 3.9.

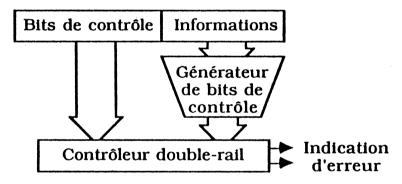

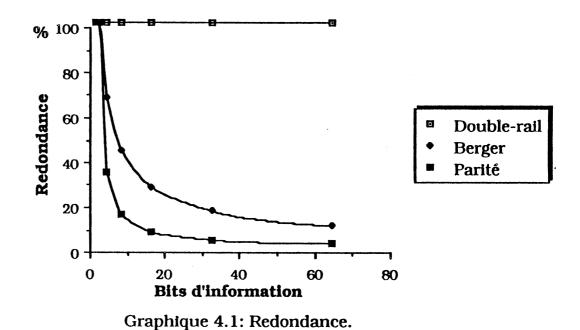

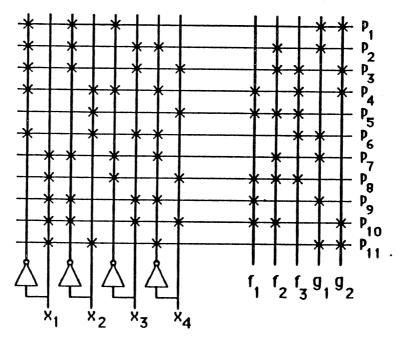

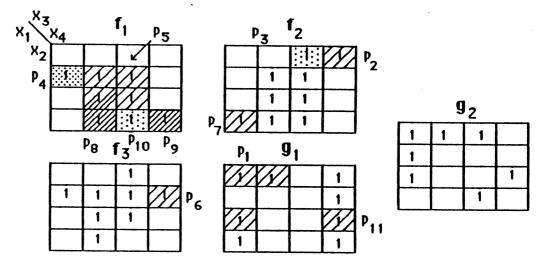

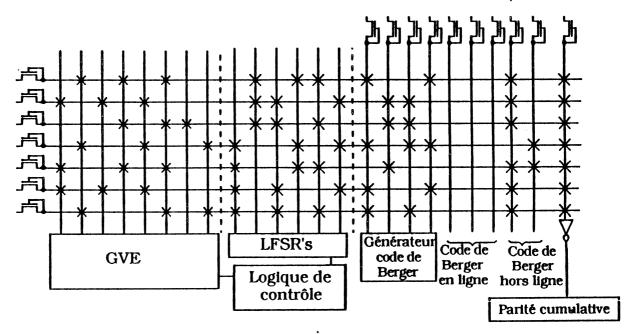

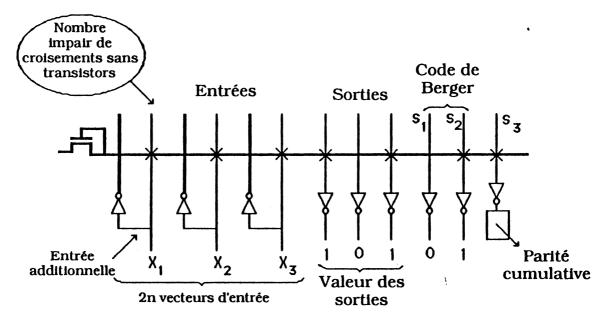

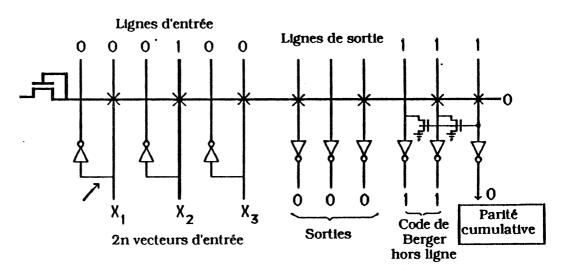

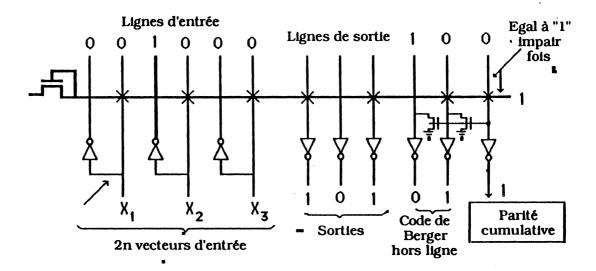

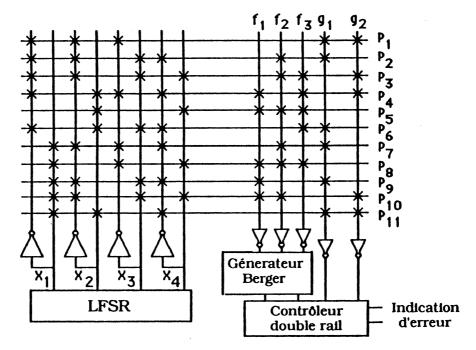

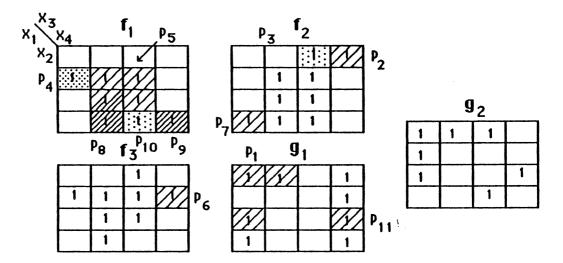

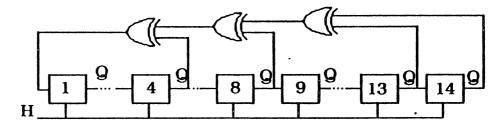

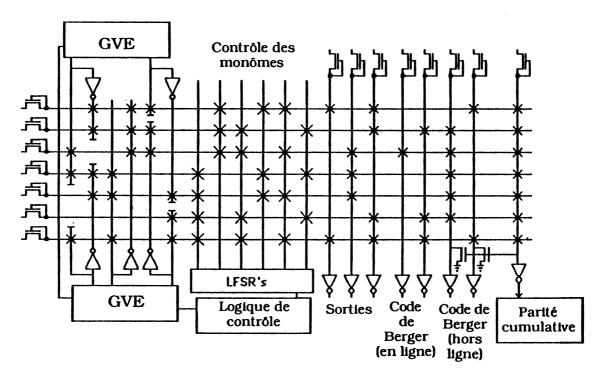

Figure 3.9: Schéma proposé par TREUER, FUJIWARA et AGARWAL.