# All-digital RF signal generation using delta-sigma modulation for mobile communication terminals

Antoine Frappé

#### ▶ To cite this version:

Antoine Frappé. All-digital RF signal generation using delta-sigma modulation for mobile communication terminals. Micro and nanotechnologies/Microelectronics. Université des Sciences et Technologie de Lille - Lille I, 2007. English. NNT: . tel-00280968

### HAL Id: tel-00280968 https://theses.hal.science/tel-00280968

Submitted on 20 May 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITE DES SCIENCES ET TECHNOLOGIES DE LILLE

Ecole Doctorale Sciences Pour l'Ingénieur

#### **THESE**

En vue de l'obtention du grade de DOCTEUR DE L'UNIVERSITE DE LILLE

Discipline: Electronique

Présentée et soutenue publiquement le 7 décembre 2007 par

#### Antoine FRAPPÉ

# ALL-DIGITAL RF SIGNAL GENERATION USING $\Delta\Sigma$ MODULATION FOR MOBILE COMMUNICATION TERMINALS

GENERATION NUMERIQUE DE SIGNAUX RF POUR LES TERMINAUX DE COMMUNICATION MOBILE PAR MODULATION  $\Delta\Sigma$

#### Jury:

| M.  | Paul-Alain | ROLLAND    | Président          |

|-----|------------|------------|--------------------|

| M   | Michiel    | STEYAERT   | Rapporteur         |

| M.  | Patrick    | LOUMEAU    | Rapporteur         |

| M.  | Andreas    | KAISER     | Directeur de thèse |

| Mme | Andreia    | CATHELIN   | Examinateur        |

| M.  | Bruno      | STEFANELLI | Examinateur        |

#### **Abstract**

# All-digital RF signal generation using $\Delta\Sigma$ modulation for mobile communication terminals

Mobile communication applications increasingly demand ubiquitous access to wireless networks across multiple standards and frequency bands. Software radio architectures implemented in advanced nanometer scale technologies are largely investigated to meet this challenge. In particular, the interface from the digital to the analog/RF world is projected to move as close as possible towards the antenna. In this work a digital transmitter architecture based on  $\Delta\Sigma$  modulation is investigated, and a prototype digital RF signal generator has been implemented to prove the feasibility of the concept.

The proposed architecture is built around two oversampled  $3^{rd}$ -order lowpass digital  $\Delta\Sigma$  modulators that provide a multiplexed high-speed 1-bit data stream directly coding the RF signal in the digital domain. The modulators noise-shaping transfer functions move the quantization noise out of the transmit band of the considered standard, allowing to reach a high signal-to-noise ratio and extremely low distortion in the transmit band. The output stream can then be fed to an efficient switching-mode power amplifier.

The UMTS standard has been taken as the application example, and a digital RF signal generator providing the 1-bit output stream at 7.8Gs/s has been designed in a 90nm CMOS technology. The effective sampling rate of the low-pass  $\Delta\Sigma$  modulators is in this case 3.9GS/s. Thorough optimization at the architectural and logic level was mandatory: quantized modulator coefficients, redundant arithmetic with complementary signal paths, non-exact output quantization and anticipated output evaluation have been implemented to reach the high sampling rate. 3-phase differential dynamic logic clocked by a DLL has been used at the circuit level.

The fabricated prototype transmitter IC demonstrates full functionality up to a 4GHz main clock frequency, reaching a maximum bandwidth of 50MHz at 1GHz center frequency with a 3.1dBm peak output power. When using the first image band, the transmit band can be moved up to 3 GHz, however with reduced output power due to the sin<sub>c</sub> shaping function.

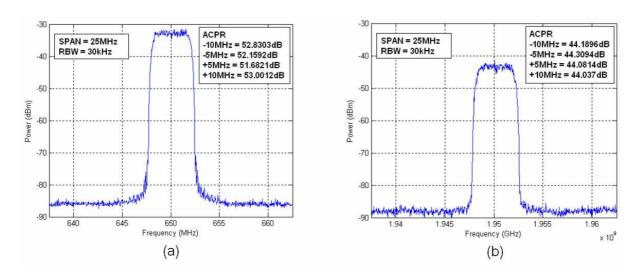

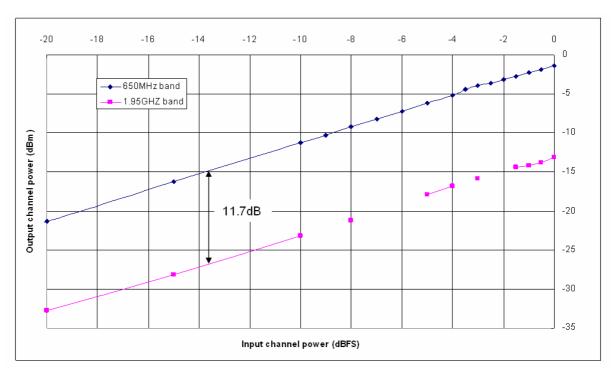

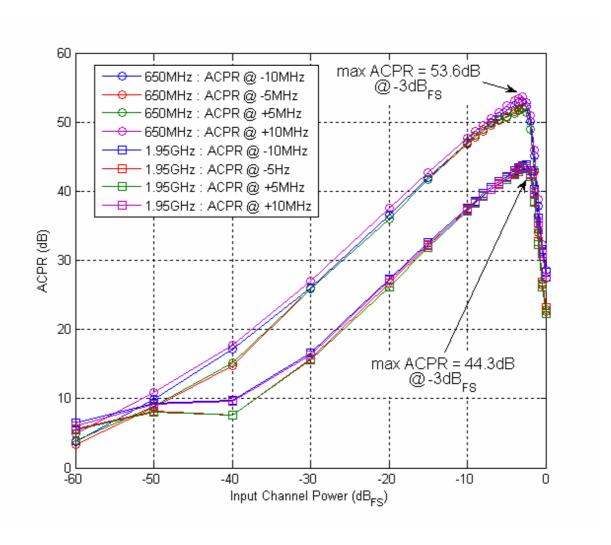

With a 2.6GHz main clock frequency and 5MHz WCDMA modulated channel at a carrier frequency of 650MHz, a channel output power of -3.9dBm and 53.6dB of ACPR are obtained. With the same settings, a channel output power of -15.8dBm and an ACPR of 44.3dB is reached in the 1.95GHz image band, which fulfills minimum UMTS requirements. The chip size is 4×0.8mm² and it has an active area of 0.15mm². Its power consumption is 69mW for a 2.6GHz operating clock frequency.

**Keywords:** delta-sigma modulation, digital transmitter, redundant arithmetic, software radio, RF, UMTS, switching-mode power amplifier, 90nm CMOS.

This thesis work has been performed in the Integrated Circuits Design Group / Microélectronique Silicium of the ISEN department of the Institut d'Electronique, de Microélectronique et de Nanotechnologies (IEMN), 41, bd Vauban, 59000 Lille, France.

#### Résumé

# Génération numérique de signaux RF pour les terminaux de communication mobile par modulation delta-sigma

Les appareils de communications mobiles demandent de plus en plus un accès omniprésent aux réseaux sans fils à travers différents standards et bandes de fréquences. Les architectures radio-logicielles, conçues dans des technologies nanométriques avancées, sont très largement étudiées pour atteindre cet objectif. En particulier, l'interface entre les mondes numériques et analogiques/RF semble se déplacer au plus proche de l'antenne. Dans ce travail, une architecture de transmetteur numérique, basée sur la modulation  $\Delta\Sigma$ , est étudiée et un prototype de générateur de signaux RF numériques a été fabriqué pour prouver ce concept.

L'architecture proposée est construite autour de deux modulateurs  $\Delta\Sigma$  passe-bas suréchantillonnés du 3<sup>ème</sup> ordre qui fournissent un signal multiplexé sur 1 bit à haute cadence, qui code directement le signal RF dans le domaine numérique. Les fonctions de transfert des modulateurs comportent une mise en forme du bruit de quantification pour le déplacer en dehors de la bande d'émission du standard considéré, permettant ainsi d'atteindre un rapport signal-à-bruit élevé et peu de distorsion dans la bande d'émission. La séquence de sortie peut ensuite être appliquée à l'entrée d'un amplificateur de puissance commuté ayant une bonne efficacité.

Le standard UMTS a été choisi comme exemple d'application et un générateur de signaux RF numérique, fournissant un signal de sortie sur 1 bit à 7.8Géch/s a été réalisé dans une technologie 90nm CMOS. La cadence d'échantillonnage effective des modulateurs  $\Delta\Sigma$  passe-bas est dans ce cas de 3.9Géch/s. Une optimisation approfondie au niveau architectural et au niveau logique a été obligatoire : une quantification des coefficients des modulateurs, une arithmétique redondante comprenant des signaux complémentaires, une quantification de sortie non exacte et une évaluation anticipée de la sortie ont été implémentés pour parvenir à la cadence désirée. Une logique dynamique différentielle sur 3 phases d'horloge, générées par une DLL, a été utilisée au niveau circuit.

Le circuit intégré du transmetteur prototype démontre une fonctionnalité complète jusqu'à une fréquence d'horloge de 4GHz, permettant ainsi d'atteindre une bande passante maximum de 50MHz autour d'une fréquence porteuse de 1GHz avec une puissance de sortie en pic de 3.1dBm. Si la première bande image est utilisée, la bande d'émission peut être déplacée jusqu'à 3GHz, avec cependant une puissance de sortie réduite à cause de la fonction de mise en forme du sinus cardinal. Avec une fréquence d'horloge de 2.6GHz et un canal WCDMA de 5MHz modulé autour d'une fréquence porteuse de 650MHz, la puissance de canal en sortie est de -3.9dBm et 53.6dB d'ACLR sont obtenus. Avec les mêmes paramètres, la puissance du canal en sortie est de -15.8dBm et un ACPR de 44.3dB est atteint pour la bande image à 1.95GHz, ce qui rentre dans les spécifications UMTS. Les dimensions du circuit sont 4×0.8mm², tandis que l'aire active est de 0.15mm². La consommation du circuit est de 69mW sous 1V pour une fréquence d'horloge de 2.6GHz.

**Mots-clés :** modulation delta-sigma, transmetteur numérique, arithmétique redondante, radio logicielle, RF, UMTS, amplificateur de puissance commuté, CMOS 90nm.

Thèse preparée dans l'equipe Conception de Circuits Intégrés / Microélectornique Silicium du Département ISEN de l'Institut d'Electronique, de Microélectronique et de Nanotechnologies (IEMN), 41, bd Vauban, 59000 Lille.

## **Acknowledgments**

"With a little help from my friends" (John Lennon and Paul McCartney)

I wish to thank people from the electronic team:

Andreas Kaiser, my thesis director, for his guidance, support and his constant motivation to probe further;

Bruno Stefanelli, for his collaborative efforts on chip design and layout;

Valérie Vandenhende, for her administrative support;

Jean-Marc Capron, for interesting discussions;

Axel Flament, for the fun he brings and the friendly work we have made;

And Manu, Droudrou, Sophie, Jean, Crépin, Christophe, Fanou, Sophie, Ben, Dimitri, Patrick ...

I will miss you when I will leave.

A great acknowledgement to Raphael Daouphars, who sets me on the way to many improvements in my work;

I also thank the faculty of ISEN and IEMN, for its hearty welcome;

Thanks to Andreia Cathelin and her team at STMicroelectronics for interesting meetings and for the access to state-of-the-art technology processes;

Thanks to subcontractors, especially CIBEL firm and Mr Gamberini, for their successful attempts on restrictive assemblies;

Many thanks to Rédha Kassi and Christophe Loyez, from IRCICA, for test facilities;

Thanks to my friends and my family for everyday support;

Thanks to every person who followed this work, closely or by far.

### **Contents**

| Abstract       | •••••••••••••••••••••••••••••••••••••••          | i    |

|----------------|--------------------------------------------------|------|

| Résumé         | ••••••                                           | iii  |

| Acknowledge    | ments                                            | V    |

| Contents       | ••••••                                           | vii  |

| Glossary of a  | acronyms                                         | xi   |

| List of figure | es                                               | xvii |

| List of tables | 5                                                | xxi  |

| Introduction   | ••••••••••••                                     | 1    |

| Chapter 1      | Background                                       | 5    |

| 1.1 Softw      | are defined radio                                | 5    |

|                | Universality of RF transmitters                  |      |

|                | deal software radio                              |      |

|                | of-the-art in transmitter architectures          |      |

|                | Analog front-end architectures                   |      |

|                | Digital IF architecturesDigital RF architectures |      |

|                | S standard specifications                        |      |

|                | ntroduction to UMTS                              |      |

|                | Protocol layers                                  |      |

| 1.3.1.2        | Access mode and frequency allocation             |      |

| 1.3.2 U        | JMTS specifications for transmitters             |      |

| 1.3.2.1        | Spectrum emission mask                           |      |

| 1.3.2.2        | Adjacent Channel Leakage Power Ratio             |      |

| 1.3.2.3        | Spurious emissions                               |      |

| 1.3.2.4        | Error Vector Magnitude                           |      |

| 1.4 Concl      | usion                                            | 19   |

| Chapter 2      | Digital transmitter architecture                 | 21   |

| 2.1 Globa      | ıl transmitter architecture                      | 21   |

| 2.1.1               | Transmitter architecture and frequency planning            | 21 |

|---------------------|------------------------------------------------------------|----|

| 2.1.2               | Digital upconversion and noise-shaping architecture        |    |

| 2.1.3               | Power amplifier and antenna filters                        |    |

| 2.1.3.              |                                                            |    |

| 2.1.3.              | Power DAC non-idealities                                   | 32 |

| 2.1.3.              | 3 Antenna filters                                          | 34 |

| 2.2 UM              | ITS implementation case of the digital transmitter         | 36 |

| 2.2.1               | Proposed digital transmission chain                        | 36 |

| 2.2.2               | Baseband processing                                        | 36 |

| 2.2.3               | Sample rate conversion                                     | 39 |

| 2.2.4               | Digital $\Delta\Sigma$ modulators                          | 41 |

| 2.2.4.              | 1 Lowpass $\Delta\Sigma$ modulator architecture            | 41 |

| 2.2.4.              | 2 Simulated performances                                   | 43 |

| 2.3 Coi             | nclusion                                                   | 44 |

| Chapter 3           | Delta-Sigma modulator system design                        | 47 |

| •                   |                                                            |    |

|                     | architecture optimization                                  |    |

| 3.2 Log             | gic design issues                                          |    |

| 3.2.1               | Critical path and digital implementation issues            |    |

| 3.2.2               | Adder architectures analysis                               |    |

| 3.2.3               | Circuit level adders design considerations                 | 54 |

| $3.3  \Delta\Sigma$ | architecture with redundant arithmetic                     | 56 |

| 3.3.1               | Redundant number representation                            | 56 |

| 3.3.2               | Structures for redundant addition                          | 57 |

| 3.3.3               | $\Delta\Sigma$ modulator architecture in BS representation | 61 |

| 3.3.4               | Simulation results                                         |    |

| 3.4 Out             | put quantizer in Borrow-Save arithmetic                    | 65 |

| 3.4.1               | Non-exact quantization                                     | 65 |

| 3.4.2               | Output signal precomputation                               | 69 |

| 3.5 Co              | nclusion                                                   | 70 |

| Chapter 4           | Digital transmitter circuit design                         | 73 |

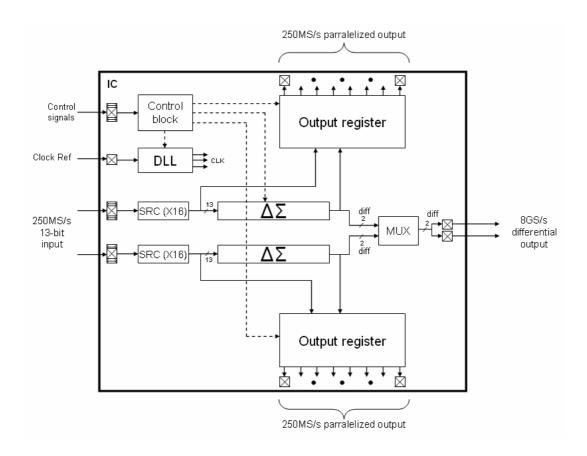

| 4.1 Tra             | nsmitter IC description                                    | 73 |

| 4.1.1               | IC structure                                               | 73 |

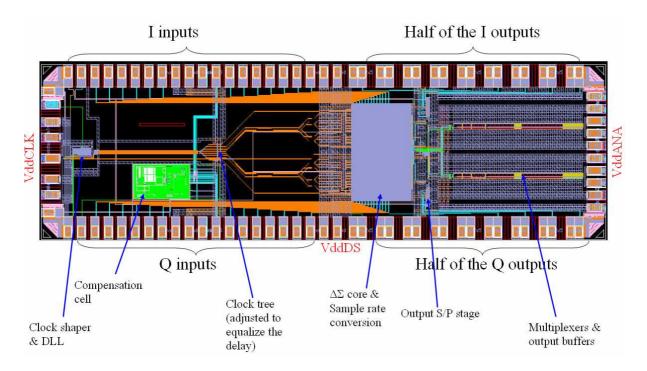

| 4.1.2               | IC configuration and layout                                | 74 |

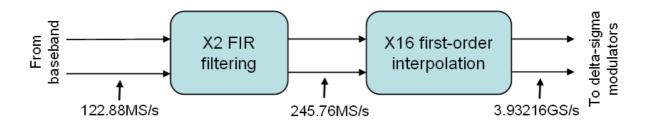

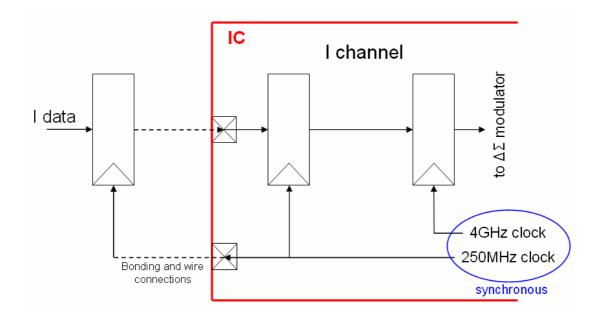

| 4.2 San             | nple rate conversion block design                          |    |

| 4.2.1               | Block structure                                            | 75 |

| 4.2.2               | TSPCFF registers                                           | 78 |

| 4.3 Dig             | rital delta-sigma modulator circuit design                 | 81 |

| 4.3.1               | Global structure                                           |    |

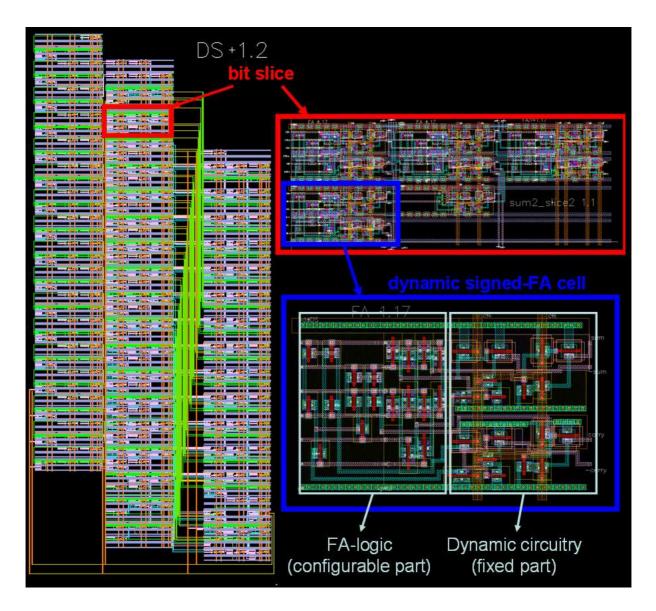

| 4.3.2               | Dynamic FA circuit description                             | 82 |

| 4.3.3               | Initialization circuitry                                   |    |

| 4.3.4               | $\Delta\Sigma$ modulator layout view                       |    |

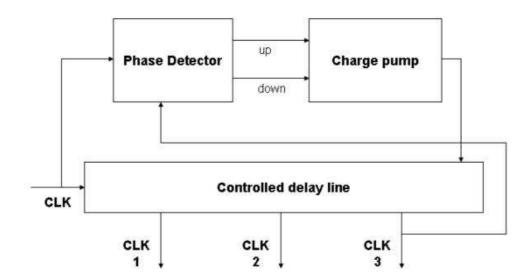

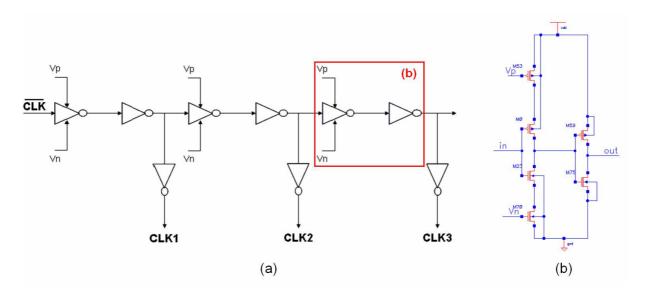

| 4.4 Clo             | ck generation and distribution                             |    |

| 4.4.1               | Controlled delay line description                          |    |

| 4.4.2               | Phase comparator and charge pump                           |    |

| 4.4.3               | DLL mechanism and clock signals characteristics            |    |

| 4.5 Dig             | ital mixer and output stages design                        |    |

| _                   | Digital mixer structure                                    | 94 |

| 4.5.2       | Output stages                                        | 95  |

|-------------|------------------------------------------------------|-----|

| 4.6 Cor     | clusion                                              |     |

| Chapter 5   | Experimental results                                 | 97  |

| 5.1 Firs    | t prototype IC (FULBERT I)                           | 97  |

| 5.1.1       | Test hardware description                            |     |

| 5.1.1.1     | 1                                                    |     |

| 5.1.1.2     |                                                      |     |

| 5.1.2       | Measurement results                                  |     |

| 5.1.2.1     |                                                      |     |

| 5.1.2.2     |                                                      |     |

| 5.2 Sec     | ond prototype IC (FULBERT II)                        |     |

| 5.2.1       | Changes and enhancements                             |     |

| 5.2.2       | Test hardware description                            | 105 |

| 5.2.3       | Measurement results                                  | 106 |

| 5.2.3.1     | Core functionality                                   | 107 |

| 5.2.3.2     | Measurement results at a 2.6GHz main clock frequency | 108 |

| Free        | quency Spectra                                       | 108 |

|             | PR vs Channel Power                                  |     |

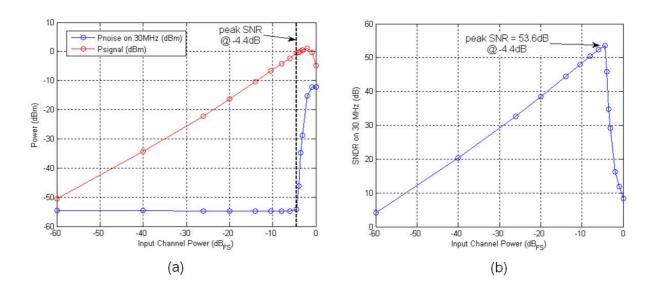

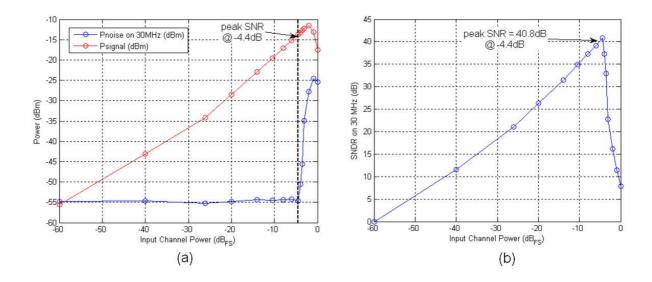

| SNI         | OR vs Channel Power                                  | 113 |

| EV          | M measurements                                       | 114 |

| Out         | put Jitter                                           | 115 |

| Sun         | nmary of measurements with a 2.6GHz main clock       | 116 |

| 5.2.3.3     | 1                                                    |     |

| Pov         | ver consumption                                      | 117 |

|             | lution of ACPR                                       |     |

|             | lution of SNDR                                       |     |

|             | lution of EVM                                        |     |

|             | lution of the channel power                          |     |

|             | lution of the jitter                                 |     |

|             | nmary of measurements                                |     |

|             | Comparison with similar works                        |     |

| 5.3 Cor     | clusion                                              | 125 |

| Conclusion  | ••••••                                               | 127 |

| Pare        | allel works                                          | 127 |

|             | onfigurability                                       |     |

|             | are directions                                       |     |

| Ribliogran) | hy                                                   | 131 |

| Dionograpi  |                                                      |     |

| Résumé en   | français                                             | I   |

|             | itexte                                               |     |

|             | hitecture du transmetteur numérique                  |     |

|             | ception système du modulateur $\Delta\Sigma$         |     |

|             | ception circuit du transmetteur numérique            |     |

|             | ultats expérimentaux                                 |     |

| Cor         | clusion                                              | XII |

### Glossary of acronyms

$\Delta\Sigma$  Delta-Sigma

3G Third Generation of mobile phone wireless systems

4G Fourth Generation of mobile phone wireless systems

ACLR Adjacent Channel Leakage Ratio

ACPR Adjacent Channel Power Ratio

ADC Analog-to-Digital Conversion/Converter

AWG Arbitrary Waveform Generator

BAW Bulk Acoustic Wave

BP BandPass

BPF BandPass Filter

BS Borrow-Save

BSD Binary Signed-Digit

C2 Two's complement

CDMA Code Division Multiple Access

CDMA2000 Code Division Multiple Access 3G US standard

CIC Cascade Integrator Comb

CIFB Cascade of Integrators with FeedBacks

CIFF Cascade of Integrators with FeedForwards

CLA Carry-LookAhead adder

CLK Clock

CMOS Complementary Metal Oxide Semiconductor

CORDIC Coordinate Rotation Digital Computing

CPL Complementary Pass-transistor Logic

CSA Carry-Save adder

CSK Carry-Skip adder

CSL Carry-SeLect adder

DAC Digital-to-Analog Conversion/Converter

dBc Power referenced to a carrier power, expressed in decibels

dB<sub>FS</sub> Power referenced to a full-scale sine wave, expressed in decibels

dBm Power referenced to 1 milliWatt, expressed in decibels

DC Direct Current

DCO Digitally Controlled Oscillator

DCS Digital Cellular System

DDR Double Data Rate

DECT Digital Enhanced Cordless Telecommunications

DLL Delay Locked Loop

DPCCH Dedicated Physical Control CHannel

DPDCH Dedicated Physical Data CHannel

DPL Double Pass-transistor Logic

DRFC Digital-to-RF Converter/Conversion

DS-CDMA Direct-Sequence Code Division Multiple Access

DS-SS Direct-Sequence Spread Spectrum

DSP Digital Signal Processing/Processor

DUT Device Under Test

ENOB Effective Number Of Bits

ETSI European Telecommunications Standards Institute

EVM Error Vector Magnitude

FA Full-Adder

FAMMP Minus-Minus-Plus Full-Adder

FAPPM Plus-Plus-Minus Full-Adder

FDD Frequency Division Duplex

FFT fast Fourier Transform

FIR Finite Impluse Response

FH-SS Frequency Hopping Spread Sprectrum

FPGA Field Programmable Gate Array

FS Full-Scale

GSM Global System for Mobile communications

GS/s Giga Samples per second

HA Half-Adder

HiperLAN2 High Performance Radio Local Area Network type 2

HPSK Hybrid Phase Shift Keying

IEEE Institute of Electrical and Electronics Engineers

IEEE802.11 Technology associated with WLAN defined by IEEE

IEEE802.20 Technology associated with MBWA defined by IEEE

IC Integrated Circuit

IF Intermediate Frequency

INS Integral Noise Shaping

IS-95 Interim Standard 95 (known as cdmaOne)

ISI Inter-Symbol Interference

I/O Input/Output

LO Local Oscillator

LP LowPass

LPDSM Low-Pass Delta-Sigma Modulator

LPF LowPass Filter

LSB Least Significant Bit

MAC Medium Access Control

MBWA Mobile Broadband Wireless Access

Mc/s Mega chips per second

MCC Manchester Carry Chain

MS/s Mega Samples per second

MSB Most Significant Bit

MUX Multiplexer

NMOS N-type Metal Oxide Semiconductor

NTF Noise Transfer Function

PA Power Amplifier

PAPR Peak-to-Average Power Ratio

PCB Printed Circuit Board

PHS Personal Handy-phone System

PHY PHYsical layer

PMOS P-type Metal Oxide Semiconductor

PN Pseudo-Noise

PWM Pulse Width Modulation

QPSK Quaternary Phase Shift Keying

RCA Ripple Carry Adder

RF Radio Frequency

RLC Radio Link Control

RRC Radio Ressource Control

RRC Root-Raised Cosine

RS Reset-Set

RX Reception

S/P Serial-to-Parallel

SD-r Signed-Digit adder in base r

SDR Software Defined Radio

SFDR Spurious Free Dynamic Range

SiP System in Package

SNDR Signal-to-Noise and Distortion Ratio

SNR Signal-to-Noise Ratio

SRC Sample Rate Conversion/Converter

STF Signal Tranfer Function

SoC System on Chip

TDCDMA Time Division Code Division Multiple Access

TDD Time Division Duplex

TSPCFF True Single-Phase Clock Flip-Flop

TX Transmission

UE User Equipment

UMTS Universal Mobile Telecommunications System

VHDL Very high speed IC Hardware Description Language

WCDMA Wideband Code Division Multiple Access

Wi-Fi Wireless Fidelity

Wimax Worldwide Interoperability for Microwave Access

WLAN Wireless Local Area Network

# **List of figures**

| Figure 1-1 Ideal software-defined radio transmitter                                                                                               | 6         |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Figure 1-2 Toward RF digital processing and software radio                                                                                        | 7         |

| Figure 1-3 Heterodyne transmitter architecture                                                                                                    | 8         |

| Figure 1-4 Homodyne transmitter architecture                                                                                                      | 8         |

| Figure 1-5 Digital-IF transmitter architecture                                                                                                    | 9         |

| Figure 1-6 Digital quadrature modulator from [10]                                                                                                 | 9         |

| Figure 1-7 Conceptual block diagram of the digital-IF heterodyne transmitter from [12]                                                            |           |

| Figure 1-8 Digital RF transmitter chain                                                                                                           | . 10      |

| Figure 1-9 DSP-based wireless transmitter architecture from [5]                                                                                   | . 11      |

| Figure 1-10 Radio interface protocol structure [22]                                                                                               |           |

| Figure 1-11 Examples of access modes for GSM, UMTS TDD and FDD                                                                                    | . 14      |

| Figure 1-12 Example of a RRC-shaped UMTS channel                                                                                                  |           |

| Figure 1-13 UMTS spectrum emission mask (related to a 1MHz measurement bandwidth)                                                                 | . 16      |

| Figure 1-14 UMTS spurious requirements                                                                                                            | . 18      |

| Figure 1-15 Amplitude and phase errors defining EVM                                                                                               | . 19      |

| Figure 2-1 Digital transmitter architecture. $f_{\it chip}$ is the chip rate, $f_{\it c}$ the carrier frequency and                               | nd        |

| $f_s$ the sampling frequency                                                                                                                      | . 21      |

| Figure 2-2 Modulator output spectrum for channels at the lowest band edge for (a) direct                                                          | 22        |

| conversion and (b) two-step conversion.                                                                                                           |           |

| Figure 2-3 Two-step upconversion transmitter architecture. <i>L</i> is a factor dependent over the chosen standard.                               | e<br>. 23 |

| Figure 2-4 Digital mixer operation. The sample rate is $4 \times f_c$ and $n = 0,4,8,12,$                                                         | . 24      |

| Figure 2-5 Possible architectures for noise shaper and upconverter: a) Bandpass $\Delta\Sigma$                                                    |           |

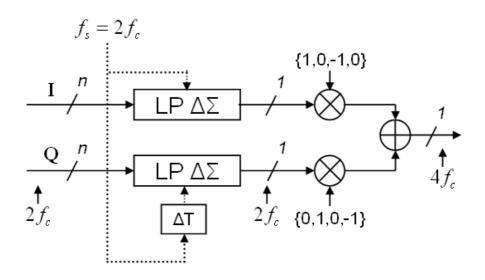

| modulator; b) Lowpass $\Delta\Sigma$ modulators                                                                                                   | 26        |

| Figure 2-6 Simplified architecture if only one sample on two is computed inside the $\Delta\Sigma$                                                | . 20      |

| modulators. The $\Delta T$ delay is equal to $1/4f_c$                                                                                             | 27        |

| ,                                                                                                                                                 |           |

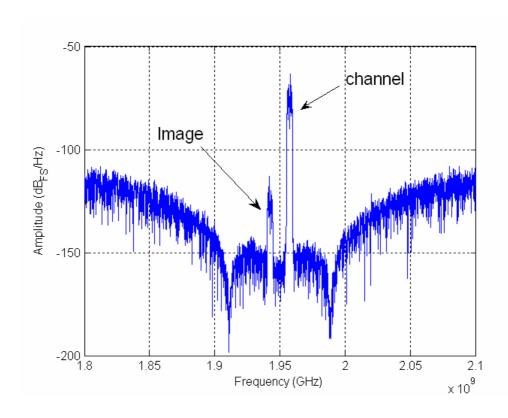

| Figure 2-7 Frequency spectrum of the output of the digital upconverter when no interpolation is done on Q channel, showing the image that appears |           |

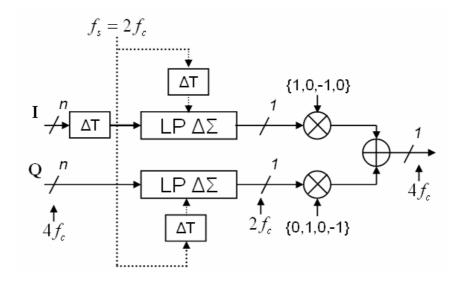

| Figure 2-8 Architecture if the $\Delta\Sigma$ modulators sampling clocks are synchronous                                                          |           |

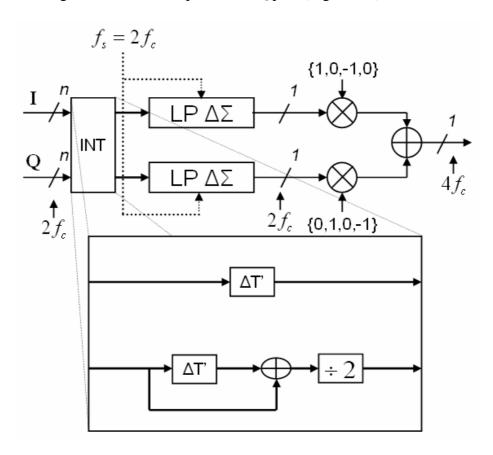

| Figure 2-9 Chosen architecture using a linear interpolation on Q channel. $\Delta T$ ' delay is equa                                              |           |

| to $1/2f_c$                                                                                                                                       |           |

| Figure 2-10 Digital upconverter output spectrum. $8^{th}$ channel is chosen. $0dB_{FS}$ refers to a fu                                            | . 29      |

|                                                                                                                                                   |           |

| scale sine wave.                                                                                                                                  |           |

| Figure 2-11 On the left, schematic of the output inverter; on the right, a diagram showing the                                                    |           |

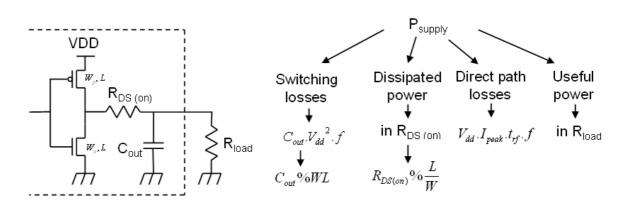

| repartition of the power supply                                                                                                                   |           |

|                                                                                                                                                   |           |

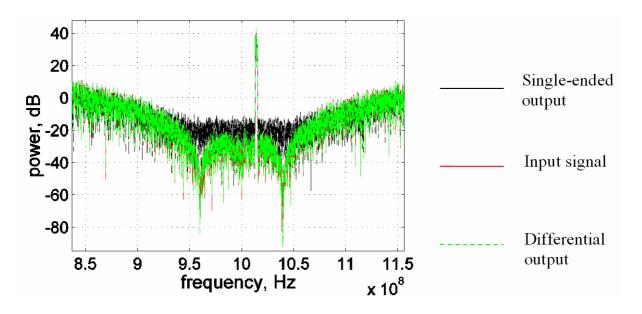

| Figure 2-13 Output spectra for ideal, single-ended and differential outputs                                                                       | . 33      |

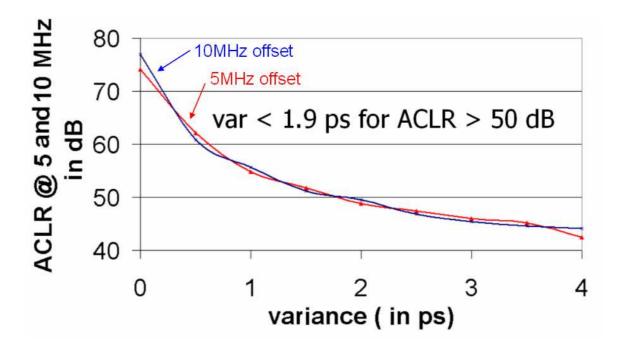

| random jitter variance                                                                                                                            | 3/1       |

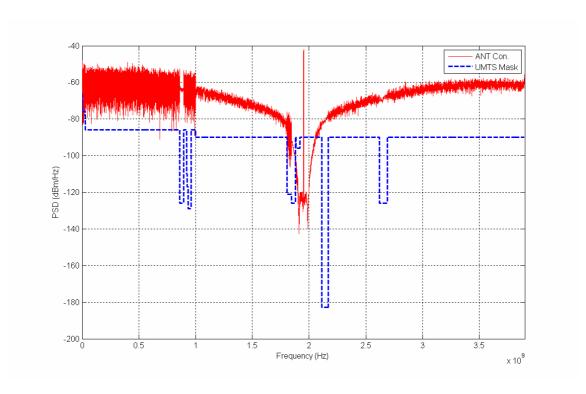

| Figure 2-15 Digital RF output reported to the antenna (the standard measurement bandwidt                                                          |           |

| has been respected (Table 1-3)) and UMTS spectrum requirements                                                                                    |           |

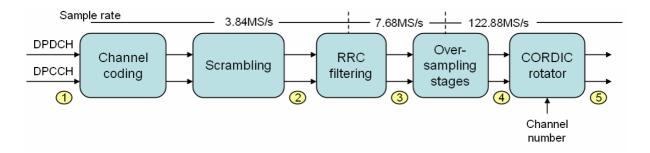

| Figure 2-16 Proposed transmitter chain                                                                                                            |           |

| m                                                                                                                                                 |           |

| Figure 2-17 Baseband processing blocks                                                                    | 37 |

|-----------------------------------------------------------------------------------------------------------|----|

| Figure 2-18 Baseband signals at each step of the baseband processing                                      | 38 |

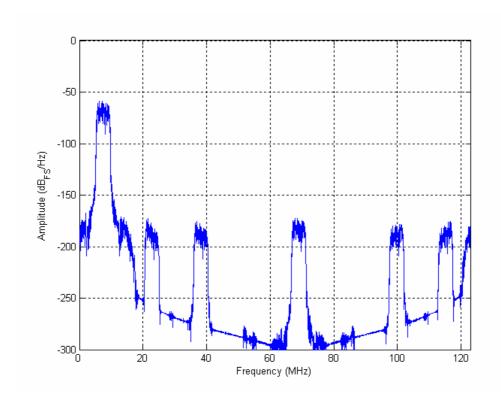

| Figure 2-19 Spectrum of the IQ baseband output signal (9 <sup>th</sup> channel is chosen arbitrarily).    |    |

| Amplitude is referred to 0dB <sub>FS</sub> (full-scale sine wave).                                        | 39 |

| Figure 2-20 Sample rate conversion blocks                                                                 | 40 |

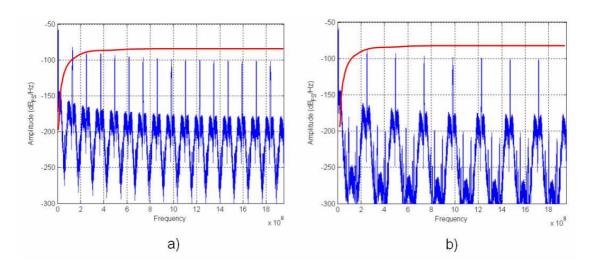

| Figure 2-21 Spectrums of the 3.9GS/s SRC output signals for the two configurations                        |    |

| previously cited. In red, the estimated shaped quantization noise brought by the $\Delta\Sigma$           |    |

| modulator.                                                                                                | 40 |

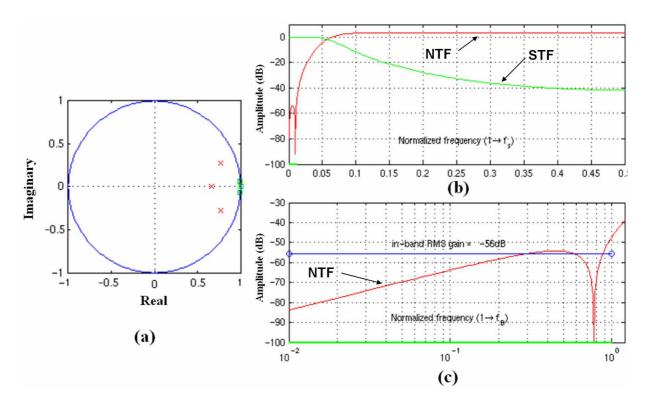

| Figure 2-22 (a) Pole-zero diagram (pole: x; zero: o); (b) NTF (red) and STF (green) of the                |    |

| generated $\Delta\Sigma$ modulator (frequency is normalized to $f_s$ =3.9GHz); (c) zoom on the            |    |

| bandwidth ( $f_b$ =30MHz)                                                                                 | 41 |

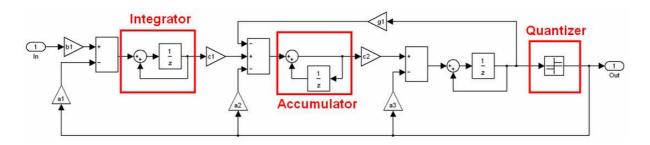

| Figure 2-23 Third-order $\Delta\Sigma$ modulator architecture                                             | 42 |

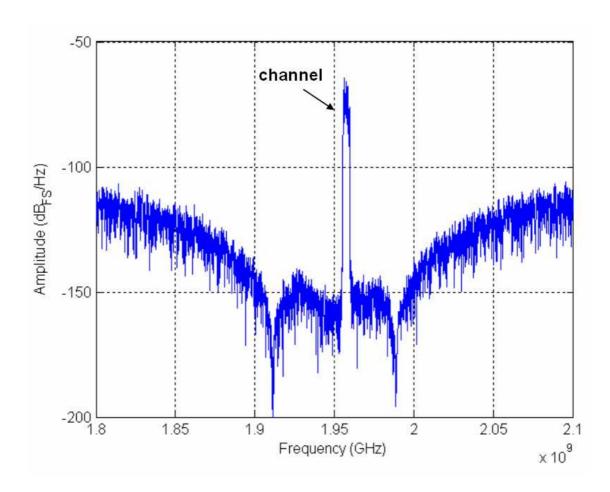

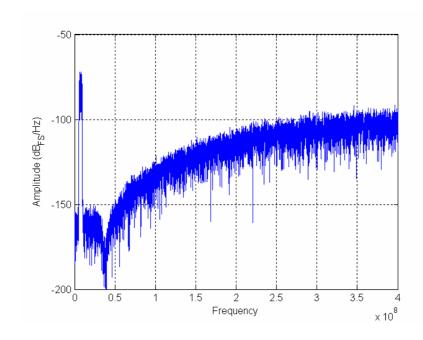

| Figure 2-24 $\Delta\Sigma$ modulator output spectrum                                                      | 43 |

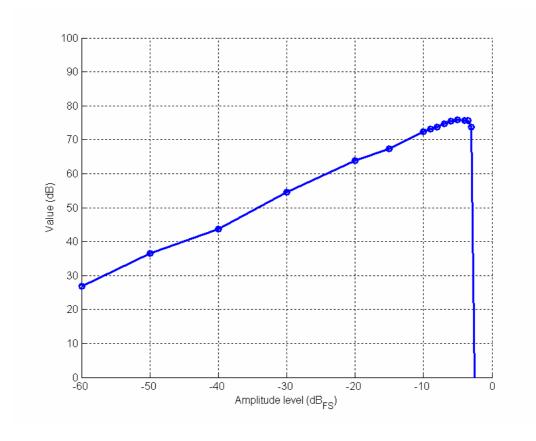

| Figure 2-25 Simulated SNDR for the ideal configuration                                                    | 44 |

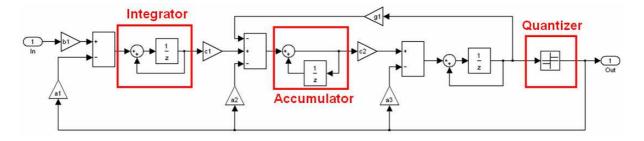

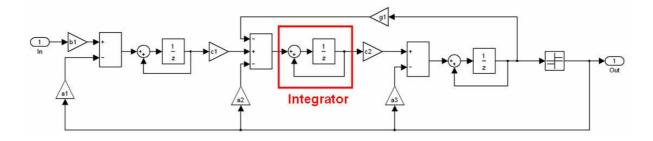

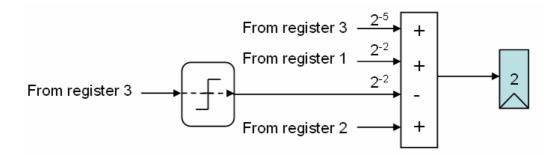

| Figure 3-1 Third-order $\Delta\Sigma$ modulator architecture                                              |    |

| Figure 3-2 Optimized $\Delta\Sigma$ architecture. The accumulator has been replaced by an integrator.     | 49 |

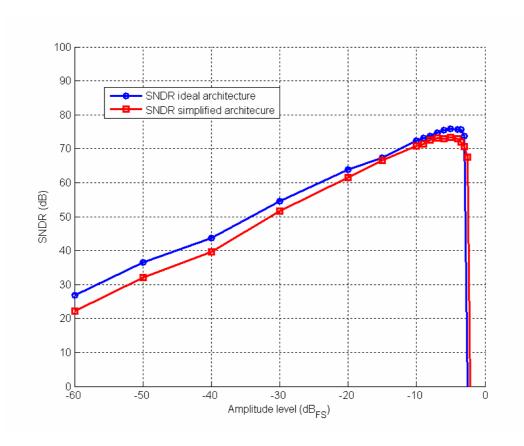

| Figure 3-3 SNDR comparison for ideal and simplified architecture                                          | 49 |

| Figure 3-4 $\Delta\Sigma$ modulator architecture showing data registers                                   | 50 |

| Figure 3-5 Critical path                                                                                  | 51 |

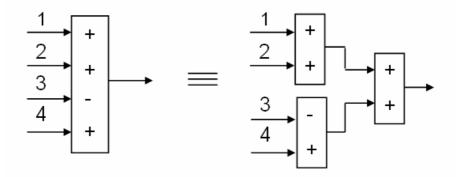

| Figure 3-6 Architecures for 4-inputs additions                                                            | 51 |

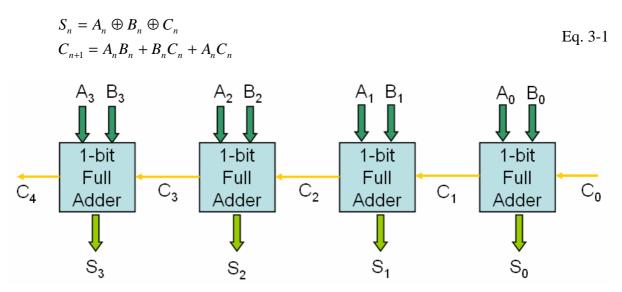

| Figure 3-7 4-bit Ripple Carry Adder architecture                                                          | 52 |

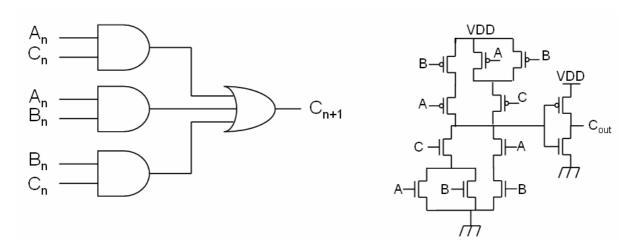

| Figure 3-8 Carry combinational logic and STMicroelectronics 90nm design kit static logic                  |    |

| implementation                                                                                            |    |

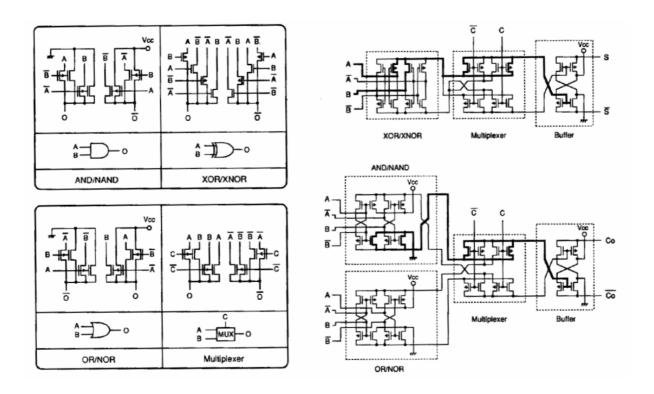

| Figure 3-9 DPL gates and full-adder implementation [48]                                                   |    |

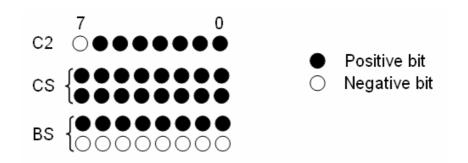

| Figure 3-10 Dot notation of two's complement, Carry-Save and Borrow-Save representation                   | n  |

|                                                                                                           |    |

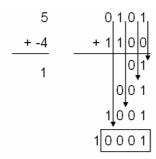

| Figure 3-11 Addition in two's complement                                                                  | 58 |

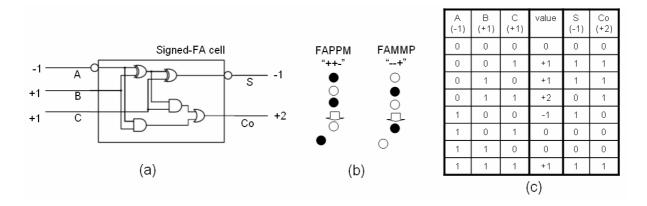

| Figure 3-12 (a) "++-"-type signed-FA cell; (b) dot notation for "++-" FAPPM and "+"                       |    |

| FAMMP types and (c) logic table related to the signed-FA cell                                             |    |

| Figure 3-13 Addition process of two BS numbers. Little dots are free places                               |    |

| Figure 3-14 Addition in BS notation                                                                       |    |

| Figure 3-15 Addition process of a BS number and a 2's complement number                                   |    |

|                                                                                                           | 60 |

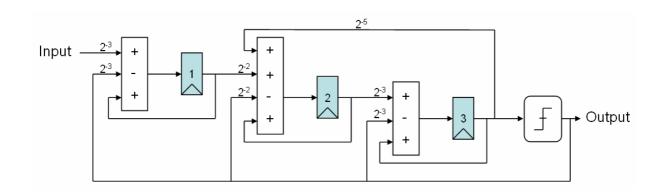

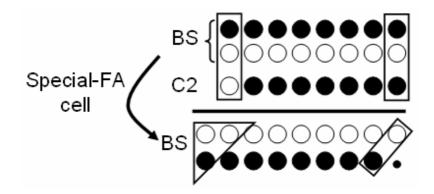

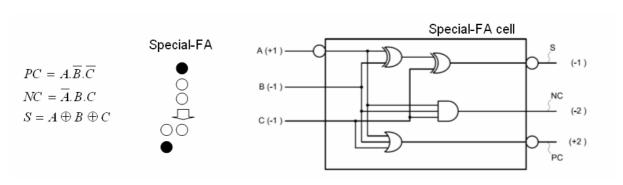

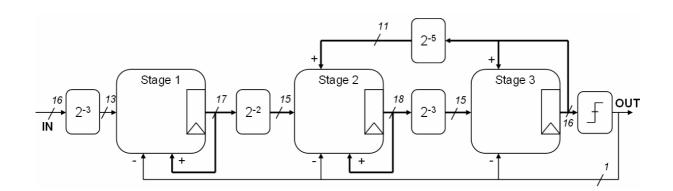

| Figure 3-17 Third-order $\Delta\Sigma$ modulator architecture                                             |    |

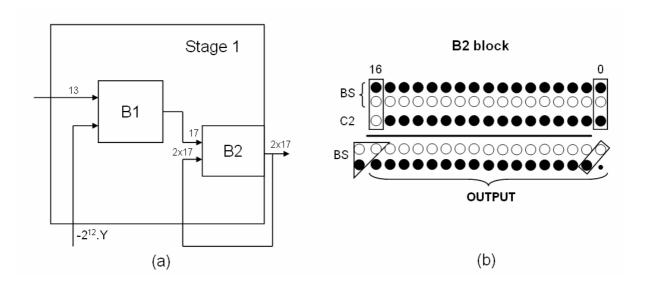

| Figure 3-18 (a) Details of the first stage and (b) dot notation associated with the B2 block              |    |

| Figure 3-19 Details of the B1 block                                                                       |    |

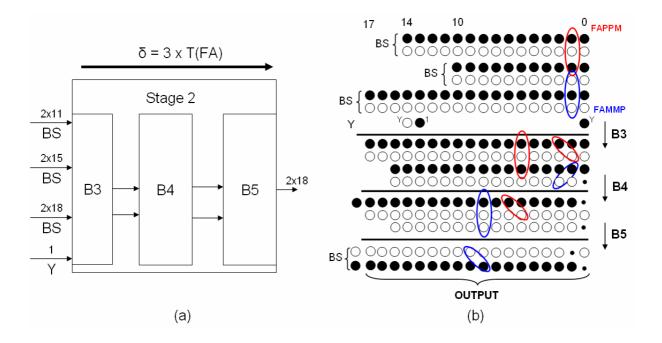

| Figure 3-20 (a) Details of the second stage and (b) dot notation associated with B3,B4 and I              |    |

| computation blocks                                                                                        |    |

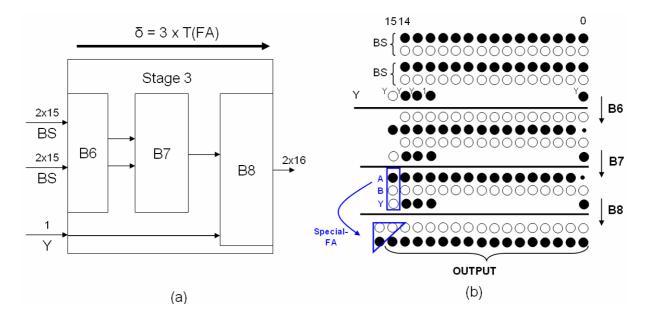

| Figure 3-21 (a) Details of the third stage and (b) dot notation associated with B6,B7 and B8              |    |

| computation blocks                                                                                        |    |

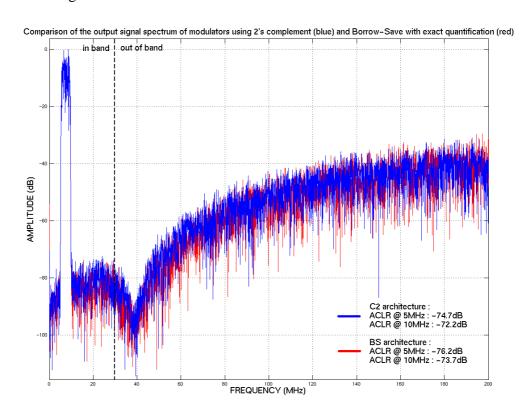

| Figure 3-22 ACLR performance comparison on the $\Delta\Sigma$ modulator output signal spectrum for        |    |

| 2's complement (blue) and Borrow-Save (red) architectures                                                 |    |

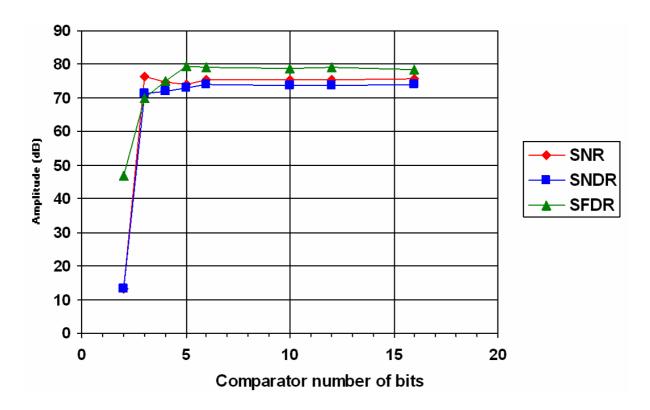

| Figure 3-23 Evaluation of the $\Delta\Sigma$ modulator performances with non-exact quantization           | 6/ |

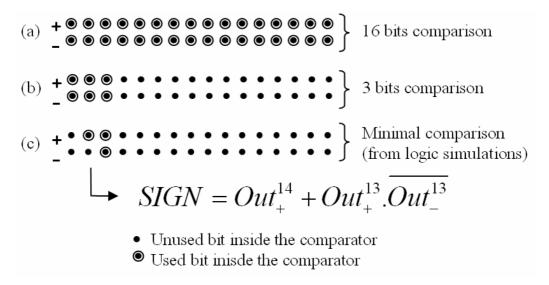

| Figure 3-24 (a), (b) and (c): Dot notations related to the bits considered inside the logic               | 67 |

| comparator                                                                                                |    |

|                                                                                                           |    |

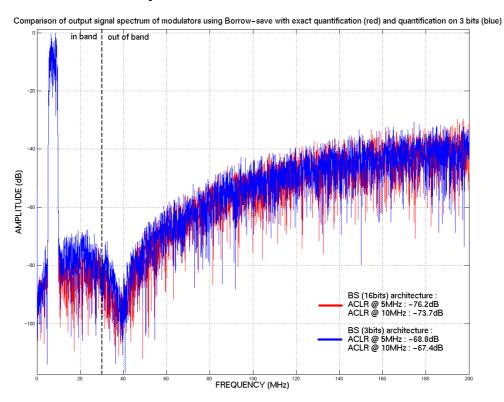

| BS architecture with exact (red) and non-exact (red) quantization                                         | υŏ |

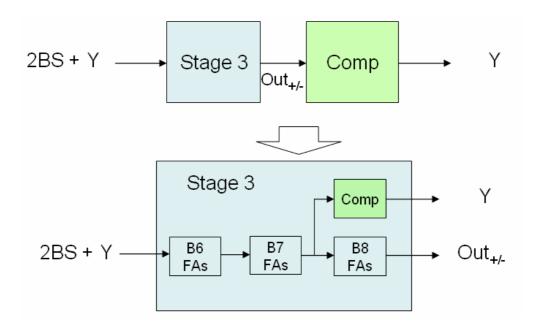

| Figure 3-26 Precomputation of the sign; <i>Y</i> is evaluated in parallel with the stage 3 output signal. | 60 |

| C                                                                                                         | 73 |

| Figure 4-2 IC block structure                                                                           | 74    |

|---------------------------------------------------------------------------------------------------------|-------|

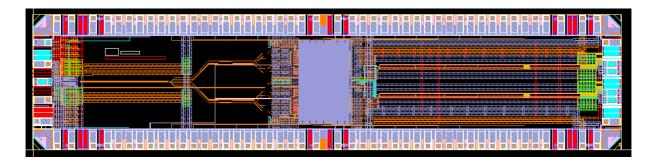

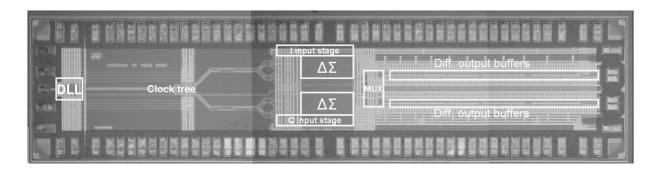

| Figure 4-3 First prototype IC layout                                                                    | 75    |

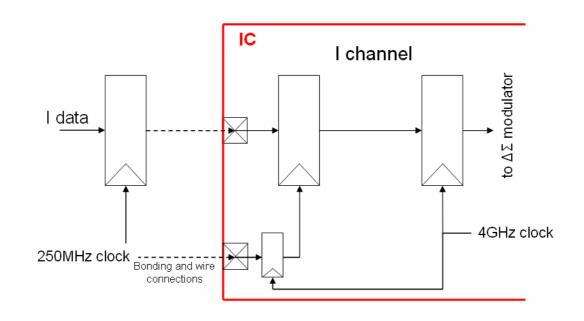

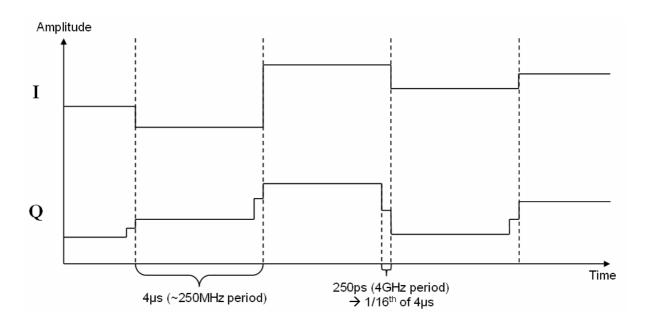

| Figure 4-4 Input sample rate conversion block and clock scheme                                          | 76    |

| Figure 4-5 Clock scheme used for data acquisition in the second prototype IC                            | 77    |

| Figure 4-6 Qualitative I and Q signals at the $\Delta\Sigma$ modulators input. Q signal has been linear | rly   |

| interpolated on each sample                                                                             | 78    |

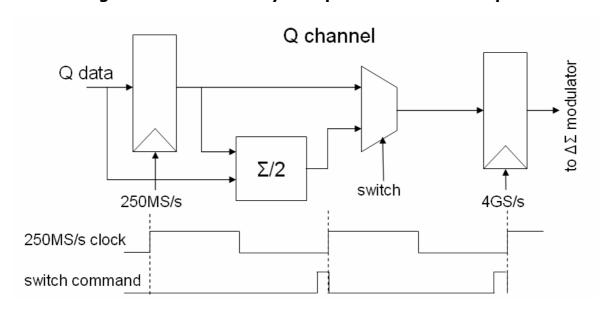

| Figure 4-7 Linear interpolation on Q channel inside SRC block                                           | 78    |

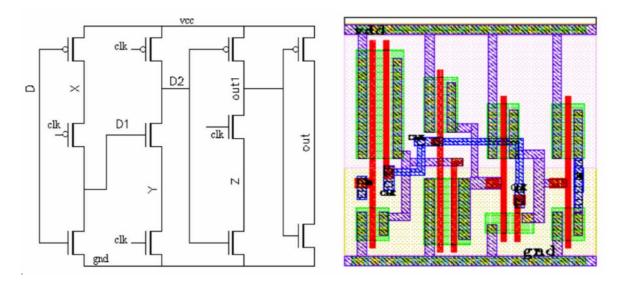

| Figure 4-8 Schematic and layout of the TSPCFF                                                           | 79    |

| Figure 4-9 Mechanism inside the TSPCFF when clock signal is low (left) and high (right)                 | 80    |

| Figure 4-10 Eye diagram of the TSPCFF output signal for a typical process corner and a                  |       |

| temperature of 80°C                                                                                     | 80    |

| Figure 4-11 Third-order $\Delta\Sigma$ modulator architecture                                           | 81    |

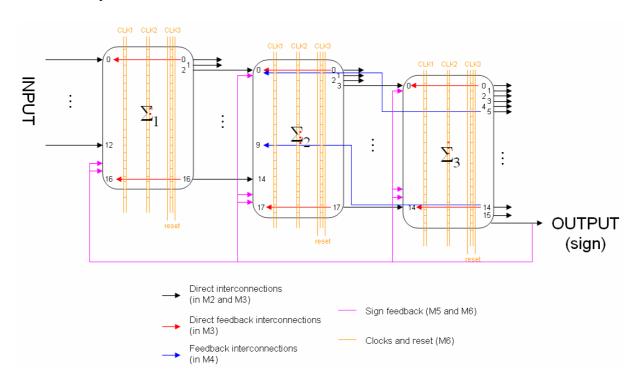

| Figure 4-12 Layout of the basic bricks and relationship between the three different clocks              | 82    |

| Figure 4-13 Differential dynamic FA cell circuit diagram (transistor gate lengths are mini-             | mal)  |

|                                                                                                         |       |

| Figure 4-14 Transient response of a FA cell with an ideal clock                                         | 83    |

| Figure 4-15 Dynamic FA cell circuit diagram, including the reset circuitry                              | 85    |

| Figure 4-16 Dynamic FA cell circuit diagram, with an improved reset circuitry (The FA le                |       |

| has been split in two differential blocks)                                                              | 86    |

| Figure 4-17 $\Delta\Sigma$ modulator layout routing strategy                                            | 87    |

| Figure 4-18 $\Delta\Sigma$ modulator layout                                                             | 88    |

| Figure 4-19 Global structure of a DLL                                                                   | 89    |

| Figure 4-20 Inverter chain constituting the voltage-controlled delay line                               | 90    |

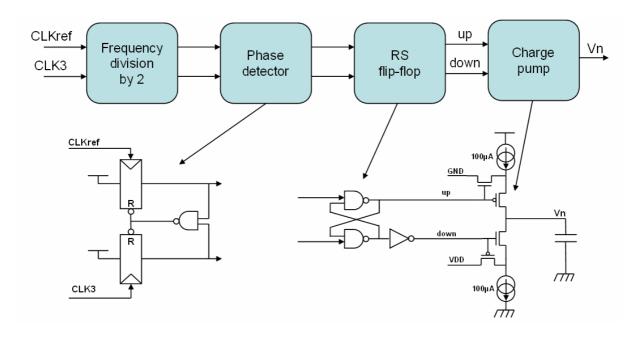

| Figure 4-21 Phase comparator and charge pump schematics                                                 | 91    |

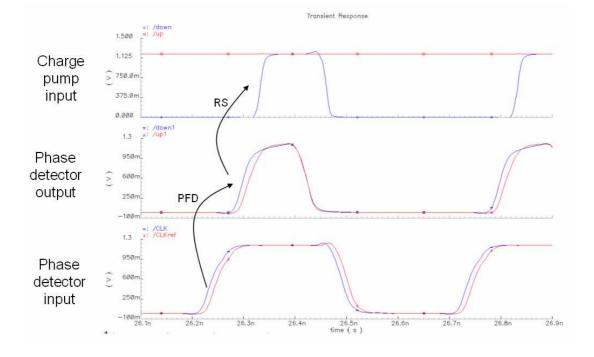

| Figure 4-22 Phase comparator and charge pump signals                                                    | 91    |

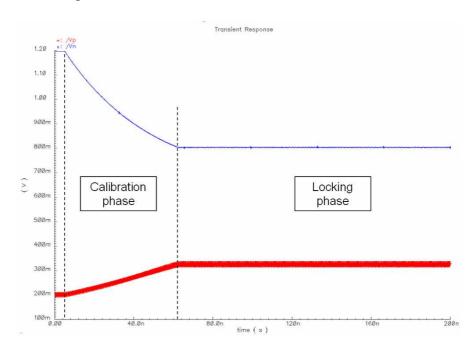

| Figure 4-23 Evolution of <i>Vn</i> and <i>Vp</i> during calibration and locking phases                  | 92    |

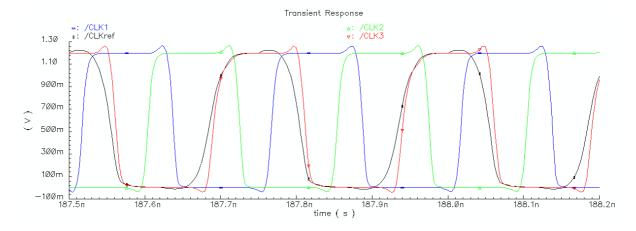

| Figure 4-24 CLK1, CLK2, CLK3 and reference clock waveforms.                                             | 92    |

| Figure 4-25 Differential output stages architecture                                                     | 93    |

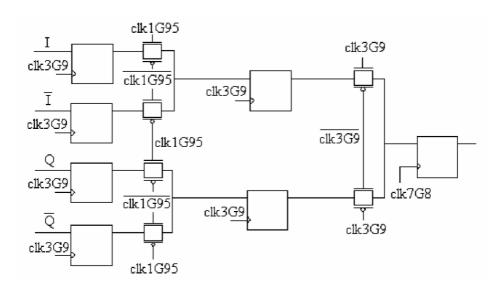

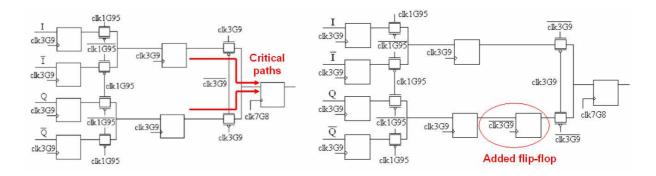

| Figure 4-26 Multiplexer architecture                                                                    | 94    |

| Figure 4-27 Multiplexer architecture, showing (left) critical paths and (right) the adopted             |       |

| solution for data-independent signal paths                                                              | 95    |

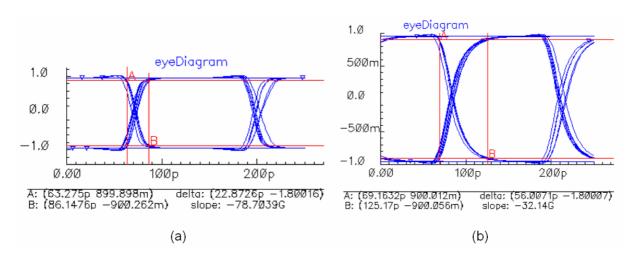

| Figure 4-28 Eye diagrams for $50\Omega$ -loaded buffers differential output signals for a slow          |       |

| process corner at 80°C (a) without and (b) with an electrical model for pads and bond                   | ding  |

| wires                                                                                                   |       |

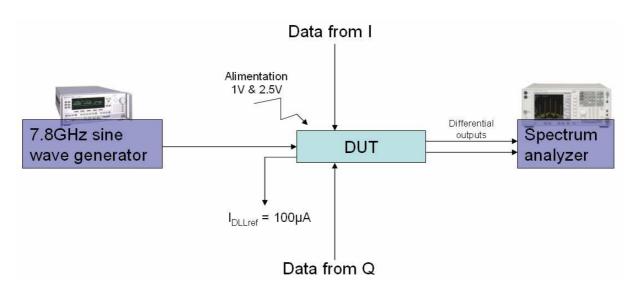

| Figure 5-1 Test hardware for the analog output analysis                                                 |       |

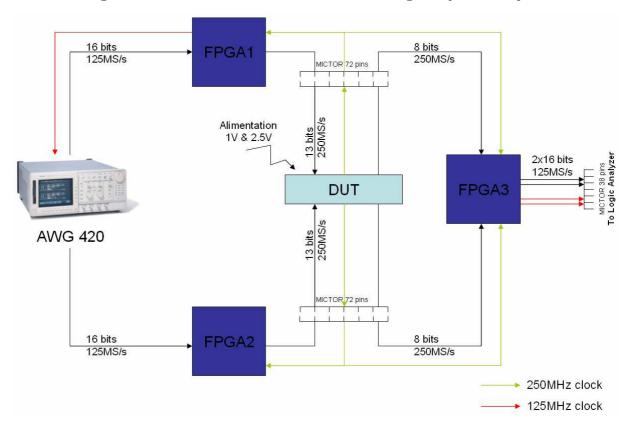

| Figure 5-2 Test hardware for the digital output test                                                    |       |

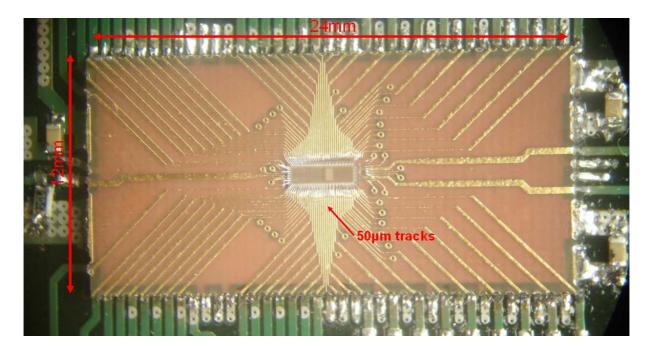

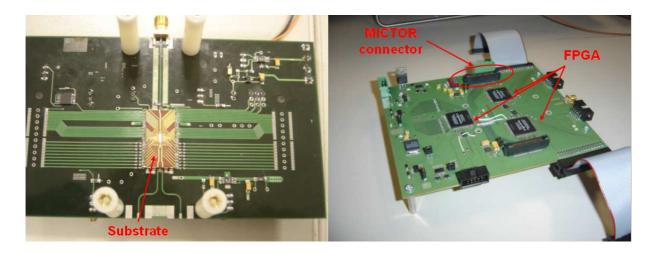

| Figure 5-3 IC wire bonded on the substrate, soldered on the daughter board                              |       |

| Figure 5-4 Daughter board (left) and motherboard (right)                                                |       |

| Figure 5-5 IC post-simulation with bonding wires                                                        |       |

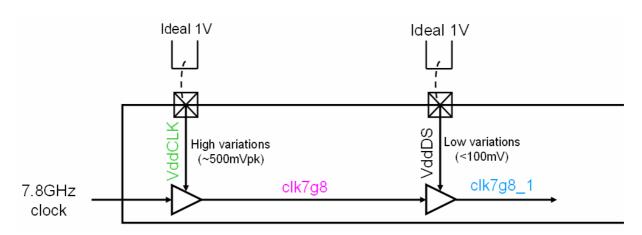

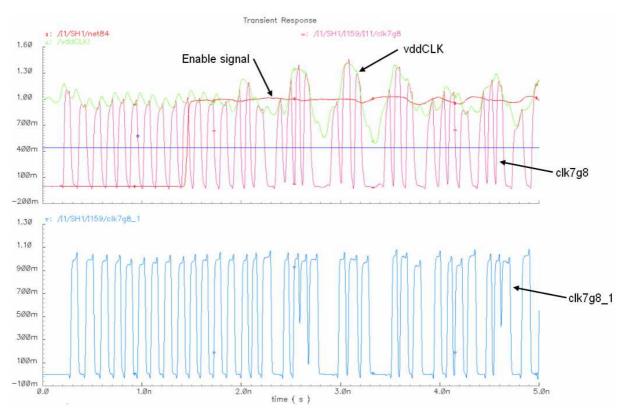

| Figure 5-6 Transient post-simulation according to Figure 5-5                                            |       |

| Figure 5-7 Eye diagram of the IC output for a 3.9GHz input clock. The IC has been placed                |       |

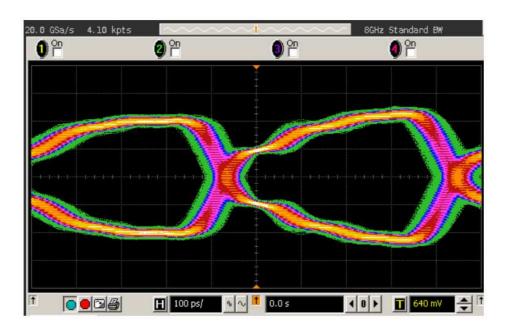

| its reset state                                                                                         |       |

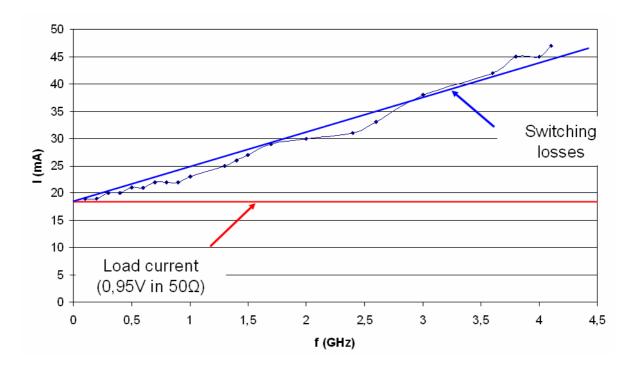

| Figure 5-8 Current consumption in output stages                                                         | . 103 |

| Figure 5-9 Layout of the second prototype IC                                                            |       |

| Figure 5-10 Die microphotograph of the prototype chip in 90nm CMOS                                      |       |

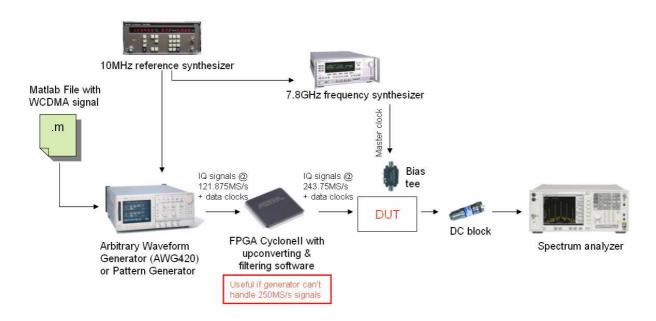

| Figure 5-11 Test setup for the second prototype IC                                                      |       |

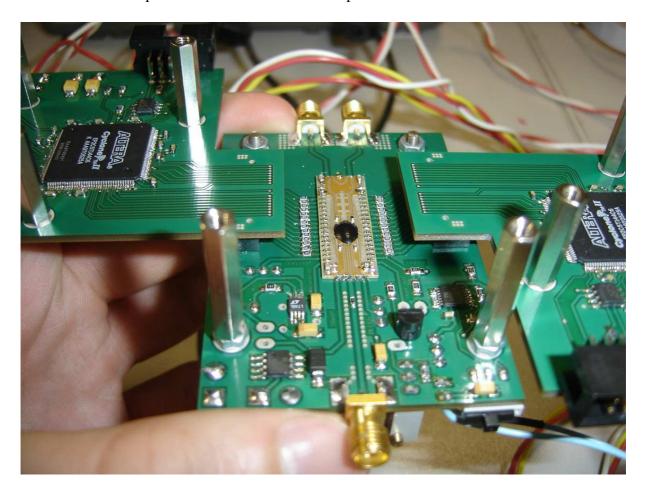

| Figure 5-12 Photography of the chip assembly and test boards                                            |       |

| Figure 5-13 Digital and analog spectrum measurements for a 2.5GHz main clock and a De                   |       |

| input signal                                                                                            | . 107 |

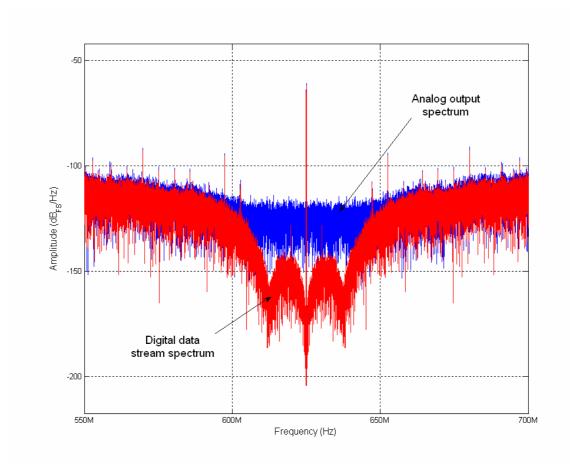

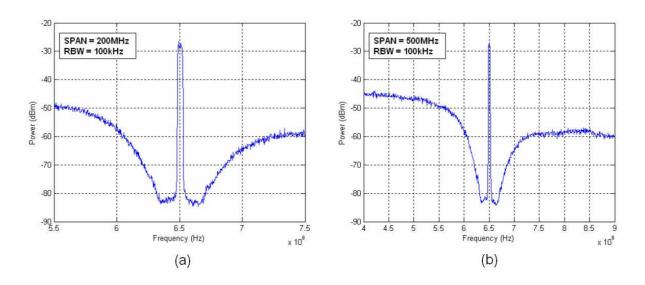

| Figure 5-14 Wideband spectrum of the chip output at 650MHz with a 5MHz input channel                  |       |

|-------------------------------------------------------------------------------------------------------|-------|

| with a span of 200MHz (a) and 500MHz (b). RBW is the resolution bandwidth                             |       |

| Figure 5-15 Wideband spectrum at 1.95GHz. The parameters are the same as Figure 5-14.                 | 110   |

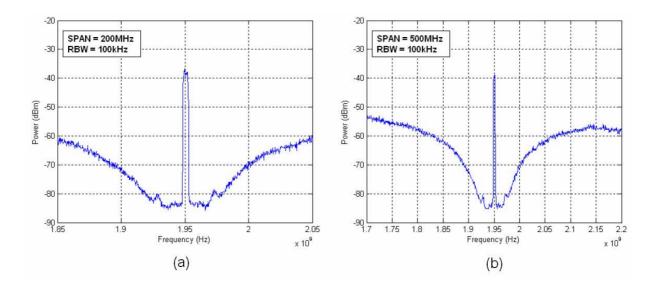

| Figure 5-16 In-band spectrum measurements for a 5MHz WCDMA channel for the                            |       |

| fundamental (a) and the image band (b)                                                                | . 111 |

| Figure 5-17 Output channel power versus the input channel power referred to the quantize              | r     |

| full-scale.                                                                                           | . 111 |

| Figure 5-18 ACPR vs Channel Power for adjacent and alternate channels around fundamental              | ntal  |

| and image bands                                                                                       | . 112 |

| Figure 5-19 650MHz fundamental band : (a) Signal and in-band noise power on 30MHz                     |       |

| related to the input channel power (b) SNDR on 30MHz vs input power                                   | .113  |

| Figure 5-20 1.95GHz image band: (a) Signal and in-band noise power on 30MHz related                   | to    |

| the input channel power (b) SNDR on 30MHz vs input power                                              |       |

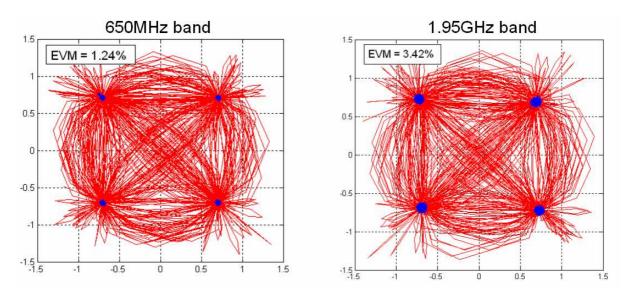

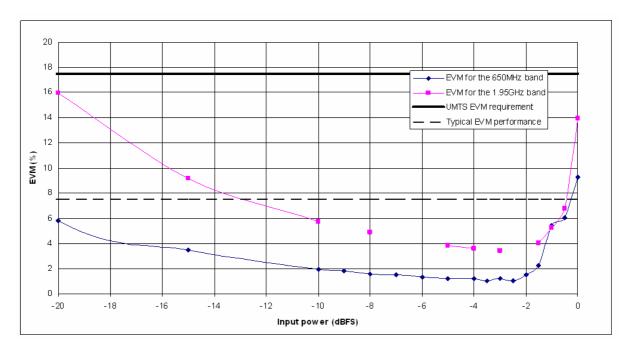

| Figure 5-21 IQ constellations for the fundamental (right) and image band (left). This plot            |       |

| leads to the EVM measurement.                                                                         |       |

| Figure 5-22 EVM versus the input channel power                                                        | 115   |

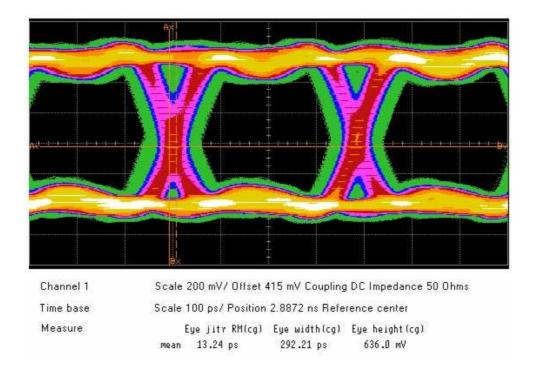

| Figure 5-23 Eye diagram of the 2.6GS/s output                                                         |       |

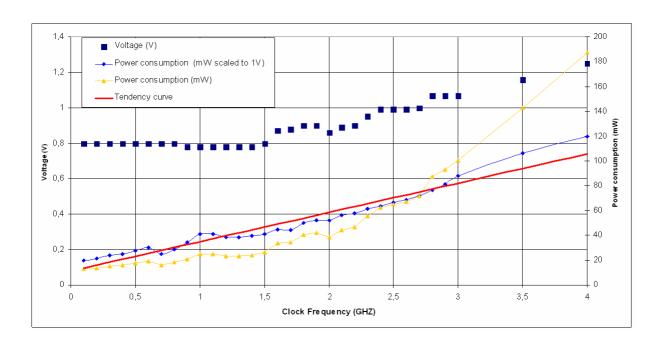

| Figure 5-24 Chip total power consumption as a function of the clock frequency                         |       |

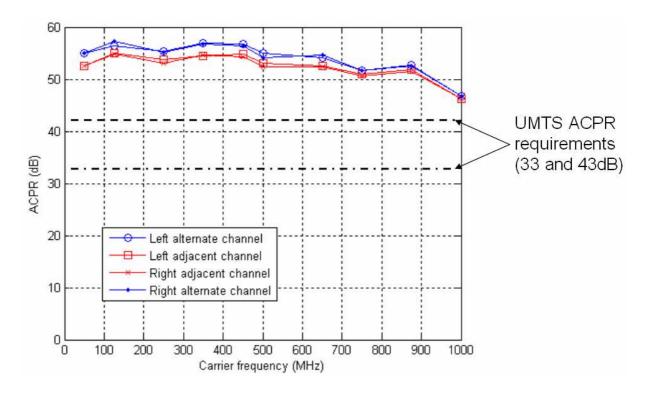

| Figure 5-25 ACPR versus carrier frequencies for fundamental bands                                     |       |

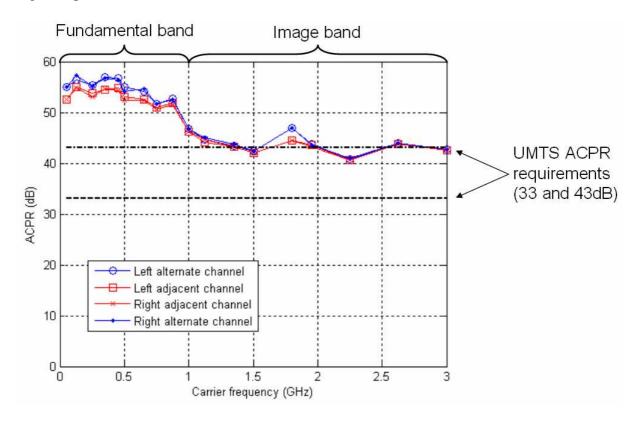

| Figure 5-26 ACPR versus carrier frequencies for fundamental and image bands                           |       |

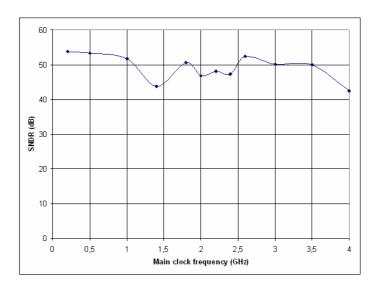

| Figure 5-27 Measured SNDR for different main clock frequencies                                        |       |

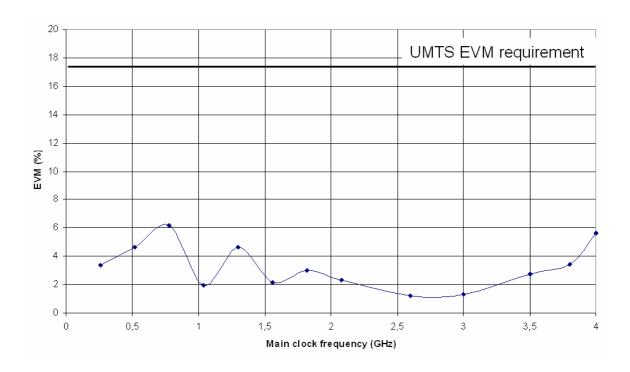

| Figure 5-28 Measured EVM as a function of the main clock frequency                                    |       |

| Figure 5-29 Output channel power versus the main clock frequency                                      |       |

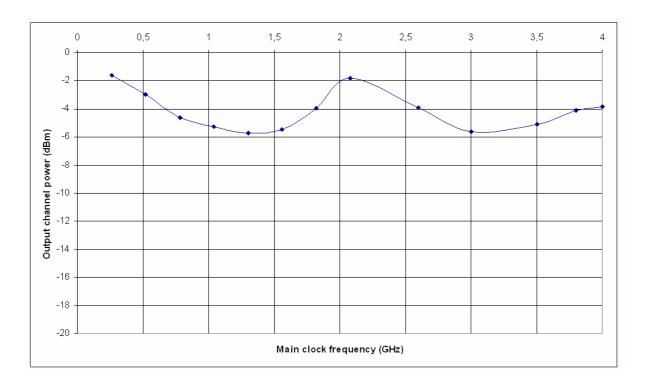

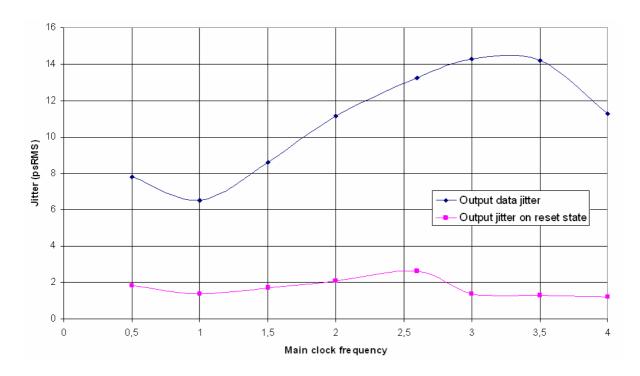

| Figure 5-30 Data and clock jitter versus the main clock frequency                                     |       |

| Figure C - 1 Output spectrum of a digital transmitter implemented with a configurable 5 <sup>th</sup> |       |

| order $\Delta\Sigma$ modulator in (a) UMTS configuration and (b) DCS1800 configuration                | 129   |

# **List of tables**

| Table 1-1 UMTS spectrum emission mask                                                  | 16           |

|----------------------------------------------------------------------------------------|--------------|

| Table 1-2 UMTS ACLR                                                                    | 17           |

| Table 1-3 UMTS spurious emissions table                                                | 18           |

| Table 2-1 Channel center frequencies for UMTS standard                                 | 23           |

| Table 2-2 Offseted channel center frequencies for UMTS standard                        | 25           |

| Table 2-3 RF clock frequency phase noise requirements                                  | 26           |

| Table 2-4 Coefficients for the $3^{rd}$ -order $\Delta\Sigma$ modulator of Figure 2-23 | 42           |

| Table 3-1 Power-of-two coefficients for the $\Delta\Sigma$ modulator                   | 48           |

| Table 3-2 SNDR degradation for Matlab and VHDL simulations                             | 50           |

| Table 3-3 Time and Area requirements for most popular <i>n</i> -bits adders            | 53           |

| Table 3-4 Illustration of Dadda's method                                               | 61           |

| Table 3-5 ACLR comparison for different $\Delta\Sigma$ modulator architecture          | 68           |

| Table 4-1 DLL clocks characteristics for 4GHz clock reference. The load is consti      | tuted by one |

| $\Delta\Sigma$ modulator                                                               | 93           |

| Table 5-1 Summary of measurements with a 2.6GHz clock                                  | 117          |

| Table 5-2 Comparison with similar works                                                | 124          |

#### Introduction

"Welcome to the machine" (Pink Floyd)

In the 2005 edition of the European Solid-State Circuit Conference (ESSCIRC) joint with the European Solid State Device Research Conference (ESSDERC), a rump session entitled "Where will the revolutionary solutions come from: Technology or Design?" has brought together eight international experts in technology/devices and advanced design to argue on the perspectives for future solutions. The final answer was that technology and design together will make barriers fall. As a member of the Integrated Circuits Design Group of the Institut d'Electronique, de Microélectronique et des Nanotechnologies (IEMN), my work is devoted to enhance the design knowledge and to probe further into state-of-the-art advanced design techniques. In this thesis work, I try to conceive, with a given technology, the most powerful and innovative system by bringing design solutions.

The application field of this work is the mobile communications, especially the transmission side. This field offers great challenges, as every new standard comes with more and more restrictive requirements. Moreover, as almost all hardware solutions, power consumption and integration are always crucial factors. From this point of view, each research team tries to tend to the chip that will integrate most functional blocks, consume less and fit with the maximum number of standards. We place ourselves in this context, in which we would like to demonstrate the feasibility and the flexibility of an innovative digital chip with potential industrial applications.

Concretely, this research work introduces an all-digital transmitter architecture able to replace with a marked improvement the front-end circuits in mobile communications terminals. This architecture takes advantage of the oversampled delta-sigma ( $\Delta\Sigma$ ) modulation,

able to quantify a digital word into a 1-bit high-speed stream without losing the information inside excessive quantization noise. The issue is by far the huge computations needed for this operation. Innovative techniques, coming from electronic or other domains, have been developed to overcome the blocking points. Huge efforts have been made to design a full 90nm CMOS chip to demonstrate the proposed concept.

Here is the chapter organization.

The first chapter presents the background of this thesis. It highlights the needs to reach ideal software radio terminals. Then, the evolution of transmitters, from nowadays analog implementations to the digital RF case is detailed, with emphasis on major publications. For the demonstration of this digital RF transmitter prototype, we choose to focus on a particular standard and then to extend to other standards. European UMTS has been first chosen for its hard-to-fulfill requirements and its novelty. Major requirements for this standard are detailed in this section.

Chapter 2 presents the digital transmitter architecture. It explains architectural choices for the system core, including the delta-sigma modulators, the digital RF upconverter and the switching-mode power amplifier. Then, a global transmitter chain is proposed. Finally, a particular implementation of the transmitter chain for UMTS case is detailed for baseband processing, sample rate conversion and delta-sigma modulation blocks.

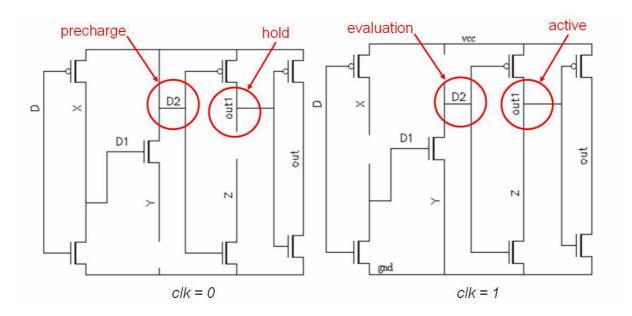

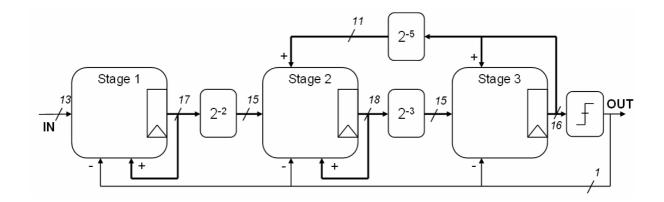

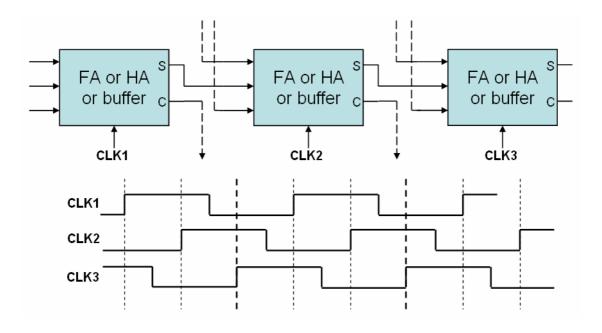

Chapter 3 deals with the  $\Delta\Sigma$  modulator system design. In this chapter, techniques to achieve the computational effort are explained. First, an optimization for digital implementation is given. Then, redundant arithmetic is introduced after having stated the critical path and limitations of 2's complement adder architectures. The  $\Delta\Sigma$  modulators design with this redundant arithmetic is fully covered. Finally, further necessary improvements, called non-exact quantization and output signal precomputation, are detailed.

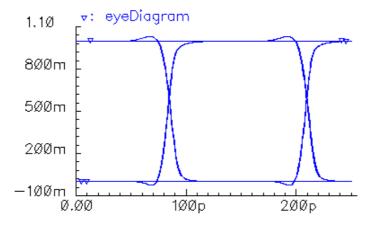

Chapter 4 details the transistor level design of the whole transmitter. The global structure and layout is given in a first section. Then, each circuit block is detailed. The sample rate conversion block description gives an emphasis on the designed high-speed registers.  $\Delta\Sigma$  modulator implementation is handled, focusing on the differential dynamic logic style. The  $\Delta\Sigma$  layout strategy is also explained. Using this dynamic logic style leads to the description of the clock generation and distribution block, implemented by a DLL. Finally, the digital mixer and output stages structures are presented.

Chapter 5 gives an overview of the test setups and measurement results and analyzes the obtained results. Two 90nm CMOS chip have been designed and tested. The first one was

not fully functional but a lot of valuable information could have been gathered. After redesign and fabrication, the second chip was operational and has been thoroughly tested. For each one, test hardware and assembly is described. Then, the measurement results are given, analyzed and compared with other literature results.

Finally, a conclusion will sum up this work with an emphasis on parallel works, reconfigurability perspectives and future directions.

# CHAPTER 1 BACKGROUND

To introduce the background of this thesis work, the concept of software defined radio will be presented. Then, a state-of-the-art in transmitter architecture is established, starting from the analog RF implementation and going to the digital RF implementation. The objective of this work is to demonstrate a digital RF transmitter based on delta-sigma modulation. In order to work with real specifications, UMTS standard has been chosen for demonstration. Requirements for this standard will be stated in order to clarify architecture choices and to evaluate the transmitter performances.

#### 1.1 Software defined radio

### 1.1.1 Universality of RF transmitters

Imagine a mobile phone able to operate all over the world and to travel on most of the wireless networks. This kind of terminal should become a reality with the growth of software-defined radio (SDR). This technology lets us manufacture flexible radios, able to adapt themselves to different standards by simply updating a firmware.

Indeed, an emitter creates electromagnetic waves on an antenna, with specific attributes related to the standard on which it operates. Nowadays, this work is performed by several specialized chips, programmed once and for all to compute signals in the targeted frequency band, according to a defined standard. As a result, those different radio terminals are not compatible and thus limited to their own specificity.

Software defined radio (also called "reconfigurable radio" or "intelligent radio") uses global programmable chips, able to switch from a standard to another by choosing the appropriate software. A SDR mobile phone should then access all networks used in the world.

Utility of SDR handsets becomes more visible as standards proliferate. Those various standards can be divided into several types [1]:

- Second generation digital radio wireless systems (GSM and DCS1800 in Europe, IS-95 in United States),

- Third generation digital radio wireless systems, such as UMTS (Europe),

CDMA2000 (United States) or TD-SCDMA (China),

- Digital cordless systems, such as DECT or PHS,

- Broadband mobile-access systems (Wi-Fi, IEEE802.11, HiperLAN2...),

- Short-range systems, such as Bluetooth.

Moreover, new systems become available, such as 4G, Wimax or IEEE802.20 or even future 60GHz WLAN standards.

Software-defined radio finds its place in future radiocommunications architectures, on the way to universal transmitters.

#### 1.1.2 Ideal software radio

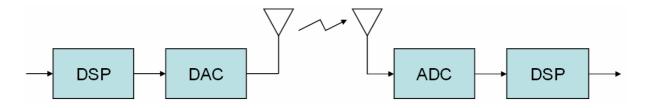

The ultimate architecture for a software defined radio should be a digital multifunction signal processor (DSP), directly connected to an antenna through a digital-to-analog converter (DAC) for emission and an analog-to-digital converter (ADC), followed by a DSP, for reception (Figure 1-1).

Figure 1-1 Ideal software-defined radio transmitter

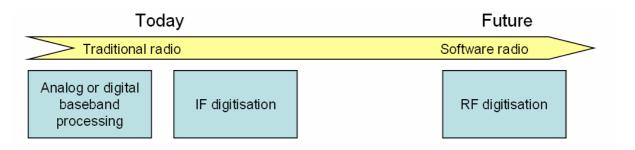

Progressive digitization of the analog blocks tends to bring the converters closer and closer towards the antenna [2, 3], starting from baseband digital processing, through intermediate frequencies (IF) digital processing, to tend toward RF digital processing (Figure 1-2). Nevertheless, relevant technical issues need to be solved in order to deploy software radio solutions. However, emergence of very high-speed digital signal processing makes the concept of SDR becoming a reality [4-6]. From this point of view, this work tries to

demonstrate the feasibility of an all-digital RF transmitter architecture, using digital deltasigma modulation and switching-mode power amplifiers.

Figure 1-2 Toward RF digital processing and software radio

# 1.2 State-of-the-art in transmitter architectures

The state of the art presented in this subpart is a comprehensive, but not exhaustive, picture of digital transmission architectures at the beginning of this work in 2004. It depicts the general trends for implementing transmission architectures. Later work and results from other research teams will be discussed in the conclusion.

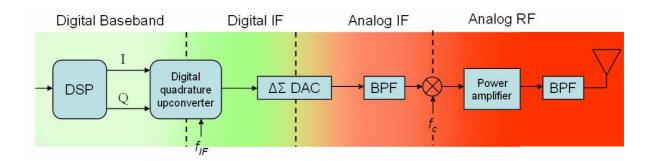

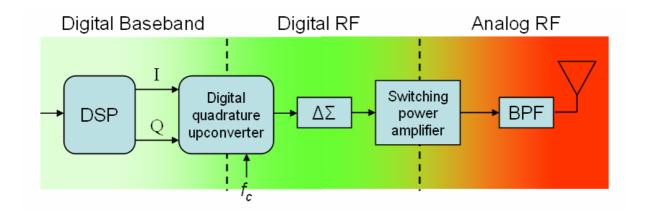

It will be shown that, following the evolution of transmission architectures, the global trend is to digitize the transmission chain. To visualize this trend, a color code has been employed on the different figures. All digital parts appear in green, whereas analog ones are in red. An intensity code is also used to separate baseband blocks (very light color) from RF parts (strong ones). IF processing blocks appear in an intermediate intensity. A cutting edge in RF transceiver architectures for WCDMA has been made in 2001 in [7].

#### 1.2.1 Analog front-end architectures

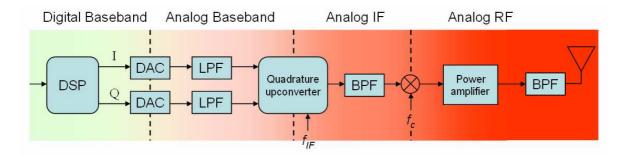

Traditionally, transmitter architectures are almost exclusively analog in all front-end parts. Digital blocks are only found in baseband and digital-to-analog conversion is made with baseband DACs at low sample rates. Then, two implementations exist:

Most of the existing transmitters are based on a two-step up-conversion architecture (Figure 1-3), called heterodyne transmitter. An interesting implementation can be found in

[8]. The signal is first up-converted to an intermediate frequency, filtered, up-converted to the radio frequency, amplified and finally filtered again before emission on the antenna. The filtering at IF or RF cannot be done with active structures, which makes it very difficult to completely integrate transmitters. Furthermore, two different local oscillator signals are needed.

Figure 1-3 Heterodyne transmitter architecture

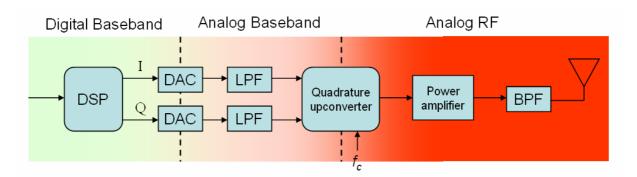

An obvious solution would be to use only a direct up-conversion architecture, where the baseband signal is directly modulated to RF (Figure 1-4). However, the direct conversion or homodyne transmitter suffers from low performances at low output power and from a phenomenon called LO-pulling. The oscillator in the frequency synthesizer operates at the same frequency as the power amplifier in the transmitter. Due to the limited amount of isolation achievable, the transmitted output signal will couple to the oscillator and seriously degrade its performances. Moreover, the quadrature upconverter suffers from a higher IQ mismatch than in heterodyne transmitters, as it is now operating at RF. Examples of homodyne implementations can be found in [9].

Figure 1-4 Homodyne transmitter architecture

### 1.2.2 Digital IF architectures

Figure 1-5 Digital-IF transmitter architecture

An evolution from previous implementations is the Digital-IF architecture, in which the digital signal is converted to analog after IF quadrature upconversion, generally using a  $\Delta\Sigma$  DAC (Figure 1-5). This architecture benefits from better silicon integration, ideal IQ matching and thus a lower error vector magnitude.

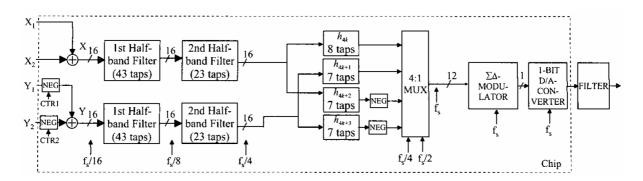

An interesting implementation is presented in [10] and [11], which details a digital quadrature modulator, associated with a 1-bit  $\Delta\Sigma$  modulator and a current-mode DAC to replace analog IF upconversion (Figure 1-6). The 0.13µm CMOS chip can work with a 700MHz clock frequency to address an IF frequency of 175MHz. It consumes 139mW at 1.5V and occupies 5.2mm².

Figure 1-6 Digital quadrature modulator from [10]

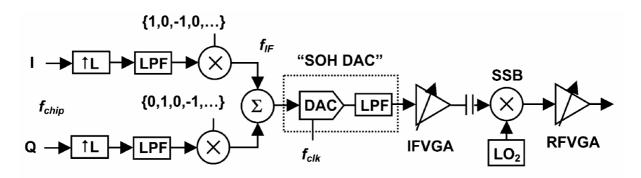

In [12], this kind of architecture is implemented using a second-order-hold DAC in 0.25µm SiGe BiCMOS (Figure 1-7). The multi-bit delta-sigma DAC is working at 250MHz. Analog Variable Gain Amplifier (VGA) and mixer stages are integrated into the chip to deliver an output power of 5dBm, while consuming 180mW at 3V. However, this structure is working with current-mode DACs, which limits, at low voltage, the maximum power that can

be delivered to a load. Such structures are incompatible with more efficient class-S power amplification.

Figure 1-7 Conceptual block diagram of the digital-IF heterodyne transmitter from [12]

## 1.2.3 Digital RF architectures

Figure 1-8 Digital RF transmitter chain

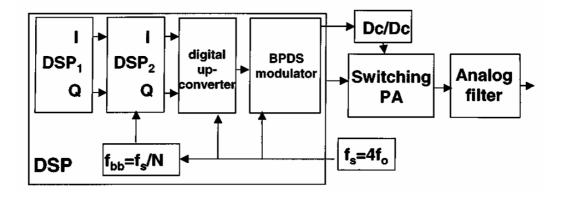

Advances and maturity of deep submicron CMOS technologies enable the DAC to reach higher sample rates. So, the idea of a digital RF implementation is rising [4, 5, 13]. It deletes all analog mixers and replaces them by a direct-digital quadrature upconverter and a switching-mode power amplifier driven by, e.g., a  $\Delta\Sigma$ -modulated high-speed signal (Figure 1-8 and Figure 1-9). An advantage is the high efficiency of the output stages. At the time of this work, no IC implementation of this kind of structures can be reported. However, ideas for such architectures are presented in several publications.

Figure 1-9 DSP-based wireless transmitter architecture from [5]

The fundamental concept is to use bandpass  $\Delta\Sigma$  modulation to produce a high-speed digital signal driving a switching PA:

- [14] demonstrates such a digital transmission chain by experimentally generating the produced bit-stream with a pattern generator and a serializer.

- [6, 15-17] present the concept and show simulation and measurement results for relatively low output frequency, extrapolating simulations to higher output frequencies.

Another method for digitally generating an RF signal is termed "Quadrature Integral Noise Shaping" (INS) and uses PWM coding scheme to generate baseband IQ complex signals. References [18] and [19] detail related architectures.

Moreover, an interesting paper [20] proposes to drive a DCO (Digitally Controlled Oscillator) with a  $\Delta\Sigma$ -modulated signal to generate the phase information and to regulate the power amplifier amplitude to control the amplitude information.

Digital generation of RF signals by  $\Delta\Sigma$  modulation and switched power amplifiers seems to be the most promising implementation in terms of configuration possibility and software radio convergence.

## 1.3 UMTS standard specifications

The Universal Mobile Telecommunications System (UMTS) in Frequency Division Duplex (FDD) mode will be first considered in order to emphasize the concept studied in this work. UMTS is the standard chosen for 3G mobile communications in Europe. Specifications for the UMTS standard are defined by ETSI [21]. These specifications cover all aspects of

transmission and reception for handset terminals. As an introduction to UMTS, only aspects that concern the definition of the global transmitter to be designed are given hereafter. Furthermore, the extension of the highlighted approach to other standards is still under investigation and will be discussed in the conclusion.

#### 1.3.1 Introduction to UMTS

### 1.3.1.1 Protocol layers

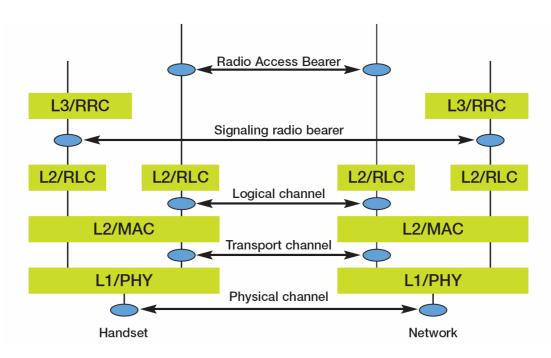

The architecture of the UMTS radio interface is structured into layers, in which protocols are based on the first three layers of the Open Systems Interconnection (OSI) reference model [22], as illustrated in Figure 1-10:

- The first layer is the physical one, devoted to transmit and receive data over the channel.

- The second layer is the medium access control (MAC), which is able to control the data sent and received and to retransmit error packets. This layer provides data and information to the physical layer.

- The third layer is the radio resource control (RRC). It controls and maps the connections.

Figure 1-10 Radio interface protocol structure [22]

In the following sections, only transmitter physical layer, starting from the baseband signals provided by the MAC layer will be considered.

### 1.3.1.2 Access mode and frequency allocation

The frequency sharing technique adopted for UMTS is the Code Division Multiple Access (CDMA): data from different users coexist within the same channel and spread spectrum modulation is used to attribute a specific code to each user. Two methods allow spreading signals: the Frequency Hopping (FH-SS) technique and the Direct-Sequence one (DS-SS) [23]. Since only the DS-SS technique is adopted in UMTS, it is shortly detailed hereafter. Direct-Sequence spread spectrum consists in multiplying the signals symbols by a specific pseudo-random binary sequence. CDMA systems using direct sequence spreading are called DS-CDMA. For UMTS, information is spread over about 5MHz, hence it is called WCDMA (W is for Wideband). Two duplex modes exist in UMTS, Frequency Division Duplex (FDD) and Time Division Duplex (TDD).

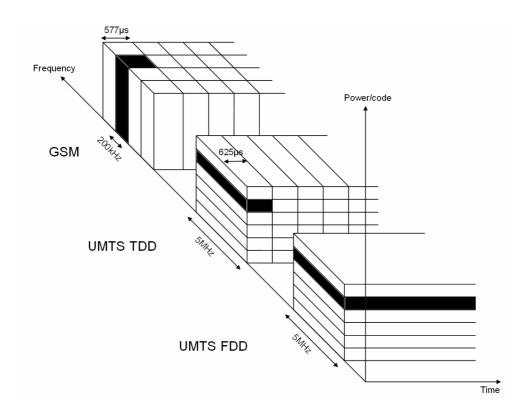

Figure 1-11 gives a comparison between spectrum access techniques used in GSM and UMTS. For GSM, the whole frequency band is split into 200kHz wide channels multiplexed in time between emission and reception. For UMTS in TDD mode, information is spread over 5MHz channels and separated per code. The transmitter and the receiver are working in half-duplex. Time slots are alternatively allocated for emission and reception. FDD mode also uses CDMA but the transceiver is working in full-duplex. The reception band is placed away from the emission band (not shown in the figure). The two front-end architectures operate at the same time, using a duplexer.

Figure 1-11 Examples of access modes for GSM, UMTS TDD and FDD

The study is focused on FDD mode in which uplink and downlink are separated in two frequency bands, instead of separated time slots. UMTS FDD operates on two 60MHz bands, separated by 190MHz. The uplink uses 1920-1980MHz band while the downlink band is located between 2110 and 2170MHz. Our interest only goes to the uplink path, from the user terminal to the base station.

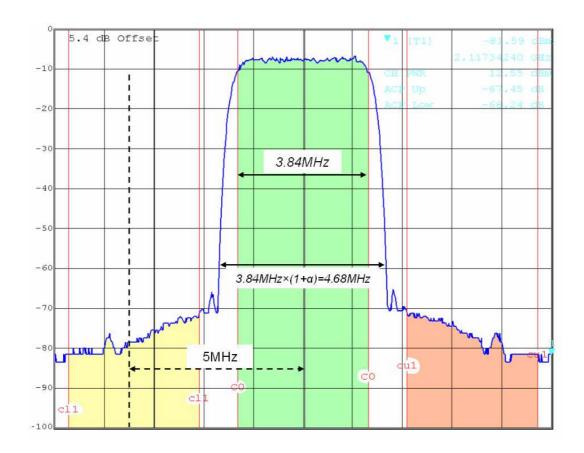

Inside the 1920-1980MHz band, twelve 5MHz wide channels exist. Chip rate is 3.84Mc/s (Mega chips/second), but data rate is tied to the spreading factor. Channels are larger than the relative chip rate due to the roll-off factor (generally stated  $\alpha$ ) of the Root-Raised Cosine (RRC) filter used. In UMTS, the roll-off factor is equal to 0.22, thus the channel bandwidth is equal to chip rate× $(1+\alpha)=4.68$ MHz. A channel is shown on Figure 1-12, illustrating the effect of the root-raised cosine filter. The modulation used by UMTS is the Quaternary Phase Shift Keying (QPSK).

Figure 1-12 Example of a RRC-shaped UMTS channel

### 1.3.2 UMTS specifications for transmitters

Specifications on spectrum emissions are given at the antenna connector. It will be considered that the antenna connector is loaded by a nominal single ended  $50~\Omega$  impedance. These specifications lead to a spectrum emission mask and out-of-band spurious emissions constraints as explained in the following sections.

### 1.3.2.1 Spectrum emission mask

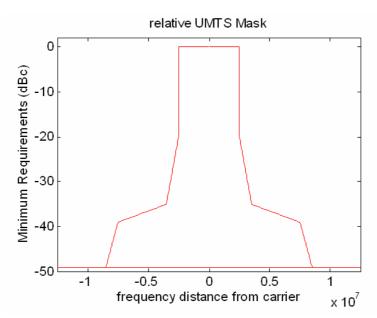

The spectrum emission mask applies to frequencies, which are between 2.5 MHz and 12.5 MHz away from the User Equipment (UE) centre carrier frequency (related to the chosen channel). The out-of-channel emission is specified relative to the RRC filtered mean power of the UE carrier. Table 1-1 shows requirements for UMTS spectrum emission mask and Figure 1-13 translates the requirements on a graph.

|                                         | Minimum requirement (Note 2)                           |                      | Measurement |

|-----------------------------------------|--------------------------------------------------------|----------------------|-------------|

| Δf in MHz (Note 1)                      | Relative requirement                                   | Absolute requirement | bandwidth   |

| $2.5 \le \Delta f \le 3.5 \text{ MHz}$  | $-35 - 15 \left(\frac{\Delta f}{MHz} - 2.5\right) dBc$ | -71,1 dBm            | 30 kHz      |

| $3.5 \le \Delta f \le 7.5 \text{ MHz}$  | $-35 - 1 \left(\frac{\Delta f}{MHz} - 3.5\right) dBc$  |                      |             |

| $7.5 \le \Delta f \le 8.5 \text{ MHz}$  | $-39-10\left(\frac{\Delta f}{MHz}-7.5\right)dBc$       | -55,8 dBm            | 1 MHz       |

| $8.5 \le \Delta f \le 12.5 \text{ MHz}$ | -49 dBc                                                |                      |             |

Note 1:  $\Delta f$  is the separation between the carrier frequency and the center of the measurement bandwidth.

Note 2: The minimum requirement is calculated from the relative requirement or the absolute requirement, whichever is the higher power.

Table 1-1 UMTS spectrum emission mask

Figure 1-13 UMTS spectrum emission mask (related to a 1MHz measurement bandwidth)

### 1.3.2.2 Adjacent Channel Leakage Power Ratio

Another parameter is defined to obtain the desired spectrum requirement. Adjacent Channel Leakage power Ratio (ACLR) is the ratio of the RRC filtered mean power centered on the assigned channel frequency to the RRC filtered mean power centered on an adjacent channel frequency. If the channel power is greater than -50dBm then the ACLR specifications in Table 1-2 should be met.

| Adjacent channel frequency relative to assigned channel frequency | ACLR Limit |

|-------------------------------------------------------------------|------------|

| + 5 MHz or – 5 MHz                                                | 33 dB      |

| + 10 MHz or – 10 MHz                                              | 43 dB      |

**Table 1-2 UMTS ACLR**

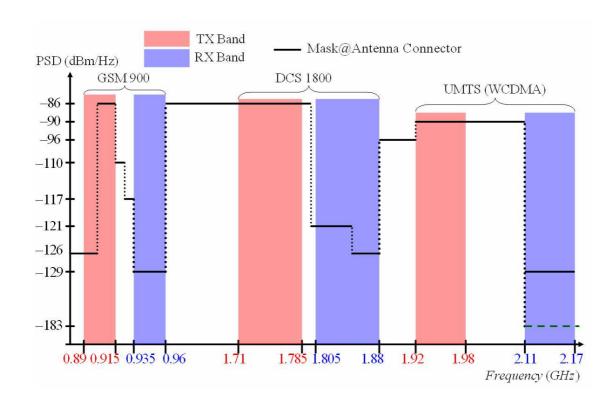

### 1.3.2.3 Spurious emissions

In addition to in-band requirements, UEs are not authorized to spread power everywhere. Some frequency bands, used in other standards, are sensitive to perturbations. To overcome this, maximum spurious emission levels are defined in determined frequency bands. Out-of-band requirements are plotted on Figure 1-14 between 900MHz and 2.2GHz. This plot corresponds to normalized power emission in dBm/Hz over standards frequency bands, as defined by the ETSI (Table 1-3). On this qualitative plot, proportionality is not respected. However, this plot is relevant for visual understanding.

Receive band specifications (RX bands) are the hardest ones to meet. For the GSM900 band, a maximum of -129dBm/Hz is required. For the DCS1800, -126dBm/Hz is the limit of spurious emission. The RX band of UMTS is placed 190MHz higher than transmit band (TX band). The maximum allowed level is -129dBm/Hz at the antenna. However, an UMTS terminal is working in full duplex using a duplexer. That means the UE is transmitting and receiving data at the same time. That's the reason why the RX band requirement must be lowered down to -183dBm/Hz. UMTS RX and DCS1800 RX specifications are the most demanding ones, as they are very close to the UMTS transmit band (TX band).

Figure 1-14 UMTS spurious requirements

| Frequency | Band (MHz) | Measurement Bandwidth | Requirement (dBm) |

|-----------|------------|-----------------------|-------------------|

| 0,009     | - 0,15     | 1 kHz                 |                   |

| 0,15      | - 30       | 10 kHz                | -36               |

| 30        | - 860      | 100 kHz               |                   |

| 860       | - 895      | 3.84 MHz              | -60               |

| 895       | - 921      | 100 kHz               | -36               |

| 921       | - 925      | 100 kHz               | -60               |

| 925       | - 935      | 3.84MHz               | -60               |

| 935       | - 960      | 100 kHz               | -79               |

| 960       | - 1000     | 100 kHz               | -36               |

| 1000      | - 1805     | 1 MHz                 | -30               |

| 1805      | - 1844,9   | 100 kHz               | -71               |

| 1844,9    | - 1880     | 3.84 MHz              | -60               |

| 1880      | - 1884,5   | 1 MHz                 | -30               |

| 1884,5    | - 1919,6   | 300 kHz               | -41               |

| 1919,6    | - 2110     | 1 MHz                 | -30               |

| 2110      | - 2170     | 3.84 MHz              | -60               |

| 2170      | - 2620     | 1 MHz                 | -30               |

| 2620      | - 2690     | 3.84 MHz              | -60               |

| 2690      | - 12750    | 1 MHz                 | -30               |

Table 1-3 UMTS spurious emissions table

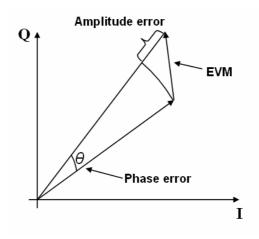

### 1.3.2.4 Error Vector Magnitude

Finally, UMTS norm defines quality criterions. A useful one is the Error Vector Magnitude (EVM) measurement. It is an evaluation of the difference between a reference data signal and the measured data signal. EVM is defined as the square root of the ratio between

the error vector mean power and the reference signal mean power, expressed in percentage. Figure 1-15 explains on an IQ diagram the phase and amplitude errors associated with the EVM definition. In normal conditions and for an output power greater than -20dBm, EVM must be lower than 17.5%. However, typical performance of mobile transmitters is an EVM of about 7%.

Figure 1-15 Amplitude and phase errors defining EVM

### 1.4 Conclusion

The work presented in this thesis is devoted to software radio, trying to approach as much as possible an ideal implementation. In a first study, the European standard for 3G communications (UMTS) is chosen for its hard-to-fulfill requirements. Main UMTS specifications, directly related to our work, have been detailed.

Nowadays, transmitters in mobile handsets are mainly analog. The trend to digitize all processing blocks brings us to find new ways of implementing transmission chains. An architecture based on digital RF  $\Delta\Sigma$  modulators, digital quadrature upconverters and switching-mode power amplifiers has been determined as a good candidate to enable digital radio and will be discussed in more detail in the next chapter.

# CHAPTER 2 DIGITAL TRANSMITTER ARCHITECTURE

The digital RF transmitter architecture, as presented in paragraph 1.2.3, can be implemented, at system level, in several different ways. In the first section of this chapter, two possible system architectures are presented and the choices made in this work justified. The more detailed structure of all sub-blocks in the selected system architecture is presented in the subsequent sections.

### 2.1 Global transmitter architecture

## 2.1.1 Transmitter architecture and frequency planning

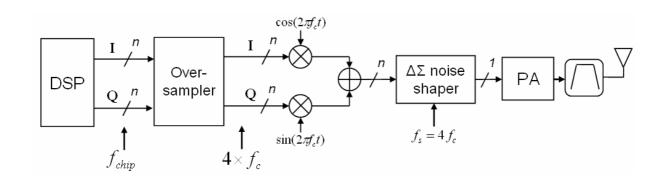

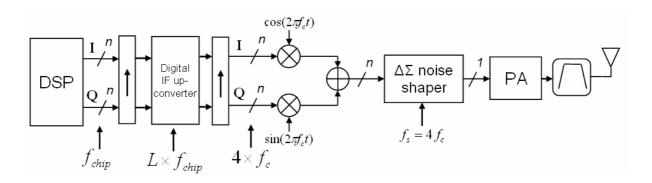

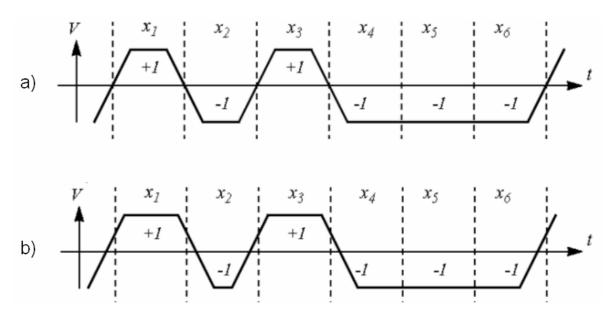

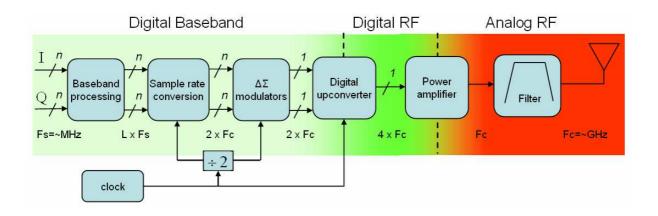

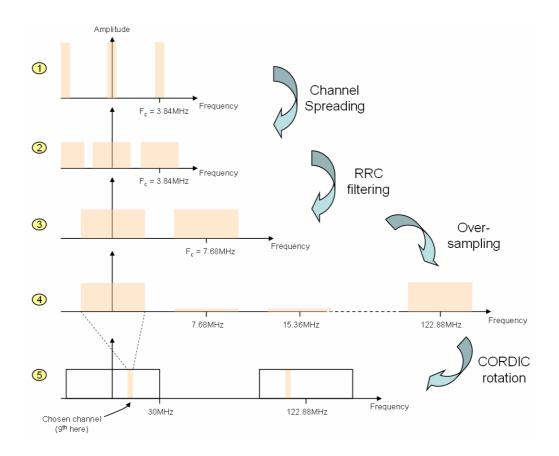

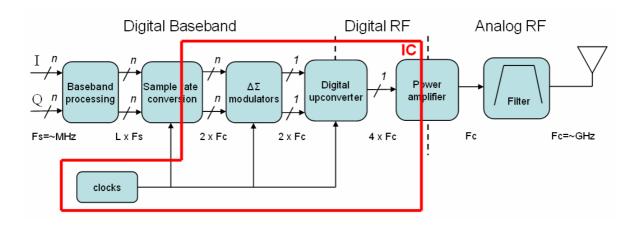

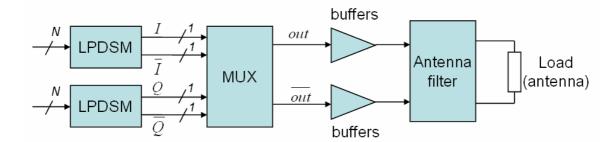

Figure 2-1 Digital transmitter architecture.  $f_{\it chip}$  is the chip rate,  $f_{\it c}$  the carrier frequency and  $f_{\it s}$  the sampling frequency.

The global function of the digital transmitter is to convert a multi-bit digital I/Q baseband signal at baseband sampling rate (chip rate) into a digital 1-bit RF signal at a very

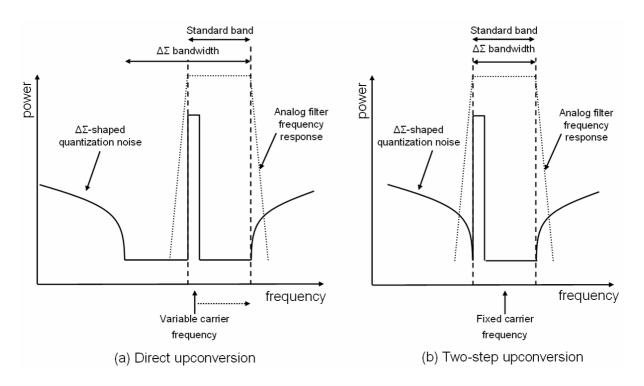

high sampling rate that can be fed to a switching power amplifier. The underlying fundamental principles are oversampling and noise-shaping. Delta-sigma modulators are used to shape the noise in an appropriate way to move it out of the targeted transmit band. The global architecture is presented on Figure 2-1. An analog filter is then necessary at the output of the digital transmitter to remove the high out-of-band quantization noise. If a fixed frequency analog filter is used, the modulator must provide low quantization noise over the full transmit band of the targeted standard for all carrier frequencies. In a simple direct-conversion architecture, the sampling frequency would be proportional to the carrier frequency. The worst-case situations are then the channels situated at the edges of the transmit band (Figure 2-2a). In fact, for a low quantization noise for all possible channels inside the standard band, the  $\Delta\Sigma$  modulator bandwidth must be twice the width of the transmit band, thus increasing the noise shaper requirements.

Figure 2-2 Modulator output spectrum for channels at the lowest band edge for (a) direct conversion and (b) two-step conversion

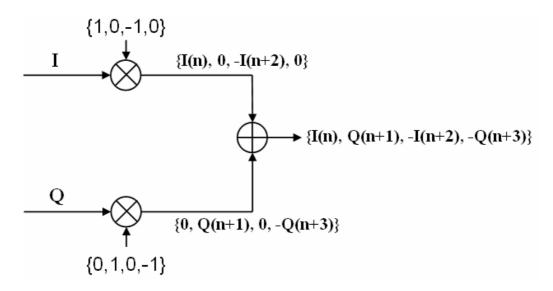

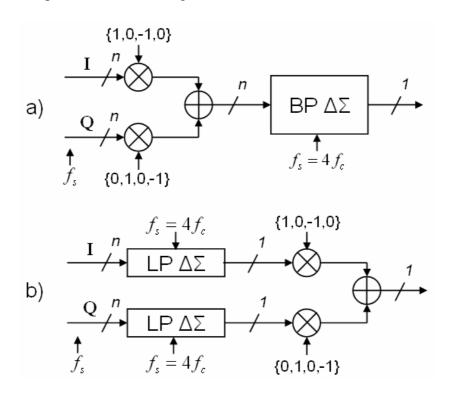

To relax the requirements on the noise shaper, a two-step upconversion architecture has been chosen (Figure 2-3). The RF sampling frequency is fixed, and the center of the noise-shaper bandwidth is placed on the center of the standard transmit band, independently of the actual channel used for the transmit path (Figure 2-2b). In the first step the complex base-band signal is moderately oversampled and then placed on the appropriate channel by a

digital multiplier. For UMTS, the corresponding 12 channel center frequencies are stated in Table 2-1 and are given by:

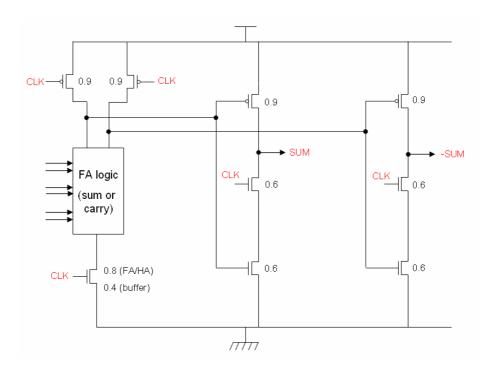

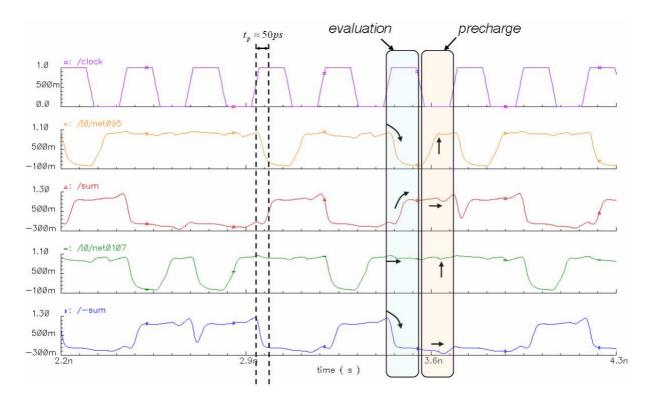

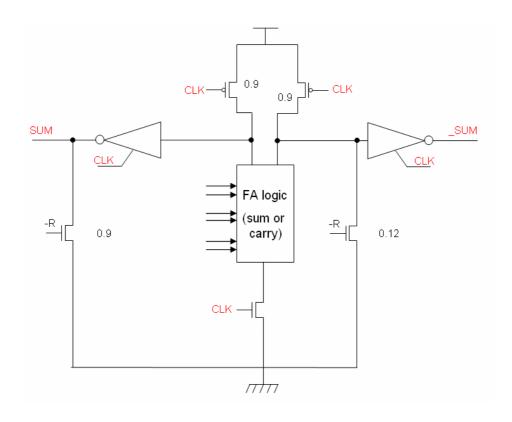

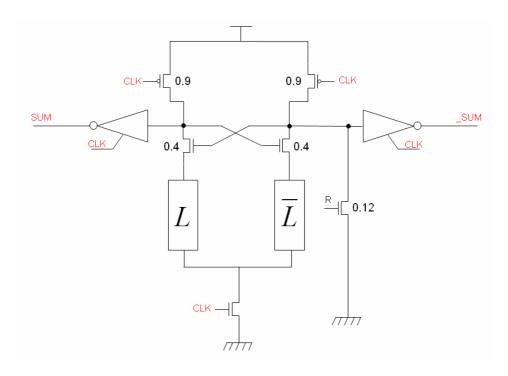

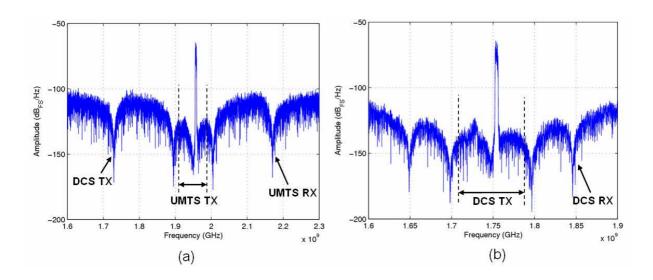

$$F_{channel} = \pm (2.5MHz + k \times 5MHz), k = 0,1,2,3,4,5$$