## Modeling flexible Networks On-Chip

L. Pieralisi

### ▶ To cite this version:

L. Pieralisi. Modeling flexible Networks On-Chip. Micro and nanotechnologies/Microelectronics. Institut National Polytechnique de Grenoble - INPG, 2006. English. NNT: . tel-00164027

### HAL Id: tel-00164027 https://theses.hal.science/tel-00164027

Submitted on 19 Jul 2007

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

N° attribué par la bibliothèque

### **THESE**

pour obtenir le grade de

#### DOCTEUR DE l'INPG

### Spécialité : « Micro et nano électronique »

préparée au laboratoire TIMA dans le cadre de l'Ecole Doctorale « E.E.A.T.S. »

présentée et soutenue publiquement

$\operatorname{par}$

Lorenzo Pieralisi

le 07/07/2006

### Titre :

Modélisation de réseau de communication flexible pour les systèmes monopuce

Directeur de thèse : Ahmed Amine JERRAYA

#### JURY

| M. Frédéric Pétrot     | , Président          |

|------------------------|----------------------|

| M. Amara Amara         | , Rapporteur         |

| M. Alain Greiner       | , Rapporteur         |

| M. Ahmed Amine Jerraya | , Directeur de thèse |

| M. Marcello Coppola    | , Co-encadrant       |

| M. Eric Flamand        | , Examinateur        |

# Résumé

Les systèmes monopuce deviennent de plus en plus complexes, intégrant composants à la fois logiciels et matériels dans le but de procurer une capacité de calcul croissante aux applications embarquées. L'interconnexion des composants devient un élément crucial de la conception ; il fournit aux concepteurs des fonctionalités avancées telles qu'opérations atomiques, transactions parallèles et primitives de communication permettant des systèmes sécurisés.

Le concept de réseau sur puce s'impose comme élément de communication pour les architectures d'interconnexion des systèmes de la prochaine génération. Le rôle des réseaux sur puce consiste à remplacer les bus partagés dont la mise à l'échelle comporte de sérieux problèmes de conception et représente un goulot d'étranglement pour le système global.

La modélisation d'un réseau sur puce est une tâche extrêmement complexe; ces modèles doivent être à la fois rapides en terme d'exécution, précis et ils doivent exporter des interfaces standard afin d'en améliorer la réutilisation. Les principales contributions de cet ouvrage sont représentées par : (1) le développement d'un simulateur de réseaux sur puce complet, précis au cycle près, basé sur OCCN, un logiciel de simulation libre disponible sur « sourceforge » à l'adresse http://occn.sourceforge.net , (2) l'intégration de plusieurs environnements de simulation hétérogènes en plate-formes très complexes utilisées pour étudier des systèmes monopuce réels produits par STMicroelectronics et (3) une connaissance complète des concepts sous-jacents aux réseaux sur puce qui a apporté une contribution importante au développement de STNoC<sup>™</sup>, la nouvelle technologie d'interconnexion de STMicroelectronics développée au sein du laboratoire Advanced System Technology (AST) de Grenoble. L'environnement de modélisation réalisé a été utilisé pour l'étude de deux systèmes monopuce réels développés par STMicroelectronics orientés vers la télévision numérique à très haute définition (HDTV).

**Mots-clés** : systèmes monopuce, qualité de service, modélisation au niveau transactionnel, co-simulation, SystemC, plate-forme, interface, POSIX, réseaux sur puce, couches réseaux, commutation par paquet.

# Abstract

The Multi-Processors Systems on a chip (MPSoC) era is bringing about many new challenges for systems design in terms of computation and communication subsystems complexity. Interconnection systems became a pivotal component of the overall design, providing designers with advanced communication features such a split transactions, atomic operations and security adds-on. Momentum is building behind Networks on-chip (NoC) as future on-chip interconnection technology. Networks on-chip role is about to take over shared busses whose scalability properties are already a major bottleneck for system design.

Modeling of on-chip network is an exacting work; networks models must be fast, accurate and they have to sport standard interfaces. The main contributions of this work to networks on-chip design and implementation are: (1) the development of a brand new, full-fledged network on-chip simulator based on OCCN, an open-source framework for NoC modeling developed within sourceforge available at http://occn.sourceforge.net, (2) the successfull integration of heterogeneous simulation environments in extremely complex platforms used to benchmark real STMicroelectronics SoC and (3) a thorough understanding and contribution to the design of STNoC<sup>TM</sup>, the new interconnection technology developed within AST Grenoble lab of STMicroelectronics for future generation systems. The modeling environment has been used to benchmark two STMicroelectronics systems on-chip for High Definition digital Television (HDTV).

**Keywords:** system on-chip, quality of service, transaction level modeling, co-simulation, SystemC, platform, interfaces, POSIX, networks on-chip, packet switching, layers. "Don't be afraid to attempt the impossible. Simply knowing what is impossible is useful knowledge – and you may well find, in the wake of some unexpected success, that not half of the things we call impossible have any right at all to wear the label." – Michael Abrash

To mum and dad, with love

# Acknowledgements

This is the part of my thesis I was raring to write, in order to thank all of the people involved directly and indirectly on its development. First and foremost, I want to thank Marcello and Master Jerraya for the simple reason that, without their immense help, I would not have achieved any of this, which actually means a lot to me. I have come a long way and I learned a lot from you. Believe me, it was such a pleasure, and the forthcoming years will prove what I am talking about. Frankly, thank you very much. A fond wink to the STNoC<sup>™</sup> cabal (alphabetical order), Ennio (STNoC<sup>™</sup> guestlist), Giuseppe, Marcela, Marcello, Michael, Miltos, Nicola, Payal, Philippe, Riccardo, Saurin, Valerio and all the guys who contributed to its development, including ST Tunis and ST Catania OCCS mates. Benchmarking made us toil, working together made us friends, and you know, at the end of the day, the acquired knowledge will make us win.

Great many thanks to Thesis committee in alphabetical order, Professor Amara AMARA, Engineer Eric FLAMAND, Professor Alain GREINER and Professor Frédéric PÉTROT, for accepting to review my PhD thesis and their willingness to attend its defence. A sad farewell from TIMA/SLS guys; working with you was a privilege and your kindness, liveliness and sympathy made my life ways better. I want to thank the Linux community for developing a top-notch operating system and for distributing it as open source. It is a monument of knowledge that must not be taken for granted. Let me thank Marcello, Stéphane and Gianluca for giving me the possibility to help them develop open-source software (OCCN). When you contribute to open source software your work is of small but immediate benefit to other people, which, after all, is the most enjoyable pleasure. Always remember, freedom does matter.

Last but not least, I want to dedicate this work to my beloved parents Bruno and Giancarla, and Ramona chérie, without whose help and love none of this would have been possible. I love you.

Lorenzo

# Table des matières

| 1        | Pré | sentation de la thèse                                                 | <b>2</b> |

|----------|-----|-----------------------------------------------------------------------|----------|

|          | 1.1 | Problématique                                                         | 2        |

|          | 1.2 | Contribution                                                          | 3        |

|          | 1.3 | Présentation de la structure de la thèse                              | 3        |

| <b>2</b> | Mo  | délisation de réseau flexible pour les systèmes monopuce              | <b>5</b> |

|          | 2.1 | Introduction                                                          | 5        |

|          | 2.2 | État de l'art                                                         | 5        |

|          | 2.3 | Méthodologie de modélisation de réseaux sur puce                      | 15       |

|          |     | 2.3.1 Simulations distribuées pour les systèmes monopuce              | 19       |

|          | 2.4 | Exploration d'architecture du réseau STNoC <sup><math>TM</math></sup> | 20       |

|          | 2.5 | Conclusion                                                            | 27       |

| 3        | SoC | Cs interconnections                                                   | 28       |

|          | 3.1 | Introduction                                                          | 28       |

|          | 3.2 | Networks on-chip motivations                                          | 28       |

|          | 3.3 | State of the art                                                      | 32       |

|          |     | 3.3.1 Shared multi-layer buses and crossbars                          | 32       |

|          |     | 3.3.1.1 AMBA Bus                                                      | 32       |

|          |     | 3.3.1.2 $\operatorname{IBM}^{\mathbb{T}}$ Core Connect                | 34       |

|   |     |       | 3.3.1.3    | STMicroelectronics STBus                          | 37 |

|---|-----|-------|------------|---------------------------------------------------|----|

|   |     |       | 3.3.1.4    | AMBA AXI                                          | 38 |

|   |     |       | 3.3.1.5    | $\mathbf{SONICS}^{\mathbb{T}M}$ Silicon backplane | 40 |

|   |     | 3.3.2 | On-chip    | switching networks                                | 42 |

|   |     |       | 3.3.2.1    | LIP6 SPIN                                         | 42 |

|   |     |       | 3.3.2.2    | Philips' Æthereal Network on-chip                 | 44 |

|   |     |       | 3.3.2.3    | MIT Raw                                           | 45 |

|   |     |       | 3.3.2.4    | Arteris NoC                                       | 48 |

|   | 3.4 | Summ  | ary of exi | isting interconnections                           | 49 |

|   | 3.5 | Concl | usion      |                                                   | 51 |

| 4 |     |       | On-chip    | : A layered approach for On-chip commu-           |    |

|   |     | ation |            |                                                   | 52 |

|   | 4.1 |       |            |                                                   | 52 |

|   | 4.2 |       |            | ip: a micronetwork of components                  | 53 |

|   | 4.3 |       | Ť          | •••••                                             | 56 |

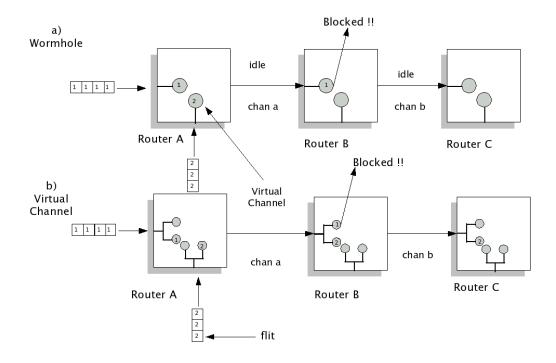

|   |     | 4.3.1 |            | l flow control                                    | 56 |

|   |     |       | 4.3.1.1    | Wormhole flow control                             | 57 |

|   |     |       | 4.3.1.2    | Virtual channel flow control                      | 57 |

|   | 4.4 | Netwo | ork Layer  |                                                   | 59 |

|   |     | 4.4.1 | Network    | topologies                                        | 59 |

|   |     | 4.4.2 | Routing    | algorithms                                        | 61 |

|   |     |       | 4.4.2.1    | Deterministic routing                             | 61 |

|   |     |       | 4.4.2.2    | Adaptive routing                                  | 62 |

|   |     | 4.4.3 | Guarant    | eed services                                      | 63 |

|   |     |       | 4.4.3.1    | Traffic shaping                                   | 64 |

|   |     |       | 4.4.3.2    | Resource reservation                              | 64 |

|   |     | 4.4.4 | Best effe  | ort services                                      | 67 |

|   |     | 4.4.5 | Arbitrat   | ion policy and algorithms                         | 68 |

|   | 4.5 | Trans | port Laye  | r                                                 | 69 |

|   |     |        |                                                                                    | ~~       |

|---|-----|--------|------------------------------------------------------------------------------------|----------|

|   |     | 4.5.1  | 0 0                                                                                | <u> </u> |

|   |     | 4.5.2  | 1                                                                                  | 73       |

|   |     |        | 4.5.2.1 Atomic transactions and compound operations                                | 75       |

|   | 4.6 | STNo   | $\mathbb{C}^{\mathbb{T}^{M}}$ network on-chip                                      | 77       |

|   |     | 4.6.1  | $STNoC^{TM}$ router                                                                | 79       |

|   |     | 4.6.2  | $STNoC^{TM}$ network interface                                                     | 82       |

|   | 4.7 | Conclu | 1sion                                                                              | 84       |

| 5 | Net | works  | <b>On-Chip Modeling: Application to <math>STNoC^{TM}</math></b>                    | 35       |

|   | 5.1 | Introd | uction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$              | 85       |

|   | 5.2 | System | n level design                                                                     | 86       |

|   | 5.3 | System | ${ m nC} \ { m environment} \ \ \ldots \ \ \ldots \ \ \ldots \ \ \ \ \ \ \ \ \ \ $ | 87       |

|   |     | 5.3.1  | SystemC Kernel                                                                     | 90       |

|   |     | 5.3.2  | SystemC groundwork for transaction-level modeling 9                                | 92       |

|   | 5.4 | Transa | action Level Modeling (TLM)                                                        | 93       |

|   |     | 5.4.1  | TLM State of the art                                                               | 95       |

|   |     | 5.4.2  | TLM OSCI standard                                                                  | 97       |

|   | 5.5 | OCCN   | I: On-Chip Communication Network                                                   | 99       |

|   |     | 5.5.1  | OCCN methodology overview                                                          | 00       |

|   |     | 5.5.2  | OCCN API and library components                                                    | )1       |

|   |     |        | 5.5.2.1 PDU                                                                        | )2       |

|   |     |        | 5.5.2.2 MasterPort/SlavePort                                                       | )6       |

|   |     |        | 5.5.2.3 Master/Slave Interfaces                                                    | )8       |

|   | 5.6 | Netwo  | rks on-chip modeling methodology                                                   | 13       |

|   |     | 5.6.1  | Routers modeling principles                                                        | 16       |

|   |     | 5.6.2  | Pipeline modeling and scheduling                                                   | 19       |

|   |     | 5.6.3  | Models profiling and simulation speed                                              | 25       |

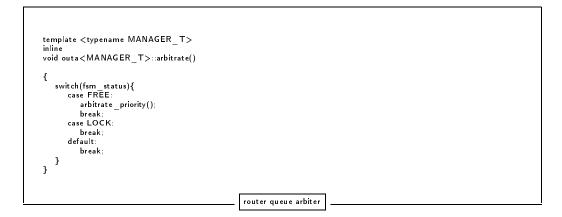

|   |     | 5.6.4  | Modularized arbitration                                                            | 30       |

|   |     | 5.6.5  | Network Interface models structure and hierarchy 13                                | 31       |

|   |     | 5.6.6  | Network interface size and frequency conversion 13                                 | 34       |

|   |     |        |                                                                                    |          |

### TABLE DES MATIÈRES

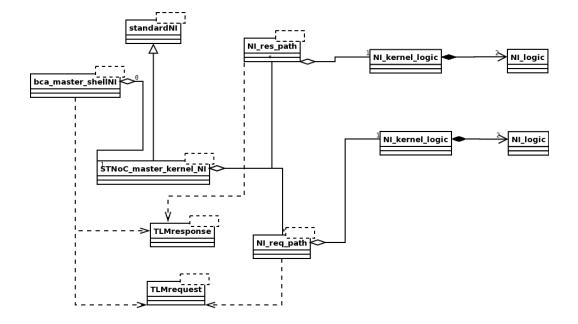

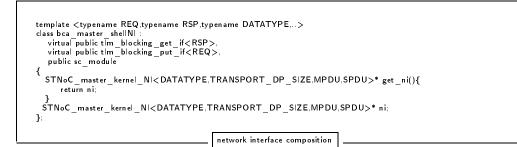

|   |     | 5.6.7   | Network interface C++ objects inheritance and com-<br>position patterns                                | . 134 |

|---|-----|---------|--------------------------------------------------------------------------------------------------------|-------|

|   | 5.7 | Co-sir  | nulation wrappers                                                                                      | . 135 |

|   |     | 5.7.1   | SystemC/Verilog wrappers                                                                               | . 137 |

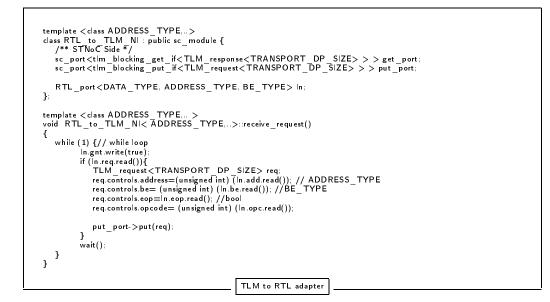

|   |     | 5.7.2   | TLM to signals wrappers                                                                                | . 138 |

|   | 5.8 | Distri  | buted simulations for Networks On-chip                                                                 | . 140 |

|   |     | 5.8.1   | POSIX primitives for concurrent simulations                                                            | . 141 |

|   |     | 5.8.2   | Delta cycle parallelism through kernel helper threads                                                  | . 142 |

|   |     | 5.8.3   | SystemC Kernel critical regions                                                                        | . 147 |

|   |     | 5.8.4   | Wrap-up and on-going work                                                                              | . 148 |

|   | 5.9 | Concl   | usion                                                                                                  | . 149 |

| 6 | STI | NoC     | benchmarking                                                                                           | 150   |

|   | 6.1 | Introd  | luction                                                                                                | . 150 |

|   | 6.2 | STMi    | croelectronics STBus based SoC                                                                         | . 150 |

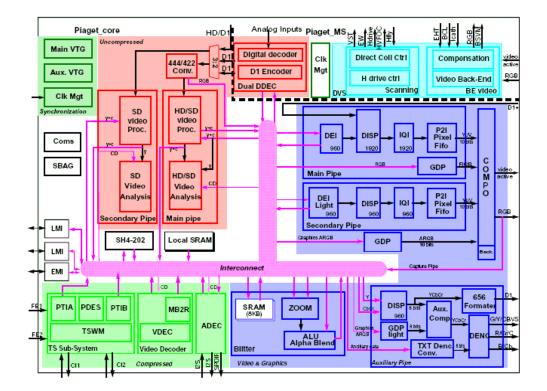

|   |     | 6.2.1   | STBus Genkit                                                                                           | . 152 |

|   |     | 6.2.2   | Mixed-level interconnection simulations                                                                | . 155 |

|   | 6.3 | Applie  | cations high-level descriptions                                                                        | . 156 |

|   |     | 6.3.1   | Video streams                                                                                          | . 157 |

|   | 6.4 | Traffic | c Modeling                                                                                             | . 159 |

|   |     | 6.4.1   | IPTG overview and sample file                                                                          | . 160 |

|   | 6.5 | Concl   | usion                                                                                                  | . 161 |

| 7 | Out | comes   | analysis of STNoC <sup>™</sup> benchmarking                                                            | 162   |

|   | 7.1 | Introd  | luction                                                                                                | . 162 |

|   | 7.2 | STNo    | $\mathbf{C}^{\mathbb{T}M}$ general characterization $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | . 163 |

|   |     | 7.2.1   | Throughput and latency measures                                                                        | . 163 |

|   | 7.3 | STNo    | $\mathbf{C}^{\mathbb{T}M}$ benchmarking of real applications                                           | . 169 |

|   | 7.4 |         | usion                                                                                                  |       |

| 8 | Cor | nclusio | ns and future work                                                                                     | 175   |

| 8.1 | Introduction                          |

|-----|---------------------------------------|

| 8.2 | Security monitoring                   |

| 8.3 | Towards clustered NoC-based platforms |

| 8.4 | Conclusion                            |

# Table des figures

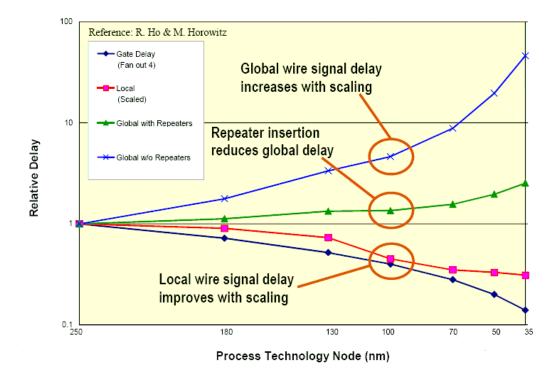

| 2.1  | Architecture de bus AHB                                                                         | 6  |

|------|-------------------------------------------------------------------------------------------------|----|

| 2.2  | Bus multicouche                                                                                 | 9  |

| 2.3  | Structure du protocole d'interconnexion                                                         | 10 |

| 2.4  | Réseau vu comme un ensemble de commutateurs et interfaces                                       | 11 |

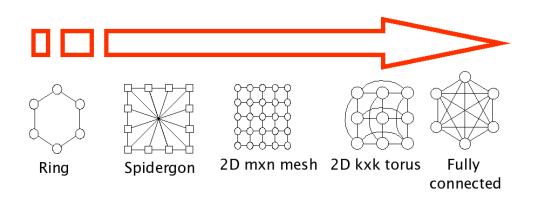

| 2.5  | Exemples de topologies                                                                          | 14 |

| 2.6  | Couches du protocole OCCN                                                                       | 15 |

| 2.7  | Infrastructure d'un modèle de nœud                                                              | 17 |

| 2.8  | Modèle de microarchitecture d'une interface réseau                                              | 18 |

| 2.9  | Modèle UML d'une interface réseau                                                               | 19 |

| 2.10 | Environnement d'exploration d'architecture pour $\operatorname{STNoC}^{{\scriptscriptstyleTM}}$ | 21 |

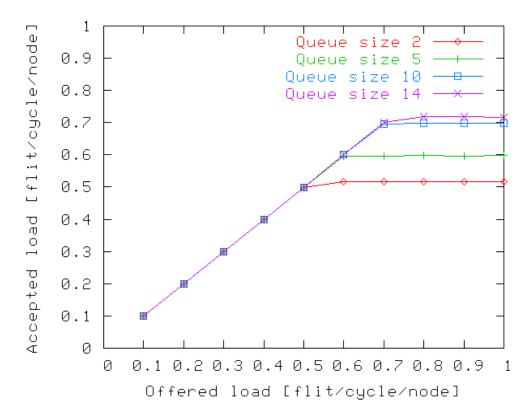

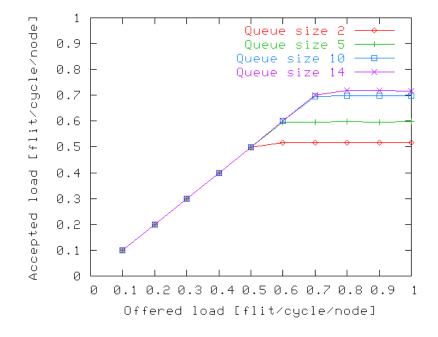

| 2.11 | Débit atteignable par un réseau STNoC <sup>TM</sup> $8x8$                                       | 22 |

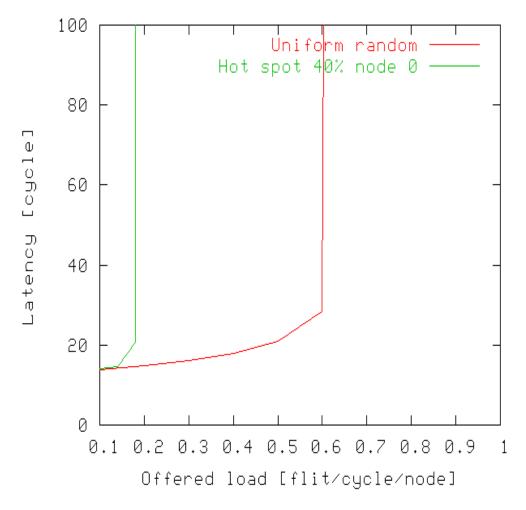

| 2.12 | Latences d'un réseau STNoC <sup>TM</sup> $8x8$                                                  | 23 |

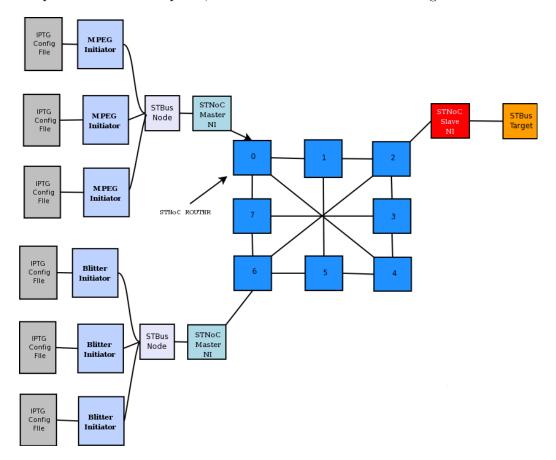

| 2.13 | Architecture de l'expérimentation menée sur $\mathrm{STNoC}^{{\scriptscriptstyleT\!\!M}}$       | 24 |

| 2.14 | Qualité de service appliquée                                                                    | 25 |

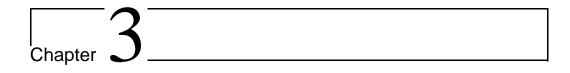

| 3.1  | Local vs. Global wires delay                                                                    | 30 |

| 3.2  | AMBA bus architecture                                                                           | 33 |

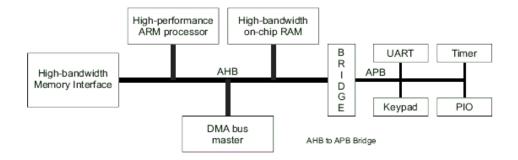

| 3.3  | AHB bus microarchitecture                                                                       | 34 |

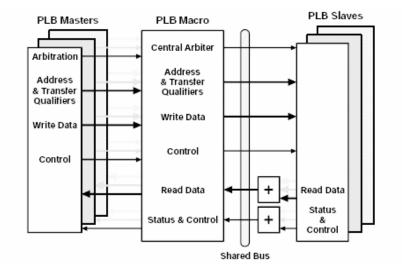

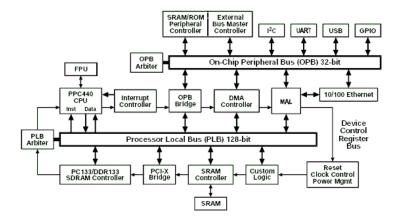

| 3.4  | PLB interconnection                                                                             | 36 |

| 3.5  | CoreConnect Based System-on-a-chip                                                              | 36 |

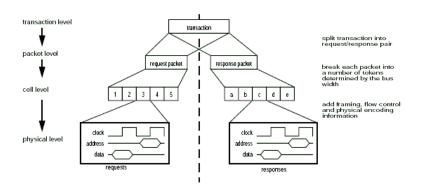

| 3.6  | STBus protocol hierarchy                                                                        | 37 |

|      |                                                                                                 |    |

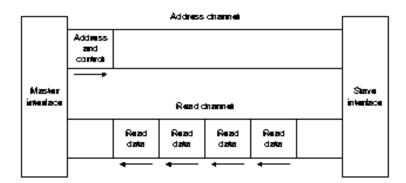

| 3.7        | AXI read channel overview                 | 39  |

|------------|-------------------------------------------|-----|

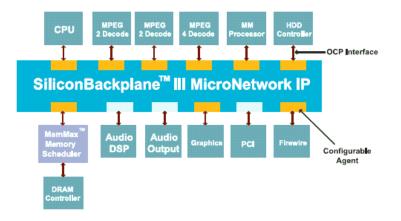

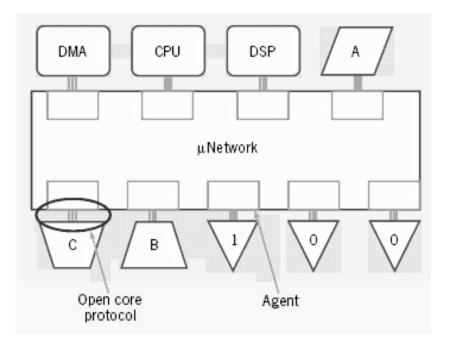

| 3.8        | Silicon backplane                         | 41  |

| 3.9        | Silicon backplane block integration       | 42  |

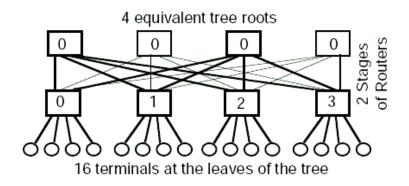

| 3.10       | SPIN topology: A Fat-Tree Network         | 43  |

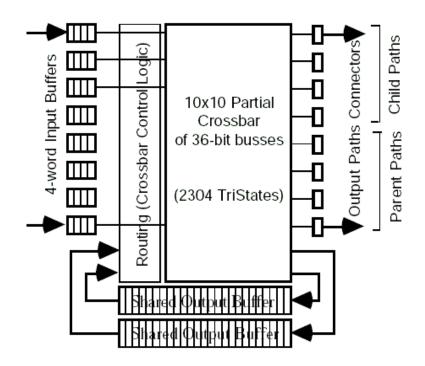

| 3.11       | SPIN router macrocell microarchitecture   | 44  |

| 3.12       | Overview of an Æthereal router            | 45  |

| 3.13       | RAW interconnect                          | 46  |

| 3.14       | RAW tiles                                 | 47  |

| 3.15       | NoC layers in Arteris solution            | 48  |

| 3.16       | Arteris "Danube" design flow              | 49  |

| 4 1        |                                           | 50  |

| 4.1        | OSI stack paradigm                        | 53  |

| 4.2        | Layers clustering                         | 55  |

| 4.3        | Virtual channel vs. wormhole flow control | 58  |

| 4.4        | Example of networks topologies            | 60  |

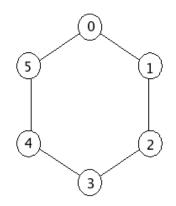

| 4.5        | Example of ring topology                  | 62  |

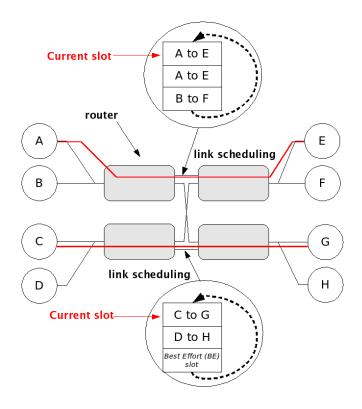

| 4.6        | TDM network example                       | 66  |

| 4.7        | Transport layer                           | 70  |

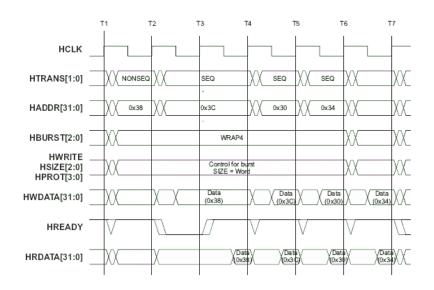

| 4.8        | AHB wrap4 burst transaction               | 71  |

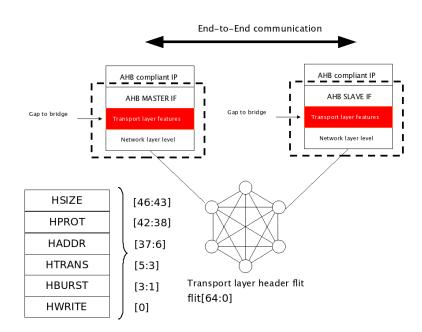

| 4.9        | AHB end-to-end connection                 | 72  |

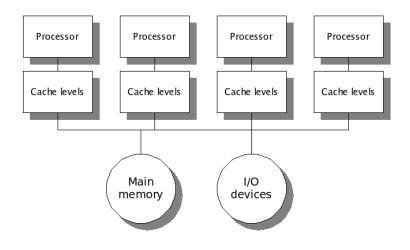

| 4.10       | UMA multiprocessors architecture          | 74  |

| 4.11       | NUMA multiprocessors architecture         | 74  |

| 4.12       | Example of race prevention                | 77  |

| 4.13       | Generic NoC router microarchitecture      | 79  |

| 4.14       | Spidergon topology                        | 80  |

| 4.15       | $STNoC^{TM}$ packet layering              | 83  |

| <b>F</b> 1 |                                           | 0.0 |

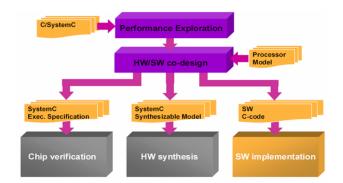

| 5.1        | SystemC flow                              |     |

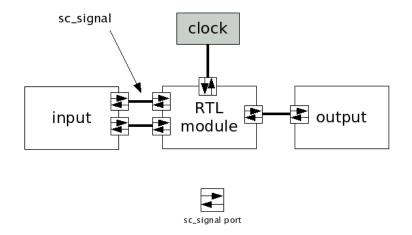

| 5.2        | SystemC sample RTL model                  |     |

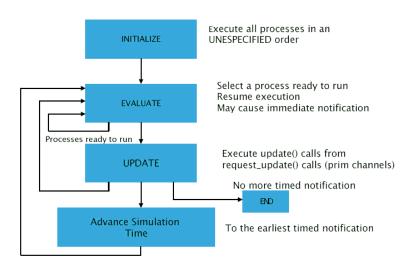

| 5.3        | SystemC scheduler scheme                  | 91  |

### TABLE DES FIGURES

| 5.4  | SystemC Simple Bus TLM structure                                   |

|------|--------------------------------------------------------------------|

| 5.5  | TLM stack                                                          |

| 5.6  | OSI like OCCN layering model                                       |

| 5.7  | OCCN API class hierarchy                                           |

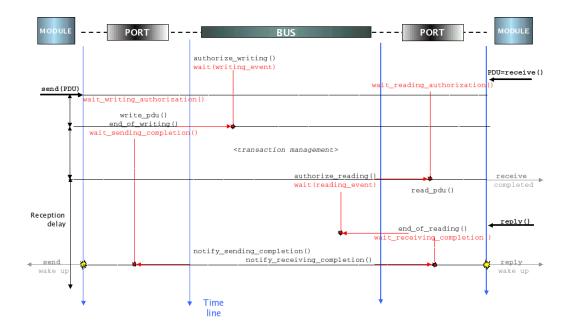

| 5.8  | Send/Receive protocol example                                      |

| 5.9  | Example of protocol implementation through MsgBox functions 111 $$ |

| 5.10 | Standard router sketched micro-architecture                        |

| 5.11 | Standard router link protocol handshake                            |

| 5.12 | Router model infrastructure                                        |

| 5.13 | Simulation speed comparison                                        |

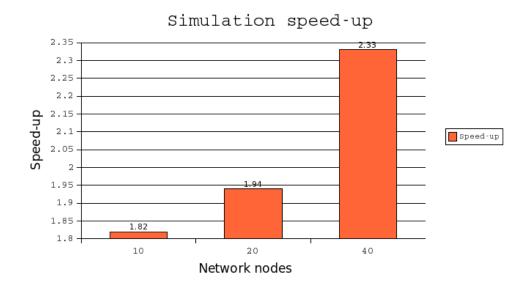

| 5.14 | Simulation speed-up                                                |

| 5.15 | Mock-up of a NI microarchitecture                                  |

| 5.16 | NI UML basic representation                                        |

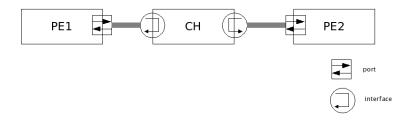

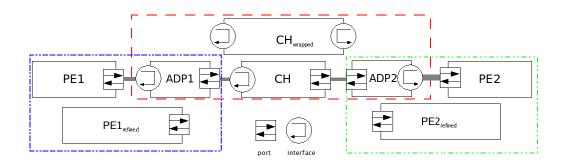

| 5.17 | Simple architecture example                                        |

| 5.18 | Wrapper example                                                    |

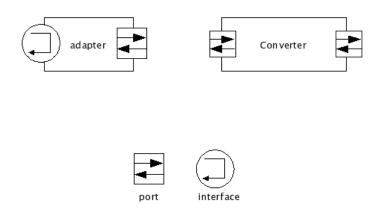

| 5.19 | Adapter/Converter                                                  |

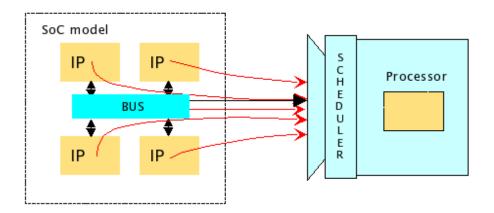

| 5.20 | Parallel resources                                                 |

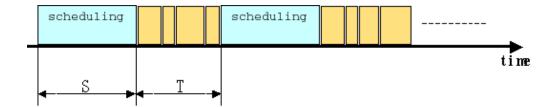

| 5.21 | SystemC scheduler flow of time                                     |

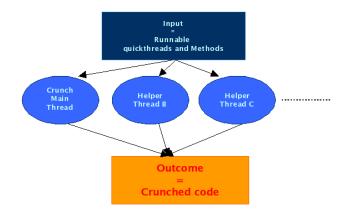

| 5.22 | Working crew paradigm                                              |

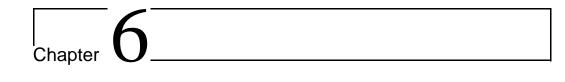

| 6.1  | An example of a STMicrolectronics SoC                              |

| 6.2  | STBus genkit design flow                                           |

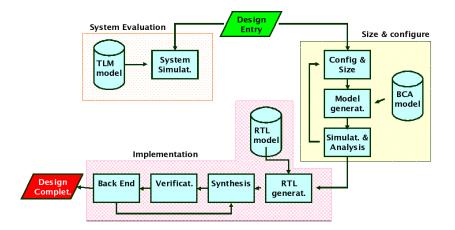

| 6.3  | NoC QT graphical user interface                                    |

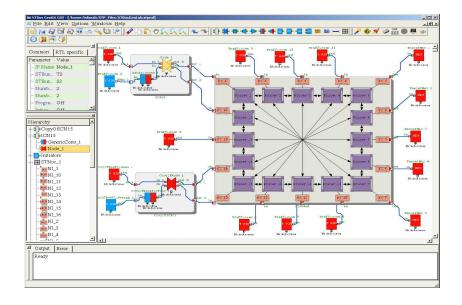

| 6.4  | STNoC design flow extension                                        |

| 6.5  | Example of MPEG P-frame                                            |

| 6.6  | Pseudo IPTG config file                                            |

| 7.1  | Accepted throughput                                                |

| 7.2  | Latency: random and hot-spot traffic                               |

| 7.3  | $STNoC^{TM}$ mappings                                              |

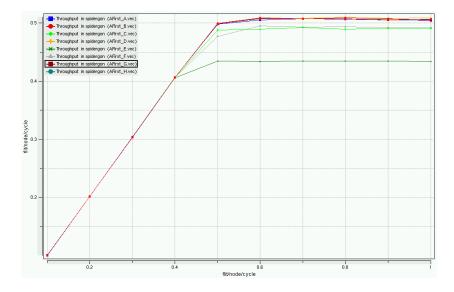

| 7.4 | Throughput measure in a $6x6$ network $\ldots \ldots \ldots$ |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.5 | Latency measure in a $6x6$ network                                                                                                                                           |

| 7.6 | An STNoC <sup>TM</sup> case study $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 170$                                                                       |

| 7.7 | MPEG QoS proof of concept, FIFO starvation avoidance $\ . \ . \ . \ 171$                                                                                                     |

| 7.8 | High-Definition (HD) QoS proof of concept, FIFO starvation<br>avoidance                                                                                                      |

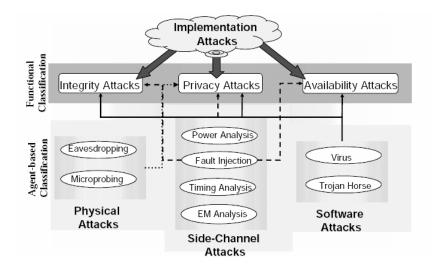

| 8.1 | Security attacks classes                                                                                                                                                     |

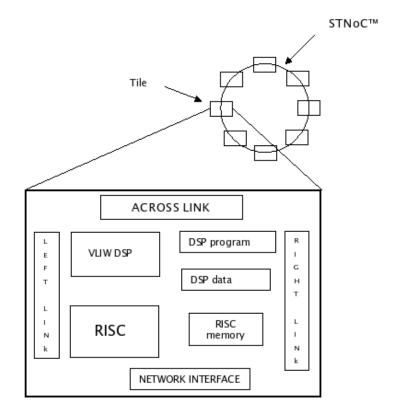

| 8.2 | $STNoC^{TM}$ in a multi-tile parallel architecture                                                                                                                           |

# Liste des tableaux

| 5.1 | OSCI terminology | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 98  |

|-----|------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| 5.2 | VHDL vs. OCCN    |   |   |   |   |   | • |   |   |   |   |   |   |   | • |   |   |   |   |   |   | • |   |   |   | • | 130 |

## Présentation de la thèse

### 1.1 Problématique

Au cours des trois décennies écoulées, depuis 1975, l'industrie des semiconducteurs a été gouvernée par la loi de Moore, qui affirme que le niveau d'intégration des circuits double tous les 18 mois [34]. Ceci a amené à la possibilité d'intégrer dans une seule puce l'ensemble des fonctions d'un système informatique : acquisition des données depuis des capteurs analogiques ou des réseaux de communication, traitement du signal, analyse et prise de décisions, émission de données ou rétroaction sur le monde extérieur. Une telle situation laisse entrevoir le développement de produits électroniques de faible coût, destinés au grand public, et dotés de fonctions intelligentes, grâce à l'emploi de tels systèmes embarqués ou systems on-chip. Le concept de system-on-chip implique une complexité croissante concernant la spécification, la vérification fonctionnelle et temporelle ainsi que le test de circuits monolithiques de plus de 200 millions de transistors. Ces aspects étaient encore gérables pour des circuits plus petits, et leur intégration en plus grands systèmes modulaires était plus aisée, précisément parce que les éléments restaient séparables.

A l'heure actuelle, toutes les méthodes de conception commencent par fragmenter le système en éléments plus petits (processeurs, DSP, mémoires, interfaces, ...), si possible puisés dans des bibliothèques. Le problème incontournable qui se pose est le suivant :

• Par quel moyen implémenter la communication entre ces éléments ?

De nombreux travaux de recherche sont désormais présents en littérature, tous abordant l'étude d'une nouvelle méthodologie pour l'implémentation de l'interconnexion pour circuits intégrés : les ainsi-dits Networks-on-chip [40]. Le rôle des réseaux sur puce consiste à résoudre les divers problèmes qui affligent la technologie d'interconnexion couramment utilisée pour les systèmes monopuce, le bus partagé. En particulier, ces systèmes contiennent de plus en plus d'éléments, ce qui implique des besoins en bande passante et latence maximum de plus en plus strictes, concept qui contraste avec la nature partagée d'un bus, qui pose donc des problèmes non négligeables en terme de mise à l'échelle.

### **1.2** Contribution

Les travaux de cette thèse consistaient à étudier, modéliser et implémenter, un réseau de communication flexible pour les futurs systèmes monopuce. Une nouvelle méthodologie de modélisation permettant la simulation au cycle près de réseaux complexes a été développée, qui a permis une étude approfondie de plusieurs system-on-chip au sein de STMicroelectronics. En particulier, les travaux de cette thèse ont contribué d'une façon significative au flot de conception de STNoC<sup>TM</sup>, la nouvelle technologie d'interconnexion développée par STMicroelectronics. Les modèles développés dans le cadre de cette thèse constituent une partie fondamentale de la méthodologie de conception de réseaux au niveau système qui a été appliquée à deux systèmes monopuce réels développés par STMicroelectronics, orientés vers la télévision numérique à haute définition.

### **1.3** Présentation de la structure de la thèse

Ce manuscrit se compose de deux parties fondamentales :

- Une partie introductive en français, qui présente les principaux concepts et contributions.

- Une partie en anglais, dont le contenu décrit d'une façon détaillée les travaux développés.

La thèse est constituée des chapitres suivant :

• ce chapitre présente la structure de la thèse.

- le deuxième chapitre résume le contenu de la thèse en français, en décrivant les principaux points abordés, détaillés en anglais dans les chapitres qui suivent.

- le troisième chapitre réalise un état de l'art qui définit les composants d'interconnexion pour les systèmes monopuce existants ainsi que de nouvelles technologies qui viennent d'être déployées.

- le quatrième chapitre définit les couches dont un réseau se compose et les éléments architecturaux du réseau STNoC<sup>™</sup> développé par STMicroeletronics.

- dans le cinquième chapitre, la méthodologie de modélisation de réseaux sur puce développée dans le cadre de cette thèse et appliquée au flot de conception de STNoC<sup>™</sup> est expliquée en détail, ainsi qu'une méthode qui permet des simulations SystemC distribuées.

- le sixième chapitre complète la description des composants utilisés dans l'étude approfondie de systèmes monopuce réels développés par STMicroelectronics, où le bus d'interconnexion a été partiellement remplacé par une architecture de réseau STNoC<sup>™</sup>.

- le septième chapitre montre les résultats obtenus lors de tests effectués sur le réseau STNoC<sup>™</sup> dans des conditions de trafic aléatoire et de trafic engendré par des IPs de STMicroelectronics.

- enfin le huitième chapitre tire les conclusions et décrit les évolutions futures concernant STNoC<sup>™</sup> qui sont en cours chez STMicroelectronics.

# Modélisation de réseau de communication flexible pour les systèmes monopuce

### 2.1 Introduction

Ce chapitre constitue un résumé de la thèse en français ; la thèse complète est développée en détail dans la deuxième partie, en anglais, qui commence au chapitre 3. Tout au long de ce chapitre, les concepts de base de réseaux sur puce et le flot de conception du STNoC<sup>TM</sup>, la nouvelle technologie d'interconnexion au sein de STMicroelectronics, sont décrits, avec une attention particulière accordée à la modélisation du réseau et son implémentation.

## 2.2 État de l'art

Cette section vise à présenter les principales technologies qui ont été déployées jusqu'à présent et les principaux axes de recherche concernant les systèmes de communication sur puce.

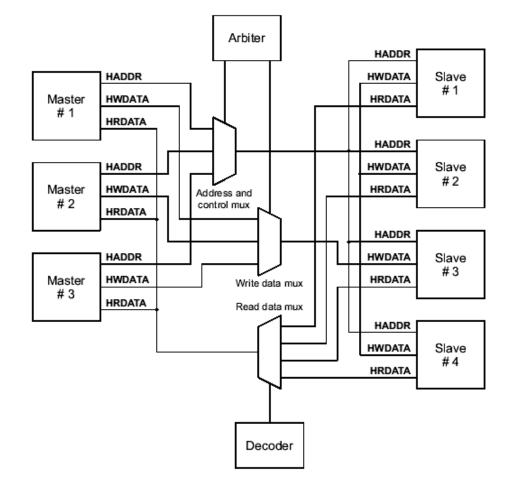

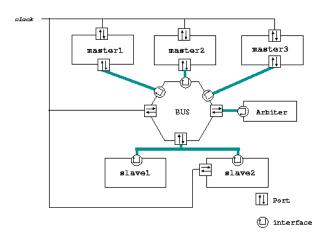

La technologie la plus utilisée pour ce qui concerne l'interconnexion des systèmes monopuce est celle du bus partagé (voir figure 2.1). Elle a déjà été utilisée dans un très grand nombre de produits, de sorte que tous les systèmes intégrés utilisent à peu près des technologies équivalentes.

Fig. 2.1: Un exemple d'architecture de bus [2] (ARM AHB).

Un bus partagé se compose notamment :

- D'un bus de données partagé (unique et connecté à tous les éléments du système).

- D'un bus d'adresses ayant les mêmes caractéristiques.

- D'un élément particulier du système, appelé arbitre du bus, connecté par des liaisons point à point à tous les autres éléments.

Tous les éléments connectés au bus sont à même d'échantillonner ou piloter les lignes du bus de données ; par contre le bus d'adresses ne peut être piloté que par certains d'entre eux, les maîtres.

Dans une architecture de bus ces éléments appelés maîtres initient les transactions sur le bus en pilotant les bus d'adresses, transactions adressées à des esclaves qui sont identifiés par des plages d'adressage. La nature partagée d'un bus implique une étape d'arbitrage qui sert à choisir le maître qui peut disposer du bus. Cette centralisation est une caractéristique spécifique qui distingue les bus partagés des réseaux de communication pour lesquels l'arbitrage est distribué. Les transactions sont soit des écritures (le maître requiert une écriture dans une zone de mémoire appartenant à l'esclave), soit des lectures (le maître demande des données à l'esclave qui les lui retourne). Il existe plusieurs extensions qui peuvent être apportées aux protocoles des bus. Par exemple l'atomicité des primitives de synchronisation entre processeurs, pour la gestion de la cohérence des mémoires caches ainsi que pour la politique d'arbitrage.

Un bus partagé, et en particulier sa topologie, possède plusieurs avantages. Premièrement, il peut supporter directement le modèle de communication par adressage mémoires des CPUs, qui représente actuellement le modèle le plus répandu pour les IPs (« Intellectual Properties » ). En y intégrant de légères modifications les interfaces du bus peuvent supporter des opérations complexes (communication par flux) et surtout réutilisables (« transactioncentric-design »). Deuxièmement, le mode de fonctionnement de l'arbitre est simple et on peut facilement l'adapter aux différentes applications requises. Finalement, le concept de bus est parfaitement maîtrisé par les concepteurs de matériel, ce qui favorise son usage et sa large diffusion.

Malheureusement un bus partagé a aussi des limites, impliquées dans la plupart des cas par sa nature partagée. Ce sont des limites qui ont stimulé sensiblement des travaux de recherche pour essayer de déterminer de vraies alternatives au concept de bus. Un bus partagé implique de nombreux problèmes de mise à l'échelle. Ceci s'avère être inacceptable, surtout pour le débit global. Un arbitrage plus sophistiqué et des mémoires cache ne peuvent qu'alléger cette contrainte assez forte. Le problème peut être résolu de deux façons : soit en augmentant la largeur du bus, soit en augmentant la fréquence d'horloge. Les deux solutions ne sont pas satisfaisantes car elles impliquent des problèmes électriques auxquels il est coûteux de remédier convenablement.

Même si le débit global est suffisant, le bus n'est plus utilisable pour des grands systèmes avec un nombre élevé d'éléments à connecter. Dans ce cas, le goulot d'étranglement devient l'arbitre central qui doit choisir un maître auquel concéder le bus parmi des dizaines. Un arbitre central peut difficilement accomplir cette tâche efficacement, sans introduire un accroissement de la latence diminuant ainsi le débit global, à cause des cycles où le bus ne peut pas être utilisé. Cet effet va empirer de plus en plus au fur et à mesure que les technologies évoluent et que l'échelle d'intégration augmente.

Un bus partagé, ne possédant aucun concept de couches de communication, empêche un découplage efficace des deux parties de calcul et de communication, ce qui représente une entrave majeure au développement de systèmes hiérarchiques.

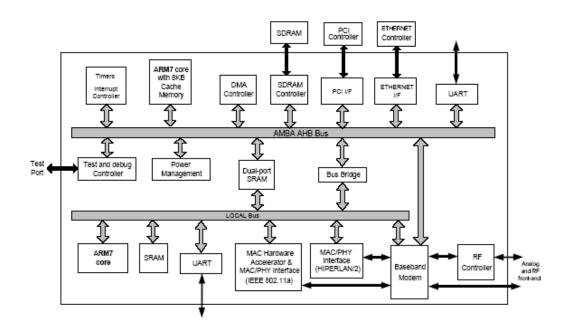

En résumant, on peut ramener toutes les limites d'un bus partagé à un problème de mise à l'échelle. Une solution assez répandue pour résoudre ce problème consiste à multiplier les bus dans les systèmes (voir figure 2.2). Ainsi, les concepteurs sont à même de découper le système en parties plus ou moins indépendantes formant une hiérarchie de bus ou un bus multi-couche. Ces bus peuvent être connectés entre eux par des ponts qui permettent de mieux gérer le débit requis et créer des liens entre les différentes parties. Une infinité de solutions est possible, ce qui favorise l'exploration d'architecture. Ceci permet de mieux choisir les arbitrages dans les divers bus grâce à une politique d'arbitrage qui devient de plus en plus distribuée par rapport au concept d'arbitre central d'un bus partagé. Beaucoup d'exemples de bus multi-couche sont déjà présents dans des produits commerciaux; le STBus [67] de STMicroelectronics et l'architecture AMBA [2] développée par ARM en représentent une partie. Toutefois ces solutions doivent être conçues adhoc pour chaque système, ce qui rend la conception coûteuse et surtout non durable. De plus, comme le nombre des composants sur puce augmente de plus en plus, la solution multi-couche ne pourra pas résoudre indéfiniment le problème fondamental de mise à l'échelle.

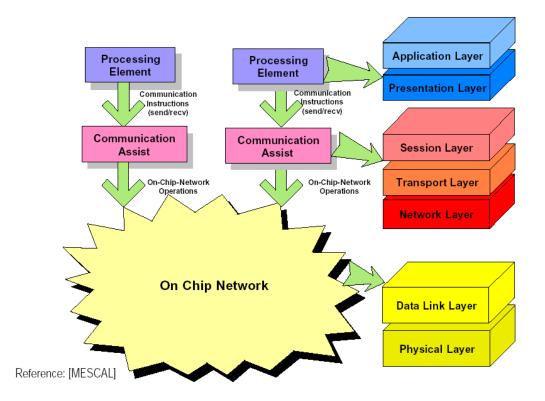

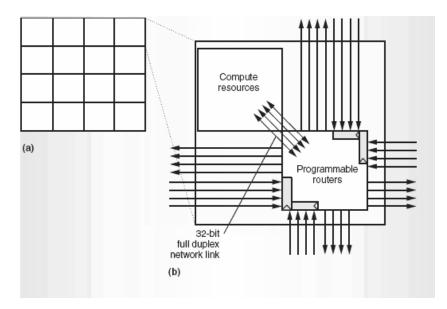

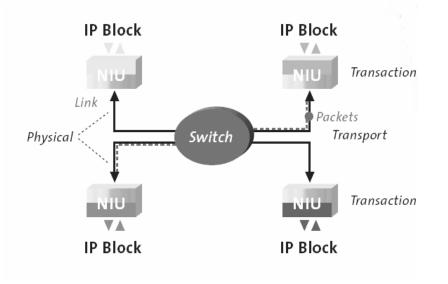

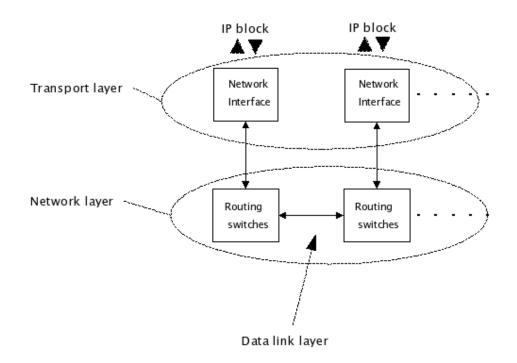

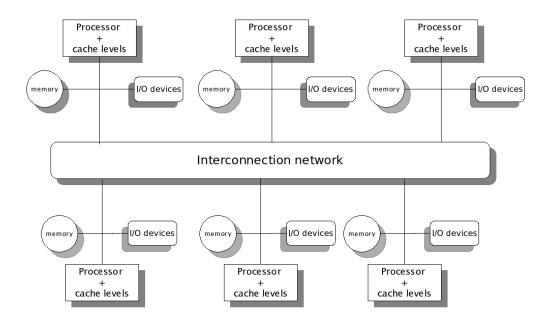

Le concept de réseau sur puce s'est imposé comme solution possible au problème de l'interconnexion (voir figure 2.3). Il existe deux raisons principales qui le soutiennent. Premièrement, les réseaux sur puce aident à résoudre les problèmes électriques que les nouvelles technologies (submicroniques) imposent, parce qu'ils structurent d'une façon convenable les fils globaux (voir

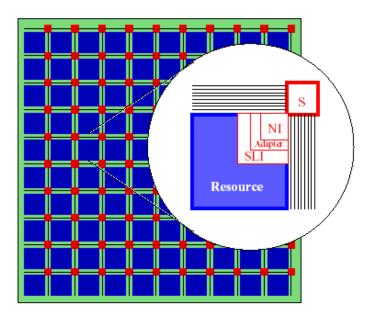

Fig. 2.2: Un exemple d'architecture de bus multi-couche

figure 2.4). En même temps ils permettent de les partager en réduisant leur nombre et en améliorant leur usage. Les réseaux sur puce peuvent être efficaces et fiables, et surtout ils facilitent la mise à l'échelle par rapport aux bus partagés et multi-couche. Deuxièmement, les réseaux sur puce aident à découpler les parties de calcul et de communication (NI - Network Interface, voir figure 2.4), ce qui est essentiel lorsqu'il faut gérer des systèmes contenant un grand nombre d'éléments. Les réseaux sur puce constituent la future technologie d'interconnexion pour les systèmes intégrés et permettent à la fois de fournir une interface complète et flexible aux couches logicielles et un niveau d'abstraction de l'interconnexion qui convienne au développement et à la conception au niveau système.

L'emploi de réseaux comme interconnexion pour systèmes sur puce implique un certain nombre de questions qui doivent être prises en compte. Contrairement aux interconnexions telles que bus ou fils point-à-point, où les modules communicants sont connectés directement, dans les réseaux ces mêmes modules communiquent par l'intermédiaire de nœuds. Ainsi, l'arbitrage d'un réseau change de centralisé à distribué et les problématiques telles que transactions désordonnées, latence élevée et contrôle de flux « end-to-end » doivent être prises en compte par les IPs ou le réseau même.

Il existe un grand nombre de propositions en littérature concernant les

Fig. 2.3: Structuration de la communication pour les futures systèmes sur puce

Fig. 2.4: Réseau vu comme un ensemble de commutateurs (S), interfaces (NI), et ressources. Le réseau permet une effective structuration de l'interconnexion.

réseaux sur puce, chacune avec ses atouts et ses points faibles. Il est tout à fait utile de les approfondir toutes, tout en sachant que, considérant les grands axes de recherche, deux points clés s'avèrent être fondamentaux et discriminatoires :

- 1. Topologie fixe ou paramétrable

- 2. Infrastructure mise en place pour garantir une certaine qualité de service du réseau

En ce qui concerne le premier point, une topologie fixe implique beaucoup d'avantages. La topologie étant fixe, les concepteurs peuvent mieux régler les paramètres des nœuds du réseau (mémoire tampon, canaux virtuels, algorithme de routage). Par contre, l'exploration d'architecture de l'interconnexion qui en découle s'en voit être limitée, car du moment que la topologie d'interconnexion a été fixée à priori, les concepteurs ont moins de degrés de liberté. Une topologie paramétrable possède des avantages et des points faibles spéculaires par rapport à une topologie fixe. Bien sûr, elle permet une exploration d'architecture de réseau optimale, aidant à adapter la meilleure topologie et le meilleur algorithme de routage à une application donnée. Par contre la possibilité d'avoir un réseau paramétrable implique un nombre élevé de degrés de liberté pour la conception des éléments fondamentaux du réseau (nœuds et interfaces), concept qui contraste bien souvent avec un réglage optimal et surtout à bas coût en terme de surface, détail très important pour la conception de circuits intégrés.

Le deuxième point représente une question cruciale dont la solution ne peut pas être définie incontestablement. La théorie basique des réseaux recommande deux approches pour garantir une certaine qualité de service aux IPs qui les utilisent :

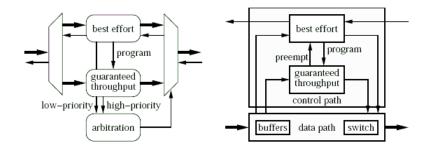

Approche « Best-Effort » : Une application est structurée sur un ensemble d'IPs communiquant par un réseau avec une certaine topologie. L'application a des besoins tels que débit et latence. Le réseau est dimensionné de façon à pouvoir fournir le débit et la latence requis. L'atout principal de cette solution est la simplicité d'implémentation et le bas coût en termes de ressources occupées qui en découle pour le système. Le point faible réside dans le fait que cette solution peut causer un surdimensionnement du réseau et, comme pour un bus multicouche, doit être appliquée cas par cas selon les conditions requises par l'application : Cette approche souffre donc d'un défaut de programmabilité.

Approche « Guaranteed services » : Le réseau de communication peut être considéré comme un fournisseur de services intégrés : les IPs requièrent certaines conditions de fonctionnement qui doivent être négociées avec le réseau. Le réseau en tant que fournisseur de service peut accepter ou refuser la connexion selon l'état actuel où le réseau se trouve. La transmission et la réception des données peuvent avoir lieu seulement après la mise en place d'une connexion entre les IPs conforme aux conditions requises. Evidemment cette approche possède un degré de programmabilité bien plus important que l'approche «best-effort»; le système a donc la qualité d'être prévisible et flexible. Le principal point faible est dû au coût en surface qui découle d'une architecture de réseau capable de fournir des services intégrés<sup>1</sup>, considérant les tenants et les aboutissants que cette caractéristique implique savoir. Laquelle de ces deux approches est la meilleure reste une question ouverte, ce seront les réalisations qui éliront la plus convenable pour chaque type d'application (étant donné que toute considération correcte devra sans doute être rapportée à chaque cas particulier).

L'évolution de ces deux approches représente la solution aux futurs systèmes de communication pour les systèmes monopuce. Dans le cadre de cette thèse, une nouvelle technologie d'interconnexion de systèmes monopuce ainsi que les outils pour sa modélisation et son implémentation ont été développés. STNoC<sup>TM</sup>, le réseau sur puce développé par STMicroelectronics, est l'aboutissement d'un grand effort de conception, dont cette thèse constitue tout de même une partie importante.

<sup>&</sup>lt;sup>1</sup>Les services garantis requièrent des composants matériels spécifiques dans les nœuds, par exemple des tables de routage; une qualité de service construite sur un réseau « best-effort » ne requiert pas de composants supplémentaires, ce qui diminue les besoins en surface.

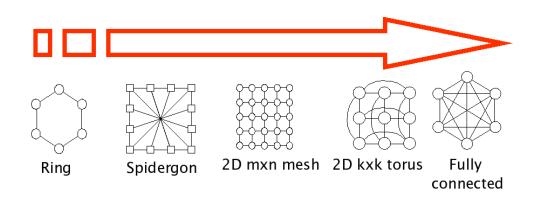

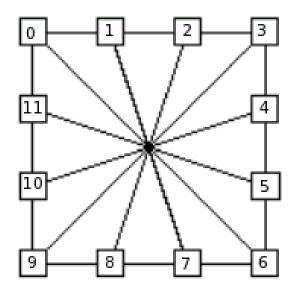

Fig. 2.5: Exemples de topologies

Le réseau sur puce STNoC<sup>TM</sup> est basé sur une topologie fixe surnommée « Spidergon » (voir figure 2.5), dont l'algorithme de routage qui détermine le chemin le plus court entre deux nœuds est le suivant (où N correspond au nombre de nœuds) :

```

\begin{array}{l} \mbox{if } (dest = curr) \ \mbox{then} \\ output \leftarrow NI \\ \mbox{else} \\ \mbox{if } (|dest - curr| \leq \frac{N}{4}) \parallel (|dest - curr| \geq (N - \frac{N}{4})) \ \mbox{then} \\ \mbox{if } (dest \in [curr + 1, ..., curr + \frac{N}{4}]) \ \mbox{then} \\ output \leftarrow RIGHT \\ \mbox{else} \\ output \leftarrow LEFT \\ \mbox{else} \\ output \leftarrow ACROSS \\ \mbox{end if} \\ \mbox{end if} \\ \mbox{end if} \\ \end{array}

```

STNoC<sup>TM</sup> a choisi comme implémentation de services une modalité « besteffort », sur laquelle une infrastructure de qualité de service très puissante et flexible a été construite; les détails de cette implémentation sont confidentiels STMicroelectronics et donc ne peuvent pas être dévoilés dans cette thèse. Un exemple d'application de cette technologie sera décrit dans la section 2.4 à la page 20. Les sections suivantes décrivent et résument le développement de l'environnement de simulation de STNoC<sup>TM</sup>, un élément qui a fait preuve de maturité et d'efficacité en systèmes réels ciblant la télévision numérique à haute définition, produits par STMicroelectronics.

## 2.3 Méthodologie de modélisation de réseaux sur puce

La conception des systèmes monopuce représente une tâche très complexe dont les différents stades deviennent de plus en plus découplés et indépendants. La définition d'un flot de conception qui fournit un niveau d'abstraction adéquat pour la conception au niveau système représente un élément fondamental pour la conception de circuits à complexité croissante.

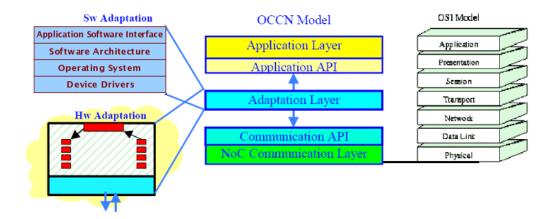

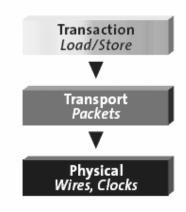

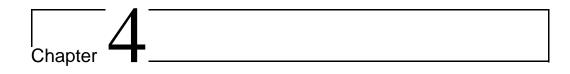

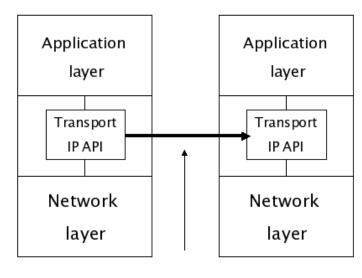

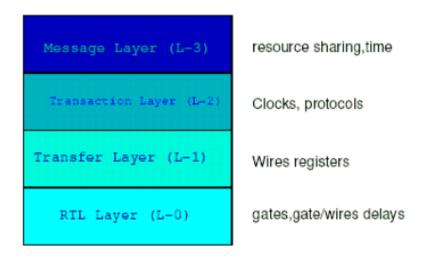

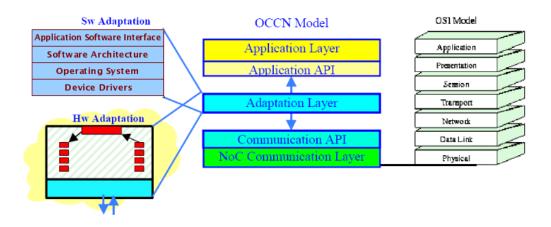

Le projet On-Chip Communication network (OCCN) [17], développé sous « sourceforge », fournit un environnement efficace et performant pour la spécification, modélisation et simulation de réseaux sur puce basé sur une méthodologie orientée objet conçue sur le noyau SystemC. OCCN augmente la productivité du développement d'adaptateurs de communication grâce à une interface de programmation (API) universelle [17]. Cette interface de communication fournit une nouvelle méthode de modélisation qui prône la création et la réutilisation de modèles exécutables au niveau transactionnel entre différentes plate-formes de simulation. La méthodologie OCCN se focalise sur la modélisation de réseaux sur puce complexes en proposant une approche par couches pour la modélisation (voir figure 2.6). OCCN définit

Fig. 2.6: Couches de modélisation du protocole OCCN

trois couches différentes. Le plus bas niveau implémenté par OCCN, intitulé NoC Communication Layer intègre une ou plusieurs couches OSI, en commençant par abstraire le niveau physique. Au plus haut niveau de la pile du protocole d'OCCN, la couche applicative se calque sur la couche applicative du protocole OSI [63]. Positionnée entre la couche applicative et la couche de communication, la couche d'adaptation implémente une ou plusieurs couches du protocole, en incluant composants logiciels et matériels.

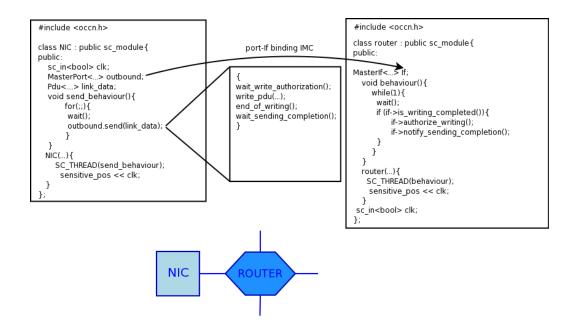

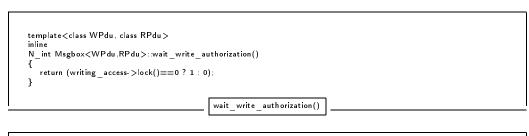

OCCN implémente la communication entre modules en utilisant l'approche générique SystemC [33], où un port peut être vu comme un point d'accès à un service définit par l'API d'OCCN. L'application du modèle conceptuel d'OCCN à SystemC est définie comme suit :

- La couche de communication est implémentée comme un ensemble de classes C++ dérivées de la classe sc\_channel. Le canal de communication établit le transfert de messages entre les différents ports selon la pile du protocole supportée par un réseau spécifique.

- L'interface de communication (API) est implémentée comme une spécialisation de la classe sc\_port de SystemC. Cette interface fournit les mémoires tampon requises pour la communication entre modules et la synchronisation.

- La couche d'adaptation convertit les transactions de requête entre modules engendrées par l'interface de l'application (API) en primitives appartenant à la couche de communication.

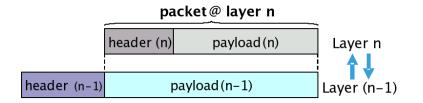

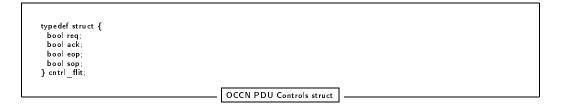

Les composants fondamentaux de l'API d'OCCN sont le « protocol data unit » (ou PDU, d'après la terminologie OSI) et les interfaces MasterPort et SlavePort. Dans OCCN la communication entre modules est basée sur des canaux qui implémentent des protocoles en définissant des règles et des types pour les PDUs. En général, les PDUs peuvent représenter des bits, des jetons, des messages d'un réseau d'ordinateurs, ou des signaux sur un réseau sur puce. Chaque PDU est composé de deux entités :

- L'en-tête intègre l'adresse de destination et il inclut l'adresse de la source. De plus, l'en-tête contient des codes d'opération qui servent à distinguer (a) requêtes / réponses (b) lectures/écritures (c) instructions de synchronisation (d) instructions bloquantes/non-bloquantes et (e) instructions de système.

- Le champ de donnée (appelé *payload*), ou *service data unit* est une séquence de bits qui n'ont pas de signification pour le canal.

Le paradigme utilisé par les interfaces de communication OCCN (objets Msg-Box) afin d'envoyer et de recevoir des données est le passage de messages,

qui définit des primitives *send* et *receive* pour communiquer par l'envoi et la réception de PDUs.

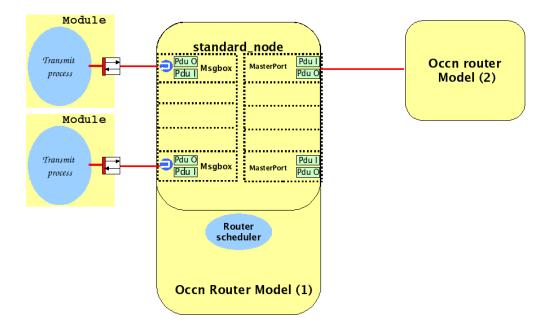

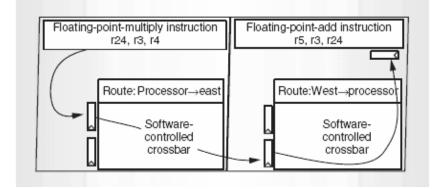

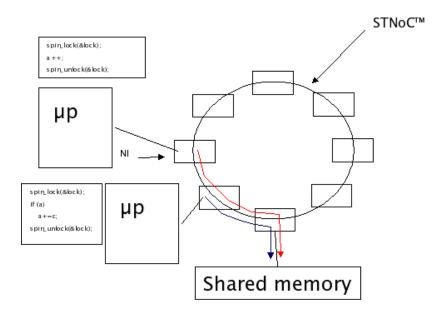

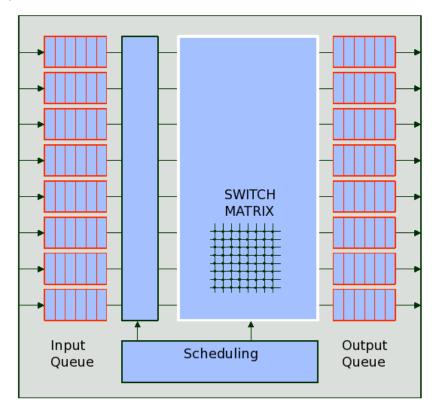

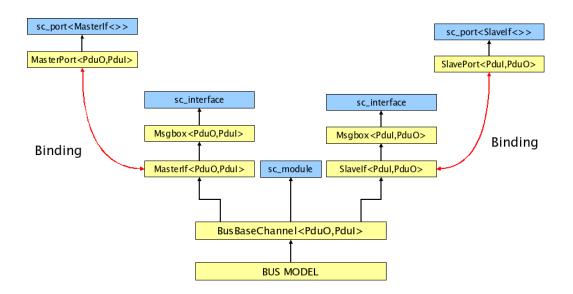

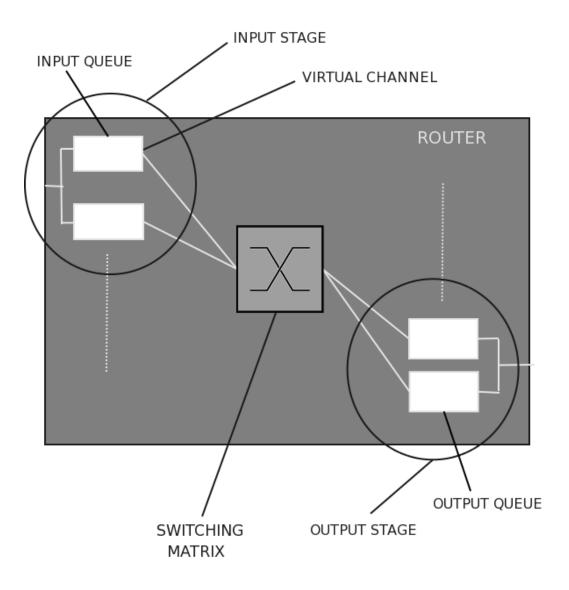

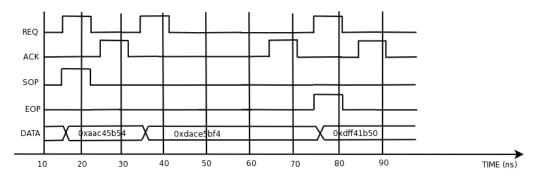

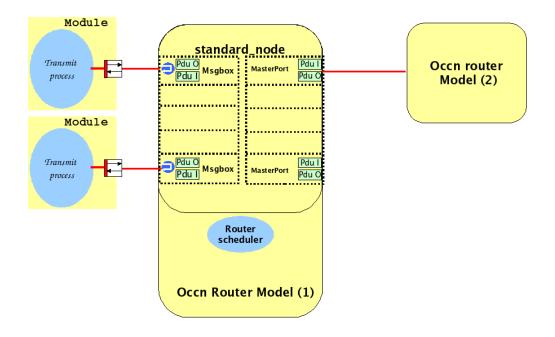

Les modèles d'interconnexion de STNoC<sup>TM</sup> ont été développés en utilisant les briques de base fournies par l'environnement OCCN. La figure 2.7 définit le squelette d'un modèle de nœud STNoC<sup>TM</sup> en OCCN. La partie maître du

Fig. 2.7: Infrastructure d'un modèle de nœud

nœud est contrôlée par un objet OCCN *MasterPort* (un port par lien d'un maître et une *Msgbox* par lien d'un esclave), qui consiste en un port SystemC hiérarchique, construit pour s'adapter aux interfaces implémentées dans les objets *MsgBox*. En OCCN un nœud peut être vu comme une machine à états hiérarchique, où les étapes de pipeline sont décomposées en entrée, commutation et sortie. Chaque étape de pipeline est composée de détails microarchitecturaux.

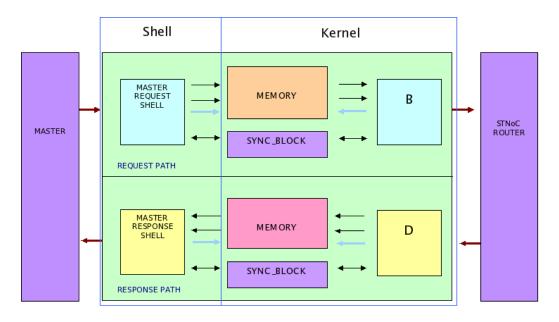

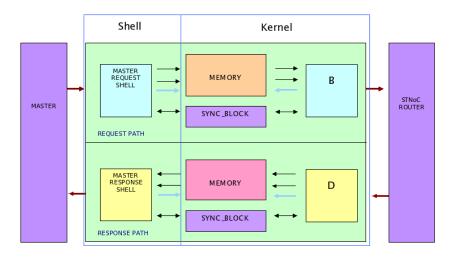

Fig. 2.8: Modèle de microarchitecture d'une interface réseau

Le modèle d'une interface réseau suit la configuration de la microarchitecture (voir figure 2.8), où le composant est divisé en deux parties principales :

- Noyau.

- « Shell ».

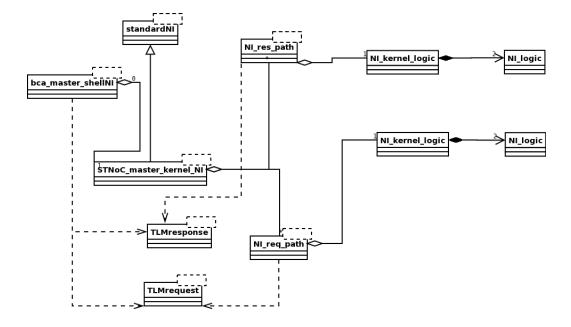

Le rôle du « shell » consiste à gérer la couche transport de l'interface réseau tandis que le noyau est chargé de contrôler le flux des données vers le nœuds et mettre en place la réalisation des paquets. La figure 2.9 définit un schéma basique en UML du modèle de l'interface réseau qui éclaircit les relations entre les différents objets utilisés. L'environnement de modélisation développé pour STNoC<sup>™</sup> autour d'OCCN contient aussi des adaptateurs qui permettent la co-simulation de modèles transactionnels tels qu'OCCN avec des composants RTL décrits soit en SystemC soit en Verilog. Le développement de ces couches d'adaptation a été une partie fondamentale de ma thèse car il a permis de réutiliser et d'adapter le nouveau flot de conception aux éléments déjà existants au sein de STMicroelectronics.

Fig. 2.9: Modèle UML d'une interface réseau

### 2.3.1 Simulations distribuées pour les systèmes monopuce

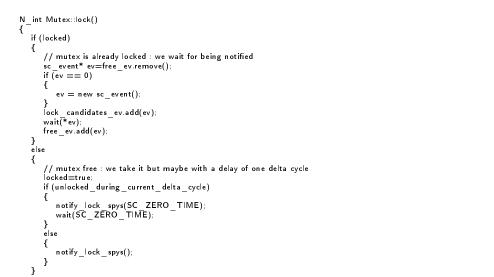

Une partie des travaux concernant la modélisation a été consacrée à la réécriture du noyau SystemC afin de permettre des simulations distribuées de systèmes monopuce. La solution mise en place est basée sur le concept de *helper threads*, à savoir des tâches d'exécution qui permettent la mise en parallèle et la concurrence lors de l'exécution de simulations en SystemC. Une première partie du travail a été nécessaire pour définir avec quelle granularité la mise en parallèle du noyau SystemC était possible.

Une fois convenu que la partie de code pouvant être mise en parallèle correspond au *delta cycle* [33], le développement du code a été assez facile. En effet, un *delta cycle* correspond au plus petit grain de synchronisation possible entre « processes » SystemC. Il restait tout de même des problèmes non négligeables concernant la protection des *sections critiques*, zones de code partagées en mémoire qui doivent être protégées afin d'éviter une concurrence indéterministe (« race conditions ») entre tâches (voir l'exemple de code suivant, qui représente une section critique dans la gestion de « processes » SystemC).

```

inline void sc_runnable::push_back_method( sc_method_handle method_h )

{

// assert( method_h->next_runnable() == 0 ); // Can't queue twice.

method_h->set_next_runnable(SC_NO_METHODS);

#ifdef MP_ST

pthread_spin_lock(&m_lock);

#endif

m_methods_push_tail->set_next_runnable(method_h);

m_methods_push_tail= method_h;

#ifdef MP_ST

pthread_spin_unlock(&m_lock);

#endif

}

Section critique, accès aux listes chaînées

```

Dans le noyau SystemC il y a beaucoup de sections critiques, en particulier en ce qui concerne la gestion des méthodes et « processes ». La solution au problème des sections critiques a été une des étapes les plus compliquées dans le cadre de cette thèse.

Des améliorations sont à l'étude pour parachever le nouveau noyau de simulation SystemC. Les premiers résultats de simulation ont démontré l'efficacité du nouveau noyau pour des modèles contenant un nombre moyen (10 - 20) de nœuds. Les simulations ont été exécutées sur une machine Intel Xeon (biprocesseur), Linux SMP 2.4, fonctionnant à la fréquence de 2.8 Ghz.

## 2.4 Exploration d'architecture du réseau ST-No $\mathbf{C}^{\mathsf{TM}}$

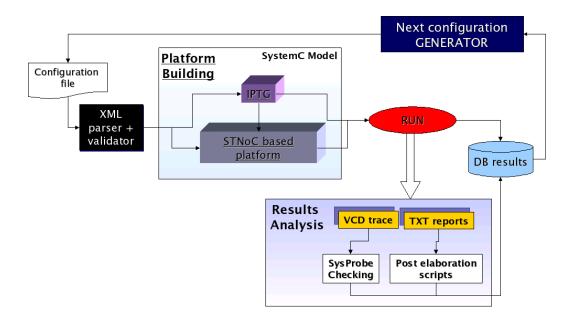

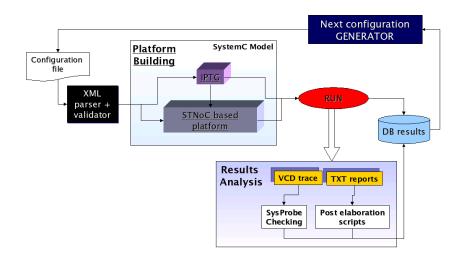

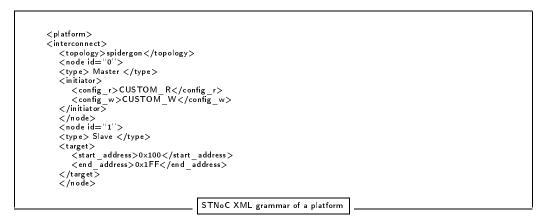

L'environnement de simulation développé dans le courant de cette thèse a été utilisé à plusieurs reprises pour l'exploration d'architecture d'interconnexions de systèmes monopuce réels de STMicroelectronics. Afin de protéger les propriétés intellectuelles de STMicroelectronics, il est impossible de décrire les études menées desdits systèmes. C'est pourquoi, dans le cadre de cette thèse, deux types de tests ont été créés expressément afin de démontrer à la fois les propriétés de STNoC<sup>TM</sup> et du simulateur. La figure 2.10 décrit le flot de conception de STNoC<sup>TM</sup> en détail. Le flot de conception fait usage de différents composants puisés dans des librairies de modèles propres à STMicroelectronics (par exemple le Genkit pour le STBus et les IP Traffic Generator pour la génération de trafic). Grâce à une forte reconfigurabilité cet instrument permet de tester et de simuler un grand nombre de configurations de réseau en un temps restreint. La configuration est faite par des fichiers XML dont la grammaire permet une analyse facile et standard pour la création et la connexion de composants.

Fig. 2.10: Environnement d'exploration d'architecture pour STNoC<sup>™</sup>

Les résultats qui suivent sont décrits dans le seul et unique but de démontrer comment on peut caractériser un vrai réseau sur puce d'un point de vue du flot de conception. Ces résultats partiels ne sont pas optimisés et ils ne correspondent surtout pas à la caractérisation officielle du réseau  $STNoC^{\mathbb{M}}$ . La caractérisation officielle de  $STNoC^{\mathbb{M}}$  est disponible comme document interne et confidentiel de STMicroelectronics et ne peut pas être dévoilée dans le cadre de cette thèse pour des raisons de confidentialité.

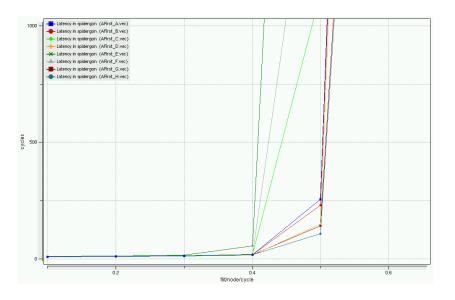

Un premier test a été écrit pour caractériser les propriétés de STNoC<sup>TM</sup> à travers un trafic purement aléatoire. La configuration choisie est celle d'un réseau STNoC<sup>TM</sup> à huit nœuds où tous les nœuds envoient et reçoivent des paquets de tous les autres. Le graphe en figure 2.11 compare le débit offert au débit accepté par le réseau. L'axe X correspond au nombre de « flits » (FLow control digITS [21]) injectés par cycle d'horloge. L'axe Y correspond aux « flits » acceptés. La courbe se compose de deux parties :

- Linéaire.

- Saturation.

En zone linéaire le réseau est à même d'accepter le trafic injecté; l'efficacité de l'algorithme de routage, du contrôle de flux et de la mise en mémoire

Fig. 2.11: Débit atteignable par un réseau STNoC $^{\mathbb{M}}$ 8x8

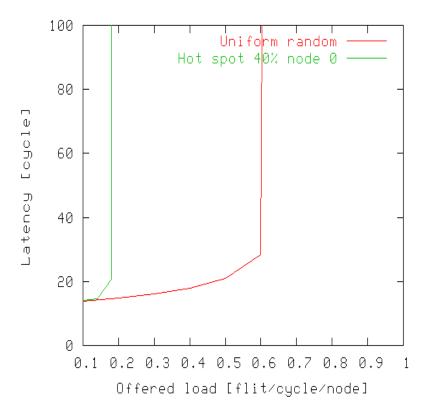

tampon peut être mesurée grâce aux latences des paquets. Dans ce but, le graphe en figure 2.12 montre les latences des paquets sur le réseau.

Plus particulièrement, le trafic injecté est de deux types :

- **Trafic aléatoire** qui consiste à envoyer des paquets uniformément distribués à tous le nœuds du réseau qui fonctionnent à la fois comme maîtres et esclaves.

- **Trafic « hot-spot »** qui consiste à envoyer un pourcentage p du trafic au nœud « hot-spot » selon la formule :

$$P(destination == hotspot) = (p) * (N-1) + (1-p) * \frac{N-1}{N} \quad (2.1)$$

où N est le nombre de nœuds et p la probabilité selon une distribution de Bernoulli d'une destination de type « hot-spot ».

Lorsque 40% du trafic est dirigé vers une seule cible (« hot-spot »), le point de saturation décroît d'une façon très importante, ce qui implique une saturation à très bas seuil.

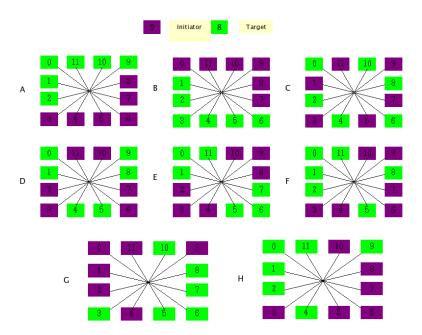

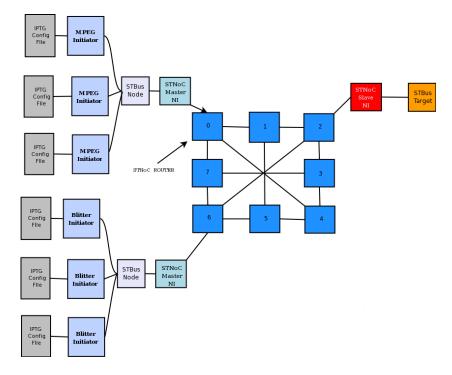

Des contraintes de confidentialité obligent à ne pas décrire les résultats, fondamentaux pour STNoC<sup> $\mathbb{M}$ </sup>, obtenus dans l'étude approfondie de deux systèmes réels produits par STMicroelectronics orientés vers la télévision numérique à très haute définition. Afin de remplacer ces expériences, un test simplifié a été mis en place, dont le schéma est montré en figure 2.13. Deux

Fig. 2.13: Architecture de l'expérimentation menée sur STNoC<sup>™</sup>

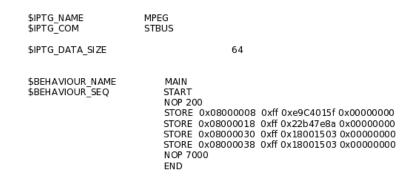

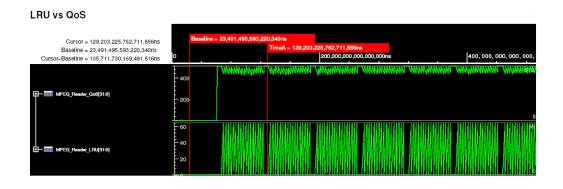

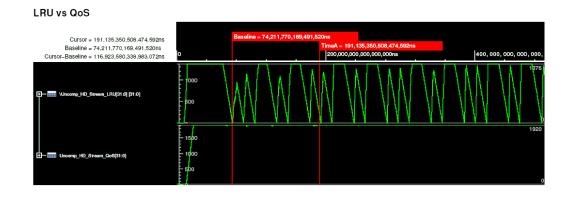

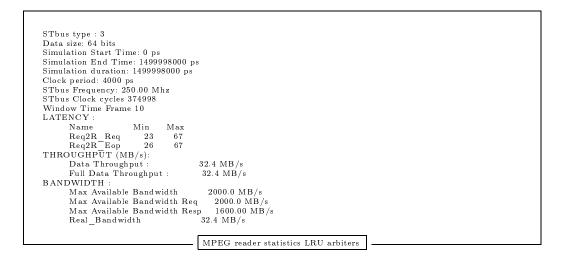

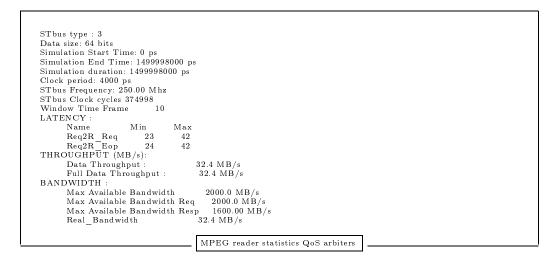

sous-systèmes (MPEG et Blitter) ont été modélisés en utilisant les générateurs de trafic IPTG développés par STMicroelectronics. Une première mesure a été effectuée sur l'occupation des FIFOs du maître MPEG qui exécute des lectures. En figure 2.14 une trace vcd de l'occupation des FIFO du maître MPEG en lecture est montrée, pour deux cas :

- Arbitrage « Least Recently Used » (LRU), qualité de service non intégrée.

- Qualité de service intégrée.

| LRU vs QoS                                                                                                               |                                                                                                                       |                          |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------|

| Cursor = 129,203,225,762,711,856ns<br>Baseline = 23,491,495,593,220,340ns<br>Cursor-Baseline = 105,711,730,169,491,516ns | Baseline = 23,491,495,593,220,340 ns<br>TimeA = 129,203,225,782,711,856 ns<br>200,000,000,000,000,000,000,000,000,000 | 400, 000, 000, 000, 000, |

| D- MPEG_Paeder_Ood[31:0]                                                                                                 | - 200<br>- 200                                                                                                        | o<br>o                   |

| D- MPEG_Reader_LRU(31:0)                                                                                                 |                                                                                                                       |                          |

Fig. 2.14: Effet de l'arbitrage sur l'occupation des FIFOs des maîtres MPEG

Un but impératif dans la conception d'une interconnexion consiste à éviter une situation de « famine » d'une IP pour ce qui concerne les transactions à traiter. C'est le cas d'une FIFO dont l'occupation croise l'axe X (confronter figure 2.14). Si la FIFO est vide, ce qui arrive régulièrement avec un arbitrage LRU qui ne garantit pas un débit correct, l'IP ne peut avancer dans le traitement des données. Ceci s'avère être un problème grave, signifiant que l'interconnexion ne procure pas le débit nécessaire.

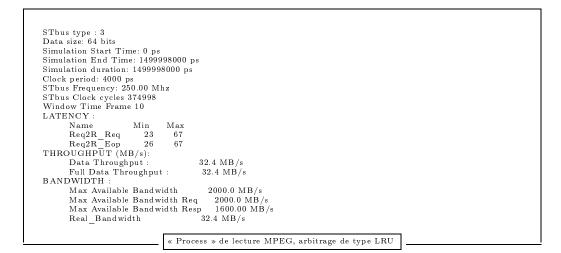

Il existe une réponse à ce problème; cette réponse, implémentée en STNoC<sup>™</sup>, est dénommée qualité de service. Les détails d'implémentation ne peuvent être dévoilés pour des raisons de confidentialité. Par contre, la figure 2.14 montre très clairement que lorsque STNoC<sup>™</sup> intègre des arbitres capables de garantir une qualité de service nécessaire, le comportement de la FIFO, et du coup de l'application, est bien meilleur. Non seulement l'occupation ne descend jamais à zero, mais elle reste à des valeurs toujours élevées, ce qui garantit un très bon fonctionnement en toutes conditions. En ce qui concerne la comparaison des latences sur le réseau, STNoC<sup>™</sup> utilise un outil dénommé SysProbe. Les latences peuvent être mesurées de différentes façons (de la requête à l'acquittement, de la requête à la réponse), et les résultats sont disponibles en format texte.

Ce fichier de texte produit par SysProbe montre les champs les plus intéressants des statistiques mesurées sur  $STNoC^{TM}$ . Des valeurs sont obtenues statiquement, d'autres dynamiquement. Dans cet exemple le débit demandé par le maître MPEG est d'environ 30 Moctets par seconde. Le débit disponible en réponse est limité par la sérialisation des transactions en « flits » (FLow control digITS).

Les « flits » de header (en-tête) ne sont pas comptés comme débit disponible parce qu'ils transportent des informations de contrôle. Les opérations sont toutes des lectures de 32 octets, sur un chemin de données de 64 bits, ce qui fait qu'un cinquième de la bande disponible est utilisé pour envoyer des contrôles (un paquet de réponse est composé de cinq « flits » : 1 de *header* + 4 de *payload* 4x8=32 octets). En intégrant le mécanisme de qualité de service, le réseau permet de limiter les latences (voir les statistiques qui suivent).

| STbus type : 3<br>Data size: 64 bits<br>Simulation Start Time: 0 ps<br>Simulation End Time: 1499998000 ps<br>Simulation duration: 1499998000 ps<br>Clock period: 4000 ps<br>STbus Frequency: 250.00 Mhz<br>STbus Clock cycles 374998<br>Window Time Frame 10<br>LATENCY:<br>Name Min Max<br>Req2R_Req 23 42<br>Req2R_Eop 24 42<br>THROUGHPUT (MB/s):<br>Data Throughput : 32.4 MB/s<br>Full Data Throughput : 32.4 MB/s<br>BANDWIDTH :<br>Max Available Bandwidth 2000.0 MB/s |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data size: 64 bits<br>Simulation Start Time: 0 ps<br>Simulation End Time: 1499998000 ps<br>Simulation duration: 1499998000 ps<br>Clock period: 4000 ps<br>STbus Frequency: 250.00 Mhz<br>STbus Clock cycles 374998<br>Window Time Frame 10<br>LATENCY :<br>Name Min Max<br>Req2R_Req 23 42<br>Req2R_Eop 24 42<br>THROUGHPUT (MB/s):<br>Data Throughput : 32.4 MB/s<br>Full Data Throughput : 32.4 MB/s<br>BANDWIDTH :<br>Max Available Bandwidth 2000.0 MB/s                  |

| Simulation End Time: 1499998000 ps<br>Simulation duration: 1499998000 ps<br>Clock period: 4000 ps<br>STbus Frequency: 250.00 Mhz<br>STbus Clock cycles 374998<br>Window Time Frame 10<br>LATENCY:<br>Name Min Max<br>Req2R_Req 23 42<br>Req2R_Eop 24 42<br>THROUGHPUT (MB/s):<br>Data Throughput: 32.4 MB/s<br>Full Data Throughput: 32.4 MB/s<br>BANDWIDTH :<br>Max Available Bandwidth 2000.0 MB/s                                                                          |

| Simulation duration: 1499998000 ps<br>Clock period: 4000 ps<br>STbus Frequency: 250.00 Mhz<br>STbus Clock cycles 374998<br>Window Time Frame 10<br>LATENCY:<br>Name Min Max<br>Req2R_Req 23 42<br>Req2R_Eop 24 42<br>THROUGHPUT (MB/s):<br>Data Throughput: 32.4 MB/s<br>Full Data Throughput: 32.4 MB/s<br>BANDWIDTH :<br>Max Available Bandwidth 2000.0 MB/s                                                                                                                |

| Clock period: 4000 ps<br>STbus Frequency: 250.00 Mhz<br>STbus Clock cycles 374998<br>Window Time Frame 10<br>LATENCY :<br>Name Min Max<br>Req2R_Req 23 42<br>Req2R_Eop 24 42<br>THROUGHPUT (MB/s):<br>Data Throughput : 32.4 MB/s<br>Full Data Throughput : 32.4 MB/s<br>BANDWIDTH :<br>Max Available Bandwidth 2000.0 MB/s                                                                                                                                                   |

| STbus Frequency: 250.00 Mhz<br>STbus Clock cycles 374998<br>Window Time Frame 10<br>LATENCY:<br>Name Min Max<br>Req2R_Req 23 42<br>Req2R_Eop 24 42<br>THROUGHPUT (MB/s):<br>Data Throughput : 32.4 MB/s<br>Full Data Throughput : 32.4 MB/s<br>BANDWIDTH :<br>Max Available Bandwidth 2000.0 MB/s                                                                                                                                                                             |

| STbus Clock cycles 374998<br>Window Time Frame 10<br>LATENCY :<br>Name Min Max<br>Req2R_Req 23 42<br>Req2R_Eop 24 42<br>THROUGHPUT (MB/s):<br>Data Throughput : 32.4 MB/s<br>Full Data Throughput : 32.4 MB/s<br>BANDWIDTH :<br>Max Available Bandwidth 2000.0 MB/s                                                                                                                                                                                                           |

| Window Time Frame 10<br>LATENCY :<br>Name Min Max<br>Req2R_Req 23 42<br>Req2R_Eop 24 42<br>THROUGHPUT (MB/s):<br>Data Throughput : 32.4 MB/s<br>Full Data Throughput : 32.4 MB/s<br>BANDWIDTH :<br>Max Available Bandwidth 2000.0 MB/s                                                                                                                                                                                                                                        |

| LATENCY :<br>Name Min Max<br>Req2R_Req 23 42<br>Req2R_Eop 24 42<br>THROUGHPUT (MB/s):<br>Data Throughput : 32.4 MB/s<br>Full Data Throughput : 32.4 MB/s<br>BANDWIDTH :<br>Max Available Bandwidth 2000.0 MB/s                                                                                                                                                                                                                                                                |

| NameMinMaxReq2R_Req2342Req2R_Eop2442THROUGHPUT (MB/s):                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Req2R_Req         23         42           Req2R_Eop         24         42           THROUGHPUT (MB/s):             Data Throughput :         32.4 MB/s           Full Data Throughput :         32.4 MB/s           BANDWIDTH :         32.4 MB/s           Max Available Bandwidth         2000.0 MB/s                                                                                                                                                                       |

| Req2R_Eop 24 42<br>THROUGHPUT (MB/s):<br>Data Throughput : 32.4 MB/s<br>Full Data Throughput : 32.4 MB/s<br>BANDWIDTH :<br>Max Available Bandwidth 2000.0 MB/s                                                                                                                                                                                                                                                                                                                |

| THROUGHPUT (MB/s):<br>Data Throughput : 32.4 MB/s<br>Full Data Throughput : 32.4 MB/s<br>BANDWIDTH :<br>Max Available Bandwidth 2000.0 MB/s                                                                                                                                                                                                                                                                                                                                   |

| Data Throughput : 32.4 MB/s<br>Full Data Throughput : 32.4 MB/s<br>BANDWIDTH :<br>Max Available Bandwidth 2000.0 MB/s                                                                                                                                                                                                                                                                                                                                                         |

| Full Data Throughput : 32.4 MB/s<br>BANDWIDTH :<br>Max Available Bandwidth 2000.0 MB/s                                                                                                                                                                                                                                                                                                                                                                                        |

| BANDWIDTH :<br>Max Available Bandwidth 2000.0 MB/s                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Max Available Bandwidth 2000.0 MB/s                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Max Available Bandwidth Req 2000.0 MB/s                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Max Available Bandwidth Resp 1600.00 MB/s                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Real_Bandwidth 32.4 MB/s                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| « Process » de lecture MPEG, qualité de service intégrée                                                                                                                                                                                                                                                                                                                                                                                                                      |

La latence maximum est un paramètre fondamental pour les IPs, car les FIFOs internes sont dimensionnées en fonction de la latence maximum de l'interconnexion afin d'éviter une situation de « famine » pour le traitement des données. La qualité de service, en diminuant la latence maximum (de 67 à 42 cycles), améliore d'une façon très importante le comportement des IPs, y compris les besoins en surface.

# 2.5 Conclusion

Ce chapitre a permis d'introduire les principaux concepts et contributions de cette thèse. La partie restante du document (en anglais) détaille les travaux, en approfondissant tous les concepts mentionnés dans ce chapitre concernant la modélisation, la conception et l'étude de STNoC, la nouvelle technologie d'interconnexion développée au sein de STMicroelectronics.

# SoCs interconnections

# 3.1 Introduction

This chapter provides an in-depth outlook over existing interconnection architectures. First, networks-on-chip motivations are highlighted, with a clear focus on both technology and system level design issues. Secondly and finally, a state of the art section describes interconnection mediums deployed in current system-on-chip solutions, with a fleeting wink to first motivating networks on-chip examples just appearing in real designs.

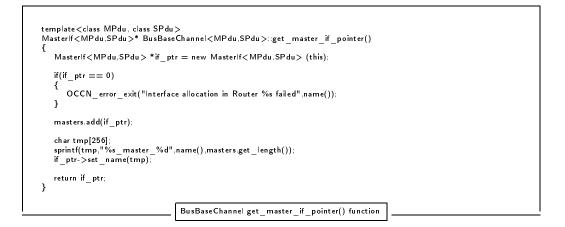

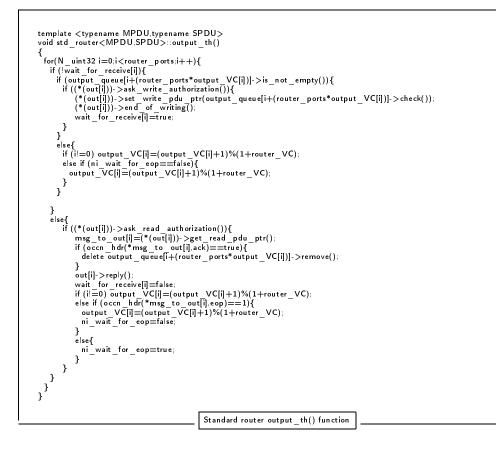

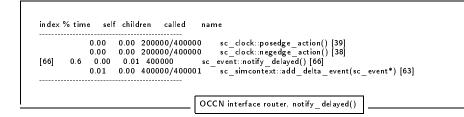

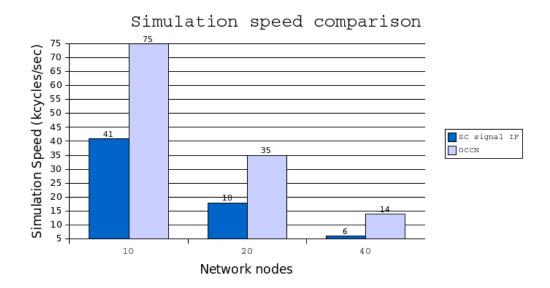

## **3.2** Networks on-chip motivations