# Contribution à la conception de circuits intégrés sécurisés : l'alternative asynchrone

Ghislain Fraidy Bouesse

#### ▶ To cite this version:

Ghislain Fraidy Bouesse. Contribution à la conception de circuits intégrés sécurisés: l'alternative asynchrone. Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble - INPG, 2005. Français. NNT: . tel-00011457v2

## HAL Id: tel-00011457 https://theses.hal.science/tel-00011457v2

Submitted on 25 Jan 2006

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

| N° a | attri | bue | e pa | ır la | ı bi | blic | othe | èque |

|------|-------|-----|------|-------|------|------|------|------|

| /_   | _/_   | _/_ | _/_  | _/_   | _/_  | _/_  | _/_  | _/   |

#### **THESE**

pour obtenir le grade de

#### **DOCTEUR DE l'INPG**

Spécialité : Microélectronique

préparée au laboratoire TIMA dans le cadre de l'Ecole Doctorale d'« Electronique, Electrotechnique, Automatique, Télécommunications, Signal »

présentée et soutenue publiquement

par Ghislain Fraidy BOUESSE

Le 1 décembre 2005

Titre:

# CONTRIBUTION A LA CONCEPTION DE CIRCUITS INTEGRES SECURISES : L'ALTERNATIVE ASYNCHRONE

Directeur de Thèse : Marc Renaudin Codirecteur : Gilles Sicard

#### **JURY**

M. Yassine Lakhnech , Président

M. Jean Jacques Quisquater , Rapporteur

M. Lionel Torres , Rapporteur

M. Marc Renaudin , Directeur de

M. Marc Renaudin , Directeur de thèse M. Gilles Sicard , Codirecteur de thèse

M. Alain Merle , Examinateur

A mon père A ma mère

#### REMERCIEMENTS

Les travaux de cette thèse ont été réalisés au sein du laboratoire TIMA, sur le site Viallet de l'Institut National Polytechnique de Grenoble. Que son directeur M. Bernard Courtois trouve ici tous mes remerciements pour son accueil au sein de son laboratoire.

Toute ma gratitude est adressée à Marc Renaudin, mon Directeur de thèse, professeur à l'Institut National Polytechnique de Grenoble, qui a accepté de me prendre comme stagiaire DEA (2000 – 2001) pour finalement me prendre en thèse en 2002. Tous mes remerciements pour ces belles années de stage et de thèse.

Je tiens à exprimer toute ma profonde reconnaissance à mon co-encadrant Gilles Sicard, maître de conférence à l'université Joseph Fourier, pour sa patience, ses conseils, ses corrections, de son soutien moral et surtout de la semaine de folie que nous avons passée avant ma soutenance.

Je voudrais remercier vivement les membres de mon jury de thèse :

- M. Lionel Torres, professeur à l'université de Montpellier II, pour avoir accepté de rapporter ma thèse et de la corriger.

- M. Jean Jacques Quisquater, professeur à l'université Catholique de Louvain, pour m'avoir fait l'honneur de participer à mon jury de thèse en tant que rapporteur.

- M. Yassine Lakhnech, professeur à l'université Joseph Fourier, pour m'avoir fait l'honneur d'être le président de mon jury de thèse.

- M. Alain Merle, responsable du Centre d'Evaluation des Technologies de l'Information (CESTI-LETI), pour avoir accepté d'être examinateur de ma thèse.

Je tiens aussi à remercier Laurent Fesquet, maître de conférence à l'Institut National Polytechnique de Grenoble, pour ses encouragements. Merci Laurent pour toutes ces heures d'enseignement.

A Alain Guyot, maître de conférence à l'Institut Polytechnique de Grenoble, j'adresse mes remerciements pour ses nombreux conseils et surtout pour m'avoir présenté à Marc.

Je souhaite remercier chaleureusement tous les membres (ex-membres) de l'équipe CIS du laboratoire TIMA. D'abords les anciens avec JB pour sa sagesse et surtout pour toutes les corrections apportées sur ce manuscrit. A frère Bob pour sa disponibilité, Dhanistha pour m'avoir appris à utiliser « design analyzer », Manu et Kamel pour m'avoir toujours mis dans l'œil du cyclone, Momo pour ses délires, Jérôme pour ces aventures et Amine pour sa discrétion. Les nouveaux en commençant par Arnaud Baixas pour ses cours de Salsa autour des FPGAs, Caroline Biasi pour son éternel beau sourire, João mon prof. Brésilien de snowboard, Fabien le meneur d'hommes, Bertrand et Yannick mes guides d'Australie, David pour les repas mexicains, Cédric pour sa simplicité, Aurélien pour sa gentillesse, Salim qui me rappelait mes 5 ans passés en Algérie, Yann pour son franc parler et pour son aide en programmation, Estelle pour son écoute, nos longues conversations et surtout pour son soutien moral et Isabelle pour l'ambiance et sa gentillesse. Très gros merci à Sophie pour tous ces circuits que nous avons pus envoyer dans les temps et surtout pour ce magnifique pot de thèse fait avec la petite mexicaine Livier. A Nico et ses belles photos, Adrien pour notre virée à Toulouse, Greg pour toutes ses soirées, à Philippe M. compagnon de bureau pendant une petite mais très riche période.

Je ne saurais oublier Damien (le Canadien), Yanick (le petit), Greg (la ciboule), Seb, Fabrice, Emeline, Clarisse, Patrick, pour toutes ces soirées, dînés, restaurants, sorties de ski et mariages toujours bien arrosés. Toute ma reconnaissance à Eleftherios pour son temps, ses conseils, son assistance et surtout pour ce magnifique voyage effectué en Grèce.

Je voudrais également remercier les administrateurs du CIME, Alexandre Chagoya, Robin Rolland et Bernard Bosc, et tout le personnel administratif du laboratoire TIMA. Tous mes remerciements à Kholdoun Torki pour son aide et à Jean François Paillotin.

Je tiens également à dire merci aux membres du CCDS, du CCREG et à mes amis qui ont pris la peine de venir assister à ma soutenance et tout particulièrement à Marlene L.

Je souhaite remercier également toutes les personnes que j'ai rencontrées dans les différents projets de recherche qui ont contribué à valoriser ce travail, à Edith Beigne et Bruno Robisson du CEA-LETI, à Jacques Sonzogni, Solenn Prevost et Pierre Yvan Liardet de STMicroelectronics Rousset, à Carine Raynaud, Jean Christophe Courrege et Benoît Feix du CESTI-THALES et à Fabien Germain de la SGDN.

Je remercie énormément ma famille, à mon père et à ma mère, à mon oncle (Nguba Martial) qui a su croire en moi, à mes frères et sœurs et particulièrement à Ya Ngoma, Ya Solange et Ya Willy présent le jour de ma soutenance et Pat D. qui a su m'accueillir à Grenoble. Au père Hiss pour son soutien indéfectible.

Une pensée particulière à tous ceux qui de près ou de loin m'ont donné un jour ce petit rayon de soleil synonyme d'amour et de lumière par sa chaleur et son éclat.

### TABLE DES MATIÈRES

| INTRODUCTION GENERALE : CONTEXTE ET MOTIVATIONS                        | 1  |

|------------------------------------------------------------------------|----|

| CHAPITRE I                                                             |    |

| CRYPTANALYSE MATERIELLE: ATTAQUES PAR CANAUX CACHES                    |    |

| 1.1 Introduction                                                       | 7  |

| 1.2 La Cryptologie : Notion de Base et terminologie                    | 8  |

| 1.2.1 La Cryptographie                                                 | 8  |

| 1.2.1.1 Notion de Clé cryptographique                                  | 8  |

| 1.2.2 Cryptage symétrique                                              | 9  |

| 1.2.2.1 Le Standard de chiffrement de données : le <i>DES</i>          | 9  |

| 1.2.3 Cryptage Asymétrique                                             | 11 |

| 1.2.3.1 Le RSA                                                         | 11 |

| 1.3 Définition de la Cryptanalyse                                      | 12 |

| 1.4 La cryptanalyse dite théorique                                     | 14 |

| 1.4.1 La cryptanalyse linéaire                                         | 14 |

| 1.4.2 La cryptanalyse différentielle                                   | 14 |

| 1.5 La cryptanalyse dite logicielle                                    | 15 |

| 1.5.1 Le cheval de Troie                                               | 15 |

| 1.5.2 Attaque par débordement de pile (Buffer overflow)                | 15 |

| 1.6 La cryptanalyse matérielle                                         | 16 |

| 1.6.1 Les attaques intrusives                                          |    |

| 1.6.1.1 Attaque par reconstruction du layout                           |    |

| 1.6.1.2 Attaque par analyse sous pointes                               |    |

| 1.6.2 Les Attaques non intrusives                                      | 17 |

| 1.6.2.1 Les Attaques par injections de fautes                          | 17 |

| 1.6.2.1.1 Génération et modèles de fautes                              | 17 |

| 1.6.2.1.2 Exploitation des fautes                                      | 18 |

| 1.6.2.2 Les attaques par analyses des signaux compromettants           |    |

| 1.6.2.2.1 Les attaques temporelles                                     |    |

| 1.6.2.2.2 Les attaques électromagnétiques                              |    |

| 1.6.2.2.3 Les attaques en puissance ou attaques par analyse du courant |    |

| 1.7 Conclusion                                                         | 28 |

|     | HAPITRE II<br>ES ATTAQUES EN PUISSANCE : ETUDE ET ANALYSE                    | 29 |

|-----|------------------------------------------------------------------------------|----|

| 2.1 | Introduction                                                                 | 29 |

| 2.2 | 2 Mesures du courant                                                         | 29 |

| 2.3 | Attaque par simple analyse du courant                                        | 32 |

|     | Attaque par analyse différentielle du courant                                |    |

|     | 2.4.1 Analyse théorique de l'algorithme : la fonction de sélection           |    |

|     | 2.4.2 Collecte d'information : mesure et mémorisation des courbes de courant | 38 |

|     | 2.4.3 Analyse des corrélations.                                              | 38 |

| 2.5 | Attaque par collisions                                                       | 43 |

| 2.6 | 5 Attaque par corrélation                                                    | 45 |

| 2.7 | 7 Réalisation d'une attaque en puissance sur un cryptoprocesseur synchrone   | 47 |

|     | 2.7.1 Architecture et caractéristiques du circuit : Cryptoprocesseur DES     |    |

|     | 2.7.2 Analyse différentielle du cryptoprocesseur                             |    |

| 2.8 | 3 Conclusion                                                                 |    |

|     | Introduction                                                                 |    |

|     | 2 Analyse du profil de courant dans un circuit intégré                       |    |

|     | 3.2.1 Analyse du courant d'une porte inverseuse                              |    |

|     | 3.2.1.1 Effet de la rampe d'entrée                                           |    |

|     | 3.2.1.1.1 Les rampes rapides                                                 | 58 |

|     | 3.2.1.1.2 Les rampes lentes                                                  | 59 |

|     | 3.2.1.2 Effet du délai                                                       |    |

|     | 3.2.1.3 Effet de la capacité.                                                |    |

|     | 3.2.1.4 Effet des commutations en sortie                                     |    |

|     | 3.2.2 Analyse du courant des portes simples et complexes                     |    |

|     | 3.2.3 Analyse du courant dans un bloc.                                       |    |

| 2.2 | 3.2.4 Sensibilité électrique d'un bloc                                       |    |

| 3.3 | 3 La cryptanalyse matérielle : les contre-mesures                            |    |

|     | 3.3.1 Les contre-mesures contre les attaques invasives                       |    |

|     | 3.3.2 Les contre-mesures contre les attaques par injection de fautes         |    |

|     | 3.3.3 Les contre-mesures contre les attaque temporelles                      | 72 |

|     | 3.3.4 Les contre-mesures contre les attaques électromagnétiques                                            | 72 |

|-----|------------------------------------------------------------------------------------------------------------|----|

|     | 3.3.5 Les contre-mesures contre les attaques en puissance                                                  | 72 |

|     | 3.3.5.1 Les méthodes de masquage et de duplication                                                         | 73 |

|     | 3.3.5.2 Méthodes par injection de bruit                                                                    | 74 |

|     | 3.3.5.3 Les méthodes par lissage et uniformisation du profil de courant                                    | 76 |

| 3.4 | Conclusion                                                                                                 | 77 |

| LA  | IAPITRE IV<br>LOGIQUE ASYNCHRONE ET LA SECURITE MATERIELLE : EVALUA<br>RCUITS QUASI INSENSIBLES AUX DELAIS |    |

| 4.1 | Introduction                                                                                               | 79 |

| 4.2 | La logique asynchrone                                                                                      | 80 |

|     | 4.2.1 Les opérateurs asynchrones                                                                           | 80 |

|     | 4.2.2 Le contrôle local                                                                                    | 81 |

|     | 4.2.3 Protocole de communication.                                                                          |    |

|     | 4.2.4 Codage des données                                                                                   |    |

|     | 4.2.5 Signaux de fin de calcul                                                                             |    |

|     | 4.2.6 Les différentes classes de circuits asynchrones                                                      |    |

|     | 4.2.7 Les circuits Quasi Insensibles aux Délais (QDI)                                                      |    |

|     | 4.2.8 Les circuits micropipeline                                                                           |    |

|     | 4.2.9 La porte de Muller                                                                                   |    |

|     | 4.2.10 Conception des circuits asynchrones                                                                 |    |

| 43  | Les circuits asynchrones et les attaques non intrusives                                                    |    |

| т.Э | 4.3.1 Choix du type de circuit asynchrone                                                                  |    |

|     | 4.3.2 Les circuits QDI et les analyses en puissance                                                        |    |

|     | 4.3.2.1 Le Codage de données <i>en p parmi n</i>                                                           |    |

|     | 4.3.2.1 Le Codage de données <i>en p parmi n</i>                                                           |    |

|     | 4.3.2.3 Chemins de données équilibrés                                                                      |    |

| 4.4 | Evaluation de la logique asynchrone <i>QDI</i> : Cas d'un cryptoprocesseur asynchrone                      |    |

|     | 4.4.1 Architecture du cryptoprocesseur                                                                     |    |

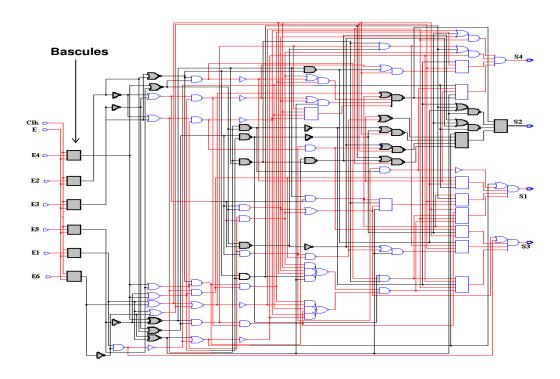

|     | 4.4.1.1 Le banc de registres                                                                               |    |

|     | 4.4.1.2 Les Interfaces                                                                                     |    |

|     | 4.4.1.3 le Bloc de chiffrement asynchrone                                                                  | 95 |

|     | 4.4.2 Caractéristiques des circuits                                                                        | 96 |

|     | 4.4.3 Résultats des attaques en puissance                                                                  | 98 |

| 4.5 Conclusion                                                                                 | 101        |

|------------------------------------------------------------------------------------------------|------------|

| CHAPITRE V<br>ANALYSE FORMELLE DES CIRCUITS QUASI INSENSIBLES AUX DEI                          | LAIS 103   |

| 5.1 Introduction                                                                               | 104        |

| 5.2 Représentation formelle des circuits asynchrones <i>QDI</i>                                | 104        |

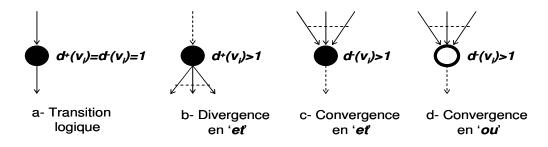

| 5.2.1 Graphe orienté d'un circuit asynchrone <i>QDI</i>                                        | 104        |

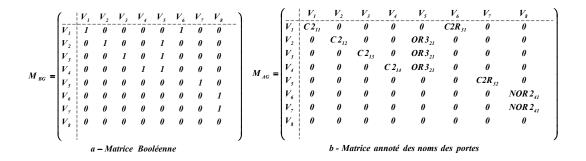

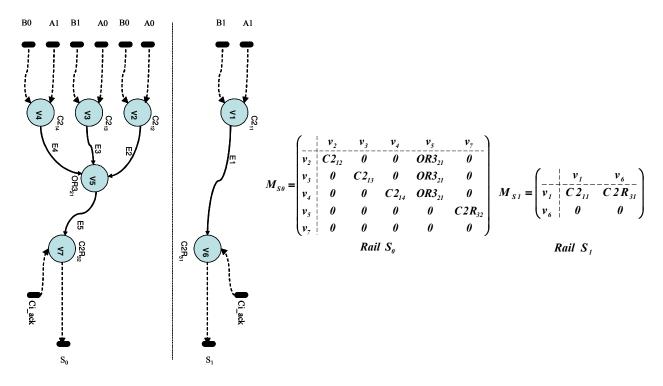

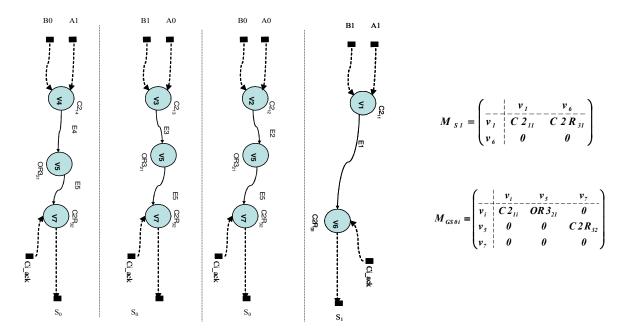

| 5.2.1.1 Matrice d'adjacence                                                                    | 106        |

| 5.3 Analyse au niveau logique : symétrie des chemins de données                                | 107        |

| 5.3.1 Notion de chemin d'exécution                                                             | 108        |

| 5.3.2 Les graphes isomorphes                                                                   | 111        |

| 5.4 Analyses au niveau électrique : Identification des fuites d'informations                   | 112        |

| 5.4.1 Modèle électrique d'un circuit asynchrone <i>QDI</i>                                     | 113        |

| 5.4.2 Application de l'attaque DPA sur le modèle formel                                        | 115        |

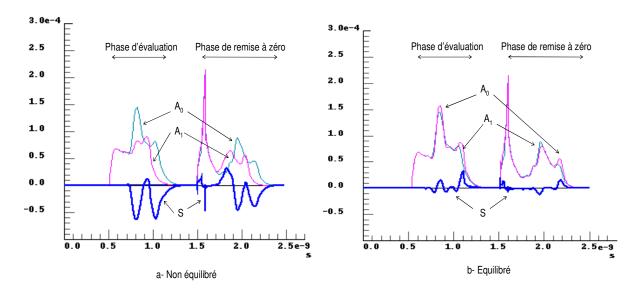

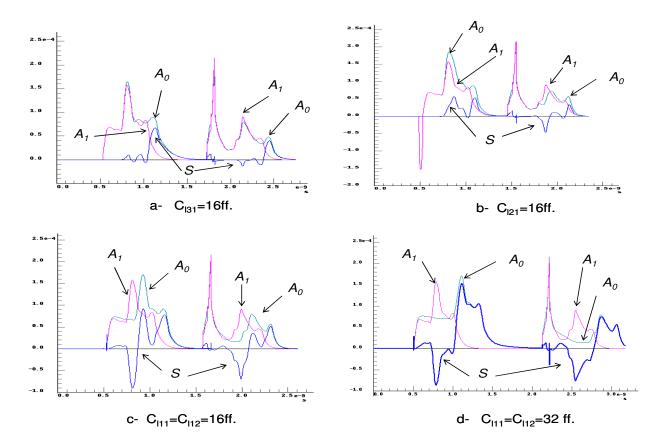

| 5.4.3 Validation par simulation électrique                                                     | 116        |

| 5.5 Conclusion                                                                                 | 118        |

| CHAPITRE VI PROTECTION DES CIRCUITS QUASI INSENSIBLES AUX DELAIS : FI CONCEPTION SECURISE      |            |

| 6.1 Introduction                                                                               | 121        |

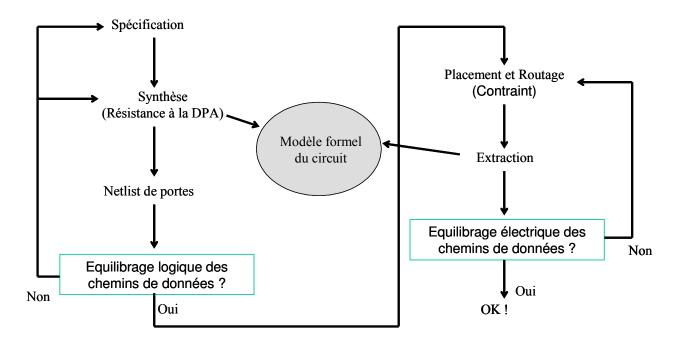

| 6.2 Flot de conception sécurisé des circuits <i>QDI</i>                                        | 122        |

| 6.2.1 Critère d'évaluation de la dissymétrie électrique                                        | 123        |

| 6.2.2 Placement routage contraint                                                              | 123        |

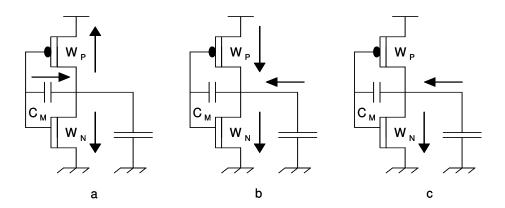

| 6.2.3 Cellules asynchrones                                                                     | 124        |

| 6.3 Les cryptoprocesseurs asynchrones AES                                                      | 126        |

| 6.3.1 Le banc de registres et les interfaces                                                   | 127        |

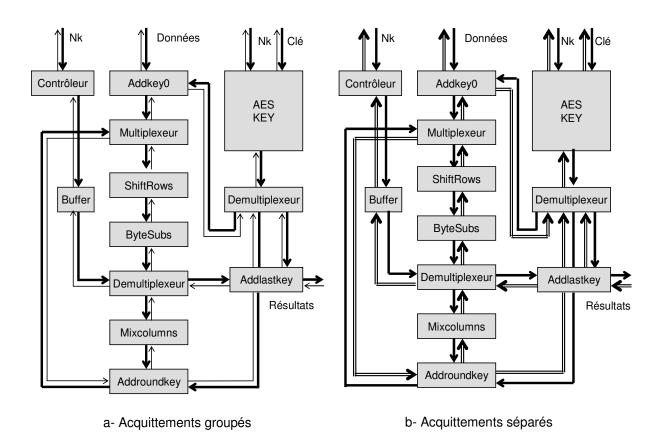

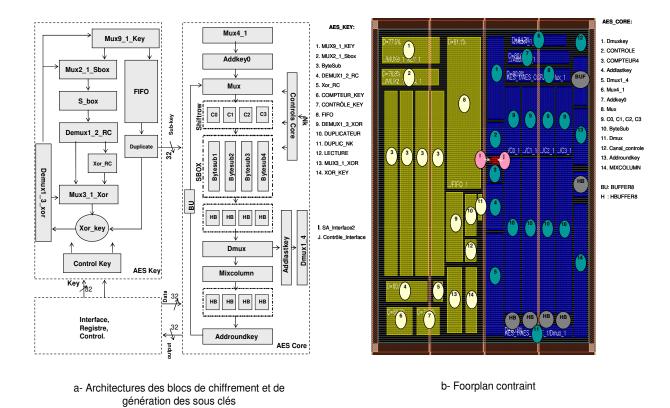

| 6.3.2 Le bloc de chiffrement ( <i>AES_core</i> ) et le bloc de génération des clés ( <i>AB</i> | ES key)128 |

| 6.3.3 Caractéristiques des circuits                                                            |            |

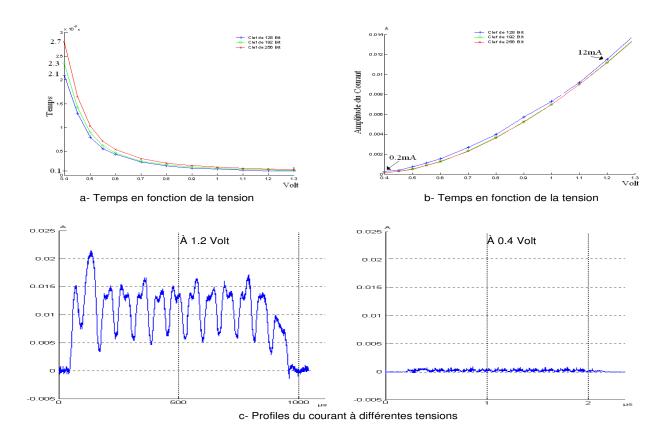

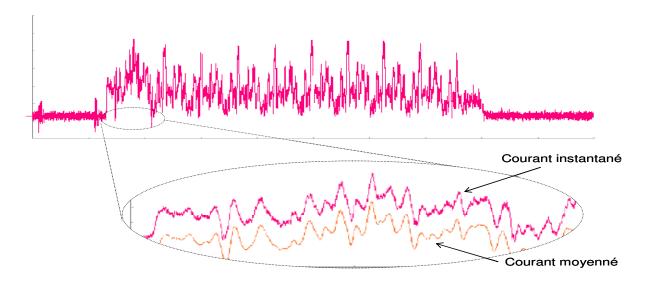

| 6.3.4 Résultats des analyses en courant                                                        |            |

| 6.4 Conclusion                                                                                 |            |

| CHAPITRE VII<br>PROTECTION DES CIRCUITS QUASI INSENSIBLES AUX DELAIS :             |              |

|------------------------------------------------------------------------------------|--------------|

| CONTRE-MESURES                                                                     | 139          |

| 7.1 Introduction                                                                   | 139          |

| 7.2 Méthode par transpositions aléatoires des chemins de données                   | 140          |

| 7.2.1 Transpositions aléatoires des chemins de données : Définition                | 140          |

| 7.2.2 Application de la DPA sur le modèle formel avec transpositions des chemins d | e données143 |

| 7.2.3 La fonction de transposition des chemins de données                          | 144          |

| 7.2.4 Discussion                                                                   | 145          |

| 7.2.5 Etude de cas : le cryptoprocesseur asynchrone DES                            | 146          |

| 7.2.6 Validation par simulations électriques                                       | 149          |

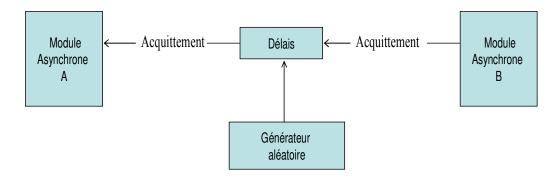

| 7.3 Méthode par décalage aléatoire des signaux d'acquittements                     | 152          |

| 7.3.1 Les signaux d'acquittements                                                  | 152          |

| 7.3.2 Décalage aléatoire des signaux d'acquittements : Analyses formelles          | 153          |

| 7.3.3 Discussion                                                                   | 155          |

| 7.3.4 Réduction des émissions electromagnétiques                                   | 158          |

| 7.3.4.1 Résultats des analyses : simulations électriques                           | 159          |

| 7.3.5 Etude de cas : cryptoprocesseur <i>DES</i> en logique asynchrone <i>QDI</i>  | 161          |

| 7.4 Conclusion                                                                     | 164          |

| CONCLUSION ET PERSPECTIVES                                                         | 165          |

| BIBLIOGRAHIE                                                                       | 169          |

| BIBLIOGRAHIE DE L'AUTEUR                                                           | 177          |

#### LISTES DES FIGURES

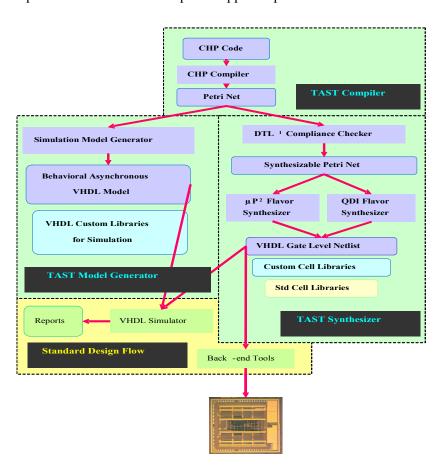

| Figure 1 : Flots de conception supportés par l'environnement <i>TAST</i> .                                                                                                                          | 3           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

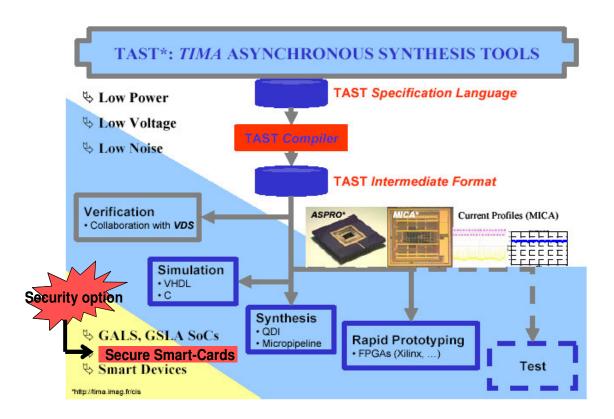

| Figure 2 : Le projet <i>TAST</i>                                                                                                                                                                    | 4           |

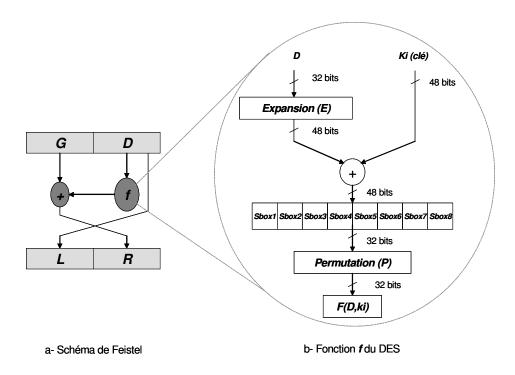

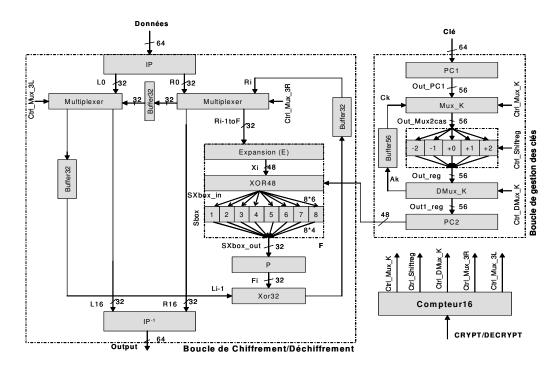

| Figure 1.1 : Schéma de Feistel et la fonction f du Standard de chiffrement de données                                                                                                               | 10          |

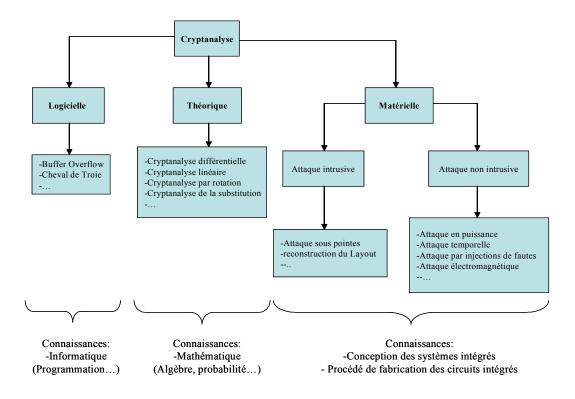

| Figure 1.2 : Les attaques cryptanalytiques et les compétences requises                                                                                                                              | 13          |

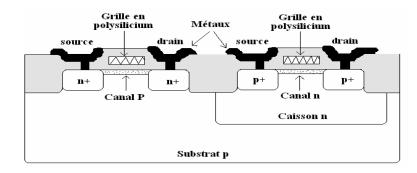

| Figure 1.3 : Vue en coupe des transistors <i>CMOS</i> de type <i>N</i> et <i>P</i> sur un substrat                                                                                                  | 25          |

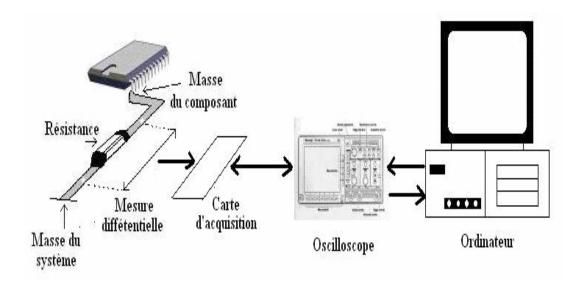

| Figure 2.1 : Schéma de mesure et d'acquisition automatique des courbes de courant                                                                                                                   | 30          |

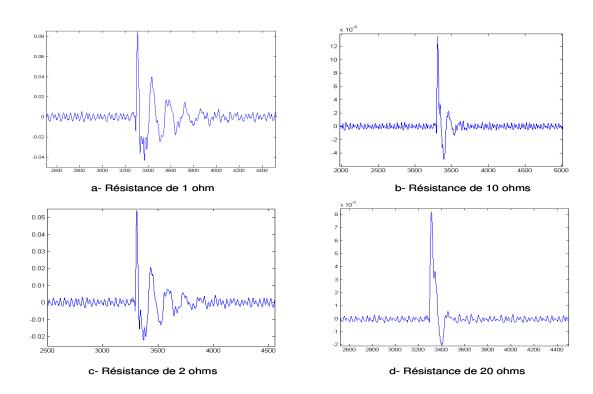

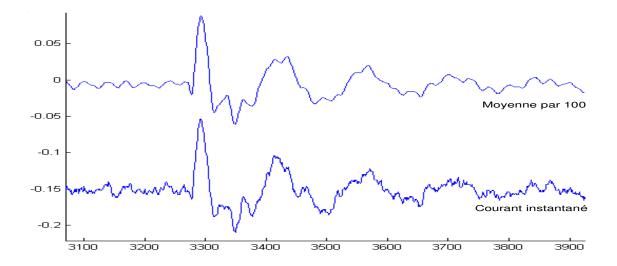

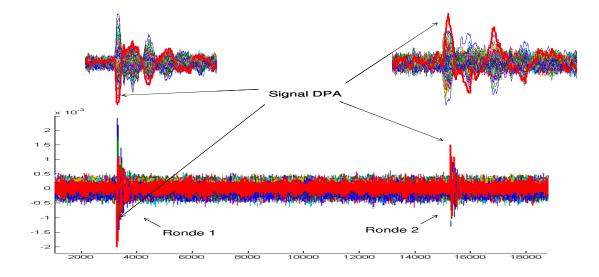

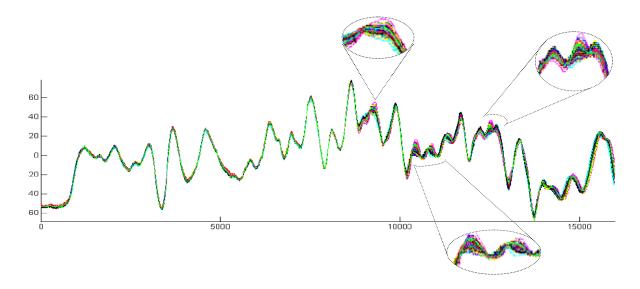

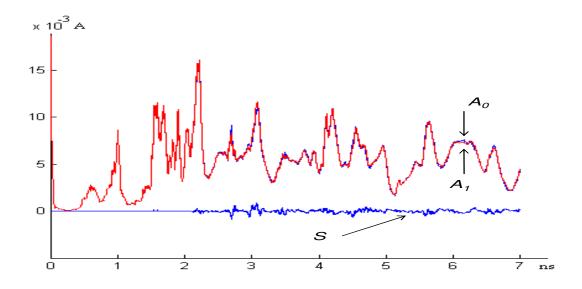

| Figure 2.2 : Mesures différentielles de la première itération de l'algorithme du <i>DES</i> sur un cryptoprocesseur synchrone. Courbes de courant moyennées par 100                                 | 31          |

| Figure 2.3 : Courbe de courant réalisée par <i>GEMPLUS</i> sur une implémentation <i>RSA</i> utilisant l binaire présentée au chapitre I (cf. § 1.6.2.2.1)                                          |             |

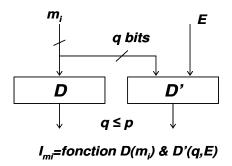

| Figure 2.4: Analyse des dépendances du courant consommé dans une architecture en fonction d'entrées $m_i$                                                                                           |             |

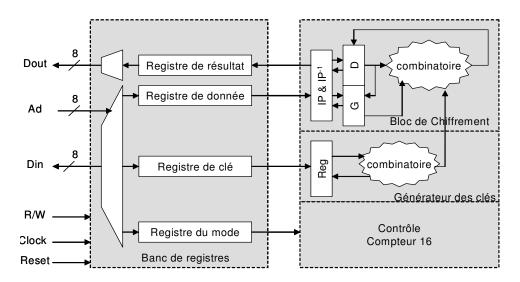

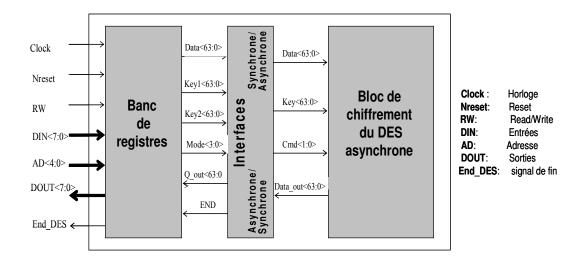

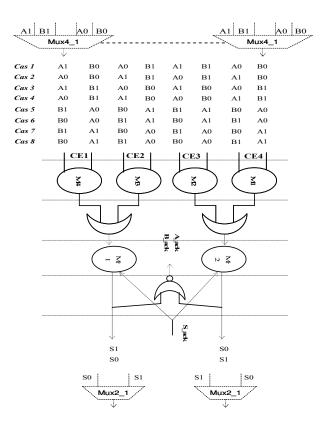

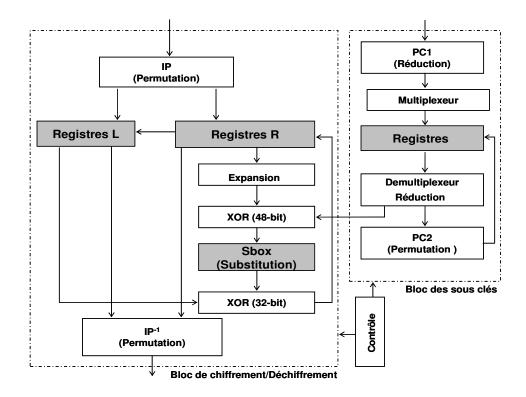

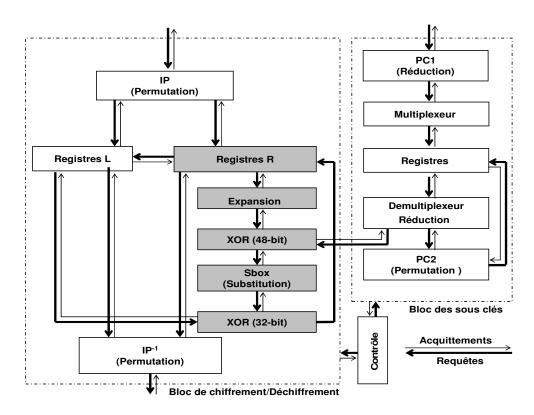

| Figure 2.5 : Architecture du cryptoprocesseur synchrone DES                                                                                                                                         | 47          |

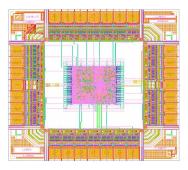

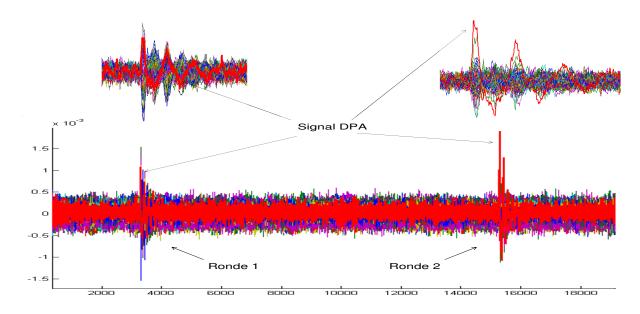

| Figure 2.6 : Layout du cryptoprocesseur Surface du cœur: 370μmx370μm, Surface avec plots 1050μmx1050μm                                                                                              |             |

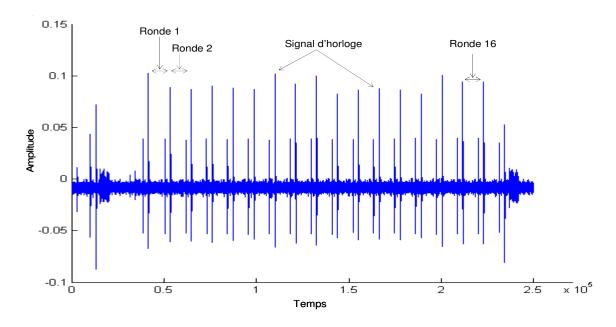

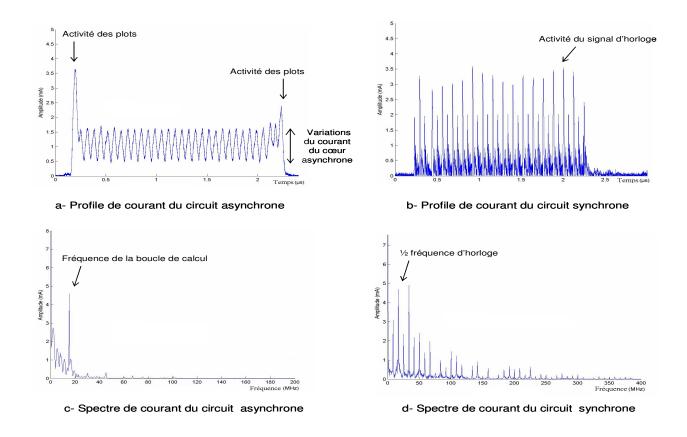

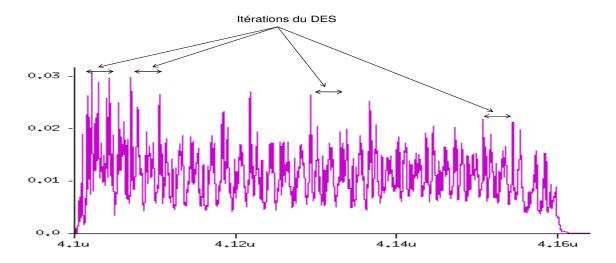

| Figure 2.7 : Profil de courant du cryptoprocesseur synchrone <i>DES</i>                                                                                                                             | 49          |

| Figure 2.8 : Courant moyennée et instantané de la première itération du cryptoprocesseur sync                                                                                                       | hrone 50    |

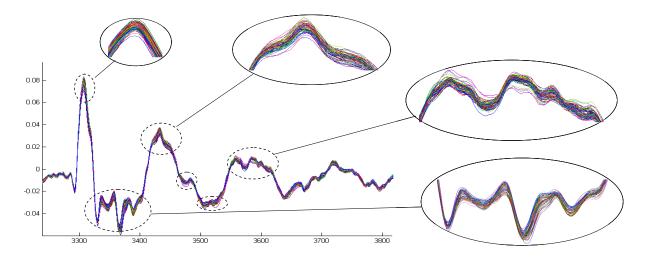

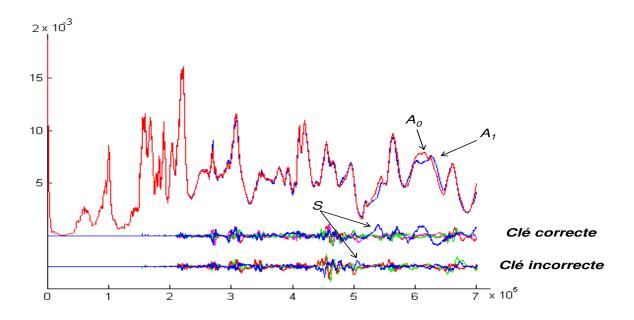

| Figure 2.9 : Analyse des corrélations entre les données manipulées et les courbes de courant                                                                                                        | 50          |

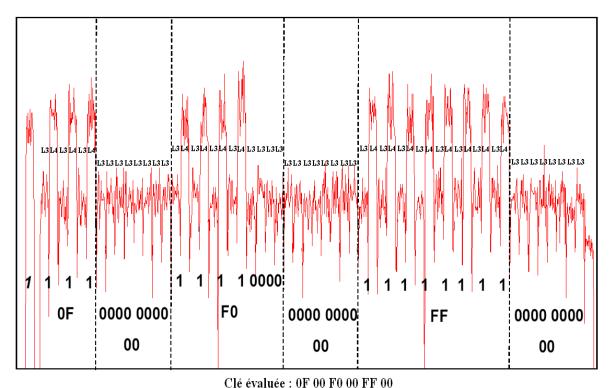

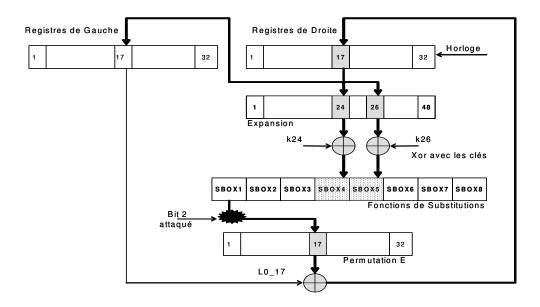

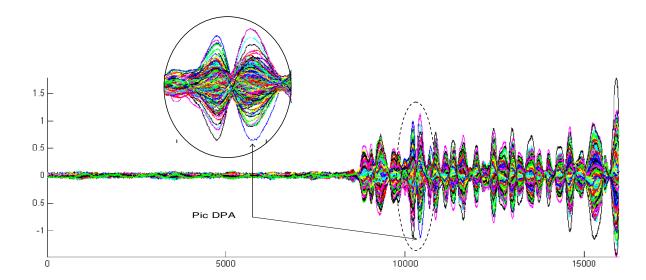

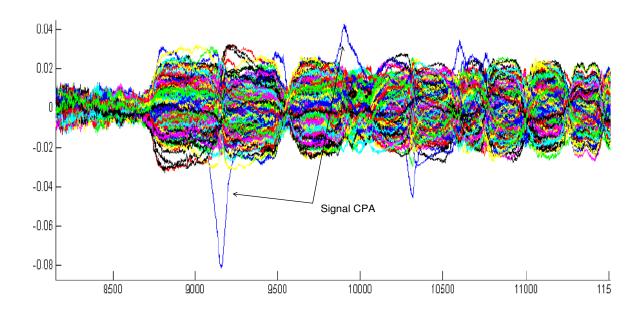

| Figure 2.10 : Signal <i>DPA</i> sur le bit 2 en sortie de la <i>SBOX1</i>                                                                                                                           | 51          |

| Figure 2.11 : Chemin de données du bit 2 en sortie de la SBOX1                                                                                                                                      | 52          |

| Figure 2.12 : Signal <i>DPA</i> sur le bit 3 en sortie de la <i>SBOX1</i>                                                                                                                           | 52          |

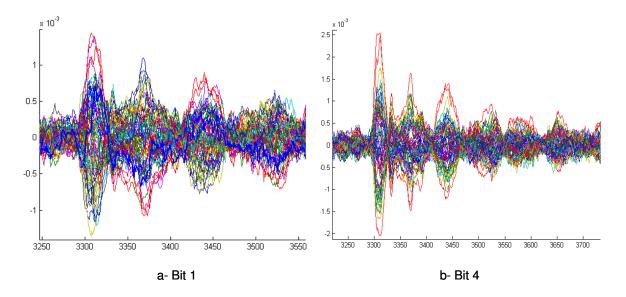

| Figure 2.13 : Signaux <i>DPA</i> sur les bits 1 et 4 en sortie de la <i>SBOX1</i>                                                                                                                   | 53          |

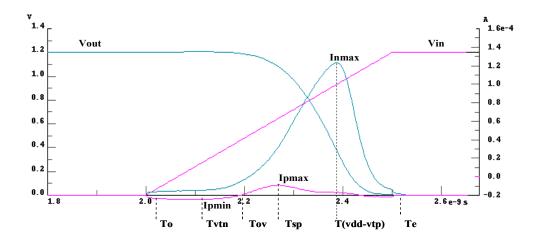

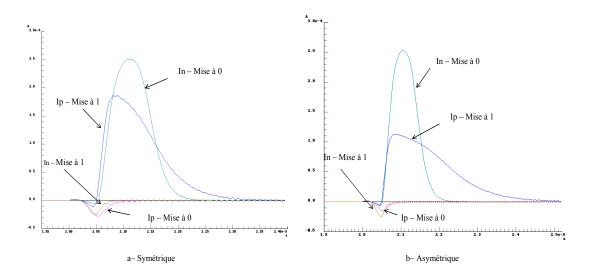

| Figure 3.1 : Tensions d'entrée/sortie et courants des transistors <i>P</i> et <i>N</i> dans un inverseur <i>CMO</i> asymétrique (k=Wp/Wn=1,79) sur front montant. La capacité de charge est de 16fl |             |

| Figure 3.2 : Zones de fonctionnement de la porte inverseuse. a- correspond à la zone surtensio de cour circuit et c- correspond à la zone de décharge                                               |             |

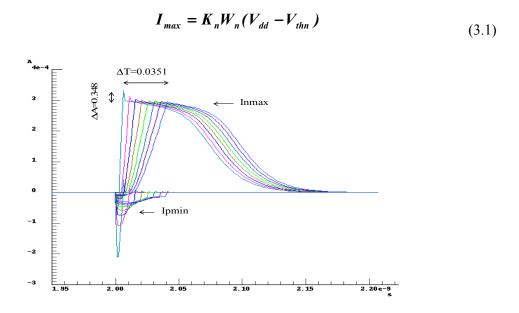

| Figure 3.3 : Effet d'une rampe rapide sur le profil de courant. L'intervalle de variation de la ra $_{\rm que} 5ps \le \tau_{\rm in} \le 40ps$                                                      | mpe est tel |

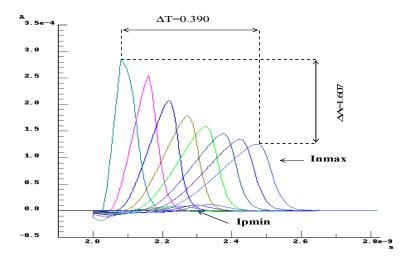

| Figure 3.4 : Effet d'une rampe lente sur le profil de courant. L'intervalle de variation de la rampe $80 \text{ ps} < \pi < 160 \text{ ps}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| que $80 ps \le \tau_{in} \le 160 ps$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 60 |

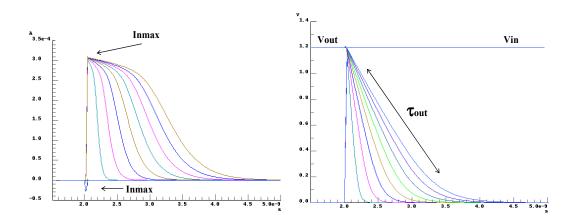

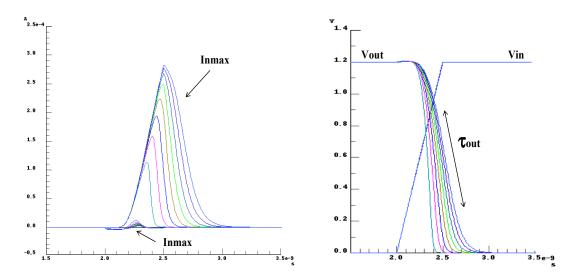

| Figure 3.5 : Effet de la capacité de charge sur le profil de courant et sur la rampe de sortie dans le                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| des rampes rapides ( $\tau_{in} = 40 ps$ ) pour C: $80 fF \le C \le 320 fF$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 61 |

| Figure 3.6 : Effet de la capacité de charge sur le profil de courant et sur la rampe de sortie dans le des rampes lentes ( $\tau_{in} = 50 ns$ ) pour C : $10 fF \le C \le 80 fF$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| Figure 3.7 : Profils des courants des transistors $P$ et $N$ des portes inverseuses symétrique et asymétrique $P$ and $P$ and $P$ and $P$ are $P$ and $P$ and $P$ are $P$ are $P$ and $P$ are | _  |

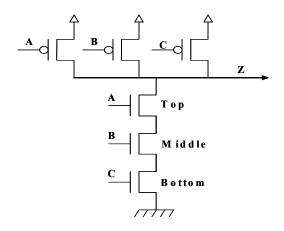

| Figure 3.8 : Schématique d'une porte <i>CMOS NAND</i> à 3 entrées                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

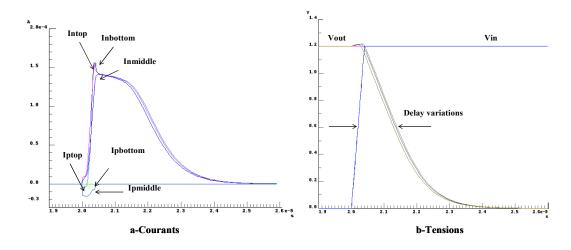

| Figure 3.9 : Profils de courant des transistors en série d'une porte <i>NAND</i> à 3 entrées et variations dans le domaine des rampes rapides                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

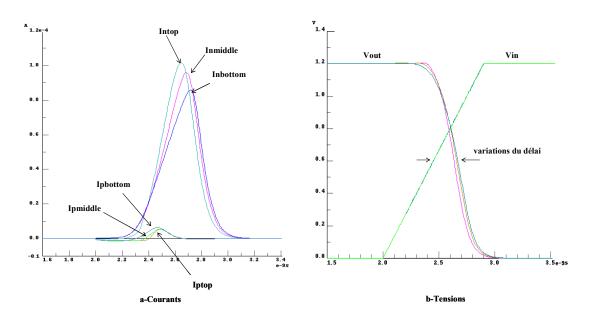

| Figure 3.10 : Profils de courant des transistors en série d'une porte <i>NAND</i> à 3 entrées et variation dans le domaine des rampes lentes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| Figure 3.11 : Schématique du bloc SBOXI : Chemin de donnée du bit de sortie 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67 |

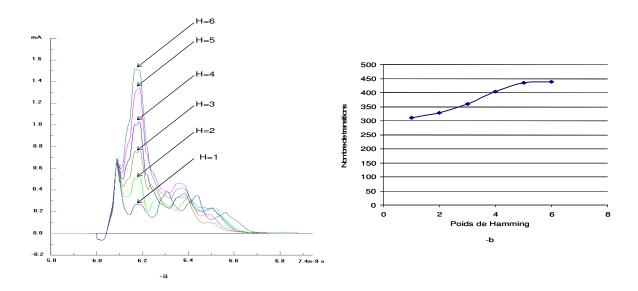

| Figure 3.12 : Courants et variations du nombre de commutations en fonction du poids de Hammi entrées dans le bloc <i>SBOX1</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •  |

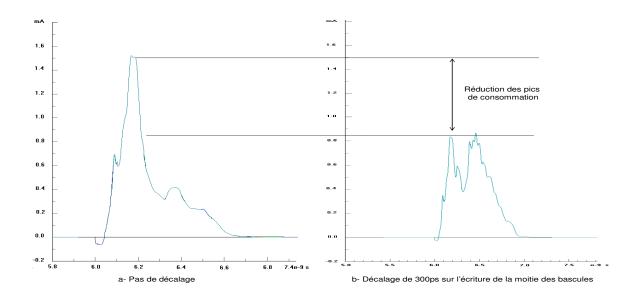

| Figure 3.13 : Courant de la <i>SBOX1</i> avec et sans décalage implémenté sur l'écriture dans la moitié registres d'entrées.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

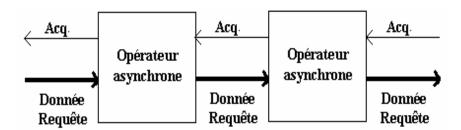

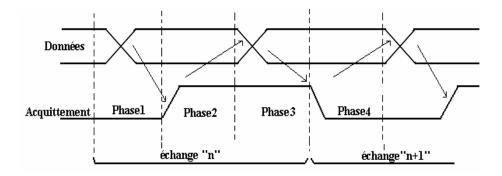

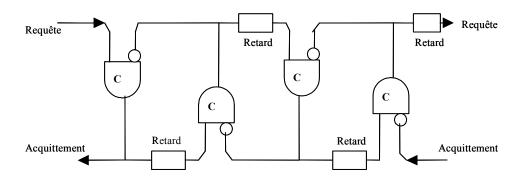

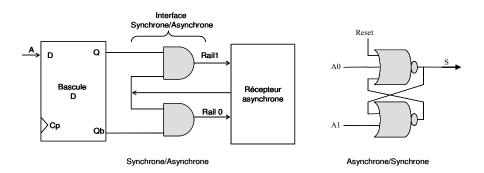

| Figure 4.1: Communication de type requête - acquittement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 81 |

| Figure 4.2: Principe du protocole 4 phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 82 |

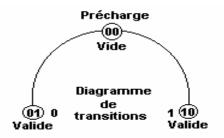

| Figure 4.3: Codage trois états                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83 |

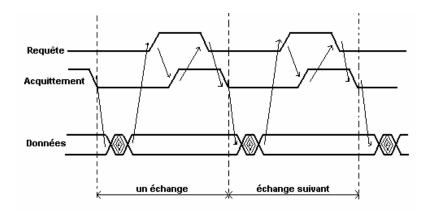

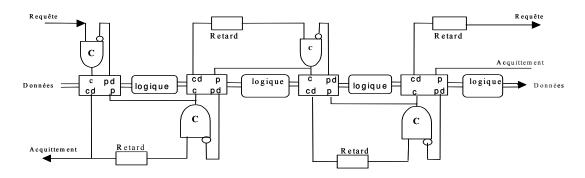

| Figure 4.4: Protocole de communication 4 phases "données groupées" ou Bundled Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 83 |

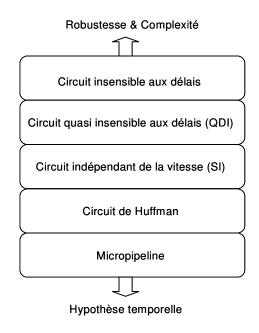

| Figure 4.5: Différentes classes des circuits asynchrones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 84 |

| Figure 4.6: Structure de base des circuits Micropipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 86 |

| Figure 4.7: Structure Micropipeline avec traitement et registre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 86 |

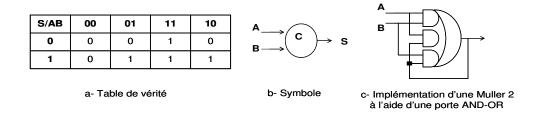

| Figure 4.8: Table de vérité, symbole et exemple d'implémentation d'une porte de Muller à 2 entr<br>l'aide d'une porte complexe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

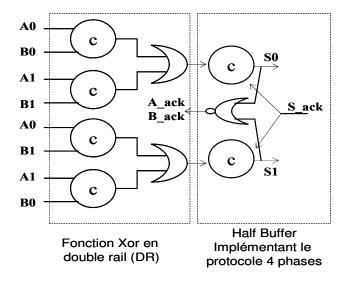

| Figure 4.9: Codage en double rail d'un digit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 89 |

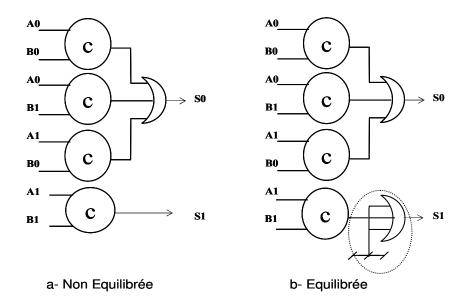

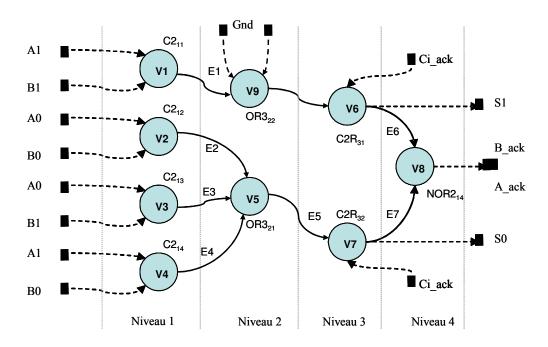

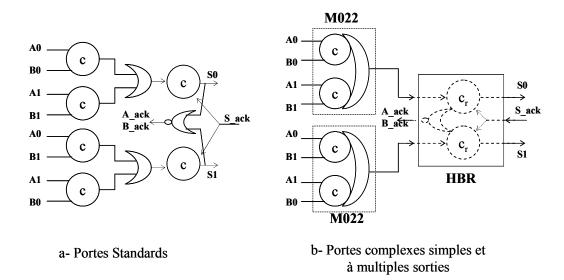

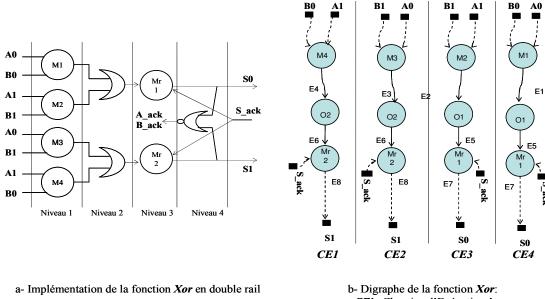

| Figure 4.10: Opérateur logique Xor' en double rail implémentant un protocole 4 phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 91 |

| Figure 4.11: Porte logique <i>And</i> en double rail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 91 |

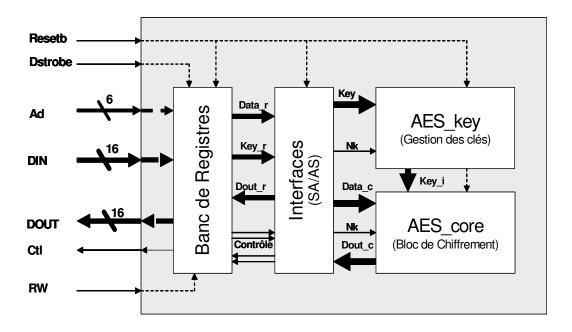

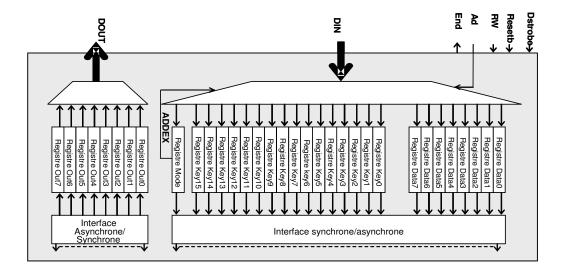

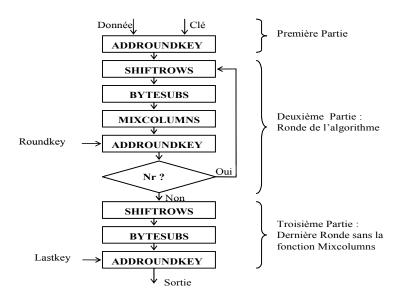

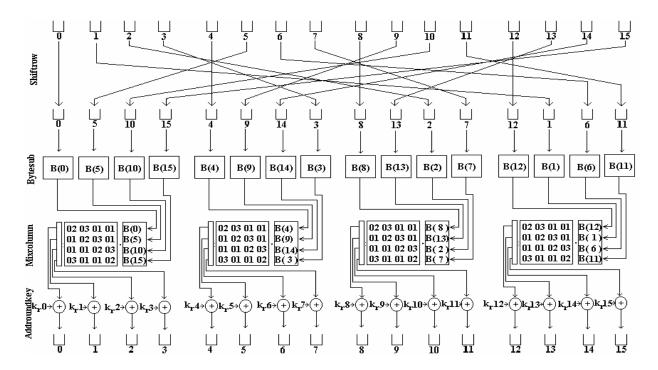

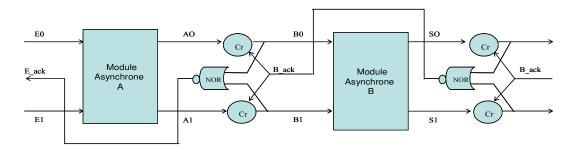

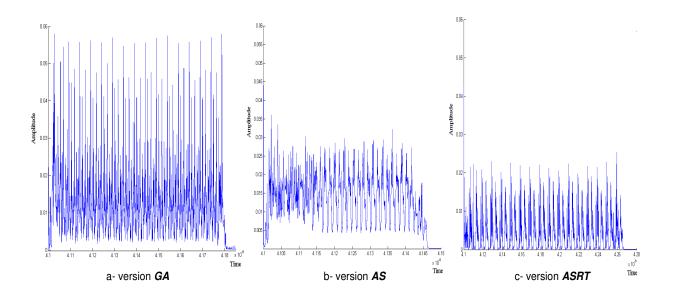

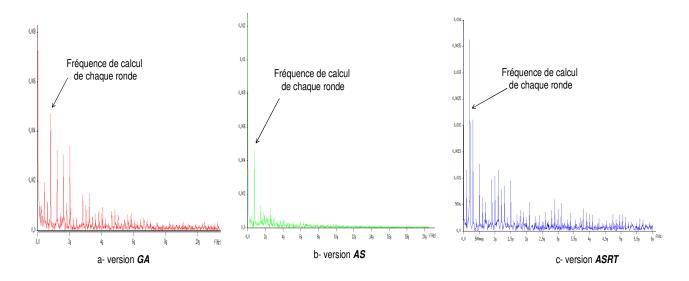

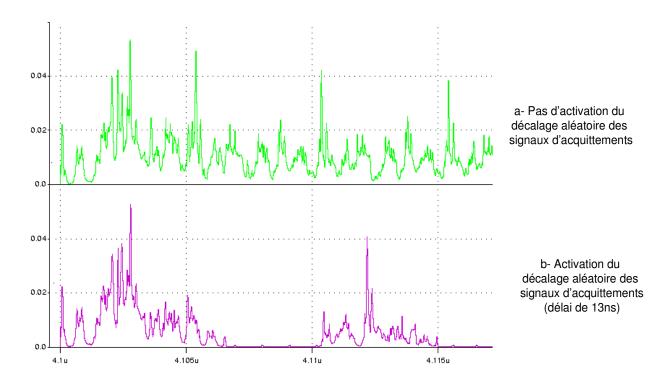

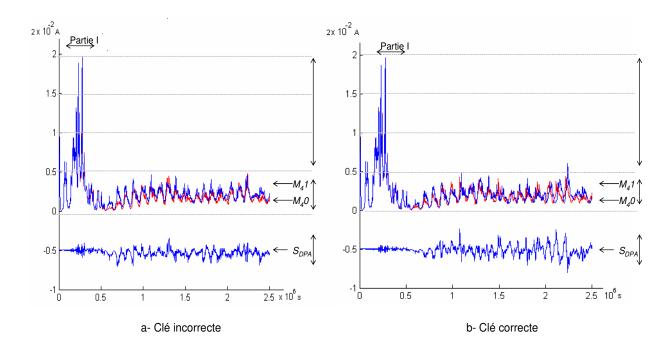

| Figure 4.12: Architecture globale du cryptoprocesseur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 93 |