# Synthèse au niveau système et conception de systèmes mixtes logiciels/matériels

T. Ben Ismail

#### ▶ To cite this version:

T. Ben Ismail. Synthèse au niveau système et conception de systèmes mixtes logiciels/matériels. Autre [cs.OH]. Institut National Polytechnique de Grenoble - INPG, 1996. Français. NNT: . tel-00010766

#### HAL Id: tel-00010766 https://theses.hal.science/tel-00010766

Submitted on 26 Oct 2005

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

présentée par

#### Tarek BEN ISMAIL

#### pour obtenir le titre de **DOCTEUR**

#### de l'INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

(arrêté ministériel du 30 Mars 1992)

Spécialité : Informatique

## SYNTHÈSE AU NIVEAU SYSTÈME ET CONCEPTION DE SYSTÈMES MIXTES LOGICIELS/MATÉRIELS

Date de soutenance : 9 Janvier 1996

Composition du Jury:

Messieurs Guy MAZARÉ Président

Ivo BOLSENS Rapporteur

Patrice QUINTON Rapporteur

Jean-Louis LARDY Examinateur

Ahmed Amine JERRAYA Examinateur

Thèse préparée au sein du Laboratoire TIMA-INPG 46, Avenue Félix Viallet, 38031 Grenoble

A ma mère,

A mon père,

A Hatem, et

A Samia,

#### Résumé

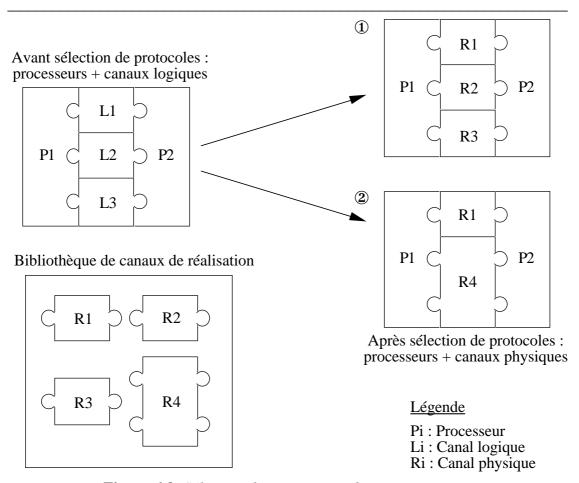

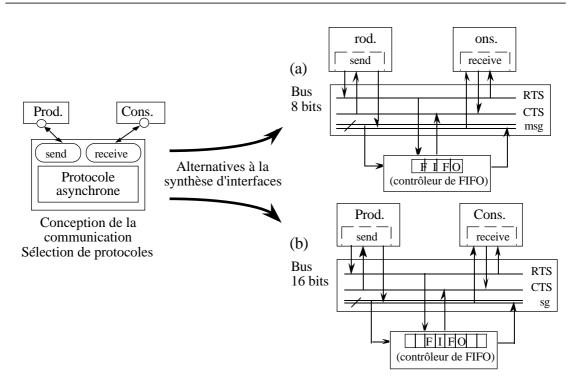

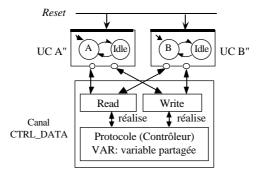

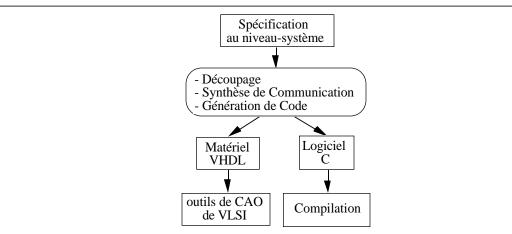

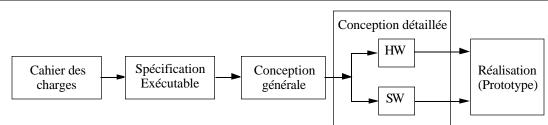

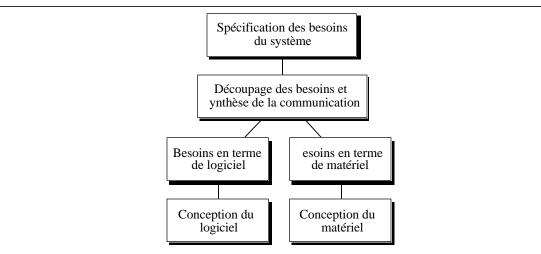

L'objet de ces travaux de thèse est d'étudier la spécification et la synthèse de systèmes de contrôle, qui peuvent être composés à la fois de logiciel et de matériel, sur des architectures multiprocesseurs (ASIC, FPGA, et logiciel). Ce sujet de recherche fait partie à la fois de la synthèse de systèmes VLSI et de la conception mixte logicielle/matérielle. Afin d'atteindre ces objectifs, une méthodologie qui permet de concevoir conjointement le logiciel et le matériel a été développée. L'originalité de ce travail vient du fait que les spécifications à traiter sont décrites à un très haut niveau d'abstraction, appelé "niveau système", avec le langage SDL. Ceci permet de concevoir des applications de plus en plus complexes. Ces travaux traitent principalement le problème du découpage de systèmes de contrôle en sous-systèmes de granularité plus fine et donc plus facilement synthétisables. L'approche de découpage qui a été développée se base sur une boîte à outils qui offre au concepteur le moyen de transformer, raffiner, découper un système puis d'affecter chaque sous-système à une technologie particulière en logiciel (C) ou en matériel (VHDL). La méthode de découpage suivie est interactive et utilise une forme intermédiaire basée sur un modèle de machines à états finis étendues communicantes via des canaux abstraits. Une autre tâche tout aussi importante dans cette méthodologie de raffinement est de synthétiser la communication entre les différentes partitions résultat d'un découpage. Cela se traduit par une étape d'allocation de protocoles de communication et une étape de synthèse d'interfaces entre les sous-systèmes communicants. La première étape consiste à sélectionner dans une bibliothèque les modèles de communication nécessaires entre les sous-systèmes. La deuxième étape consiste à adapter ou générer les interfaces des différents sous-systèmes.

**Mots clés:** synthèse au niveau système, conception conjointe logiciel/matériel, machine d'états finis étendue, SDL, C/VHDL, découpage de descriptions, synthèse de la communication, sélection de protocoles de communication, génération d'interfaces.

#### **Abstract**

The objective of this thesis is to develop a system-level specification and synthesis approach that allows an interactive hardware/software codesign of applications onto multiprocessor architectures composed of ASICs, FPGAs, or software processors. This thesis presents a hardware/software codesign methodology that starts with a specification given in the system-level description language, called SDL, and generates, through an intermediate representation called Solar, hardware and software descriptions in VHDL and C languages respectively. Two main steps are required in order to transform this specification into mixed hardware/software descriptions used for synthesising the hardware and compiling the software parts. Firstly, a system-level partitioning step is needed in order to transform, and split the model into a set of communicating subsystems. Secondly, a communication synthesis step, including protocol selection and interface generation tasks, is needed in order to refine the model into a set of interconnected subsystems. Each of these subsystems is described either in C code or in VHDL. Software parts may be compiled for a standard microprocessor and hardware parts may feed existing high-level synthesis tools in order to programme FPGAs or design ASICs.

**Keywords:** System-level synthesis, hardware/software codesign, extended finite state machine, SDL, C/VHDL, partitioning, communication synthesis, communication protocol selection, interface generation.

### Table des Matières

| Liste | des Figures                                                        | vii |  |  |  |  |

|-------|--------------------------------------------------------------------|-----|--|--|--|--|

| Liste | des Tableaux                                                       | x   |  |  |  |  |

| Chap  | pitre 1: Introduction                                              | 1   |  |  |  |  |

| 1.1.  | Motivations                                                        | 2   |  |  |  |  |

| 1.2.  | La conception conjointe de logiciel/matériel                       | 3   |  |  |  |  |

| 1.3.  | Objectifs                                                          |     |  |  |  |  |

| 1.4.  | Contribution                                                       |     |  |  |  |  |

| 1.5.  | Plan de la thèse                                                   | 7   |  |  |  |  |

| Chap  | pitre 2: Modèles, langages de spécification au niveau système,     |     |  |  |  |  |

|       | et systèmes de conception logiciel/matériel                        | 9   |  |  |  |  |

| 2.1.  | Introduction                                                       | 10  |  |  |  |  |

| 2.2.  | Systèmes de conception conjointe logiciel/matériel : État de l'art |     |  |  |  |  |

|       | 2.2.1. Taxonomie des outils de conception logiciel/matériel        | 13  |  |  |  |  |

| 2.3.  | Modélisation: État de l'art                                        | 15  |  |  |  |  |

| 2.4.  | Langages du niveau système : État de l'art                         | 19  |  |  |  |  |

|       | 2.4.1. Taxonomie des langages de spécification                     | 20  |  |  |  |  |

|       | 2.4.1.1. Puissance d'expression                                    | 20  |  |  |  |  |

|       | 2.4.1.2. Puissance d'analyse                                       | 22  |  |  |  |  |

|       | 2.4.1.3. Arguments commerciaux                                     | 23  |  |  |  |  |

|       | 2.4.2. Comparaison des langages de spécification                   | 23  |  |  |  |  |

| 2.5.  | Conclusion                                                         | 26  |  |  |  |  |

| Chap  | pitre 3: Modélisation pour la synthèse de systèmes mixtes          |     |  |  |  |  |

|       | logiciels/matériels                                                | 27  |  |  |  |  |

| 3.1.  | Introduction                                                       | 28  |  |  |  |  |

| 3.2.  | Le format SOLAR : Les concepts de base                             | 28  |  |  |  |  |

| 3.3.  | La table d'états                                                   | 33  |  |  |  |  |

| 3.4.  | L'unité de conception                                              | 34  |  |  |  |  |

| 3.5.  | Le canal de communication                                          | 35  |  |  |  |  |

| 3.6   | Conclusion                                                         | 30  |  |  |  |  |

# Liste des Figures

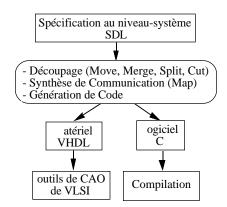

| 1.1.  | La statégie de conception d'un système                                     | 4  |

|-------|----------------------------------------------------------------------------|----|

| 2.1.  | Approche typique de synthèse                                               | 12 |

| 2.2.  | Étapes du cycle de développement d'un système                              | 12 |

| 2.3.  | Modèle de machine à états finis pour un four à micro-onde                  | 17 |

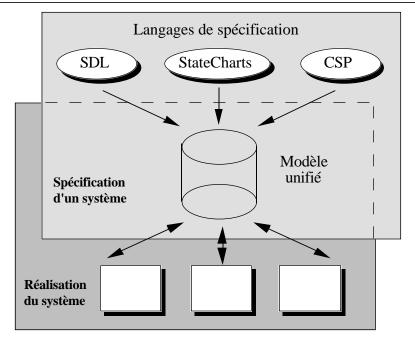

| 3.1.  | Environnement de Solar                                                     | 29 |

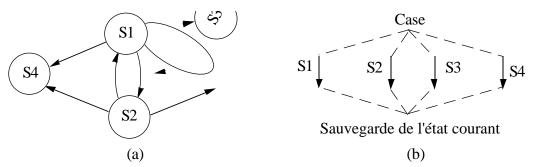

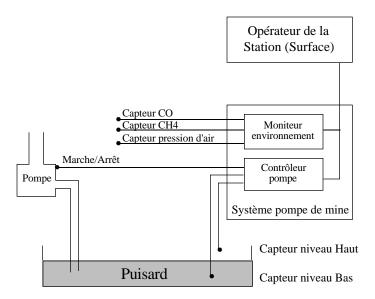

| 3.2.  | Système de contrôle d'une pompe minière                                    |    |

|       | (a) Représentation schématique                                             |    |

|       | (b) Représentation au niveau système par des MEFs communicantes            | 30 |

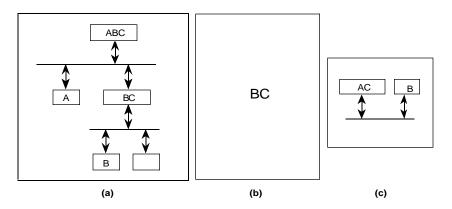

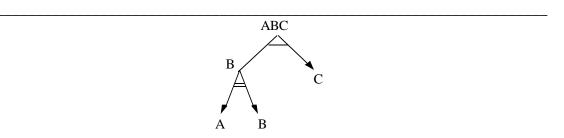

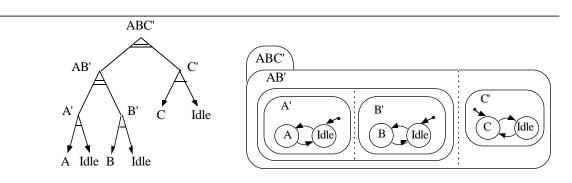

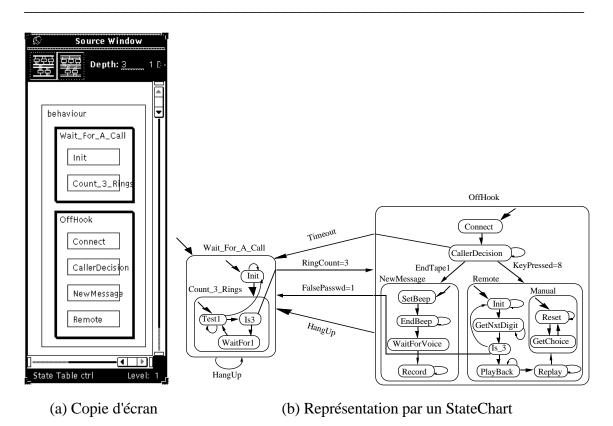

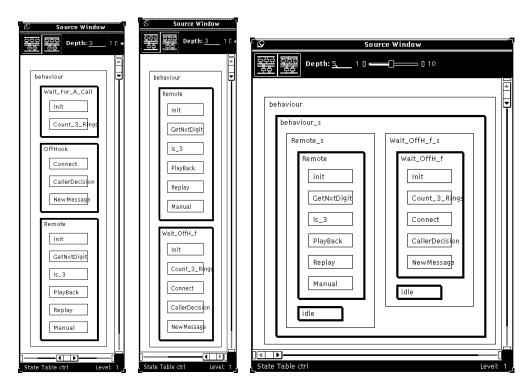

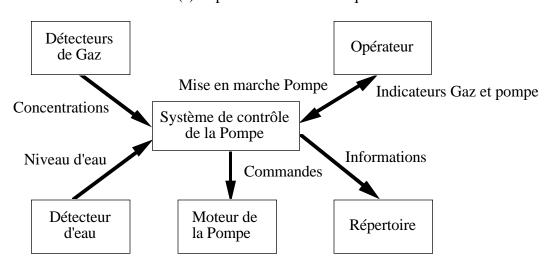

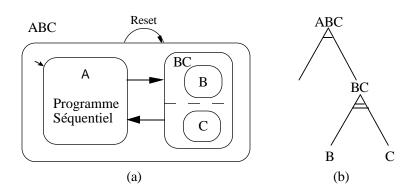

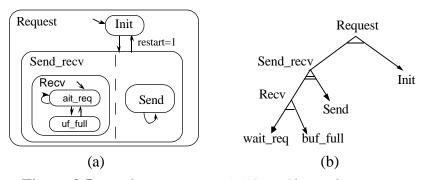

| 3.3.  | (a) Représentation de ABC par un StateCharts                               |    |

|       | (b) Représentation hiérarchique de ABC                                     | 32 |

| 3.4.  | Attributs d'une table d'états                                              | 33 |

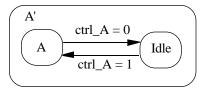

| 3.5.  | Machine Request : (a) Représentation par un StateCharts,                   |    |

|       | (b) Représentation hiérarchique et parallèle de la table d'état : Request  | 34 |

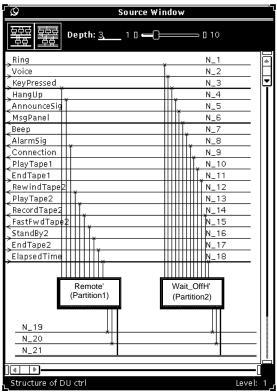

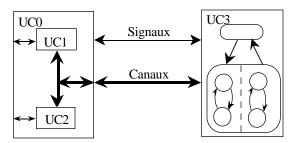

| 3.6.  | Unités de conception                                                       | 35 |

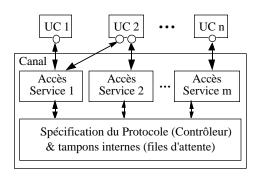

| 3.7.  | Structure d'un canal Solar qui offre m services                            | 36 |

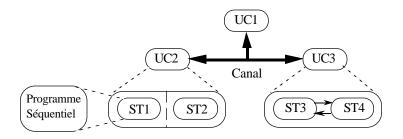

| 3.8.  | Niveaux d'abstraction d'un canal connectant deux processeurs :             |    |

|       | (a) vue conceptuelle, (b) extrait de la spécification en Solar du système, |    |

|       | (c) description en Solar d'un canal,                                       |    |

|       | (d) réalisation d'une unité canal physique                                 | 38 |

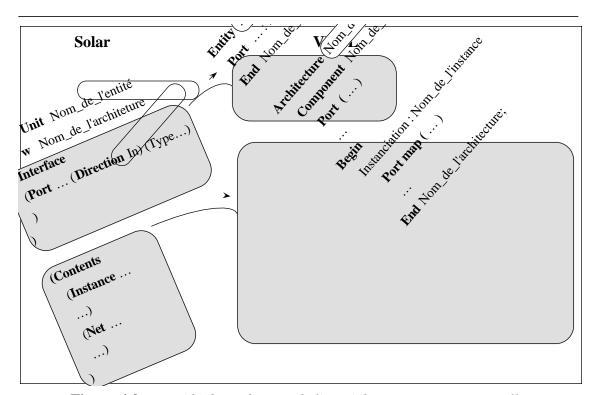

| 3.9.  | Organisation de la structure d'une description en Solar                    | 39 |

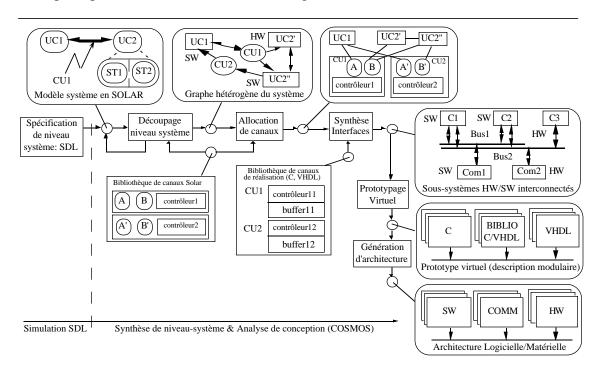

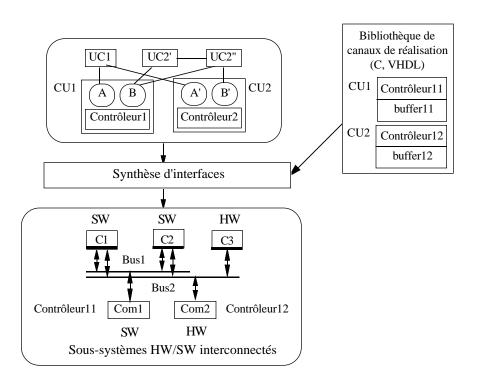

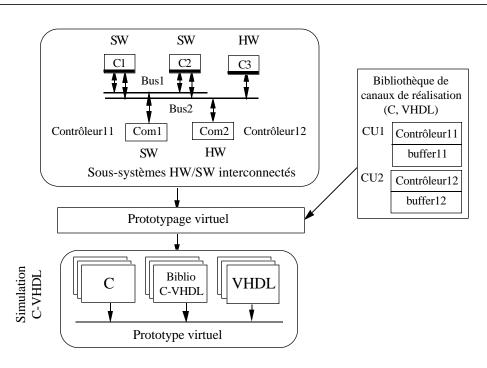

| 4.1.  | Approche de synthèse dans COSMOS                                           | 42 |

| 4.2.  | Saisies des spécifications                                                 | 44 |

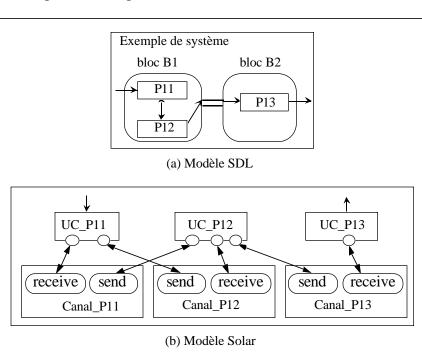

| 4.3.  | Conversion du modèle SDL en un modèle Solar                                | 45 |

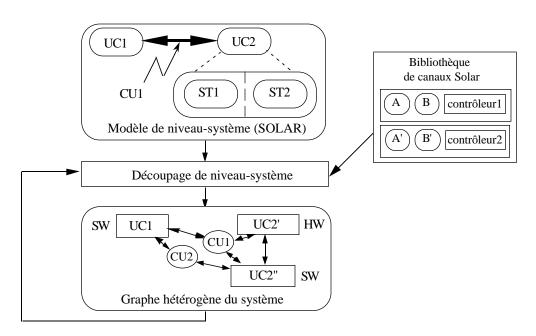

| 4.4.  | Étape de découpage dans COSMOS                                             | 49 |

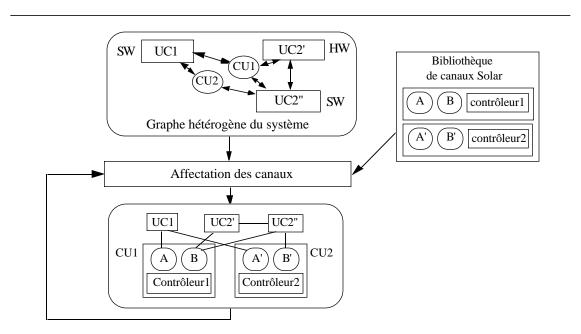

| 4.5.  | Étape d'affectation des canaux                                             | 51 |

| 4.6.  | Étape de synthèse des interfaces                                           | 52 |

| 4.7.  | Étape de génération d'un prototype virtuel                                 | 53 |

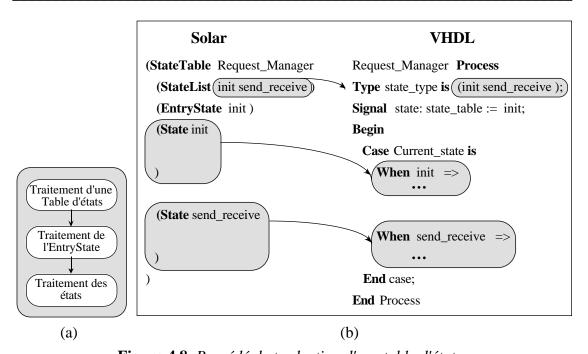

| 4.8.  | Procédé de traduction d'une table d'états :                                |    |

|       | (a) Flot de traitement, (b) Exemple de traduction d'une table d'états      | 55 |

| 4.9.  | Procédé de traduction de l'unité de conception structurelle                | 56 |

| 4.10. | Style de description d'un programme C généré :                             |    |

|       | (a) Modèle de la machine d'états décrite en Solar,                         |    |

## Liste des Tableaux

| 2.1. | Tableau comparatif des outils de conception logiciel/matériel | 14 |

|------|---------------------------------------------------------------|----|

| 2.2. | Comparaison des langages de spécification                     | 24 |

| 4.1. | Correspondance entre Solar et VHDL comportemental             | 54 |

| 5.1. | Résultat de fusion de MEFs                                    | 69 |

| 5.2. | Estimation du coût de chaque processus de la figure 5.2       | 69 |

| 5.3. | Résultats de découpage du système de la figure 5.2            | 70 |

| 5.4. | Performances des partitions générées à la suite du découpage  | 90 |

"Nous avançons dans l'obscurité, lentement, nous n'avons guère de force. Mais nous avançons et notre marche au milieu des ténèbres infinies me paraît magnifique. Le doute n'est point pour nous «un oreiller commode» où l'on pose la tête pour rêver. L'état de doute représente une étape dans la recherche scientifique où vont naître les hypothèses que l'on devra vérifier."

Robert DEBRÉ dans le livre "Ce que je crois", 1976.

#### Introduction

\_\_\_\_\_

Dans ce chapitre d'introduction, les motivations et les objectifs de cette thèse seront définis. Les différents problèmes rencontrés dans la synthèse au niveau système et lors de la conception conjointe de logiciel/matériel seront passés en revue. Une approche de ces problèmes et les idées conduisant à leurs résolutions seront présentées. La contribution apportée au cours de cette thèse sera brièvement exposée. Finalement, un plan de la thèse sera fourni.

#### Modèles, langages de spécification au niveau système, et systèmes de conception logiciel/matériel

\_\_\_\_\_

Le but de ce chapitre est de présenter l'état de l'art des systèmes de conception logiciel/matériel ainsi que des modèles et langages de spécification au niveau système. Les systèmes existants de conception mixte logicielle/matérielle seront passés en revue. Les caractéristiques de chaque système seront détaillées afin de montrer les domaines d'application respectifs. Ensuite, une comparaison des langages de spécification au niveau système sera proposée à travers les concepts inhérents à chaque langage.

# Modélisation pour la synthèse de systèmes mixtes logiciels/matériels

\_\_\_\_\_

Dans ce chapitre le format intermédiaire, Solar, sera présenté. Ce format sert de modèle de représentation de spécifications provenant de langages de description de logiciel ou de matériel. Ainsi les parties logicielles et matérielles d'un même système peuvent être unifiées dans le même format Solar. Le modèle de description adopté dans Solar est une extension au modèle des machines à états finis. Les extensions concernent le parallélisme, la hiérarchie, la communication entre machines à états finis, et le traitement des exceptions.

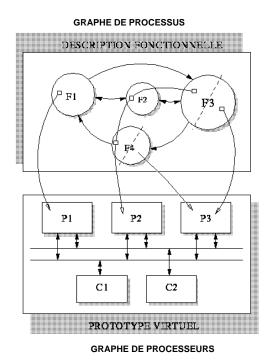

# Méthodologie de conception dans COSMOS

\_\_\_\_\_

Le but de ce chapitre est de donner une vue globale de COSMOS, une nouvelle méthode de conception conjointe logicielle/matérielle. Cette approche se compose d'un ensemble d'étapes qui servent à transformer une spécification de haut niveau en une réalisation comportant à la fois du logiciel et du matériel. Dans ce chapitre, chaque étape sera décrite à travers les modèles qu'elle utilise et les transformations qu'elle est amenée à réaliser.

#### Le découpage de systèmes au niveau système

\_\_\_\_\_

Le but de ce chapitre est de présenter une nouvelle méthode de découpage de systèmes pour la conception conjointe de systèmes mixtes pouvant contenir du logiciel et du matériel. Il s'agit de transformer une description système en un ensemble de sous-systèmes appelés partitions. Chaque partition comporte une ou plusieurs fonctions du système. Ce découpage sert à réduire la complexité des éléments traités lors de la conception mais aussi à choisir une réalisation (matérielle ou logicielle) pour chaque sous-système. La méthode de découpage proposée se situe au niveau système et se base sur le principe diviser pour régner. Cette méthode est interactive et permet l'application d'un ensemble de primitives de découpage et de transformation.

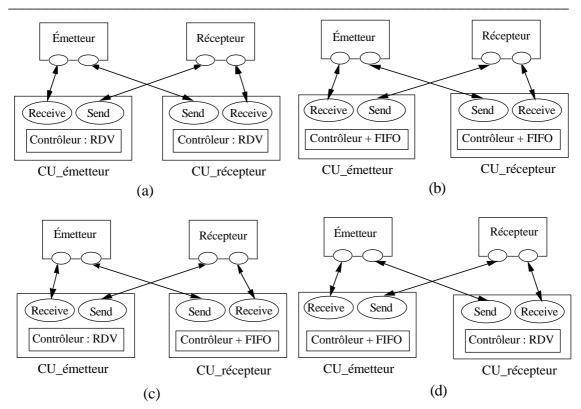

#### La synthèse de communication

\_\_\_\_\_

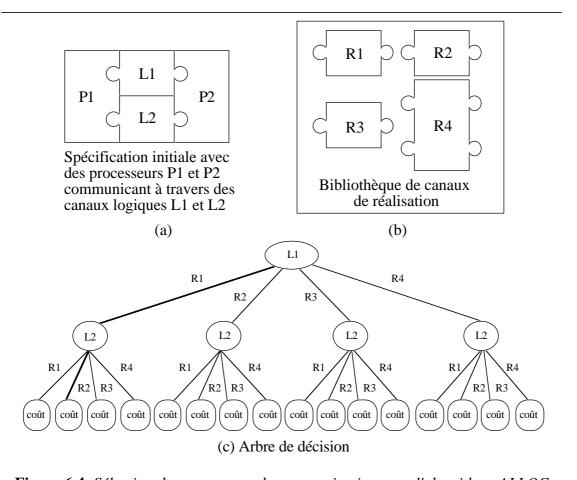

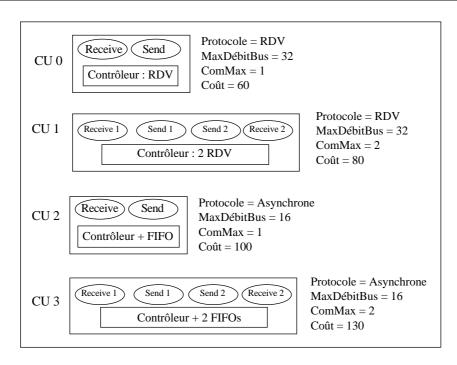

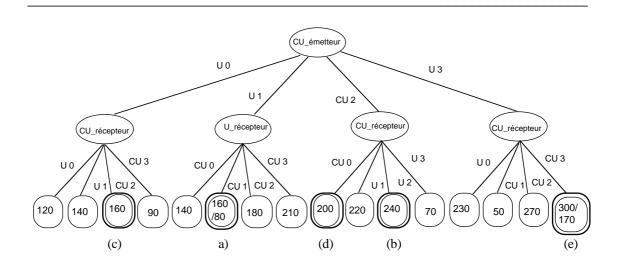

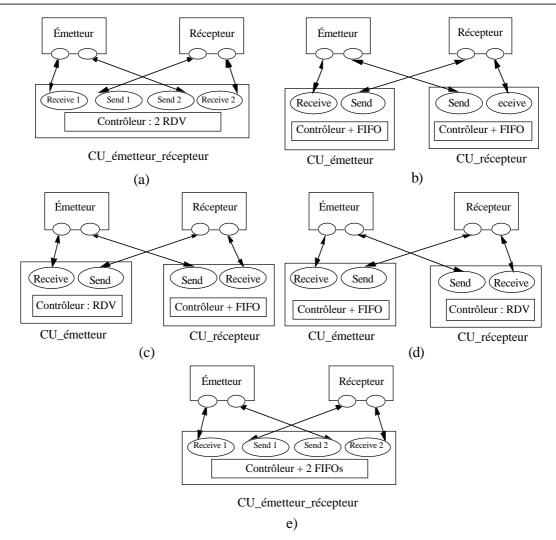

Le but de ce chapitre est de présenter une approche de synthèse de la communication au niveau-système. Cette étape est vue comme un problème d'allocation d'unités de communication e.g. canaux avec leurs protocoles. Cette synthèse de communication comporte à la fois la synthèse de protocoles et la synthèse d'interfaces. La première consiste à choisir des protocoles (standards ou spécifiques) pour établir des communications entre les différents composants d'un système. La deuxième sert à adapter l'interface des sous-systèmes afin de communiquer à travers les protocoles préalablement sélectionnés.

Conclusions et perspectives

## Bibliographie

#### **Bibliographie**

- [Abri88] J-R. Abrial, "Une Approche Formelle du Développement des Logiciels," Génie logiciel & Systèmes experts, N° 11, Mars 1988.

- [AdSc93] J.K. Adams, H. Schmitt, and D.E. Thomas, "A Model and Methodology for Hardware-Software Codesign," Handouts of Int'l Wshp on Hardware-Software Co-design, Cambridge, Massachusetts, IEEE CS Press, October 1993.

- [AnBa94] S. Antoniazzi, A. Balboni, W. Fornaciari, and D. Sciuto, "A Methodology for Control-Dominated Systems Cedesign," Proc. Third Int'l Wshp on Hardware/Software Codesign (CODES/CASHE), Grenoble, France, IEEE CS Press, pp. 2-9, September 1994.

- [AnCa93] P. Angosto, B. Caillaud, M. Delaure, R. Gueschel, B. Jouga, D. Le Foll, J. Maret, P. Rocher, and G. Vaucher, "L'ingénierie des protocoles," InterEditions Publishers, Paris, 1993, 222 pages.

- [Andr91] G.R. Andrews, "Concurrent Programming, Principles and Practice," Benjamin/Cummings (eds), Redwood City, Calif., pp. 484-494, 1991.

- [AnMa90] S. Antoniazzi, and M. Mastretti, "An Interactive Environment for Hardware-Software System Design at the Specification Level," Microprocessing & Microprogramming, North-Holland, Vol. 30, pp. 545-554, 1990.

- [Arno90] A. Arnold, "Systèmes de transitions finis et sémantique des processus communicants," Technique et Science Informatiques (TSI), Vol. 9, N° 3, Bordas (eds), pp. 193-216, 1990.

- [Atam94] Y. Atamna, "Réseaux de Petri temporisés stochastiques classiques et bien formés : définition, analyse et application aux systèmes distribués temps réel," Rapport LAAS N° 94418, Thèse de Doctorat, Université Paul Sabatier, Toulouse, Octobre 1994.

- [AuBe94] M. Auguin, M. Belhadj, J. Benzakki, C. Carrière, G. Durrieu, Th. Gautier, M. Israël, P. Le Guernic, M. Lemaître, E. Martin, P. Quinton, L. Rideau, F. Rousseau, and O. Sentieys, "Towards a Multi-Formalism Framework for Architectural Synthesis: the ASAR Project," Proc. Third Int'l Wshp on Hardware/Software Codesign (CODES/CASHE), Grenoble, France, IEEE CS Press, pp. 25-32, September 1994.

- [BaEc93] M. Bauer, and W. Ecker, "Communication Mechanisms for VHDL Specification and Design Starting at System Level," Proc. VHDL Forum for CAD in Europe, Spring '93 Meeting, Innsbruck, Austria, pp. 95-106, March 1993.

- [BaRo92] E. Barros, and W. Rosentiel, "A Method for hardware Software Partitioning," IEEE Comp. Euro, 1992.

- [BaRo94] E. Barros, W. Rosentiel, and X. Xiong, "A Method for Partitioning UNITY Language in Hardware and Software," Proc. European Design Automation Conference (EuroDAC), IEEE CS Press, Grenoble, France, September 1994.

## **Publications personnelles**

#### **Publications** personnelles

#### Publications dans des ouvrages et des revues

- [BIJe95] T. Ben Ismail, and A.A. Jerraya, "Synthesis Steps and Design Models for CoDesign," IEEE Computer, Special issue on Rapid-Prototyping of Microelectronic Systems, Vol. 28, N° 2, February 1995, pp. 44-52.

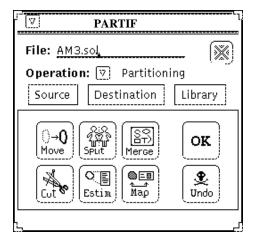

- [BIOB95] T. Ben Ismail, K. O'Brien, and A.A. Jerraya, "PARTIF: Interactive System-level Partitioning," to appear in VLSI Design, Special issue on Decomposition Systems, Gordon & Breach Science Publishers, 1995.

- [BIDa95] T. Ben Ismail, J-M. Daveau, K. O'Brien, and A.A. Jerraya, "A System-Level Communication Synthesis Approach for Hardware/Software Systems," to appear in Int'l Journal Microprocessors and Microsystems, special issue on Hardware/Software Codesign, Butterworth-Heinemann Publishers, 1995.

- [JeOB93] A.A. Jerraya, K. O'Brien, and T. Ben Ismail, "Linking System Design Tools and Hardware Design Tools," Proc. Conference on Hardware Description Languages (CHDL), Ed. D. Agnew, L. Claesen, and R. Composano, Publ. Elsevier, Ottawa, Canada, April 1993, pp. 331.

- [DaBI96] J-M. Daveau, T. Ben Ismail, G. Marchioro, and A.A. Jerraya, "Protocol Selection and Interface Generation for HW-SW Codesign," submitted to IEEE Transactions on VLSI Systems, Special issue on Design Automation of complex integrated systems, September 1996.

- [BIMa96] T. Ben Ismail, G. Marchioro, and A.A. Jerraya, "Découpage de Systèmes VLSI à partir d'une Spécification de haut niveau," accepté à Technique et Science Informatiques (TSI), Hermes (eds), 1996.

#### Publications dans des conférences internationales

- [BIOJ94] T. Ben Ismail, K. O'Brien, and A.A. Jerraya, "Interactive System-level Partitioning with PARTIF," Proc. European Design & Test Conference (ED&TC), Paris, France, IEEE CS Press, March 1994, pp. 464-468.

- [BIA94a] T. Ben Ismail, M. Abid, K. O'Brien, and A.A. Jerraya, "An Approach for Hardware-Software Codesign," Proc. Int'l Wshp on Rapid System Prototyping (RSP), Grenoble, France, IEEE CS Press, June 1994, pp. 73-80.

- [BIA94b] T. Ben Ismail, M. Abid, and A.A. Jerraya, "COSMOS: A CoDesign Approach for Communicating Systems," Proc. Int'l Wshp on Hardware/Software Codesign (CODES/CASHE), Grenoble, France, IEEE CS Press, September 1994, pp. 17-24.

- [BIJe94] T. Ben Ismail, and A.A. Jerraya, "Tutorial: Hardware/Software Codesign," Invited paper, Eighth Brasilian Symposium on Integrated Circuits Design, Gramado, Brasil, November 1994, pp. 17.

#### Glossaire

#### Glossaire

**ADA** Langage de programmation (standard ISO)

ADDL Algorithm Design Description Language

Langage de spécification basé sur un sous-ensemble de Pascal et une extension afin de décrire le parallèlisme et une sémantique

matérielle

**ASIC** Application Specific Integrated Circuit

Circuit intégré dédié à une application

**ATM** Asynchronous Transfer Mode

Protocole de communication asynchrone à haut débit

B Langage formel basé sur les mathématiques

CX Langage de sépécification qui est une extension au langage C pour

décrire le parallèlisme entre processus et les contraintes de temps

**CAO** Conception Assistée par Ordinateur

**CCITT** International Consultative Committee for Telegraphy and

*Telephony*

Organisme de normalisation des protocoles de communication

**CMOS** Technologie de fabrication des circuits intégrés

**CODES** Outil de conception logicielle/matérielle à Siemens

**Co-simulation** Simulation mixte logicielle/matérielle e.g. en C et en VHDL

**Co-spécification** Spécification hétérogène d'un système e.g. en C et en VHDL

**COSMOS** Projet de conception mixte logiciel/matériel en cours de

développement dans l'équipe SLS du laboratoire TIMA

COSYMA Outil de conception logicielle/matérielle à l'Université de

Braunschweig

**CPU** Central Processing Unit

Unité centrale de calcul

**CRCW** Concurrent Read Concurrent Write

Lectures parallèles et écritures parallèles

#### Annexe B

# Étude des principales approches de conception de logiciel/matériel

L'objet de cet annexe est de fournir une étude des principales approches de conception de logiciel/matériel. Ces approches sont développées soit dans des universités soit dans des centres de recherches rattachés à des compagnies industrielles.

#### Annexe C

#### Algorithmes des primitives

\_\_\_\_\_

Dans cet annexe les algorithmes des primitives de découpage et de synthèse de communication seront présentés. Ces algorithmes ont été programmés en langage C++ dans un environnement de stations de travail sous le système d'exploitation UNIX.

#### Annexe D

#### Exemples en SDL graphique

\_\_\_\_\_

Dans cet annexe deux exemples en SDL graphique seront présentés. Le premier est un système émetteur/récepteur et le deuxième est un bloc simplifié de télécommande d'un satellite. Pour le système émetteur/récepteur, une description en SDL sera donnée, ensuite des copies d'écran des représentations graphiques en Solar seront présentées, et finalement, les descriptions C et VHDL générées automatiquement seront proposées.

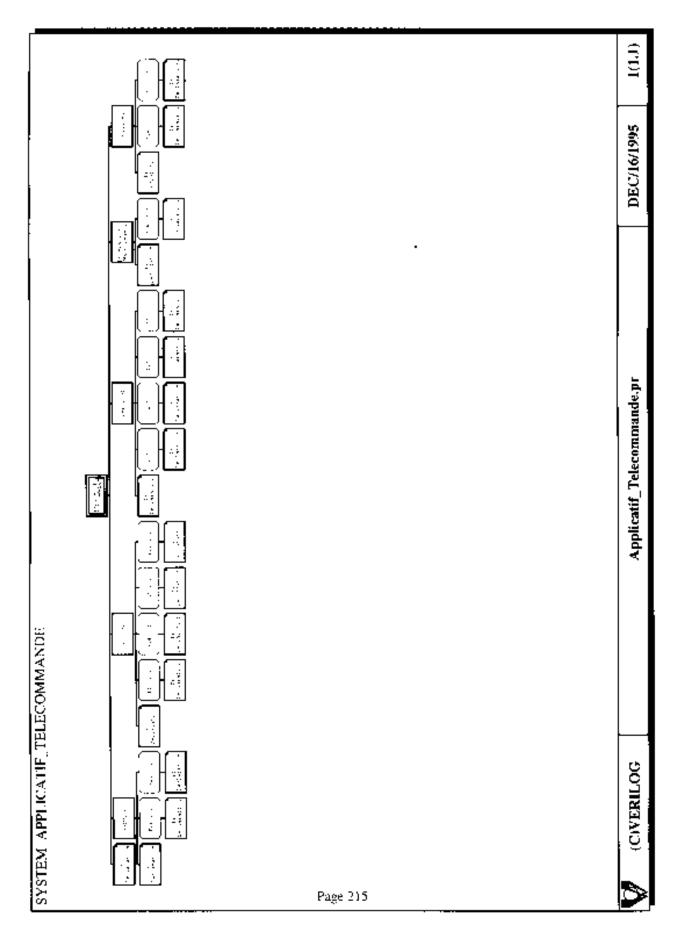

| Description e | n SDL | graphique | du | système | Émetteur/Récepteur |

|---------------|-------|-----------|----|---------|--------------------|

|               |       |           |    |         |                    |

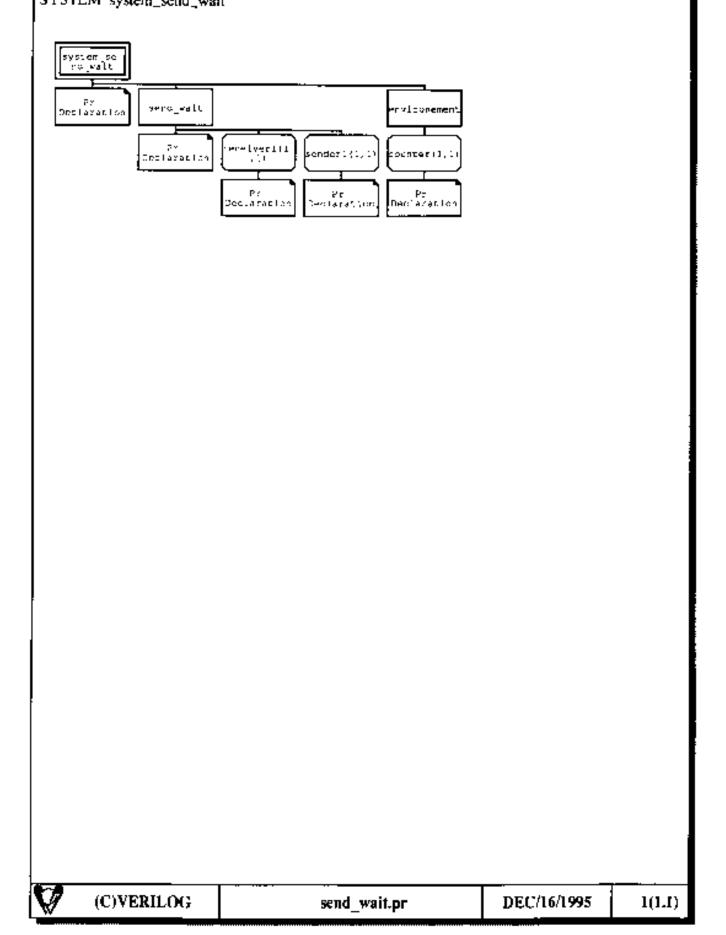

# Représentations du système graphiquement en Solar

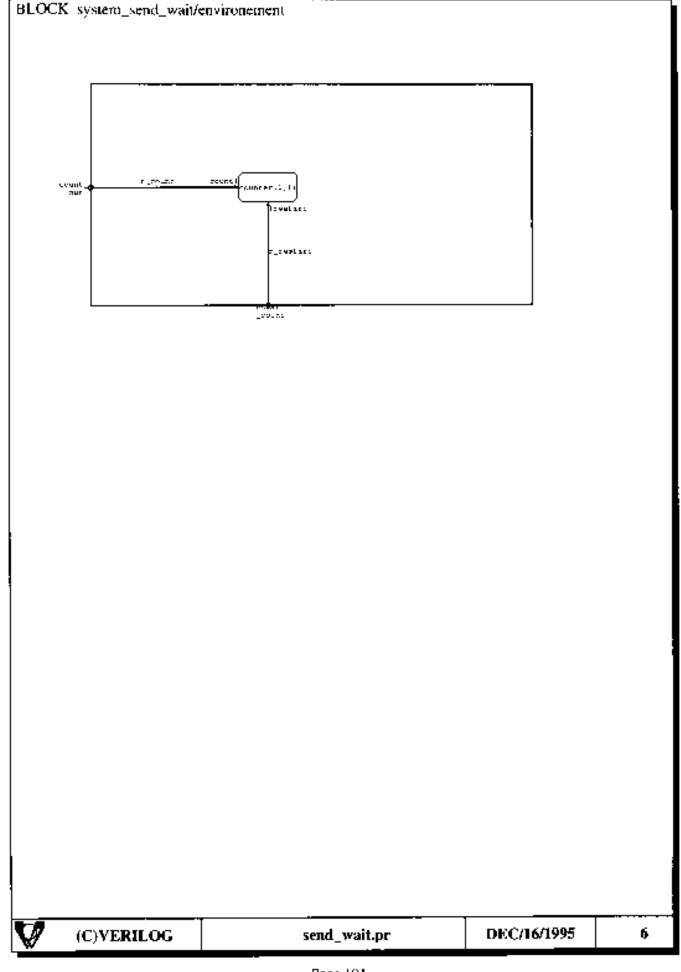

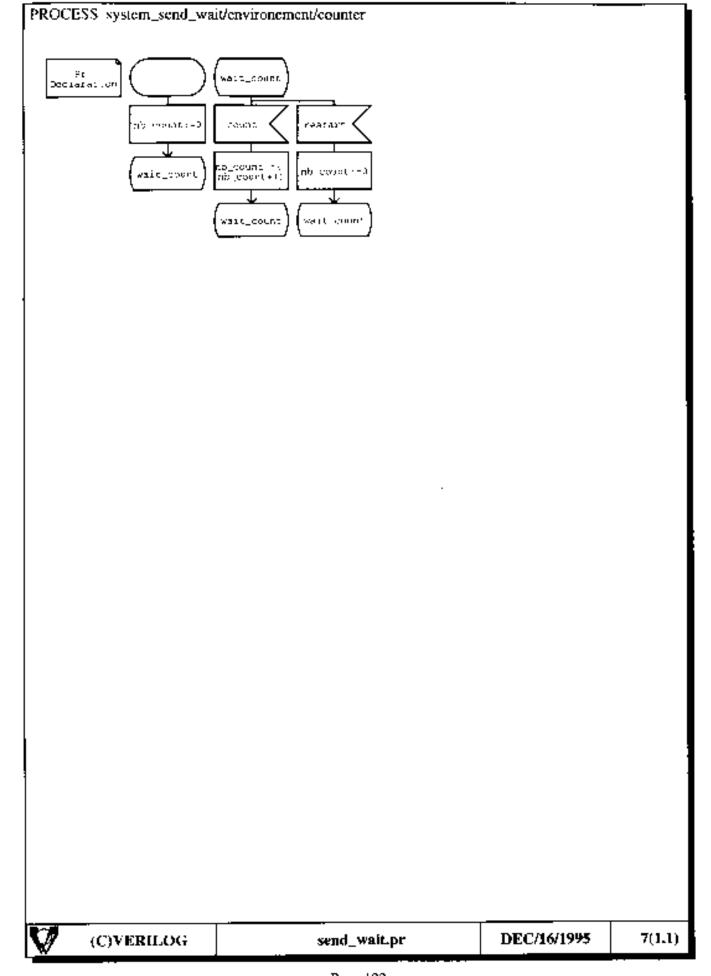

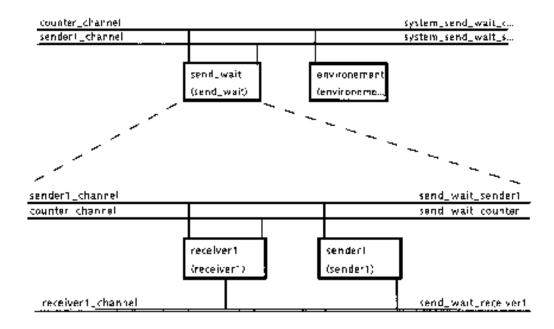

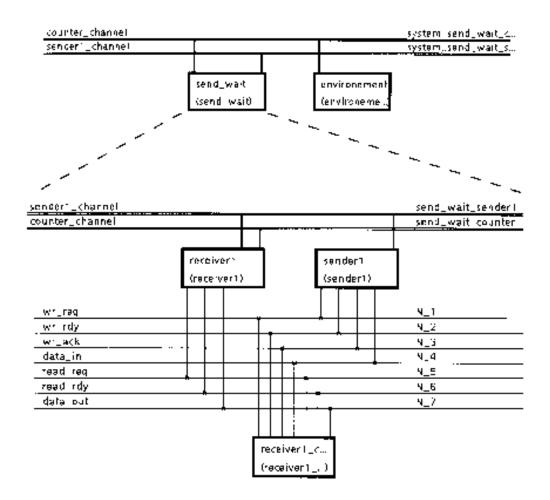

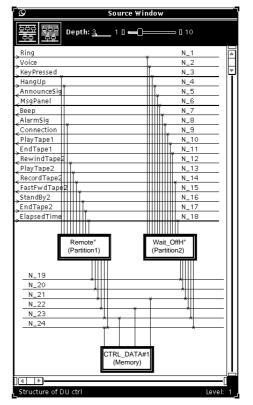

Représentation graphique de la description en Solar du système émetteur/récepteur.

L'unité "send want" est hiérarchique et contient les deux unités (processus) d'émission et de réception. Les dittérentes unités sont connectées à travers des canaux de Solar. Dans cette représentation et celles qui survent, la convention suivante à été utilisée : les canaux et signaux externes sont représentés en haut des unités alors que les canaux et signaux internes sont représentés en bas.

Annexe D. Exemples on SDI.

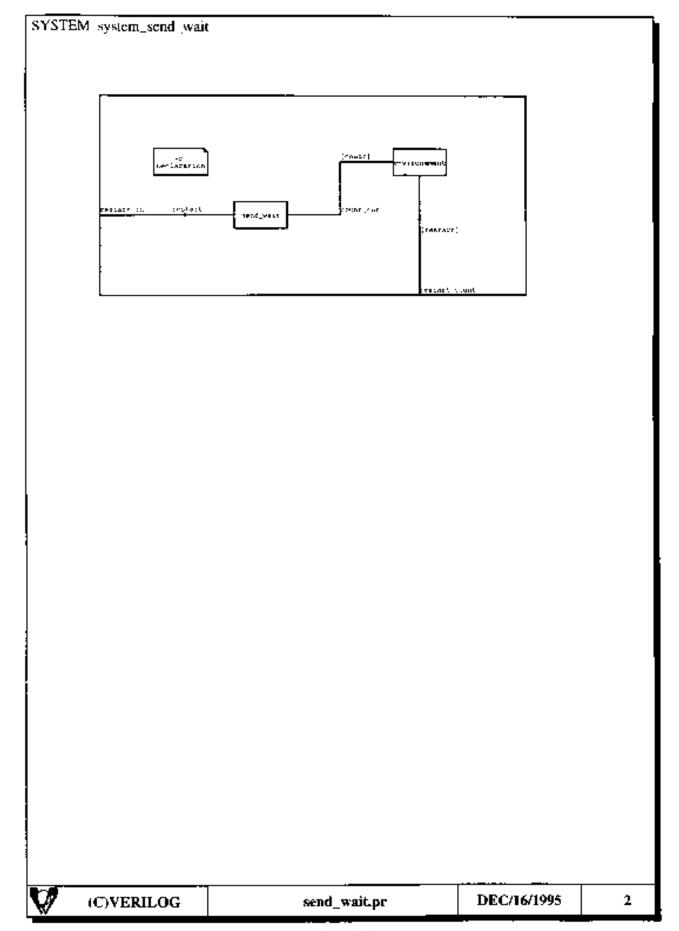

Représentation graphique de l'unité "send\_wait" après application de l'opération "MAP" sur le canal appelé "receiver1\_channel" qui est montré dans la figure précédente.

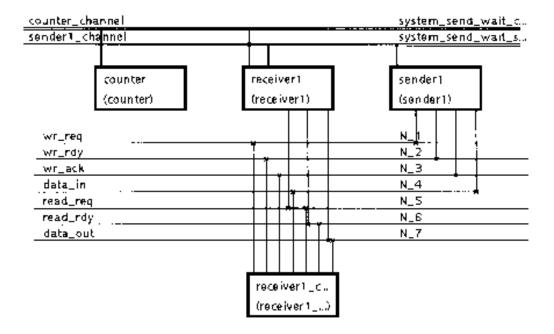

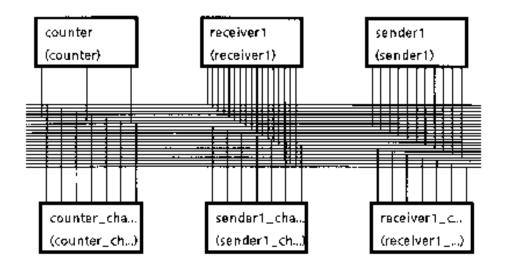

Représentation graphique de tout le système après deux applications successives de l'opération "FLAT" sur l'unité "send-wait" et l'unité "environement". Cette opération "FLAT" est appliquée à une unité à la fois et met à plat un seul niveau de sa hiérarchie.

Annexe D. Exemples en SDL

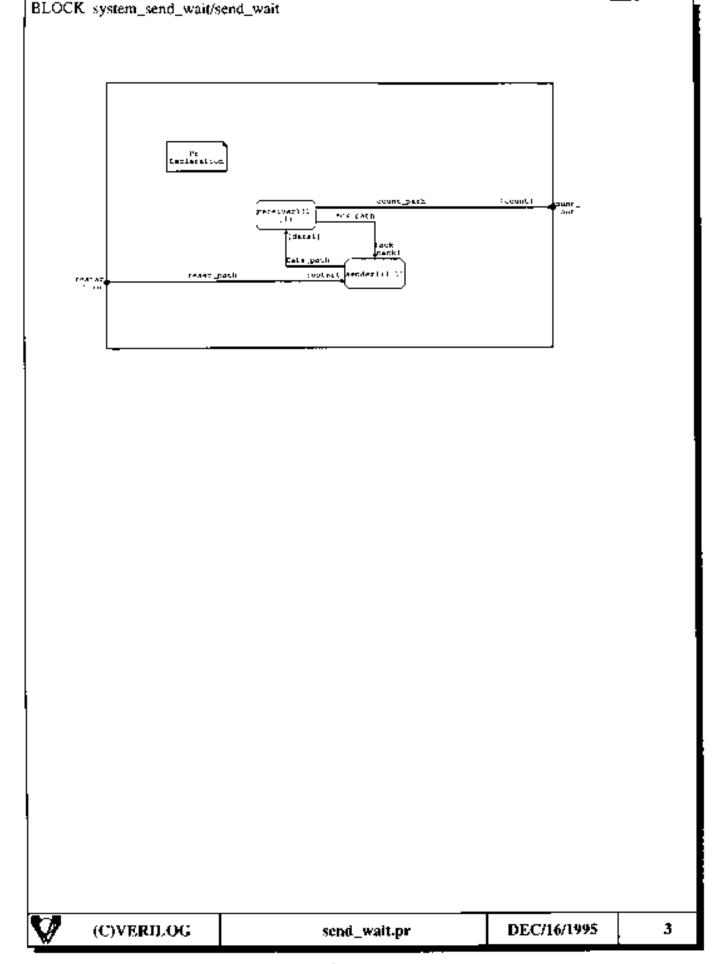

Représentation graphique de tout le système après deux applications successives de l'opération "MAP" sur le canal "sender1\_channel" et le canal "counter\_channel" de la l'igure précédente. Le résultat est un système composé d'unités interconnectées uniquement à travers des signaux et sans canaux.

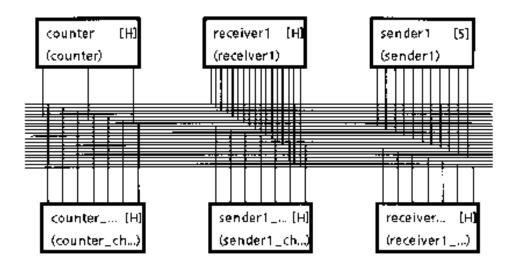

Représentation graphique de tout le système après affectation de chaque unité à une réalisation logicielle ou matérielle.

La notation "[S]" veut dire que l'unité correspondante est affectée à une réalisation en logiciel. De la même manière la notation "[H]" veut dire que l'unité correspondante est affectée à une réalisation en matériel.

## Description de l'Émetteur générée automatiquement en C "DU senderl.c"

```

/* C-Bile OU_sendorito */

/* CHOSE feet_Of ViewObject CotViewbype Thehaviour* */

/*DObject_Of OU_sendorit/

/**DObject_Of OU_sendorit/

rincludes000b;ect_00f/

Annolude *DU_senderl n*

.,,,,,,.....

×

111

int PCAST.

. *processDOOngeor_CCf/

. j

umic DD_sendari()

iΕ

/*interfaceFracessECObject CC DU_senderlitt.vcl*/

/* iSadeObject_CO */

/* ViewObject_CO */

٤?

۱Ŀ

/*deSineParamCel;ProcedureOnjost CC*.

15

:::

INTESER datapat_signa/:

TNTECER process_idput_signal;

/wdofinePeramCallProcedureObject_SC*/

::1

22

23

24

TNTEGER dataget_signal:

25

/* ContestsObject CC*/

20

27

28

/fgender1_hehzviourDU_sender1*/

INTEGER count = 1 , /*ConstUbject_CC*/

≱deline _count

29

INTEGER restart = 2 : /*ConstObject_CC*/

#define _restart 2

20

21

32

INTEGER ank - 4 / /*Constablect_CC*/

33

#define _wck %

34

LWCDGER next_to_send, /*VarObject_00*/

/* SCObject_CS_RECLAREZPE */

16

97

typedel enum

! 4

stateCable_sender1TDLEState,

: 9

4::

imitialState,=a:r_ackState

) statebable_sender1ShahaTypo.

41

statetable_sender(SpaceType statetable sender(NextState - in)t:0(Stare:

4.5

statetable_senderiStoreType INITIALState = statetable_senderiMextShore:

43

int AGAIN = 1:

44

int ToSend = 0;

int ToReceive = 1:

4%

4%

while (AGAIN == 1)

47

46

44

if (AGAIN == 1)

50

if (ToSend == 1) /*TestItDoSend*/

51

52

52

DD_schderlitfSendOUT(IPCKEY):

54

ToSend = 1:

55

56

2,50

≣7

50

TH_sendorlibfReceiveIN(IPCKEY):

59

/*end if (AGAIN == 1) */

60

switch(statetable_senderlNextState) /* STObjack CD */

61

62

63

64

mase initialState : /*STRINGOpe_StateObject CC*/

next_to send = 1.0 %; /* Ass)gnObject CI */

65

process idput_signal = 2 :/*PARASSIGF)agSTRINGCDeParamassCbjedr CC*/

66

put_signalProc(&(next_to_send).aproness_ideput_signal (* /*3CaliObject_CC*/

scacetable_senderlNextState = walt_ackShahe; /* NxtstCbject_CC */

67

68

59

] break:/*AREAKCompCond*/

case wait_ackState : /*STRINGOpe_StateObject_CC*/

70

71

72

ger_signalPros(&(signal(): /*PCallObject_CC*/

73

/*CaseCbject_CC*/

if ((signal)==(restart) | /* Alcobject CC */

74

75

ſ

paramput_signal = 111 :/*PARASSTGFlagSTRINGOpeParamassObject_CC*/

76

77

process_idput_signal = 2 //*PARASSIGFlagSTRINGOpeParamagasObject_CC*/

28

state(able_sender)NextState = wait_ackState; /* NxtstChject_CC 1/

62

eise

```

```

is ((signal) -- (mok) ) /* Alcobyoot CD */

34

35

16

67

next_to send = !(next_to_send!*( l ) ): /* AssignObject CC */

process idput signal = 2 :/*FARASSIGFlagSTRINDOpeParamassObject CC*

pur_signalPrec(&(next_to_send),&process idput signal (: /*PCallObject CC*

statetable_sender!NextStare * wair_ockState; /* NxcatCoject_CC **

48

44

::11

91

90

90

if (/signal)==(neck) ( /* AltObject_CC */

process idput_signal = I :/*FAMASSIGFlagSTRINGOpeRecemmasCD;ect_MC*/

put signalProc%(next_to_send).sprocess_idput_signal): /*PCallObjecr_co**

scattedable senderINextState = wait_autState; /* NxtatObject_Co */

54

95

96

97

Ģ3

| break;/*BREAKCompCond*/

) it end while (ASAIN -- I) '/

:00

:41

resumm AGAIN:

-- CommentsObject_CC+/

: 32

: 3 !

144

105

106

107

"fsonderi _behaviourDC_sender1"/

fendProcessBUUbject_CC*/

106

129

/f end DU_sendert.c */

```

Description du reste du système générée automatiquement en VHDL "send\_receive.vhd"

```

<u>:</u>

Generated by AMICAL transvMDE (PAC) V 3.0 of ChrCCL-1994

Reside Colt BU_counter

Tobrary mys.,7:

haw mul 7. TYPES. 211.

ä

hise mot 0.abithmetic.ell:

10

library SYMOPSYS,

1:

use SYMOPSYS.arrributos.all:

library MOPK:

13

use woRS.send_warrpkg.a.l,

14

......

entity DU_counter()a

generic: LPCKBY = INTEGER: ();

16

: 3

Fort (

writeg: N BIT_VECTOR(1 no 0):

writeg: Dur bIT_VECTOR(1 no 0):

writeg: Dur bIT_VECTOR(1 no 2):

data is. IN INTEGER_VECTOR(1 no 0):

20

20

read_req : OUT BIT:

read_rdy : IN DIT:

data_out : IN INTEGER

23

24

25

26

27

29

29

ead DO_counter;

.....

applifiedture | counter behaviour of DU_counter is

beuin

provess

31

33

71

٠,

variable dataget_signal : INTEGER;

: :

procedure get_signal( variable data : incut INTEGER ):

procedure get_signal( variable data : incut INTEGER ) is

::)

ξģ

34

begin

•

PHALL := 1:

while (PDALL = 1) loop

•1

•2

case get signalNEXT_STATE is

when; request ! => read req <= '1';

46

47

68

45

get signalNEXT_STATE := wait_rrdy :

whon) wait_ridy ( => if NOT(( text_riy= 'l') ) then

50

wait until ( read_rdy= 1');

51

52

53

54

end if.

gon sichalNEXT_STATE := get :

when | get | =>

| data | = | data_out;

| read_req <= | 10 :

35

56

57

ger signalNEXT STATE := FIBLE \times when obsers +\times PCALL (--0) ,

53

36

ger_signalNEXT STATE := cequest ;

90

61

61

63

end case :

end (cop:

ċ٤

Ċά

end ger_signal:

ĊS

constant rount: INTEGER := ( 1 ) :

constant restart: INTEGER := ( 1 ) :

constant nack: INTEGER := ( 4 ) :

constant ack: INTEGER := ( 5 ) :

variable nb_count : INTEGER .

7ن

ĠΞ

69

70

71

type statetable_counterSTATE_TYPE is ( initial, wait_count ):

variable statetable_counterNEXT_STATE : statetable_counterSTATE_TYPE := initial

72

74

75

76

begin

----

27

28

case statetable counterNEXT_STATE is

19

when( insteal ( =>

ΕU

nn_count := 2 /

```

```

statetable_counterNEXT_STATE --- wait fount .

33

when! wait_count : ->

24

get_signal: signal (:

f ( Bignel - count)

85

86

87

Oter.

nb_count := ( nb_count ( 1 );

statetable_counterNEXT_STATE ( ) wait_fount (

sa

89

wire

of / signal- restart)

90

91

then

mb_doubt = 3 -

90

95

and if:

44

95

end ić.

95

9.5

98

end case :

919

and process :

and counter behavious:

103

104

105

126

107

Tibrary SYNCESYS,

hise AVMAPSYS.attributes.ail:

Tibrary WORK;

use WCRK, send_wantpkg.ail:

------

108

entity DO_receiver( is generic) ISCKEY - INTEGER:-1()

109

110

111

Port :

wr_req: TN SIT_VECTOR() to 2 ()

wr_rdy: OUT BIT_VECTOR() to 3 ();

wr_ack: OUT BIT_VECTOR() to 3 ();

data_in: IN INTEGER_VECTOR() to 3 ();

112

113

104

11.

read_req : OUT BIT:

read_rdy : IN BIT:

date_out : IN INTEGER

116

and DN receiveri

12.j

12.1

anomitachure | received: behaviour of DU_teceiver1 is

123

123

negin

process

124

125

variable FCALL : INTEGER := 1 :

125

127

123

123

rype got signilstate type is ( PIDDE, request wait_rody, g+0 );

variable got signalNEXT_PEATS : qet_bignalSTATS_TYPE := request;

defineParamCallProcedureObject_vv

Parnable dataget signal . INTEGER:

130

progedure gor signal) variable data : inout INTEGER (:

procedure got signal) variable data : input INTBOBR ! .a

131

132

pegin

133

136

DOMESTIC:

while (FCALL - 1) loop

135

136

137

case get signalNEXT STATE is

138

-----

when( regulat 1 -> read_neg <- '1'

139

140

ger_signalNEXT_STATE .- wait_srdy :

141

when( wash ordy ) ->

if NOT(: read rdy= 1') : then

wait until ( read rdy= '1'):

142

140

:44

end it:

145

:40

147

146

read_req <-

101.

149

150

get_signalNEXT_STATE .- PIDLE .

.51

.51

when others as

SCALL -- 0 :

get_signalNEXT STATE :- request :

_50

155

end case :

156

end loops

end gen_signal/

type put_signalSTATE_TYPE is : PIDLE. request. Warrawdy, submit i: variable put signalNEXT_STATE : put_signalSTATE_TYPE := request; pet;seParamCallFrocedureObject_VV

161

variable dataput signal : INTEGER:

```

```

variable process_idput_signal : INTMGER:

16%

procedure put_signal) variable data : input INTEGER: variable process id : input I

STEGER ):

procedure put signal: variable data : :nout INTEGER: variable process id : inout 1

166

MORGER ) 15

157

153

Degine

. . . .

. . . . . . . .

POALL := 1:

. # 9

while (PCALL - 1) Toop

179

: 97

: 77

: 74

case put_signalNLXT_STATE is:

whom: toquest : =>

wr req! process id - .= '1',

put sign=!NEWT STATE .= wait wrdv :

275

176

195

178

when ( wait wrdy ) =>

if NOT(/ wr rdy) process_id (= -11) : then

wait until ( wr rdy) process id (= -11);

. 20

160

ona of,

dara in) process id | := dama,

101

por_signalNEXT_STATE := submit .

157

when submin ( -> in MOT)( wr_ack) process id (- (1)) then

193

194

wart until ( we_ack) process_od (- 1910)

185

166

end if:

wr_deq( process_id ) := 101;

put_signalNEXT_STATE := PIDLE :

1 F 7

184

when others =>

189

PUBLIC := 3 ·

193

publisignalNEXT_STATE := request :

191

19%

end dase .

193

194

who loop:

106

.....

ine.

end put sidsel:

107

constant count: INTEGER = 1 1 ; constant restart: INTEGER = 1 2 ; constant restart: INTEGER = 1 4 ; constant ack: INTEGER = 1 5 ; vaciable sext_ro_versive: INTEGER ; variable num_tick: INTEGER; variable temp: INTEGER; type statetable receiverISTATE TYPE is

0.6

199

100

101

102

203

2014

type statetable_receiver187ATE_TYPE is ( initsal, wait data ).

variable statetable_receiver18EXT_STATE : statecable receiver18TATE_TYPE := in.

2415

20%

rial

242

205

necin

209

case statetable_receive:1NEXT_GTATE (a

201

2::3

2::3

when( initial ) =>

314

next_to_receive := 0 :

217

216

217

mum tick := 0 :

when( wait_data ! =>

got signal) Lemp (:

if | temp= 111 ) them

31F

219

2001

2001

2007

2004

2005

next,to_receive := 0 :

num tick := 0 :

statetable_receive:19EXT_STATE --- wair data :

if ( temps next_to_receive) then

next_to_receive := ( next_to_receive + 1 ).

process_idput_signal -= 1 : 2CallCbject_genBVHDL

::::A

227

pub_signal() ack, process_idput_signal(),

num_blck := { num_blck + l();

228

229

if ( num_tick= 10 ) then

precess_idput_signal -- 1 : PCA.!Object genBVHDL

230

231

put signal( count, process_lopur_signal ),

statetable_receiverINEXT_STATE :- want data .

1:32

433

234

335

336

scatchable_receive: NEXT_STATE : - wait data .

2.17

338

⇒na if:

3.19

240

alsa

process_idput_signal := 1 : PCallObject genBVEDL

241

242

pub signal( nack, provess_udpyt_signal ),

```

```

|statetable_receives1NEXT_STATE | := |wait_data |

34%

244

:425

cod af.

.JA

257

248

end sta

169

-----

1. :0

ond case :

::::

2:57

end process

-

- 9 /

And reservery behaviour,

354

395

(:brary SYNOPSYS)

Hac SYMOPSVS.actributes.all.

366

29.7

Tibrary WORK:

25.8

mine WORK.send_waitpkn.all,

369

.....

360

ennisy - EU menderi is

genemani IPOKEY : INTEGES:-II/

361

261

Port (

263

264

wilmed: IN RIT_MECTOR() to 0 () willed; OUT BIT_MECTOR() to 0 ); wilked: OUT BIT_MECTOR() to 0 ); data_in: IN INTEGER_MECTOR() to 0

265

266

267

read_req : OUT DIT:

read_rdy : IN DIT:

data_out : IN INTEGER

26a

369

370

271

ond DU_senderi:

372

373

architecture senderl_behaviour of DU_sender1 :8

374

pegin

200

process

.276

variable PUALL : INTEGER := 1 :

rype put signalSTWTE_TYPE is | FIDLE, request. wait_widy, submit |:

variable put signalNEXT STATE | put_signalSTWTE_TYPE := request:

derineParamCallProcedureObject VV

277

378

270

260

201

war(able daraput signal : INTEGER;

warrable process idput signal : INTEGES.

202

procedure pur signar, variable data : imput INTEUER: variable process_id : input I

263

NTEGER );

processory pur signati variable data : input INTEGER: variable processor : input 1

284

NTEGER ) (8

285

Segin

286

. . . . . . . . . . .

287

POALL :- 17

MARLE (PCALE - 1) loop

288

289

290

case put_signalNEXT_STATE is

291

whent request ( ->

292

wo_seq( process_nd ) -- '1';

293

295

296

wait until ( wr_rdy( process_ut )= '1');

end if;

297

292

data_in/proceas_id/(:- %ara/

put_signalNEXT_STATE :- sommer:

299

360

362

362

when I submit ( ) => 10 MAT(( wc_a(k) process id (- '3') ) then 10 MAT(( wc_a(k) process id (- '3') ) then

wait until ( wr_nak( procession )= '1'), end if:

303

394

wz_teg) process_nd + :- 107:

put_signalNEXT_STATE :- FIFEE;

005

006

007

when others ->

PCALL : 7 0 :

304

put_signalNEXT_STATE -- request.

304

____

300

end case :

411

312

end loos:

311

214

end out signal:

. . . . . . . . . . . . . . . .

215

type get_sigmalSTATE_TYPE is ( PIDNE, request, wait redy, get ):

216

vaciable get_signa.NEXT_STATE : get signalSTATE TYPE := request;

217

--definePacamCallProceduraChject VV

318

319

variable datager_signal : INTEGER,

procedure get_sigmal( variable data : inout INTEGER (:

procedure get_sigmal( variable data : inout INTEGER ) is

320

322

begin.

```

```

123

_____

1.14

SCALL := 1:

1.25

while speaks = 1; loop

372E

-----

)27

328

case get signalNEXT STATE is

119

313

63.1

when wast_rady ) => if NOT1( read_rdy= '11') ; then

330

323

324

325

walt cntil ( read_rdy= 'T');

end if;

326

qet_signal9EXT_STATE := qet ;

327

when: get | =>

data := data_out:

338

329

read_req s= '2';

qet_signalNEXT_STATE   := PCDLE, ;

340

Sai

when others 49 FCALL := 0 :

341

qot sichalNEXT[STATE :- (equest /

.40

! 44

14%

end case :

146

end .oop:

-----

348

end get_aignal;

149

constant count: INTEGER := ( ] [ ] : constant restart: INTEGER := ( ] [ ] : constant nack: INTEGER := ( ] [ ] : constant ack: INTEGER := ( ] 5 ] : variable next_to_send : INTEGER : ( ) type statetable xemierISTATR fiver is /

Opti

350

350

353

354

type statetable_sender1STATB_fYPB is ( initial, wait_ack ):

variable statetable_senderlnEXT_STATE : Statetable sender.STATE :: initial

357

256

besin

......

366

961

hase statetable senderINEXT STATE is

363

363

when( initial ! =>

mext to send := 0 /

164

16%

process idput signal : 2 / Prof.Object_genBVEDL

465

pur_signal) | nexr_to_send.process_idpat_signal (

367

staterable_sender:NEXT_STATE :- #ail_ack :

465

when: warr_ack ) ->

369

_get_signal( signal(:

379

371

it : signal- restact)

Chen

paramput_signal := 111 :--9CallCbject men3VHDL

process_idput_signal := 2 :--PCallCbject genBVHDL

372

373

put_signal: paramput_signal, process idput signal (,

next_to_send := / - 1 );

374

375

376

statetable_senderINEXT_STATE    .= wait sck :

377

if : signal= ack)

378

370

Chen

mext_to_send := ( mext_to_send - 1 ):

350

351

350

3.63

else

if ( signal= mack)

354

365

356

then

367

0.68

369

390

end if:

emd if.

391

392

end if.

353

354

395

end case :

196

457

end process :

398

⇔nd senderl_behaviour:

369

400

Tibbacy JYNOPSYS:

401

Wse SYNOPSYS, attributes, all:

402

Tabaday WORK:

403

956 WORK.send_waitpkq.all;

```

```

404

405

40€

entity receives, channel is penetic; <code>SPOWEY</code> - <code>TMTEGER:-1);</code>

107

406

Post i

wholeg: IN BIT_VECTOR(1 to 2 );

wholeg: IN BIT_VECTOR(1 to 2 );

wholey: OUT BIT_VECTOR(1 to 2 );

whole, OUT BIT_VECTOR(1 to 2 );

data in: IN INTEGER_VECTOR(1 to 1 ),

year req . IN BIT;

char rey . OUT BIT;

data_rey . OUT BIT;

4:19

4.70

411

411

414

410

end receive: [_onannel,

410

417

architecture | receiver(_channel_view of receivent channel is

418

319

began

400

process

4:::

variable PIALL : INTEGER := 1 -

420

constant mb sender: INTUSEA (* 1 2 ) /

constant queue site: INTUSEA (* 1 204 ) ;

--IntSbject ponETypEof--XARNING, maybe type is re-delined here:

423

424

425

426

427

Throughout gonerypoor--xamble, maybe type is terdelines here

type INTEGER_VECTOR is array ( NATURAL range <> ) of INTEGER;

variable queue_in_prr : INTEGER := ( 1 );

variable queue_in_prr : INTEGER := ( 1 );

variable queue_our_prr : INTEGER := ( 1 );

variable todoce : INTEGER := ( 1 );

type controllerSTATE_TYPE is ( Init, send seceive );

428

429

420

401

vatiable controllerMEXT_STATE : controllerSTATE_TYPE := imit:

402

433

434

Segin

433

4.16

made contoolie:NEXT_STATE is

4.17

4 ! 4

439

when: Init ) =>

queue_in_pts := 1 /

queue_out_pts := 1 /

redies = 1 /

443

greue_in_pts :=

441

442

indise .=

controllerNEXT_STATE = = send_receive :

440

when( send receive : =>

444

445

Mon Decimed Faractob; ect_genUVMDL

446

.....

447

end case .

448

449

450

end process :

451

452

and receiver1_channel view:

453

libiary SYMOPSYS;

454

use SYNO9SY3.attributes.all.

455

library wORX:

450

use work, send_waitpkg.all:

457

-----

416

cntity sendedl_changelins

qendedc iPCKBY : INTEGER:-1();

4.19

4660

461

Fort (

writeg: IN BIT_VECTOR() for 2 );

writeg: IN BIT_VECTOR() for 2 );

writeg: Out BIT_VECTOR() for 2 );

data_in: IN INTEGES_VECTOS() for 1 );

read_req : IN BIT:

read_req : OUT BIT;

data_out : OUT INTEGES ();

sendes() channel;

466

464

464

466

4619

467

466

469

and sendeslichemnel:

.....

4770

architecture | sengeri_channel view of senderl_channel is

4772

47/2

begin

process

477.1

4774

veriable PCALL + INTEGER := 1 :

475

constant mb_sendar: INTEGER := ( 2 ) :

constant queue_sion: INTEGER := ( 1024 ) :

470

477

--IntObject_genSTypDof--MARNING, maybe type is re-derined hore:

type INTEGER_VECTOR is array | MATURAL range <> ) of INTEGER.

472

479

variable queue : INTEGER VECTOR(1 to queue_size) ;

variable queue_in_phr : INTEGER := ( 1 ) ;

variable queue_nuh phr : INTEGER := ( 1 ) ;

variable indice : INTEGER := ( 1 ) ;

type controllerSTATE_TYPE := ( Init, send_receive );

460

461

462

463

variable controllerMEXT_STATE . controllerSTATE_TYPE := Init:

```

```

137

tecin

184

489

490

hase combrollerNEXT_STATE is

491

492

when Init i ->

queve_in_prv -- 1 :

queve_ingrv -- 1 :

queve_out_gar -- 1 :

indice -- 1 :

controllerNEWT_GTATB := send_receive :

493

154

455

496

497

when recd_seceive : to

498

-- Not Defined_PacactObject_genEVNDL

499

:1.0

:": .

end case :

16.20

and process :

::: •

504

⇒od sendort channel view:

575

library (YMOPSYS)

506

507

508

use SYNOPSYS, accomitenes in the

Inbracy WORK:

509

use WORK.send_waitpkg.4.1;

511

-----

entity counter_channe: (s

qeneric/ ISONEY - INTEGER:=1);

512

513

generic/ 1908E9 -

Post (

514

wr_req: IN SIT_VECTOR(1 to 2 );

wr_rdy: OUT BIT_VECTOR(1 to 3 );

wr_avk: OUT BIT_VECTOR(1 to 3 );

data_in= IN INTEGER_VECTOR(1 to 3 );

516

517

9.9

read_req : IN BIT;

read_rdy : OUT DIT;

dats_out : OUT INTEGER

520

52:1

922

end nounter channel:

503

-----

Architecture | counter_channel_view of counter_channel is

504

506

506

process

927

509

509

variable FCALL : INTEGER := I :

Congrant the sender. INTEGER := : 2 | :

Congrant quade side: INTEGER := : 1024 : :

TorSopeor gonETypEof--WARNING, maybe type is re-defined here:

F37

F31

Incompose gonBTypEof--WARNING, maybe type is re-defined here;

ryme integer vector is array ( NATURAL range <> ) of intEGER* vector() to queue_site* ( vectable quote to ptr : integer := ( _ _ ) ),

vectable quote to ptr : integer := ( _ _ ) ;

vectable quote to ptr : integer := ( _ _ ) ;

vectable quote_our_por : integer := ( _ _ ) ;

vectable indice : integer := ( _ _ ) ;

type control(e)(TATE_TYPE is ( Intr, send receive );

vectable control(e)(TATE_TYPE := control(etSTATE_TYPE := intt;

573

524

525

536

537

529

509

540

begin

541

542

case controllerNEXT_STATE is

540

544

445

when( Init ) as

quene_in_ptr == l /

quene_out_ptr == l /

ierite

946

:47

indice := 1 :

tentroller&BXT_GTATE -- send_vecervo :

949

449

950

when: send_reveive : ->

951

-- Not Defined ParactObject_genBVEDL

952

990

end case :

554

5115

556

end process :

557

end counter_channel_view:

556

library mv1_7:

use mv1_7.TYPES.all:

use mv1_7.arithmetro all:

559

560

561

entity DU_system_send_ward (A

562

qeneric( 120KEY : INTEGER: *1);

563

Port (

564

end DU_system_send_wait:

erchitecture Structure of DU_system_send_wait is

565

556

```

```

signal W_1 : BIT_VECTOR(1 to 2 ) : signal W_2 : BIT_VECTOR(1 to 2 ) : signal W_3 - BIT_VECTOR(1 to 1 ) : signal W_4 - ENTENSET_VECTOR(1 to 2 ) ;

569

569

370

471

K_5 DIT

572

signal

573

signal

K_6 : DIT :

574

575

signal

NIT : INTEGER :

N 1 : UST_VECTOR(1 to 2 ) :

N 2 : UST_VECTOR(1 to 2 ) :

N 3 : UST_VECTOR(1 to 2 ) :

signal

576

577

signa:

M 4 : INTEGER_VECTOR(1 to 0 ) :

M 4 : INTEGER_VECTOR(1 to 0 ) ;

M 6 : Bit :

M_6 : Bit :

M_7 : INTEGER :

ergna:

570

579

signe:

signal

580

signai

581

signal

M_1 : INLEGAR :

M_1 : BIT VEXTOR(1 to 2 : :

M_2 : BIT VEXTOR(1 to 2 : :

M_3 : BIT VEXTOR(1 to 2 : :

M_4 : INTEGER VECTOR(1 to 2 : :

582

signal

583

damped

signal

584

585

signal

signal N_S : BIT :

signal N_S : BIT :

386

987

signal N.7 : INTEGER :

584

589

component EC counter

generic( IPCEEY : INTEGER:=1);

590

591

E92

Post I

we req: IN BIT_VEXTOR(1 to 0 ): while the corr bit_VECTOR(1 to 2 ); while between sets of bit_VECTOR(1 to 2 );

503

504

505

data in: IN INTEGER_VECTOR(1 to 3 ):

506

read_reg : OUT BIT:

read_rdy : IN BIT:

data_out : IN INTEGER

537

538

539

end component:

630

component DU_receiver1

generic: IPCKBY: INTEGER:-1;:

604

602

600

Port :

wc_teq= IN RTT_VECTOR(1 to 2 ):

wc_tdy= OUT RTT_VECTOR(1 to 2 ),

wc_ack= OUT RTT_VECTOR(1 to 2 ),

wc_ack= OUT RTT_VECTOR(1 to 2 ),

data_in: IN INTEGER VECTOR(1 to 2 )

read_reg: OUT RIT:

read_rdy: IN RTT;

604

635

636

603

608

609

data_out : IN INTEGER

610

authorized base

éi Li

611

component counter_commet

613

deneric: IPCKEY : INTEGER:-1);

Port (

614

wr req: IN BIT_VECTOR(1 to 2 ),

wr rdy, our BIT_VECTOR(1 to 2 );

wr ack, our BIT_VECTOR(1 to 2 );

515

515

517

data in: IN INCOMER_VECTOR(1 to 2 );

513

read req : IN EIT:

read rdy : DUT BIT:

dara but : DUT INTEGER

510

520

531

920

end component,

923

komponent EU semderi

generic: IDCKEY : INTEGER:=1).

524

wr_req: IN BIT_VECTOR(1 to 2 );

wr_rey: OUT BIT_VECTOR(1 to 2 );

wr_ack: OUT BIT_VECTOR(1 to 2 );

526

527

529

dona_on: IN INTEGER_VACTOR(1 to 2 ):

600

read_req . Off Bir:

read_rdy . IN Bir:

data_out . IN INTELER

630

931

63.2

630

end component:

component sender: channel generic! CPCRBY : CRTEGER. =1):

635

636

Port 1

wr_req: IN EIT_VECTOR(1 to 2);

wt_rdy: OUT BIT_VECTOR(1 to 2 );

wr_nck: OUT BIT_VECTOR(1 to 2 );

data in: IN INTEGER_VECTOR(1 to 2 );

tread edg : IN UIT;

tread edg : OUT BIT;

data out : OUT BIT;

637

638

639

640

540

540

543

and component;

544

component receiverl_channel

645

generic: IFCKEY : INTEGER:-1);

646

Port :

647

wr_req: IN BIT_VECTOR(1 to 2 );

wr_rey: Our BIT_VECTOR(1 to 2 );

643

649

```

```

wriack: OUT BIT_VECTOR() for 0 ): data in. IN INTEGER_VECTOR() for 1 ). read req : IN DIT: read rdy : OUT BIT:

650

á'n.

6152.

453

dans but : OUT INTEGER

9.5

554

555

end component:

556

557

counter : DU_counter

658

659

General Map + 1908EY #8 1)

600

861

Post Map :

read require 5,

602

read odv-PN 6,

cara but-PN 7

863

::

564

received1 : DU_receiver1

| Genetic Hap | TROKEY | v 2)

ists i

Bush

#BY

564

Fort Map:

w_{2,2,2} \in \mathbb{N}_{+} \times \mathbb{N}_{+}

669

671

671

672

673

w z \bot z d y z \circ N \bot 2 \; .

wr zck=>N_3.

data in: >N_4.

read req=>N_5;

rmad réyabbió

daha mutabbi T

674

675

676

676

679

686

FORE Pack

ar\_req->N-1\;,

wr_rdy-bN_0,

wr_ack-bN_s,

A4:

642

data_js=>N_4.

read_req=>N_5.

read_rdy=>N_6.

64.1

644

645

data_out->N_V

Ι,

646

Sender: 30_sender: Sender: 30_sender: 30_sen

697

ARA

699

690

Post Hage

wc_ceq=*3_1.

691

we_{-}edy = 89_{-}^{-}2

69%

walack-split.

693

694

data_in=>K_4

555

read_reg=>N_3.

read cdy=>N_8.

556

597

data out=>N_7

genderlichannol . denderlichannel

699

690

Genernic Map ( IFCMEY => 5)

700

701

Pown Map (

wr req=>N_1

wr rdy=>N_1

wr wck=>N_3

702

703

704

705

date in=>N_4

705

read req=>N_5.

707

read rdy=>N_6

709

daha buterN_7

receiver(_rhannal : raceiver(_vhannel

Generic Map ( TPTXEY => $)

703

3.10

711

010

Port Map+

713

wr\_req=>K_11.

714

w_1 = r dy + s K_1 U_1

wr_ack->N_s,

date_in=>N_4.

715

716

717

read_xeq=>N

read_rdy=>N 6.

data_out=>N 7

718

1:

719

720

721

722

723

724

725

726

end Stractuse:

configuration DU_system send_wait_Structure of DH system send_wait is

for Structure

for counter - EG counter

Use entity work.BU counter(counter_behaviour), end for:

for receiver: - BU roceiver1

use entity work.BC receiver[(receiver(_necavicur),

727

726

end loca

tor counter_channel : counter_channel was entity work.counter_channel(behaviour);

729

730

end tor:

```

```

Tor sendar1 : DO[sender]

To use entity work.DO[sender](CLI);

To end tor;

Tor sendar1_channel : sender[_channel]

Tor sendar1_channel : sender[_channel]

To end for;

Tor receiver[_channel : receiver[_channel]

To end for:

```

Annece D. Exemples on SDL

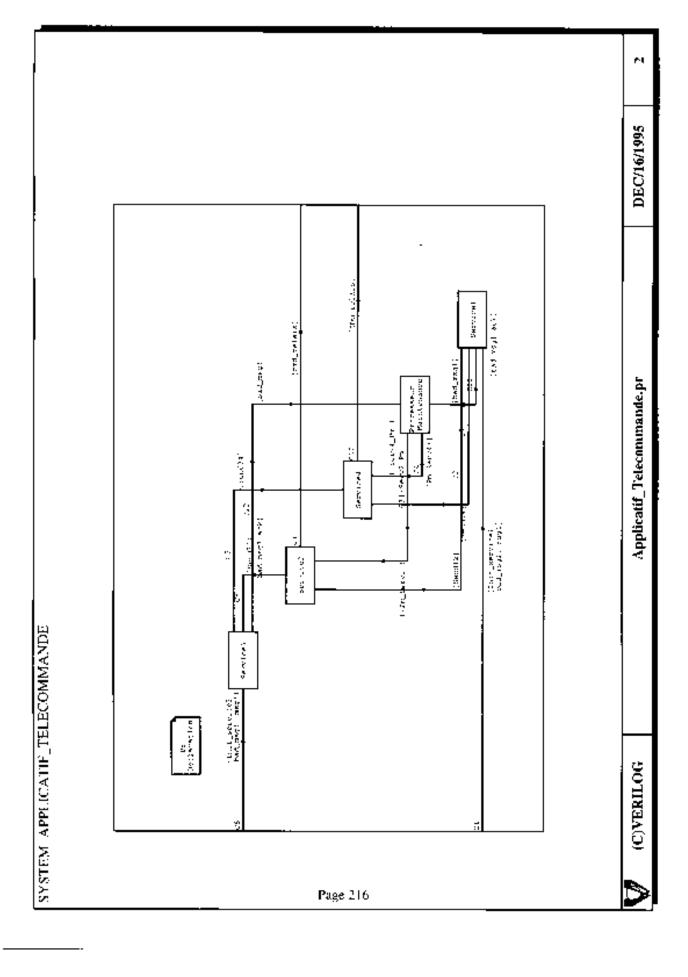

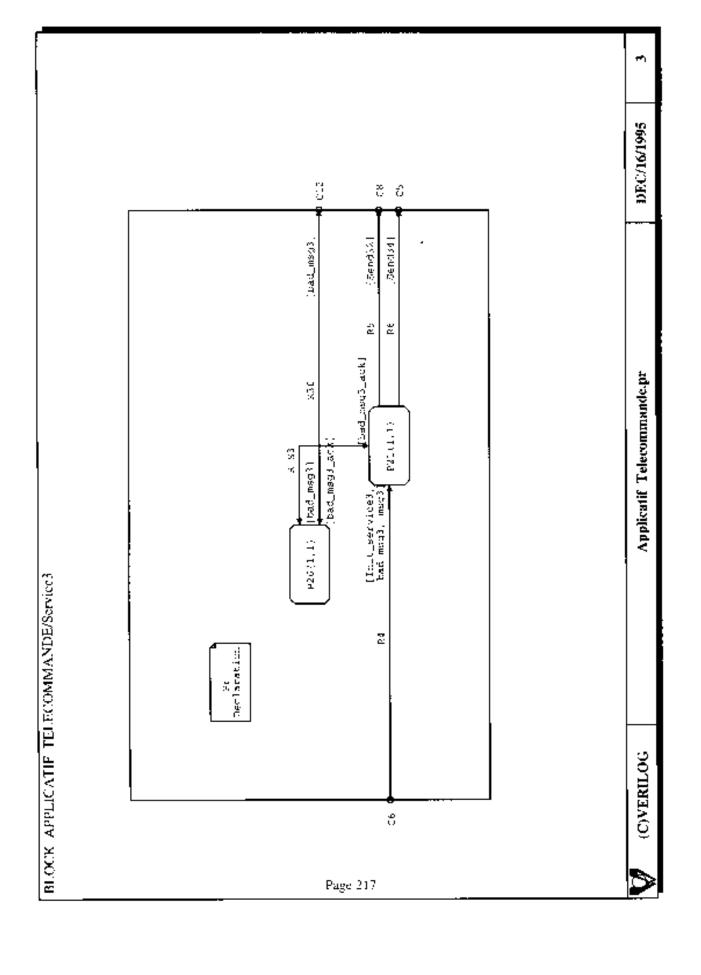

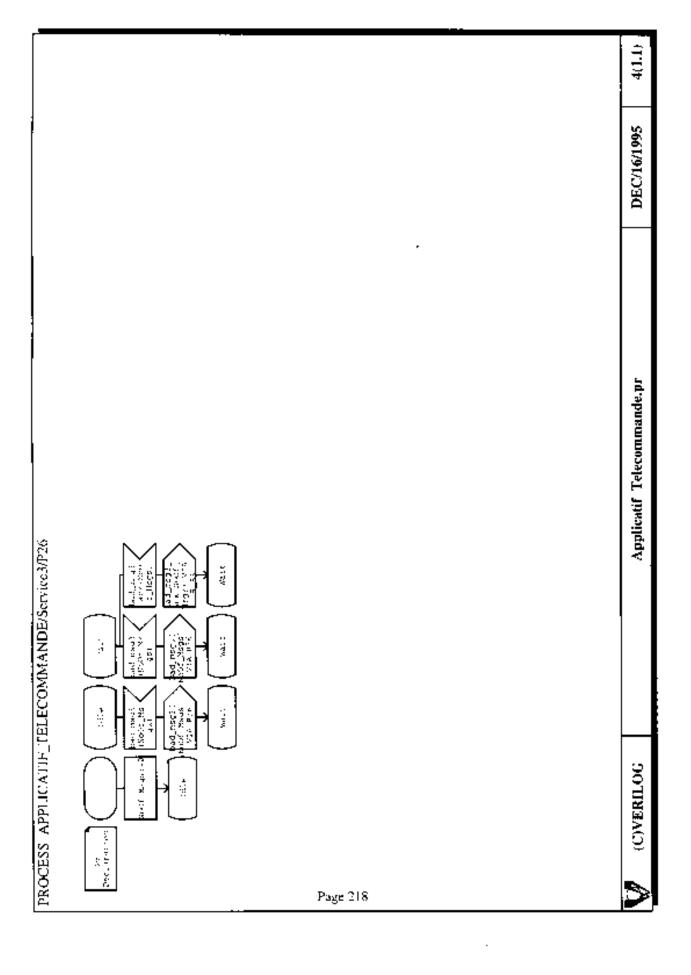

## D.2. Bloc télécommande d'un satellite

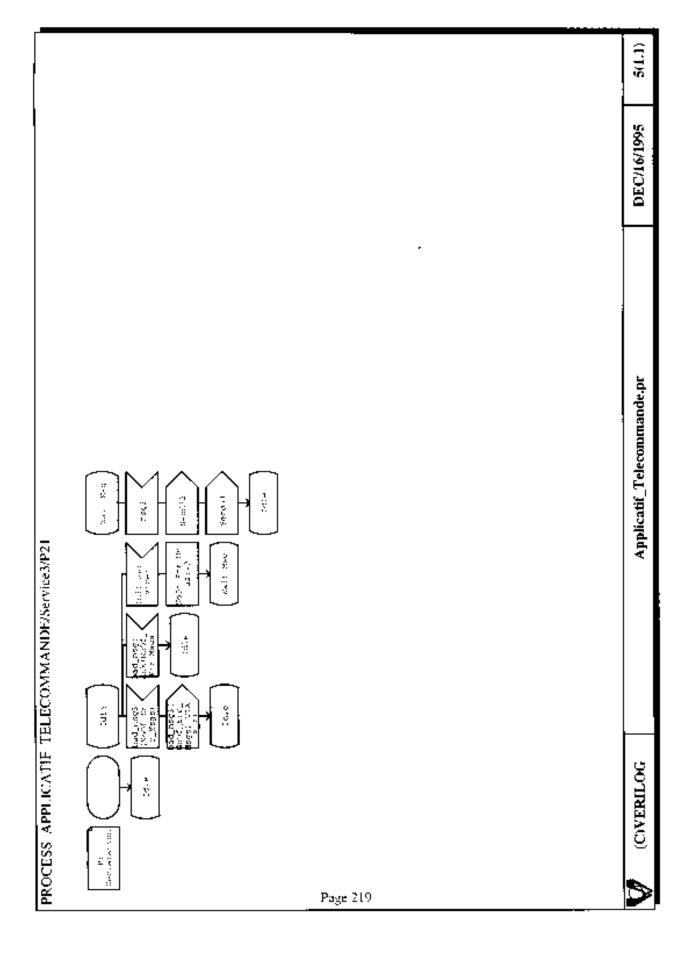

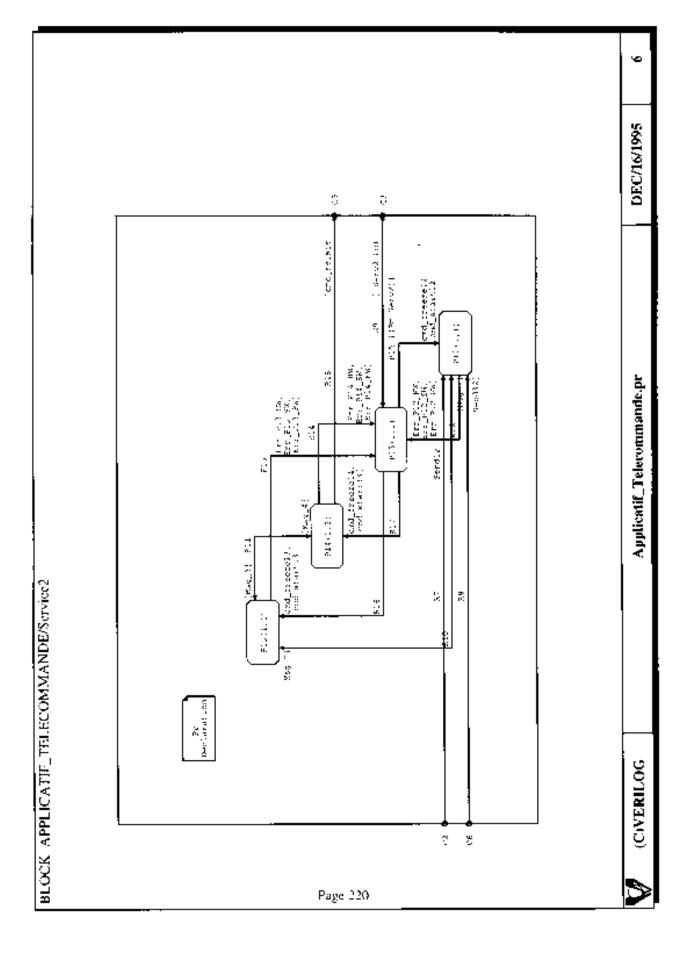

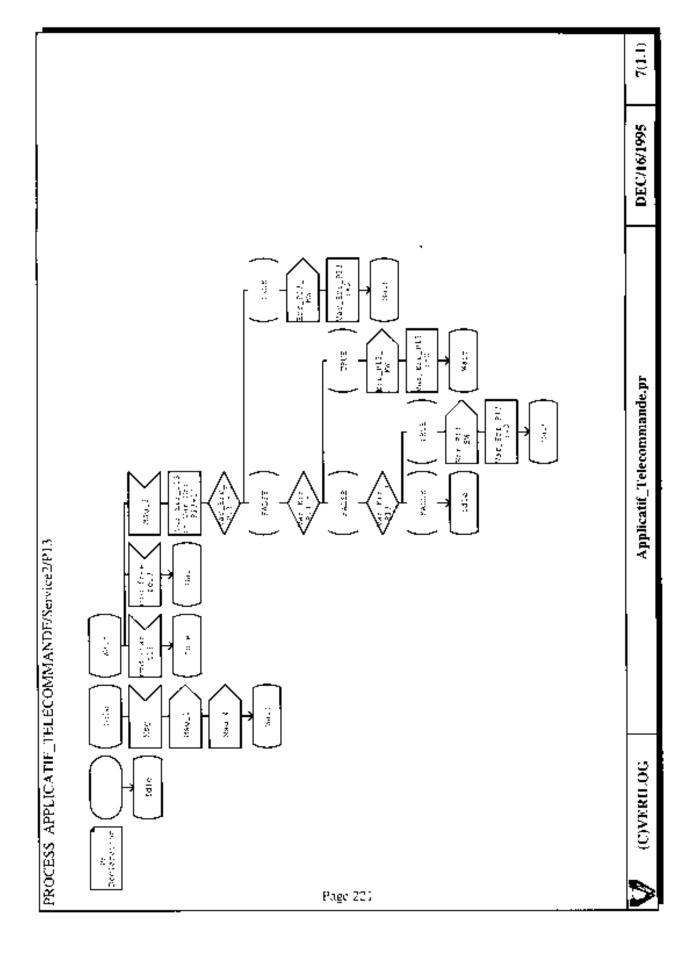

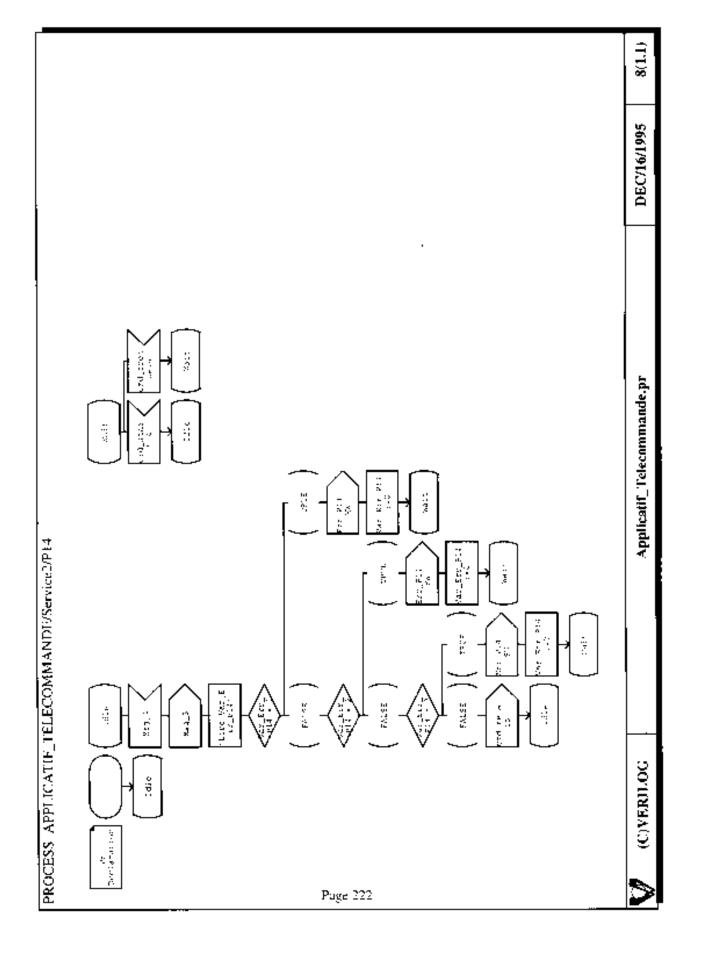

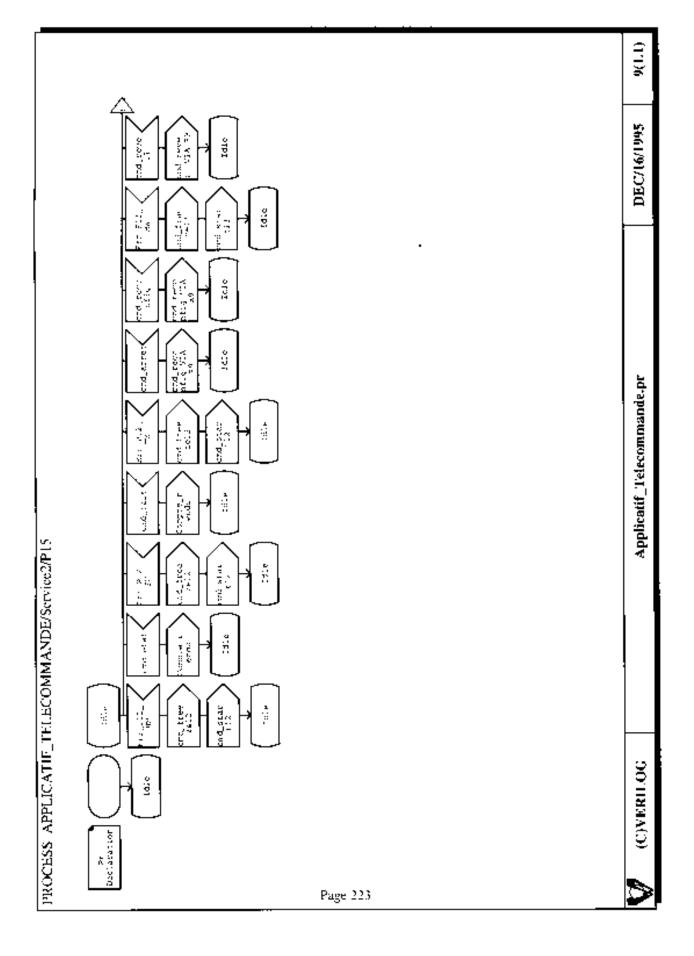

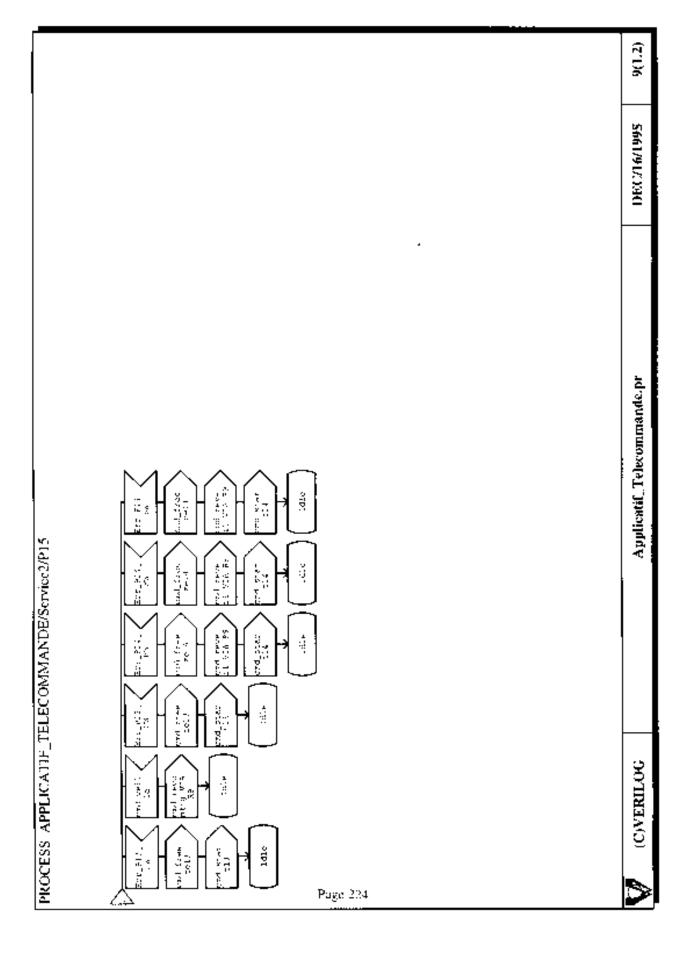

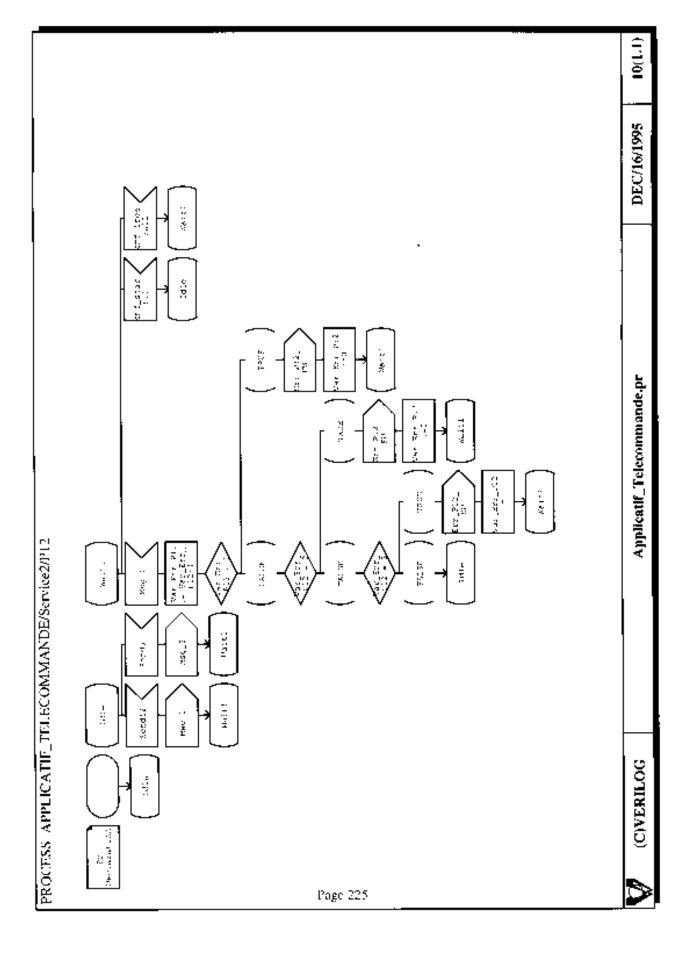

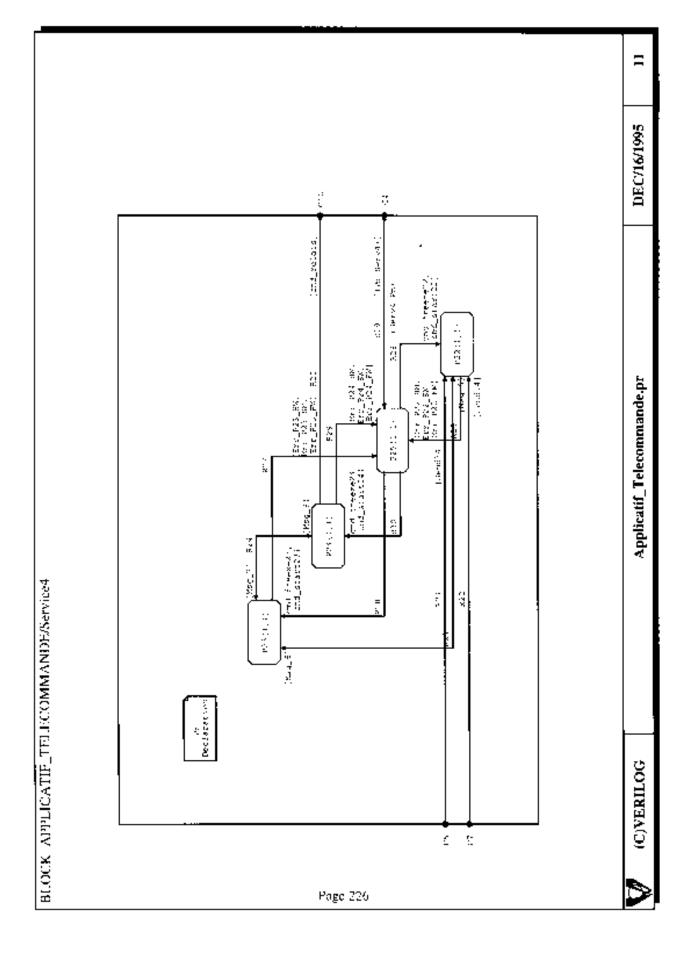

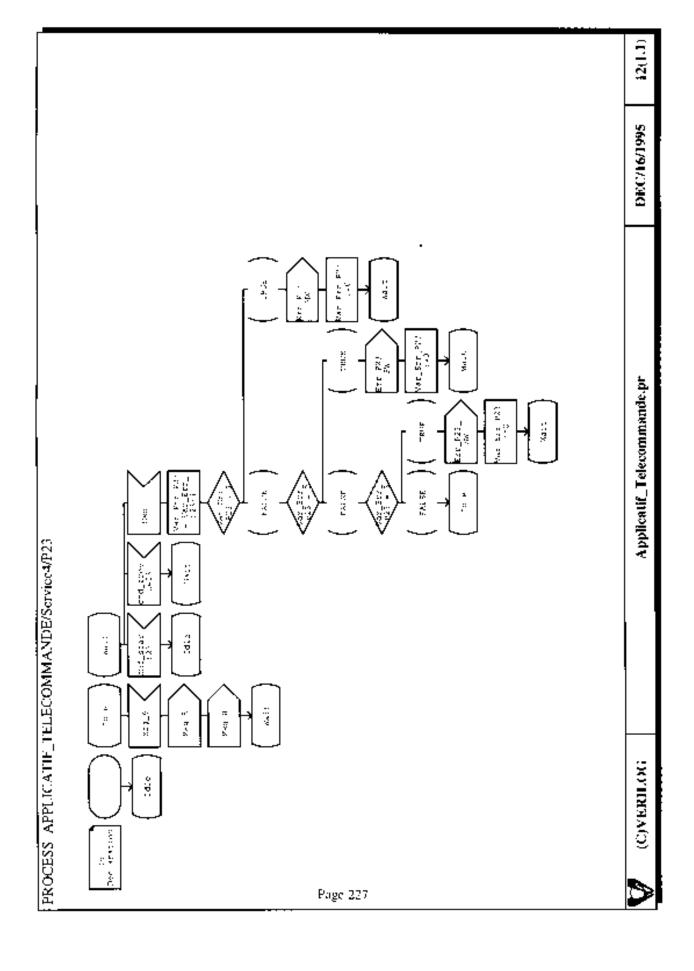

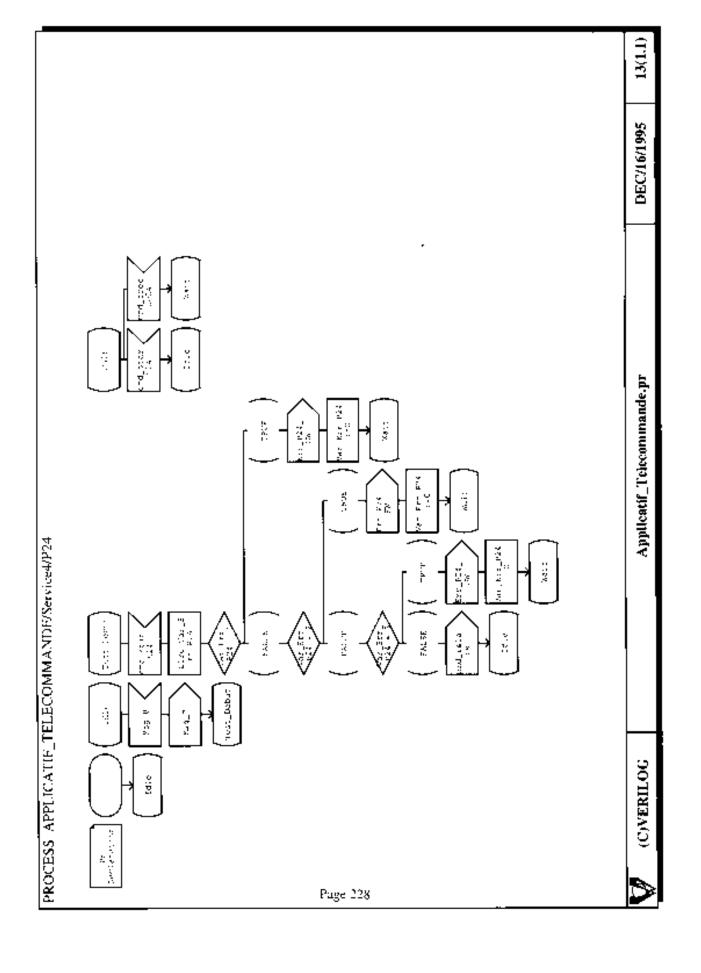

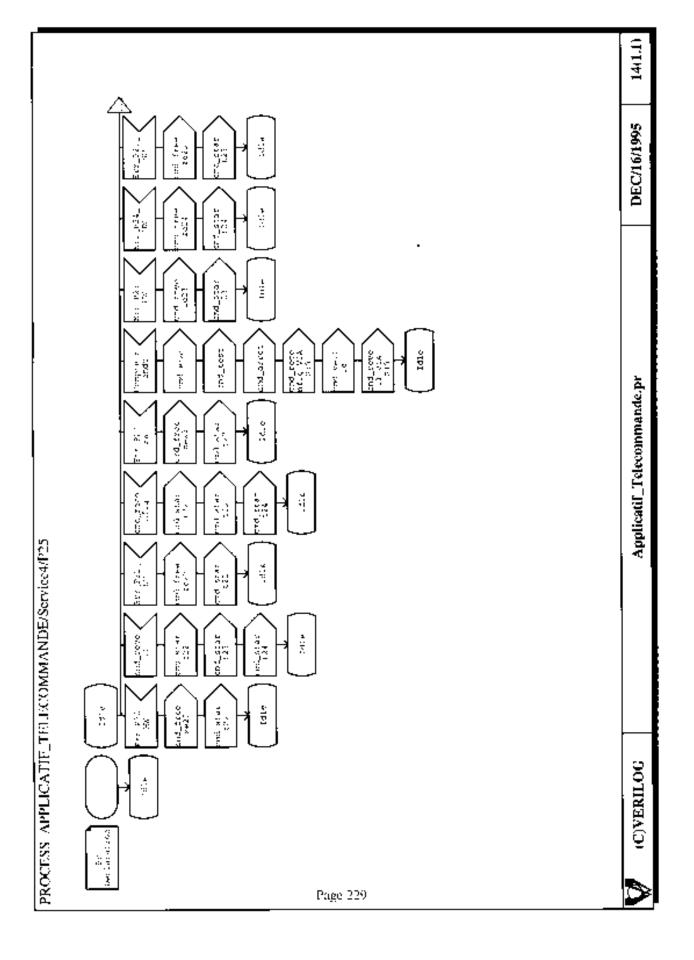

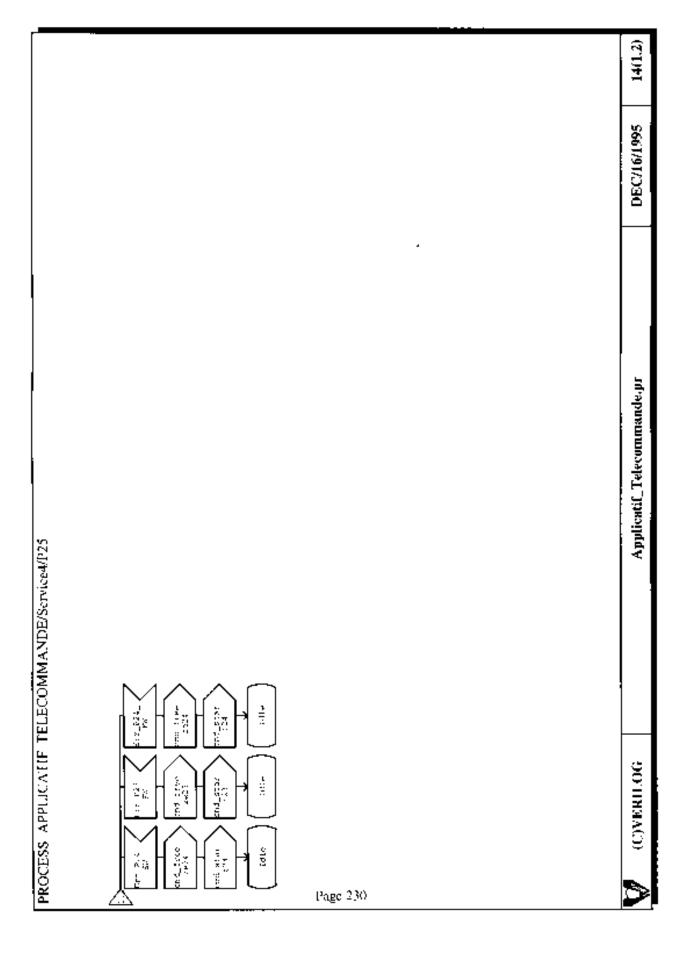

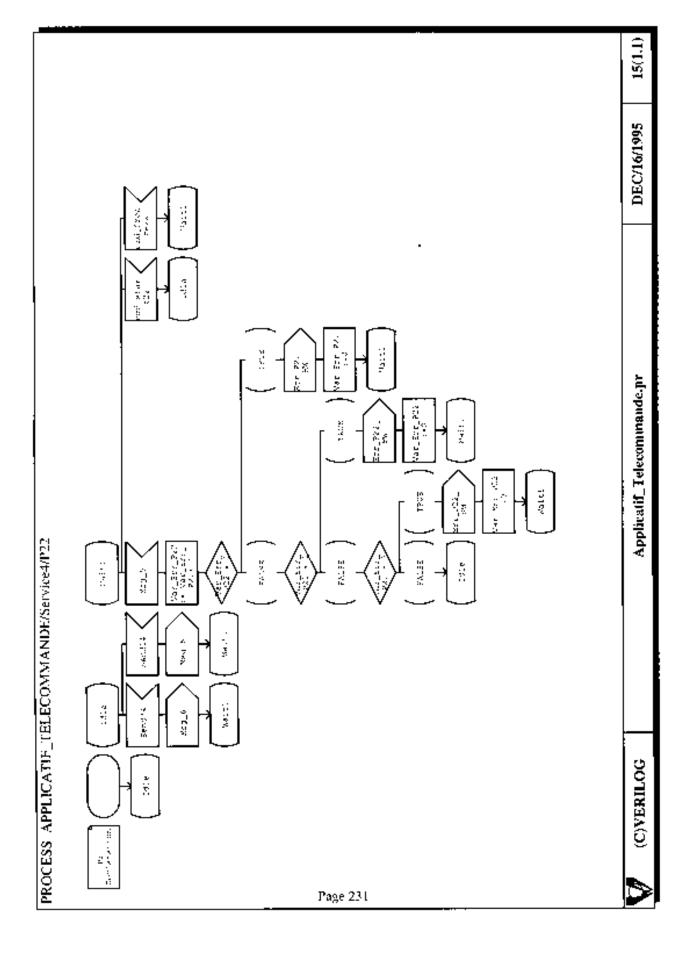

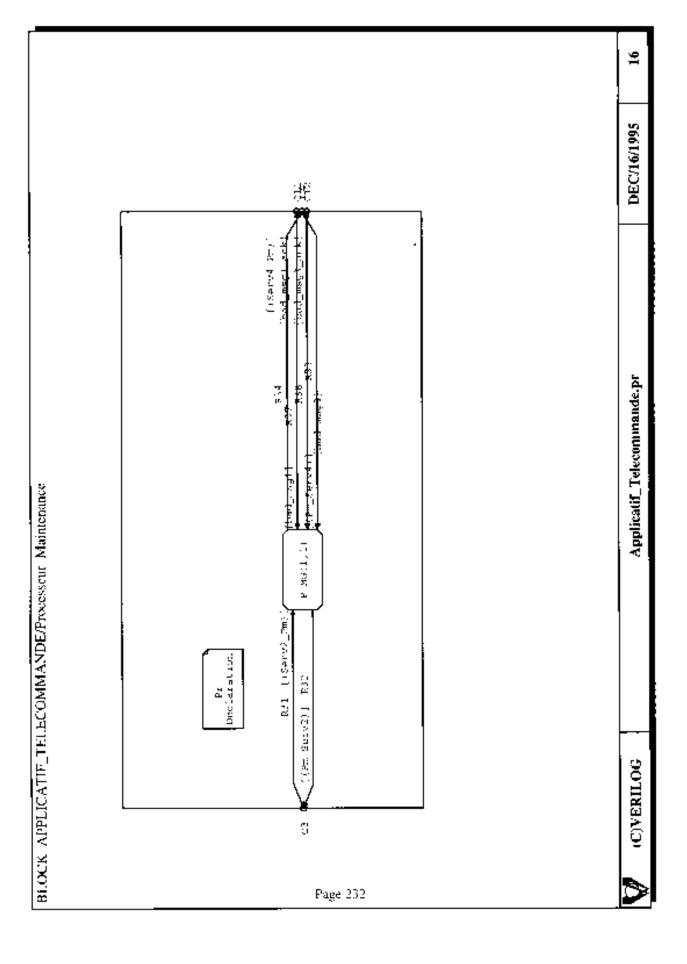

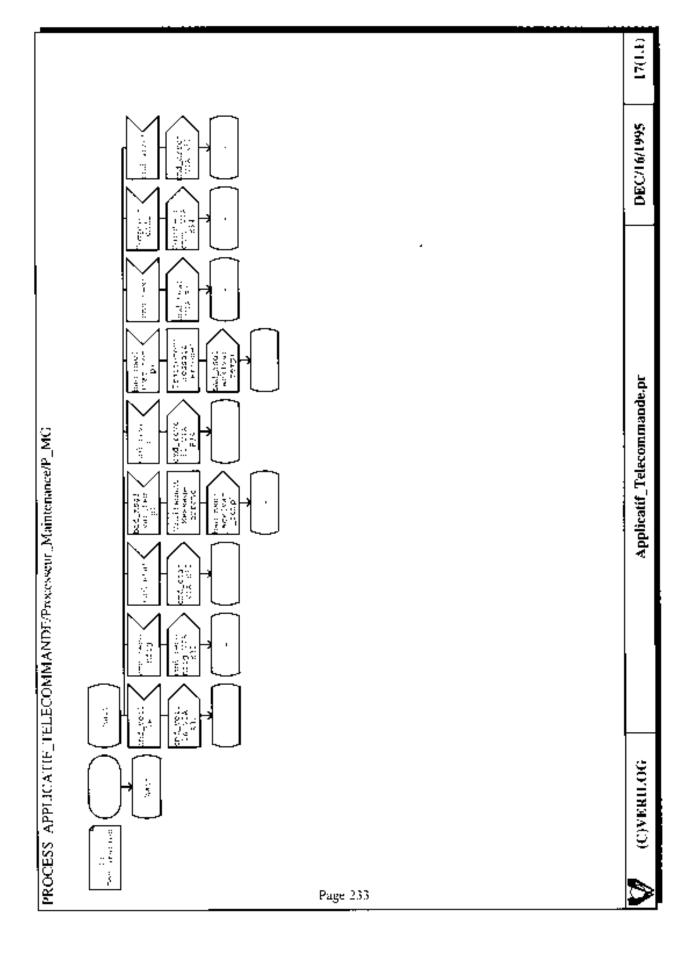

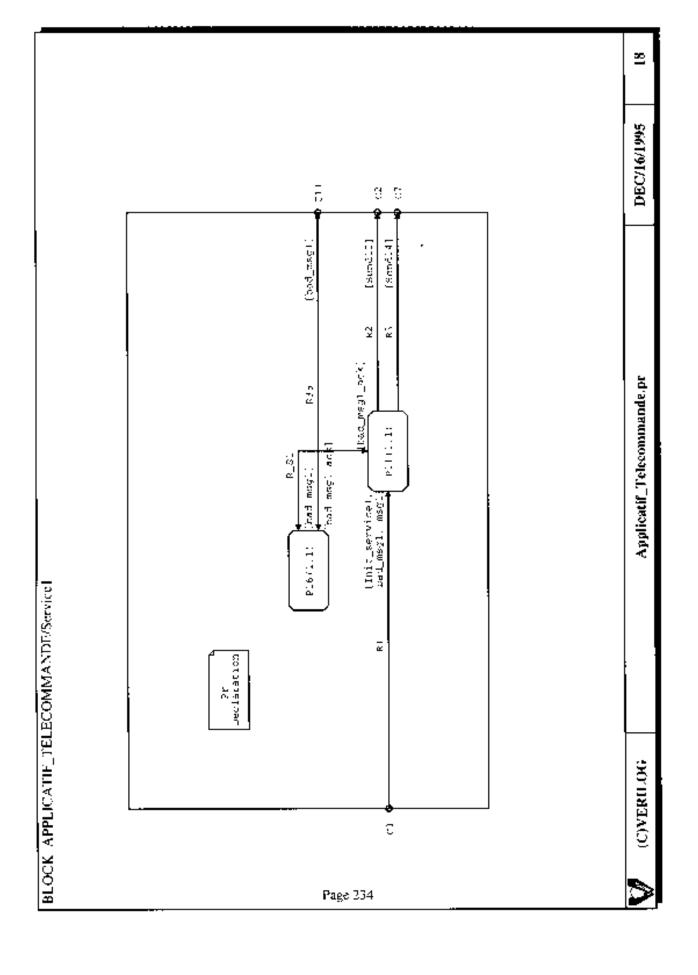

Dans ce qui suit, l'exemple de l'applicatif rélécommande d'un satellire, qui a été décrit dans le chapitre 4 (figure 4.13), sora présenté à travers sa description en SDL. Il s'agit d'un système très simplifié dont l'objet est de prendre en considération les aspects de maintenance dès la phase de spécification. Dans cet exemple les blocs SDL appelés "service1" et "service3" sont identiques. De même les blocs SDL appelés "service2" et "service4" sont identiques. Ils intègrent chacun des processus équivalents qui permettent de réagir en cas de défaillances. Le bloc appelé "Processeur\_Maintenance" comporte un processus de maintenance global de tout le système

Description en SDL graphique du bloc, simplifié, de télécommande d'un satellite qui est présenté à la figure 4.13

Annexe D. Exemples en SDL

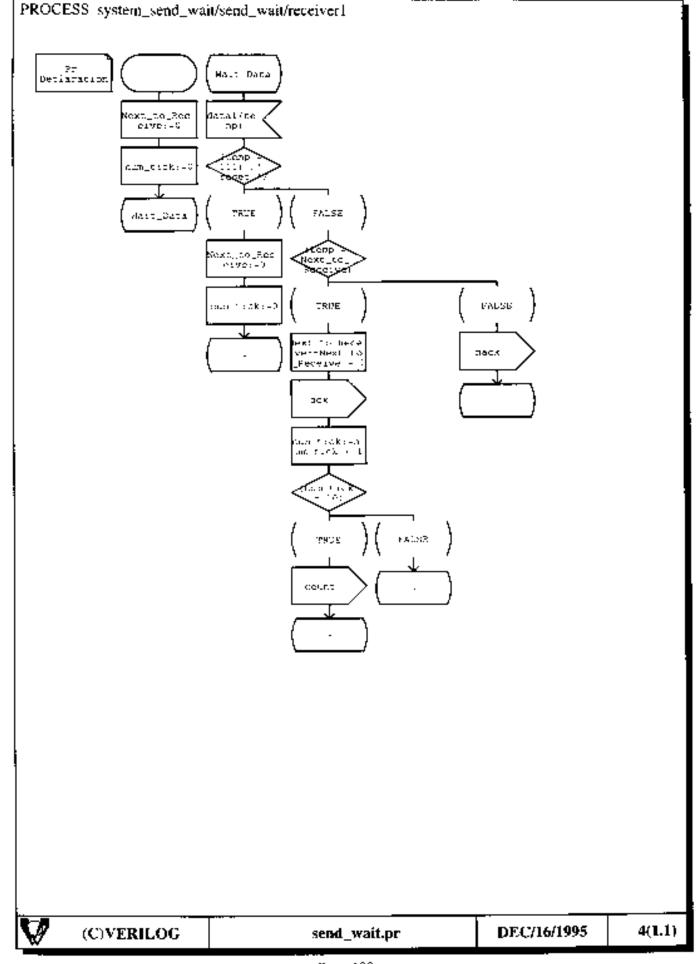

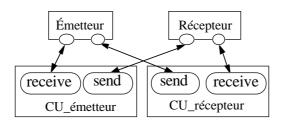

# D.1. Système émetteur/récepteur

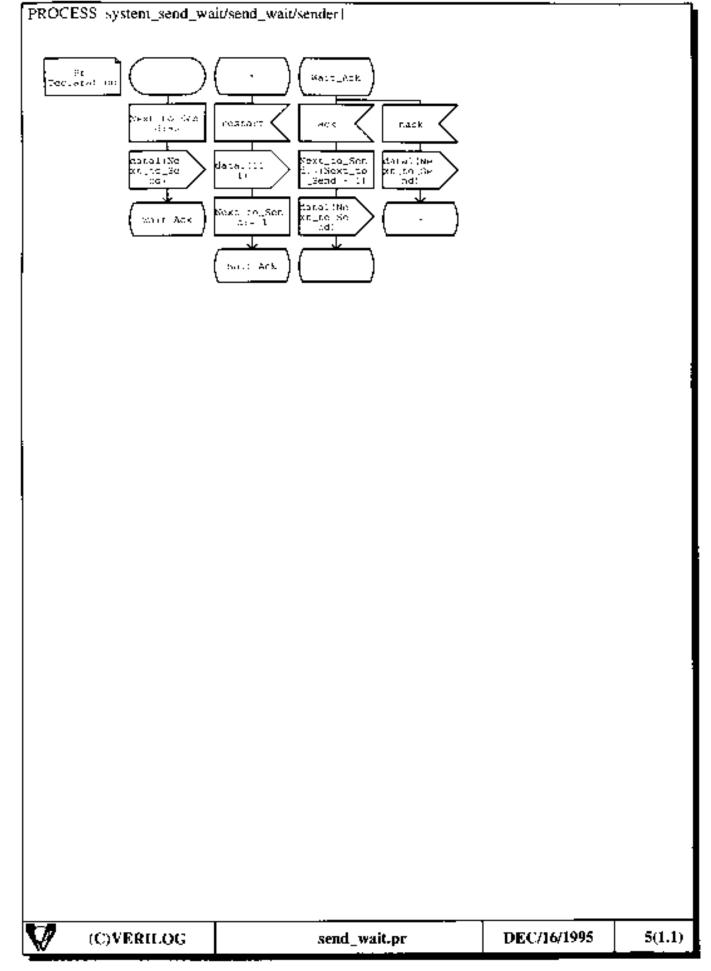

Ce système est composé de deux blocs; le premier, appelé "send\_wait", est composé des deux processus émetteur et récepteur; le deuxième, appelé "environnement", modélise l'environnement. Ce dernier bloc contient un processus, appelé "counter", qui incrémente une variable à chaque fois que le processus récepteur reçoit dix messages.

Dans ce qui suit les notations utilisées dans SDL graphique sont décrites.

| Déclarations                 |

|------------------------------|

| Bloc                         |

| Processus                    |

| État initial                 |

| État                         |

| Retour à l'état<br>précédent |

| Émission                     |

| Réception                    |

|                              |

### C.1. Introduction

L'objet de cet annexe est de présenter les algorithmes des différentes primitives de découpage et de synthèse de la communication qui ont été présentées dans les chapitres 5 et 6. Tout d'abord, les notations qui seront utilisées dans ces algorithmes seront proposées.

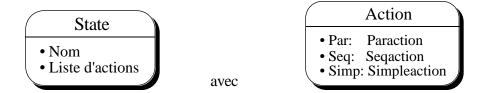

En Solar, un état (State) est défini par les attributs suivants :

Paraction (resp. Sequetion) est un constructeur qui définit des actions parallèles (resp. séquentielle). Le constructeur Simpleaction désigne une instruction simple tel qu'une affectation ou bien une instruction conditionnelle.

**Notation :** parent(A, B) est la machine qui contient les deux machines A et B.

A précède B dans parent(A, B) si l'entrée par défaut de parent(A, B) est A.

Le signe '+' sera utilisé pour représenter l'opérateur de concaténation et 'U' dénote l'opérateur d'union.

```

\{ N_X \text{ est le nom de la machine } X \}   \{ G_X \text{ est l'exception de la machine } X \}   \{ S_X \text{ est la liste des états dans la machine } X \}   \{ E_X \text{ est la liste des états d'entrée de la machine } X \}   \{ D_X \text{ est l'état suivant par défaut dans la machine } X \}   \{ R_X \text{ est l'état de réinitialisation de la machine } X \}   \{ V_X \text{ est la liste des variables de la machine } X \}   \{ Block_X \text{ est la liste des états et tables d'états de la machine } X \}

```

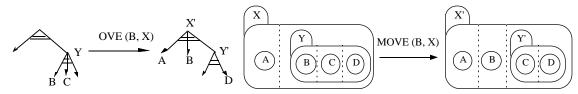

## C.2. Primitive Move

## Algorithme:

```

Move (P, Q)

<u>début</u>

cas de chemin entre P et Q

: \; \mathsf{Par}_Q := \; \mathsf{Par}_Q \; \; \mathsf{U} \; \; \{ \; \mathsf{P} \; \}

Parallèle

Enlever la machine P de Parparent(P)

: \ \mathbf{S}_Q \coloneqq \mathbf{S}_Q \ \mathbf{U} \ \{ \ \mathbf{N}_P \}

Séquentiel

\underline{si} (EQ = N<sub>parent(P)</sub>) et (E<sub>parent(P)</sub> = N<sub>P</sub>)

\underline{alors} E_Q := \{ P \} U E_Q

<u>fsi</u>

V_Q := V_Q U V_{parent(P)}

V_{parent(P)} := \emptyset

\mathsf{Block}_Q := \mathsf{Block}_Q \ U \ \{\ P\ \}

Enlever N_P de E_{parent(P)}

Enlever N_P de S_{parent(P)}

Enlever la machine P de Block<sub>parent(P)</sub>

<u>fcas</u>

si P table d'états alors

{ héritage par P de l'exception de parent(P)}

G_P \coloneqq G_P \ U \ G_{parent(P)}

<u>fsi</u>

<u>fin</u>

```

# C.3. Primitive Merge

## Algorithme:

```

Merge (A, B)

<u>début</u>

cas de B

table d'états : N_{AB} := N_A + N_B

G_{AB} := G_A \cup G_B

si A précède B dans parent(A,B) alors

D_{AB} := D_A

E_{AB} := E_A \cup E_B

<u>sinon</u>

\mathrm{D}_{AB} := \mathrm{D}_{B}

E_{AB} := E_B U E_A

<u>fsi</u>

R_{AB} := R_A

S_{AB} := S_A \cup S_B

V_{AB} := V_A \cup V_B

Block_{AB} := Block_{A} \cup Block_{B}

\acute{e}tat : N_{AB} := N_A

G_{AB} := G_A

D_{AB} := D_A

si B précède A dans parent(A,B) alors

E_{AB} := \{ B \} U E_A

<u>sinon</u>

E_{AB} := E_A

<u>fsi</u>

R_{AB} := R_A

S_{AB} := S_A U \{ N_B \}

V_{AB} := V_A

Block_{AB} := Block_A U \{ B \}

<u>fcas</u>

<u>fin</u>

```

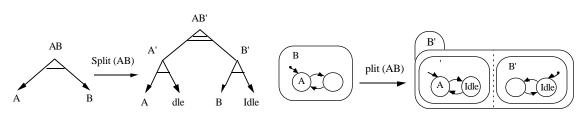

## C.4. Primitive Split

La primitive *Split*. possède un seul paramètre qui représente une MEF étendue. On fait l'hypothèse que la machine à découper est séquentielle.

```

\{ \ X : représente \ la \ machine \ à \ découper \ \}   \{ \ n : représente \ le \ nombre \ de \ machines \ dans \ la \ machine \ X \ \}   \{ \ X_i : représente \ l'une \ des \ n \ machines \ de \ X \ \}   \{ \ ctrl\_X_i : représente \ le \ signal \ de \ contrôle \ créé \ pour \ contrôler \ la \ machine \ X_i \}

```

### Algorithme:

```

\begin{array}{l} \underline{Split}\,(X) \\ \underline{d\acute{e}but} \\ \underline{pour}\,\,i=1\,\,\grave{a}\,\,n\,\,faire \\ V_{Parent}(X) \coloneqq V_{Parent}(X)\,\,U\,\,\left\{\,\,ctrl\_X_i\,\,\right\} \\ \underline{fpour} \\ \underline{pour}\,\,i=1\,\,\grave{a}\,\,n\,\,faire \\ \underline{cas\,\,de}\,\,X_i \\ \underline{s\acute{e}quentielle}:ActionSeq\,(X_i) \\ \underline{parall\grave{e}le}\,\,:ActionPar\,(X_i) \\ \underline{fcas} \\ \underline{fpour} \\ \underline{fin} \end{array}

```

Dans la première boucle les signaux de contrôle sont rajoutés dans la machine, notée Parent(X) et qui contient la machine à découper X. Les n sous-arbres de la machine hiérarchique X sont représentés par des machines  $X_i$  ( $i \in [1..n]$ ). Dans la seconde boucle, chaque sous-arbre de X est traité, selon qu'il s'agit d'une machine séquentielle ou d'une machine parallèle. Les fonctions ActionSeq et ActionPar ont chacune un paramètre. Il représente la machine à traiter qui est séquentielle pour la fonction ActionSeq et parallèle pour la fonction ActionPar. Chaque fonction introduit un état de repos (Idle) et transforme les transitions externes en affectations de signaux de contrôle. Par exemple, si dans la machine  $X_i$ , on a une transition vers la machine  $X_j$ , on transforme cette transition en la séquence suivante :  $\{ctrl_X_i := 0, ctrl_X_j := 1, \text{ état suivant} := Idle\}$ .

## C.5. Primitive Cut

Soit M une machine parallèle sur laquelle la primitive Cut va être appliquée. On suppose que cette machine contient n machines (sous-arbres de M)  $M_i$  ( $i \in [1..n]$ ) qui sont composées en parallèle. L'algorithme de la primitive Cut peut être défini comme suit:

#### **Algorithme:**

```

Cut (M)

<u>début</u>

pour chaque machine Mi dans M faire

Créer un bloc UC<sub>i</sub> (unité de conception)

Mettre Mi dans UCi

pour chaque Port qui est partagé et utilisé dans Mi faire

Créer un port dans Interface de UCi

fpour

pour chaque Constante qui est partagée et utilisée dans Mi faire

Déclarer la constante dans Mi

fpour

pour chaque Variable V qui est partagée et utilisée dans Mi faire

Ajouter dans la spécification, un canal relatif à V

Ajouter dans Interface de UCi un accès au canal de V

pour chaque utilisation de V faire

si accès en lecture alors

appeler la méthode Read du canal

<u>sinon</u>

appeler la méthode Write du canal

<u>fsi</u>

<u>fpour</u>

<u>fpour</u>

fpour

<u>fin</u>

```

# C.6. Primitive Map

Soit un ensemble de sous-systèmes communicants sur lesquels la primitive *Map* va être appliquée.

## Algorithme:

```

<u> Map</u>

début

<u>pour</u> chaque bloc UC (Unité de Conception comportementale)

pour chaque Accès dans l'interface

Identifier le canal correspondant

pour chaque appel à ce canal

Déclarer la méthode comme procédure au niveau de l'UC

Insérer les ports qu'elle utilise dans l'interface de l'UC

Transformer l'appel à la méthode en un appel de procédure

fpour

Enlever l'accès de l'interface de l'UC

Enlever toutes les méthodes du canal

Déclarer le canal comme une UC

<u>fpour</u>

<u>fpour</u>

<u>fin</u>

```

#### **B.1.** Introduction

La présente étude propose une évaluation des principales méthodologies de conception de systèmes mixtes logiciels/matériels [BIsm94b]. Différentes approches sont actuellement explorées, dans des laboratoires de recherches, pour la conception de systèmes mixtes. Dans ce qui suit, les principales méthodologies pour ce domaine seront parcourues. L'accent est essentiellement mis sur les points suivants :

- Le niveau système : Une description brève du contexte système et du style de la description en entrée.

- Le type d'application : Les types d'applications envisagées au niveau système.

- L'approche de conception : Une présentation des étapes suivies pour la conception mixte.

- L'architecture cible : Une vue générale de la plate-forme d'implantation.

- Notes : Autres informations importantes relatives à la méthodologie.

- Références : Références bibliographiques adoptées.

# B.2. Méthodologie de l'université de Californie/Berkeley: (Ptolemy)

**Niveau système**: Au niveau système, l'environnement utilisé est appelé Ptolemy. Les contraintes de conception pour un système peuvent inclure : Les contraintes temps-réel, performances requises, vitesse, surface, taille du code, consommation de puissance et la programmabilité.

**Types d'applications**: Applications de traitement du signal [Hilf85, PaLi94] (DSP: *Digital Signal Processing*) et systèmes communicants. Le logiciel est formé par un ou plusieurs programmes, souvent assez complexes, s'exécutant sur des composants programmables.

**Approche de conception** : L'approche est formée par une étape de découpage matériel/logiciel, une étape de synthèse de logiciel, une étape de synthèse du matériel et

une étape de synthèse d'interfaces matériel/logiciel. Une dernière étape concerne la simulation du système hétérogène.

Le découpage est fait manuellement. Il est guidé par les contraintes de surface, de vitesse et de flexibilité. Lors de la synthèse du logiciel pour une architecture multiprocesseurs, le découpage essai d'optimiser des fonctions coûts telles que : coût des communications, espaces mémoires locales et globales, etc. Des travaux récents [KaLe94b] parlent de découpage automatique.

La synthèse du logiciel consiste en une génération de code pour des processeurs programmables. Le code obtenu pourrait être du C ou de l'assembleur selon le processeur cible. Du côté synthèse du matériel, la description en entrée est un code SILAGE. La synthèse d'interfaces inclut :

- L'ajout de registres, files d'attentes FIFOs, et décodeurs d'adresses dans le matériel, et

- L'insertion du code pour les opérations d'entrée/sortie et les sémaphores de synchronisation dans le logiciel.

La simulation du système hétérogène a lieu une fois que la synthèse du logiciel et du matériel sont faites. Les résultats de la simulation permettent de vérifier si la conception est conforme à la spécification initiale. Cependant, à l'issue des étapes de synthèse du matériel et du logiciel, quelques estimations de performances sont faites afin de valider la conception. Les estimations concernent la surface, le chemin critique et l'utilisation de bus et de composants.

**Architecture cible** : Le logiciel peut être synthétisé pour une variété de processeurs cibles. Les processeurs cibles peuvent avoir une configuration parmi plusieurs :

- 1. Système mono-processeur,

- 2. Architecture parallèle à mémoire partagée,

- 3. Architecture parallèle avec un bus partagé,

- 4. Architecture avec passage de messages.

Dans [SrBr91], une implémentation basée sur une plate-forme d'architecture paramétrable est discutée. On utilise une bibliothèque de modules matériels et logiciels paramétrables.

**Notes** : Utilisation d'une représentation unifiée entre le matériel et le logiciel. Cette représentation facilite l'émigration de fonctions entre les implémentations.

Références: [KaLe93, KaLe94a, KaLe94b, SrBr91, Sriv92, SrBr93, ChGi93]

# B.3. Méthodologie de l'université de Californie/Stanford: (VULCAN)

**Niveau système**: La description initiale est une description fonctionnelle donnée dans le langage HardwareC. L'approche de synthèse mixte utilise d'autres langages de description de matériel tels que VHDL et Verilog. Les descriptions HardwareC consistent en un ensemble de processus interagissants qui sont instanciés dans des blocs. Un processus s'exécute en parallèle avec d'autres processus de la spécification et ce réinitialise automatiquement à sa terminaison. Il s'agit d'une extension au langage C afin d'inclure le parallélisme et des aspects pour la description de matériel.

Types d'applications : Systèmes temps-réel.

**Approche de conception :** Utilisation de contraintes temporelles. Ces contraintes sont de deux types :

- 1. Contraintes de délai Minimum/Maximum,

- 2. Contraintes de temps d'exécution.

L'estimation des délais d'opérations est basée sur la réalisation envisagée (type du matériel à utiliser et du processeur pour le logiciel). Ainsi, ce type de synthèse est orienté vers l'architecture. Les étapes suivantes sont suivies dans cette approche :

- 1. Prise en compte (saisie) du modèle,

- 2. Partitionnement matériel/logiciel,

- 3. Synthèse du modèle découpé en composants matériels et logiciels interconnectés dans une architecture cible.

L'algorithme de découpage commence avec une partition initiale où toutes les opérations, exceptées celles à délai non limité, sont affectées au matériel. La partition est raffinée par la migration d'opérations du matériel vers le logiciel afin d'obtenir une partition à moindre coût.

L'approche utilise un ensemble de modèles de graphes de séquencement avec des contraintes temporelles entre les opérations. Un ensemble de modèles de graphes de séquencement est réalisé en logiciel et un autre est réalisé en matériel. Le logiciel est composé par plusieurs programmes. Un ordonnancement est effectué sur le modèle du graphe relatif au logiciel. La concurrence entre les processus est effectuée à travers un modèle d'exécution supportant l'entrelacement.

L'interface matériel/logiciel consiste en des files de données et un contrôle qui maintient les identificateurs pour les processus activés dans l'ordre de l'arrivée de leurs données.

**Architecture cible**: L'architecture cible utilise un seul processeur qui est intégré avec un seul circuit intégré (ASIC), une mémoire et un bus. Le processeur utilise un seul niveau de mémoire et d'espace d'adressage pour les instructions et les données.

**Notes** : Utilisation des routines d'interruption pour les transferts de données d'un processus vers un ASIC. Ces interruptions sont associées à un temporisateur.

Références: [GuDM93, GuDM92, GuC92a, GuC92b, GuCo94]

# B.4. Méthodologie de l'université de Californie/Irvine: (SpecSyn)

**Niveau système :** La spécification de niveau système qui est en entrée est exprimée en SpecCharts. Les composants matériels générés sont exprimés en VHDL. Le logiciel généré est décrit en langage C.

**Types d'applications :** Pas de restrictions sur le type des systèmes traités.

**Approche de conception :** La conception au niveau système est divisée en trois phases distinctes :

1. Prise en compte de la spécification,

Annexe B.

2. Raffinement des spécifications,

3. Réalisation de la conception.

La phase de raffinement joue un rôle important dans le processus de conception.

Elle inclut les tâches suivantes :

1. Groupement d'objets : Par exemple, les variables sont groupées pour former une unité

de stockage qui pourrait être implantée par la suite comme une mémoire.

2. Association des groupes d'objets aux composants disponibles dans une bibliothèque.

3. Raffinement : il inclut les sous-tâches (1) Synthèse d'interfaces, (2) Insertion

d'arbitrage pour les canaux de communication, (3) Fusion de protocoles et (4)

Transposition des variables en adresses mémoire.

Architecture cible: L'architecture cible est une machine mono-processeur. Les

processeurs à mémoire cache et/ou avec instructions pipelinées ne sont pas pris en

considération.

**Notes**: L'évaluation des performances du système à développer est faite par les deux

techniques de simulation et d'estimation. Un estimateur de logiciel permet de fournir des

métriques à propos du logiciel généré en fonction du processeur cible. Ces métriques sont

: Le temps d'exécution, la taille de l'exécutable et celle des données. Cette approche est

basée sur l'identification des goulots d'étranglement dans le système. Il serait ainsi

possible de repérer des fonctions où l'utilisation d'un circuit spécifique peut améliorer les

performances.

**Références**: [GaVa95, GaVa94, GoGa94]

**B.5.** Méthodologie de l'université de Carnegie Mellon

Niveau système : Il s'agit d'une spécification fonctionnelle qui concerne aussi bien le

logiciel que le matériel. Le modèle utilisé est celui des processus séquentiels et

communiquants (CSP) où chaque processus est décrit d'une façon comportementale dans

un langage de description de haut niveau. La caractéristique principale de ce modèle est le

niveau d'abstraction dans lequel il représente l'interaction entre le matériel et le logiciel.

**Types d'applications :** Une classe de systèmes mixtes matériel/logiciel où l'on peut envisager l'accélération d'une fonction logicielle par l'extraction de certaines parties pour les réaliser en matériel. Les systèmes de contrôle complexes sont considérés dans cette approche.

Approche de conception : La méthodologie utilise les étapes suivantes :

- 1. Partitionnement matériel/logiciel,

- 2. Synthèse comportementale,

- 3. Compilation du logiciel,

- 4. Démonstration sur un banc de test composé par des CPUs, FPGAs et des interconnexions programmables.

La conception mixte permet de réaliser les tâches suivantes :

- 1. Caractérisation des performances du matériel et du logiciel,

- 2. Identification des partitions matériel/logiciel,

- 3. Transformation d'une description fonctionnelle en une partition, et

- 4. Synthèse du matériel et du logiciel résultants.

La simulation mixte matériel/logiciel est le moyen utilisé pour vérifier la fonctionnalité des descriptions matérielles/logicielles. Les processus à réaliser en matériel sont décrits en Verilog, le simulateur Verilog est utilisé pour les simulations comportementales. Les processus modélisant le logiciel s'exécutent comme des processus sous le système d'exploitation UNIX et communiquent avec le simulateur via des points de communication (les sockets). Les sockets sont utilisés ici pour permettre des simulations distribuées sur un réseau. La communication inter-processus est possible à travers le partage d'un espace mémoire commun.

**Architecture cible :** Utilisation d'un banc de test composé par des FPGAs et des interconnexions existantes dans la carte mère d'un ordinateur à usage général. Les composants pour applications spécifiques (ASICs) sont conçus pour coopérer avec le logiciel qui s'exécute sur un seul CPU. Ils sont connectés au système entier à travers des

Annexe B.

bus de connexion. Le prototypage est fait sur un PC-AT avec une carte composée de

FPGAs.

Notes: Le but de cette approche est de cacher les détails de l'architecture matérielle, être

explicite concernant le niveau de concurrence et le partitionnement matériel/logiciel, et de