### Heuristic reasoning for an automatic commonsense understanding of logic electronic design specifications Salvador Mir

#### ▶ To cite this version:

Salvador Mir. Heuristic reasoning for an automatic commonsense understanding of logic electronic design specifications. Micro and nanotechnologies/Microelectronics. University of Manchester, 1993. English. NNT: . tel-00010456

### HAL Id: tel-00010456 https://theses.hal.science/tel-00010456

Submitted on 7 Oct 2005

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Department of Computer Science University of Manchester Manchester M13 9PL, England

Technical Report Series UMCS-94-4-2

## Salvador Mir

HEURISTIC REASONING For An AUTOMATIC COMMONSENSE UNDERSTANDING Of LOGIC ELECTRONIC DESIGN SPECIFICATIONS

## HEURISTIC REASONING For An AUTOMATIC COMMONSENSE UNDERSTANDING Of LOGIC ELECTRONIC DESIGN

### LOGIC ELECTRONIC DESIGN SPECIFICATIONS <sup>1</sup>

Salvador Mir

Department of Computer Science University of Manchester Oxford Road, Manchester, UK.

<sup>1</sup>Copyright ©1994. All rights reserved. Reproduction of all or part of this work is permitted for educational or research purposes on condition that (1) this copyright notice is included, (2) proper attribution to the author or authors is made and (3) no commercial gain is involved.

Technical reports issued by the Department of Computer Science, Manchester University, are available by anonymous ftp from ftp.cs.man.ac.uk in the directory pub/TR. The files are stored as PostScript, in compressed form, with the report number as filename. Alternatively, reports are available by post from The Computer Library, Department of Computer Science, The University, Oxford Road, Manchester M13 9PL, UK.

## Contents

| Al       | bstra | ct                                                           | <b>5</b>  |

|----------|-------|--------------------------------------------------------------|-----------|

| De       | eclar | ation                                                        | 6         |

| Pr       | efac  | 5<br>5                                                       | 7         |

| Ac       | cknov | wledgements                                                  | 8         |

| A        | bbre  | viations                                                     | 10        |

| Sy       | mbo   | ls                                                           | 11        |

| Li       | st of | Tables                                                       | 13        |

| Li       | st of | Figures                                                      | 14        |

| Ι        | Еx    | pert Knowledge and Problem Formulation                       | 17        |

| 1        | Intr  | oduction                                                     | 18        |

|          | 1.1   | Motivations of the Research Work                             | 18        |

|          | 1.2   | Exploiting Implicit Design Knowledge                         | 20        |

|          | 1.3   | Methodology                                                  | 21        |

|          | 1.4   | Artificial Intelligence                                      | 23        |

|          | 1.5   | Relationship to Other Work                                   | 27        |

|          | 1.6   | Overview                                                     | 30        |

| <b>2</b> |       | hitecture of Digital Electronic Systems                      | <b>32</b> |

|          | 2.1   | Preliminaries                                                | 32        |

|          | 2.2   | System Model of Digital Systems                              | 33        |

|          |       | 2.2.1 Combinational Systems                                  | 34        |

|          |       | 2.2.2 Sequential Systems                                     | 36        |

|          | 2.3   | Algorithmic Model of Digital Systems                         | 39        |

|          |       | 2.3.1 Structure of Algorithmic Systems                       | 40        |

|          |       | 2.3.2 Implementation of Group-Sequential Algorithmic Systems | 41        |

|          | 2.4   | Computer Systems                                             | 45        |

|          | 2.5   | Summary of Key Concepts                                      | 47        |

| 3        | Heı  | ristic Classification of Electronic Cells and Signals | 48  |

|----------|------|-------------------------------------------------------|-----|

|          | 3.1  | Introduction                                          | 48  |

|          | 3.2  | Design Hierarchy                                      | 50  |

|          | 3.3  | Knowledge for the Classification of Electronic Cells  | 51  |

|          | 3.4  | Knowledge for the Classification of Design Signals    | 59  |

|          | 3.5  | Reasoning About a Situation                           | 61  |

|          | 3.6  | Problem Formulation                                   | 63  |

|          | 3.7  | Complexity and Strategies                             | 64  |

| II       | A    | utomatic Derivation of Heuristic Design Knowledge     | 68  |

| 4        | For  | mation of Knowledge Plans                             | 69  |

|          | 4.1  | Knowledge Plans                                       | 69  |

|          | 4.2  | Methods and Heuristics for the Formation of Plans     | 72  |

|          | 4.3  | Knowledge-derivation Functions                        | 74  |

|          | 4.4  | Example 1 — Planning by Analysis of Names             | 76  |

|          |      | 4.4.1 Heuristics Based on Naming                      | 77  |

|          |      | 4.4.2 Planning the Interface of a Cell                | 78  |

|          | 4.5  | Example 2 — Inference of Plausible Cell Types         | 79  |

|          |      | 4.5.1 Abstraction Level Analysis                      | 79  |

|          |      | 4.5.2 Logic Type Analysis                             | 81  |

|          |      | 4.5.3 Data Transportation Analysis                    | 82  |

|          | 4.6  | Number of Knowledge Plans and Complexity              | 83  |

| <b>5</b> | Ger  | neration of Cell Models                               | 86  |

|          | 5.1  | Knowledge Plans and Heuristic Models                  | 86  |

|          | 5.2  | Class Models                                          | 87  |

|          | 5.3  | Hierarchy of Models                                   | 92  |

|          | 5.4  | Logged Models and Learning                            | 95  |

|          | 5.5  | Cell Model Generation                                 | 96  |

|          |      | 5.5.1 Matching of Class Models                        | 97  |

|          |      | 5.5.2 Algorithm Complexity                            | 101 |

|          | 5.6  | Organisation of Knowledge Plans                       | 106 |

| 6        | Sele | ection of Cell Models                                 | 108 |

|          | 6.1  | Problem Definition and Complexity                     | 108 |

|          | 6.2  | Evaluating Alternatives                               | 110 |

|          | 6.3  | Evaluation of the Model of a Cell                     | 113 |

|          | 6.4  | Evaluation of a Situation                             | 115 |

|          | 6.5  | Weighting Factors                                     | 116 |

|          |      | 6.5.1 Complexity Deviation Factor                     | 118 |

|          |      | 6.5.2 A Case-Study                                    | 121 |

|          | 6.6  | Cell Complexity Estimation Function                   | 122 |

|   | 6.7 | Selection of Alternatives                     | 125 |

|---|-----|-----------------------------------------------|-----|

| 7 | Mo  | del-based Reasoning                           | 127 |

|   | 7.1 | Problem Definition                            | 127 |

|   | 7.2 | Consistency and Knowledge-propagation         | 128 |

|   | 7.3 | Specification-level Understanding             | 130 |

|   | 7.4 |                                               | 131 |

|   |     | 7.4.1 Plausible and Implausible Relationships | 132 |

|   |     | 7.4.2 Planning Groupings of Connections       | 136 |

|   | 7.5 |                                               | 138 |

|   | 7.6 |                                               | 141 |

|   |     |                                               | 142 |

|   |     | 7.6.2 Problem-solving Strategies              | 144 |

|   | 7.7 | Design Reformulation                          | 146 |

$\mathbf{148}$

### III Experimental Implementation, Applications and Conclusion

| 8  | Her   | cules: An Experimental Implementation                     | 149 |

|----|-------|-----------------------------------------------------------|-----|

|    | 8.1   | Hercules Overall Structure                                | 149 |

|    | 8.2   | System Strategy                                           | 152 |

|    | 8.3   | Current Status of the System and Limitations              | 153 |

|    | 8.4   | Number of Plans/Models Derived                            | 154 |

|    | 8.5   | Case-Studies                                              | 157 |

|    | 8.6   | System Evaluation Indicators                              | 157 |

|    |       | 8.6.1 Indicators of Design Complication                   | 158 |

|    |       | 8.6.2 Indicators of Processing Complexity                 | 160 |

|    |       | 8.6.3 Effectiveness of the Knowledge-extraction Functions | 163 |

|    |       | 8.6.4 Evaluation of the Knowledge Derived                 | 164 |

|    | 8.7   | Discussion                                                | 166 |

| 9  | Con   | clusion                                                   | 167 |

|    | 9.1   | Design Understanding — Limitations                        | 167 |

|    | 9.2   | Applications                                              | 169 |

|    |       | 9.2.1 General Issues — ECAD Frameworks                    | 169 |

|    |       | 9.2.2 Guidance and Control of ECAD Tools                  | 173 |

|    | 9.3   | Further Work                                              | 175 |

|    | 9.4   | Afterword                                                 | 176 |

| Bi | bliog | graphy                                                    | 176 |

| $\mathbf{A}$ | Decision Factors                                                                                        | 182        |

|--------------|---------------------------------------------------------------------------------------------------------|------------|

|              | A.1 Decision Factor of a Change                                                                         | 182        |

|              | A.2 Decision Factors for a Situation                                                                    | 184        |

|              | A.3 Decision Factors for a Cell Heuristic Model                                                         | 185        |

|              | A.4 Changes of Estimated Complexity                                                                     | 187        |

| В            | Semantic Networks for Name Analysis                                                                     | 190        |

|              | B.1 Meanings of a Word                                                                                  | 190        |

|              | B.2 Meaning of a Semantic Network                                                                       | 193        |

|              | B.3 Control of Name Matching                                                                            | 194        |

| С            | Combination of Evaluation-function Values                                                               | 197        |

| D            | Architecture of Computer Systems                                                                        | 199        |

|              | D.1 Uniprocessor Systems                                                                                | 199        |

|              | D.2 High-Performance Computer Systems                                                                   | 200        |

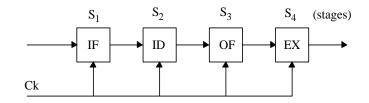

|              | D.2.1 Pipeline computers                                                                                | 201        |

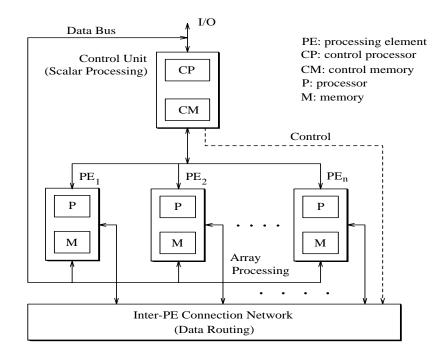

|              | D.2.2 Array Computers                                                                                   | 201        |

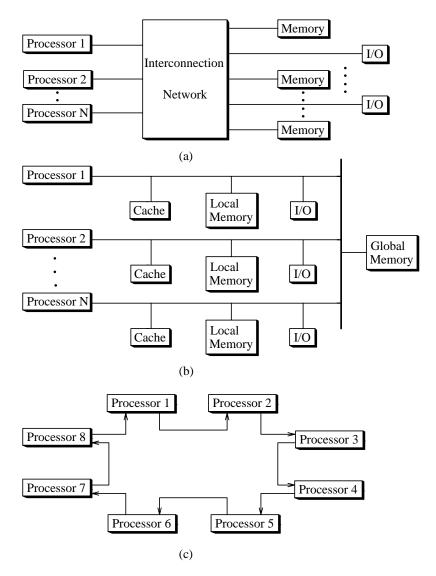

|              | D.2.3 Multiprocessor Systems                                                                            | 202        |

| $\mathbf{E}$ | Proofs                                                                                                  | <b>204</b> |

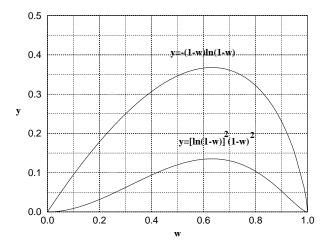

|              | E.1 Proof I                                                                                             | 204        |

|              | E.2 Proof II                                                                                            | 205        |

|              | E.3 Proof III                                                                                           | 207        |

| $\mathbf{F}$ | Design Hierarchy for the Case-Studies                                                                   | 209        |

|              | F.1 Counter $\ldots$   | 209        |

|              | F.2 H_bilbo                                                                                             | 209        |

|              | F.3 Add                                                                                                 | 210        |

|              | F.4 Valid1 $\ldots$    | 211        |

|              | $F.5  6g011a  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                          | 211        |

|              | F.6 Multmilldesign                                                                                      | 213        |

|              | F.7 Designtop1                                                                                          | 214        |

|              | F.8 18ara700a                                                                                           | 218        |

|              | F.9 Cwheel1_0 $\ldots$ | 229        |

| $\mathbf{G}$ | Example of a System Run                                                                                 | 232        |

## Abstract

An automatic *heuristic understanding* of digital electronic design specifications is discussed in this thesis. The term understanding is used in the sense that knowledge about the functionality and purpose of the cells and signals of a design is abstracted away from the specification. An heuristic analysis which exploits implicit design semantics is carried out. The analysis bypasses the examination of detailed logical and electrical data since it is aimed at the machine simulation of an heuristic way of understanding electronic design specifications exhibited by human experts. By overlooking implicit knowledge, current automatic systems are clearly at a disadvantage with respect to human experts for the analysis, design and management of electronic data. The possibility of getting the machine to heuristically understand a specification is seen in this thesis as one way of improving this situation.

The thesis defines and classifies expert knowledge about digital electronic designs, explores ways to generate expert knowledge about a design from the heuristic analysis of its specification and discusses examples of exploiting this knowledge to plan and control automatic tasks. The experimental result of this research is a knowledge-based system aimed at providing an empirical demonstration of the convenience and viability of an automatic heuristic understanding of design specifications. The method of reasoning of the system has without question limitations, but these are also faced by human experts when they attempt this task. The current prototype of the system already indicates that valid knowledge can be generated and it implements methods for avoiding the critical computational complexity of the problem.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institution of learning.

## Preface

The author graduated from Universitat Politècnica de Catalunya, Barcelona, in July 1987 with a degree in Industrial Engineering. He gained a degree of Master of Science at the University of Manchester in October 1989. He then commenced full-time research work for the degree of Doctor of Philosophy at the University of Manchester. The research done during this period is described in this thesis.

## Acknowledgements

This work evolved from the initial proposal of my supervisor, Dr. Nicholas Paul Filer, of exploiting semantic knowledge contained in an electronic design specification. I am grateful to him for this initial proposition and for his guidance and encouragement to go ahead with the work. I am also grateful to him for many corrections and comments which improved the legibility of the manuscript.

I am grateful to my family for their encouragement to get on with my life and my work, and for all those wonderful reasons which obliged me to frequently go back home to keep pace with many things that changed over there during the research time. This thesis is dedicated to my parents.

I am grateful to friends and colleagues who made the research time not only enjoyable but also possible by granting me on countless occasions the chance of enjoying their company. Pepi Aguila, Maria Teresa Arica, Jorge Artiles, Marisa Barañano, Karen Cooksey, Alain Deckers, Catherine Dubois, Amr Elleithy, Wael Fahmi, Luisa Ferriz, Ignacio Ferriz, Julio Garrido, Aurelio Gómez, Teresa Guedes, Jeremy Heald, Mark Hendrick, Choi Lin Lee, Katia Helena Lipp João, Ana Cristina Melo, Francesca Montalcini, Lidia Moraes, Georgina and Antonio Noriega, Iñaki Onandia, Maria Jose Pardo, Mouna Salem, Laura and Paolo Saviotti, Bahram Semsar Zadeh, Eduarda and Fernando da Silva, Georges Theodoropoulos, Georges Tsakogiannis, Eva Valero, Martine de Vlieger, Daniel Wray and Tim and Hilary Young all were, among others, very good company.

Colleagues in the CAD laboratory at the University of Manchester were useful in a number of ways. Daniel Wray produced a graphical interface for displaying the heuristic design knowledge generated. He patiently coped with several updatings of the scheme for the representation of knowledge. Discussions with him, and Jun-Kang Feng and Alan Williams, who worked on a formal representation of the heuristic knowledge generated, were useful to clarify the notation of the knowledge representation scheme. Discussions with Mike Brown helped me to understand the requirement for a formal representation of heuristic design knowledge. I am grateful to many colleagues in the laboratory who always helped me with the use of the computer system.

Discussions with Helena Mendes currently in the Department of Computation at UMIST in Manchester were of substantial interest to emphasise the applicability of this research to *reverse engineering* activities.

I am grateful to Mike Brown, Karen Cooksey, Alain Deckers, Laura Saviotti, Tim Young and Daniel Wray for proof-reading the manuscript.

This work was supported by a grant from the Comisión Interministerial de Ciencia y

*Tecnología* (CICYT), Madrid, to whom I am greatly indebted for the financial support provided over the research years and for the promptness and understanding demonstrated when dealing with me as a grantee.

# Abbreviations

# Symbols

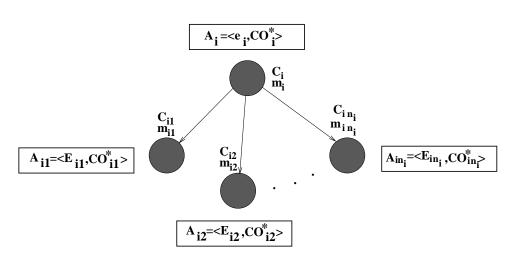

| $A_i$               | $\dots$ confidence/complexity pair for $C_i$                                                                         | $F_{i,k}$    |       |

|---------------------|----------------------------------------------------------------------------------------------------------------------|--------------|-------|

| $A_{i,j}$           | confidence/complexity pair for $C_{i,j}$                                                                             | h            |       |

| $As_i$              | $\dots \dots \dots \dots \dots$ candidate sets for $S_i$                                                             | $h_i$        |       |

| $C_c$               | content matching $n^{\underline{O}}$ combinations                                                                    | $h_{max}$    |       |

| $C_c^*$             | $\dots$ valid $n^{\underline{O}}$ combinations for $C_c$                                                             | $H_k$        |       |

| $C_i$               | $\dots \dots \dots i$ -th cell in the design                                                                         | HR           |       |

| $C_{i,j}$           | $\dots \dots j$ -th sub-cell of $C_i$                                                                                | in           |       |

| Cs                  | set of cells of a design                                                                                             | $I_c$        | .in   |

| $CO_i$              | $\dots \dots $ | $I_c^*$      |       |

| $CO_i^c$            | $\dots \dots$ calculated complexity of $C_i$                                                                         | $I_e$        | inte  |

| $CO_i^*$            | $\dots \dots $ estimated complexity of $C_i$                                                                         | $I_i$        |       |

| $CO_{i,j}$          | $\ldots \ldots \ldots \ldots \ldots \ldots \ldots $ complexity of $C_{i,j}$                                          | $I_{i,j}$    |       |

| $CO_{i,j}^*$        | $\dots \dots $ estimated complexity of $C_{i,j}$                                                                     | Ir           |       |

| $\partial$ $$       | partial derivative                                                                                                   | K            |       |

| $d_k$               | $\dots$ decision factor for the k-th slot                                                                            | $K_{av}$     |       |

| dx                  | $\dots \dots $ | $L_{av}$     |       |

| Dg                  | cell dependability                                                                                                   | $L_k$        |       |

| $D_i$               | $\dots \dots $ | $m_{av}$     |       |

| $D_{i,k}$           | $\ldots \ldots \ldots$ decision factor for $C_{i,k}$                                                                 | $m_{a  v_i}$ | 8     |

| $Ds_i$              | $\ldots$ set of down-dependencies of $C_i$                                                                           | $m_g$        |       |

| $e_{av}$            | av. confidence in selected models                                                                                    | $m_i$        |       |

| $e_i$               | $\dots \dots $ |              |       |

| $e_{i,j}$           | $\dots \dots \dots \dots \dots \dots$ confidence in $M_{i,j}$                                                        | $m_o$        | • • • |

| $E_i$               | $\dots \dots $ | mod          | • • • |

| $E_{i,k}$           | confidence in situation defining $C_{i,k}$                                                                           | $M_{i}$      | • • • |

| $EH_i$              | $\dots \dots \dots$ level of abstraction of $C_i$                                                                    | $M_{i,j}$    | • • • |

| $E_1$               | design model evaluation                                                                                              | $M_i^j$      |       |

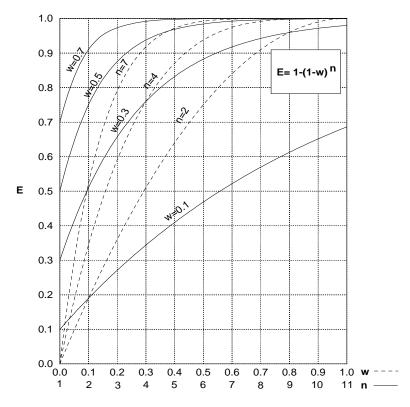

| E                   | effectiveness of set selection                                                                                       | Ms           |       |

| $\mathcal{E}_{ext}$ | k-extraction effectiveness                                                                                           | $Ms_i$       | • • • |

| $\mathcal{E}m_k$    | k-cycle av. new matches per plan                                                                                     | n            |       |

| $f_c$               | plan matching $n^{\underline{O}}$ combinations                                                                       | $n_{ci}$     | • • • |

| $f_g$               | $\dots n^{\underline{O}}$ plans from model matching                                                                  | $n_{co}$     | • • • |

| $f_k$               | $\dots$ $k$ -th cycle $n^{\underline{O}}$ solution plans                                                             | $n_{di}$     | • • • |

| $fm_k$              | $\dots$ $k$ -th cycle $n^{\underline{O}}$ available plans                                                            | $n_{do}$     | • • • |

| $Fe_k$              | k-th cycle % already existing plans                                                                                  | $n_i$        | • • • |

| $Ff_k$              | $\dots \dots k$ -th cycle $\%$ repeated plans                                                                        |              |       |

| ,k                 | $\ldots \ldots C_i$ -to- $C_{i,k}$ arc decision factor             |

|--------------------|--------------------------------------------------------------------|

| ,                  | $\dots n^{\underline{O}}$ of class models in the system            |

|                    | $\ldots$ depth-level of $C_i$                                      |

|                    | largest depth-level                                                |

| ıax                | k-th heuristic model in the system                                 |

| k<br>D             |                                                                    |

| R                  | typical interlevel complexity ratio                                |

|                    | list membership                                                    |

|                    | . interface matching $n^{\Omega}$ combinations                     |

|                    | valid $n^{\underline{O}}$ combinations for $I_c$                   |

|                    | interface name matching effectiveness                              |

|                    | $\dots \dots n^{\underline{O}}$ of instances of $C_i$              |

| j                  | $\dots \dots n^{\underline{O}}$ of instances of $C_{i,j}$ in $C_i$ |

|                    | instantiation rate of the design                                   |

|                    | $\dots \dots n^{\underline{O}}$ of reasoning cycles                |

| a v                | av. $n^{\underline{O}}$ productive cycles per cell                 |

| v                  | $\dots$ av. $n^{\underline{O}}$ cell paths                         |

| ;                  | $\dots k$ -th logged model in the system                           |

| a v                | $\dots$ average $n^{\underline{O}}$ of models per cell             |

| $a v_i$            | average $n^{\underline{O}}$ of models per cell in $S_i$            |

| g                  | $\dots \dots n^{\underline{O}}$ of model sub-cell classes          |

| i                  | $\ldots n^{\underline{O}}$ of possible models for $C_i$ and        |

|                    | $n^{\underline{O}}$ of model input ports                           |

| 0                  | $\dots \dots n^{\mathbf{Q}}$ of model output ports                 |

| od                 | modulo operator                                                    |

| i                  | $\ldots$ heuristic model selected for $C_i$                        |

| i.i                | heuristic model selected for $C_{i,j}$                             |

| j                  | $\dots \dots j$ -th heuristic model for $C_i$                      |

| i,j<br>j<br>i<br>s |                                                                    |

| $s_i$              | $\dots$ solution set for $S_i$                                     |

| <i>.</i> 1         | $\dots \dots \dots n^{\underline{O}}$ of cells in the design       |

|                    | $\dots$ $n^{\underline{O}}$ of model control input ports           |

| i                  |                                                                    |

| 0                  | $\dots n^{\underline{O}}$ of model control output ports            |

| i                  | $\dots \dots n^{\underline{O}}$ of model data input ports          |

| 0                  | $\dots n^{\underline{O}}$ of model data output ports               |

|                    | $\dots \dots n^{\underline{O}}$ of plan input ports and            |

|                    | $n^{\underline{\mathrm{O}}}$ of sub-cells of $C_i$                 |

|                    |                                                                    |

| $\dots \dots \dots$ typical complexity of $C_i$                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                             |

| $\dots \dots \dots \dots$ uncertainty about $M_i$                                                                           |

| $\dots$ $n^{\underline{O}}$ of up-dependencies of $C_i$                                                                     |

| $\dots$ uncertainty about $S_i$                                                                                             |

| $\dots$ set of up-dependencies of $C_i$                                                                                     |

| $\dots$ confidence in the k-th slot                                                                                         |

|                                                                                                                             |

| model deviation in terms of $I_{i,j}$                                                                                       |

| weighted contribution of $C_{i,k}$                                                                                          |

| weighted contribution of $k$ -th slot                                                                                       |

| vector of values                                                                                                            |

| $\dots \dots i$ -th sub-vector of vector $\underline{x}$                                                                    |

| unknown value                                                                                                               |

| composition of functions                                                                                                    |

| power operator                                                                                                              |

| integer division                                                                                                            |

| $\ldots \ldots$ arithmetic expression X                                                                                     |

| evaluates to $Z$                                                                                                            |

| numeric values are equal                                                                                                    |

| numeric values are not equal                                                                                                |

| $\ldots Z$ and $X$ are true                                                                                                 |

| and much and the                                                                                                            |

|                                                                                                                             |

| $\ldots Z$ or $X$ are true                                                                                                  |

| $\dots Z$ or X are true<br>$\dots$ if P then Q true else R is true                                                          |

| $\dots Z$ or X are true<br>$\dots $ if P then Q true else R is true<br>$\dots $ continued product                           |

| $\dots Z$ or X are true<br>$\dots $ if P then Q true else R is true<br>$\dots $ continued product<br>$\dots $ continued sum |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                        |

| $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                       |

|                                                                                                                             |

| $n_{io}$       | $\dots \dots n^{\underline{O}}$ of plan inout ports           |

|----------------|---------------------------------------------------------------|

| $n_o$          | $\dots \dots n^{\underline{O}}$ of plan output ports          |

| $\overline{N}$ | $\dots n^{\underline{O}}$ of candidate solution sets          |

| $N_{av}$       | $\dots \dots $ av. $n^{\underline{O}}$ situation sets         |

| Nf             | $\dots \dots n^{\underline{O}}$ of failed situation sets      |

| $Nf_i$         | $\dots \dots n^{\underline{O}}$ of failed sets for $S_i$      |

| $N_i$          | $\dots \dots n^{\underline{O}}$ candidate sets for $S_i$      |

| Nm             | $\dots \dots n^{\underline{O}}$ of cell models generated      |

| $Nm_{av}$      | av. $n^{\underline{O}}$ of models generated per cell          |

| Np             | $\dots \dots n^{\underline{O}}$ of cell plans generated       |

| $N p_{av}$     | . av. $n^{\underline{O}}$ of plans generated per cell         |

| $N_w$          | $\dots$ maximum $n^{\underline{O}}$ of candidate sets         |

| NF             | $\dots \dots n^{\underline{O}}$ of failed sets                |

| $NM_c$         | cell name matching effectiveness                              |

| $NM_n$         | $\dots$ net name matching effectiveness                       |

| $NM_p$         | $\dots$ port name matching effectiveness                      |

| p              | $\dots n^{\underline{O}}$ primitive cells in the design       |

| $p_g$          | $\dots \dots n^{\underline{O}}$ of plan sub-cell classes      |

| $p_i$          | $\dots \dots n^{\underline{O}}$ of plan input signals         |

| $p_o$          | $\dots \dots \dots n^{\underline{O}}$ of plan output signals  |

| $P_{av}$       | $\dots \dots n^{\underline{O}}$ cell ports                    |

| $P_i^j$        | $\dots \dots j$ -th knowledge plan for $C_i$                  |

| $r_{av}$       | av. complexity deviation factor                               |

| $r_i$          | $\ldots$ complexity deviation factor of $C_i$                 |

| $r_{i,j}$      | $\ldots \ldots \ldots$ weighting factor for $C_{i,j}$         |

| $r_k$          | $\dots$ relative importance of k-th slot                      |

| $R_{i,j}$      | $\dots \dots$ relative importance of $C_{i,j}$                |

| $R^*_{i,j}$    | $\dots \dots \dots \dots \dots $ estimated value of $R_{i,j}$ |

| $s_i$          | $\dots \dots n^{\underline{O}}$ of situations using $C_i$     |

| ${S}_i$        | $\dots \dots i$ -th situation in a design                     |

| T              | processing time                                               |

| $T_{av}$       | av. processing time per cell                                  |

| $T_c$          | $\dots$ % of correctly defined models                         |

| $T_d$          | $\dots \dots \%$ of fully defined models                      |

# List of Tables

| 1.1                                                                          | Shallow and Deep Systems                                   | 26                                              |

|------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------|

| $3.1 \\ 3.2 \\ 3.3 \\ 3.4$                                                   | Cell Types                                                 | 56<br>57<br>58<br>63                            |

| $ \begin{array}{r} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \end{array} $                    | A Knowledge Plan                                           | 71<br>79<br>81<br>82                            |

| $5.1 \\ 5.2 \\ 5.3$                                                          | Heuristic Model of the Class of Multiplexer Cells          | 90<br>95                                        |

| 5.4                                                                          | of the class, and (c) matching result                      | 98                                              |

| $5.5 \\ 5.6$                                                                 | the cells of the class, and (c) matching result            | $99 \\ 102 \\ 103$                              |

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$                                    | Evaluation of the Model of a Cell                          | 114<br>123                                      |

| $7.1 \\ 7.2$                                                                 | Propagation of Electronic Functionalities in a Primary Set | $\begin{array}{c} 135\\ 137 \end{array}$        |

| $\begin{array}{c} 8.1 \\ 8.2 \\ 8.3 \\ 8.4 \\ 8.5 \\ 8.6 \\ 8.7 \end{array}$ | Slot Weighting Factors                                     | $154 \\ 157 \\ 160 \\ 162 \\ 163 \\ 164 \\ 165$ |

| <b>B.</b> 1                                                                  | Examples of Object Names                                   | 191                                             |

# List of Figures

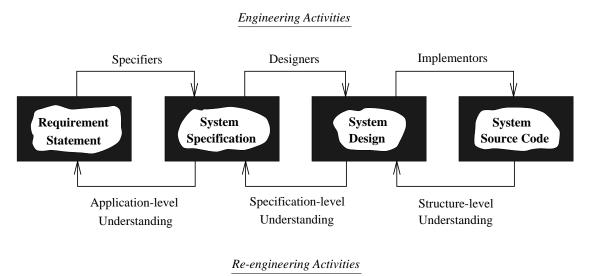

| 1.1          | Engineering and Re-engineering Activities                                                                                  | 28  |

|--------------|----------------------------------------------------------------------------------------------------------------------------|-----|

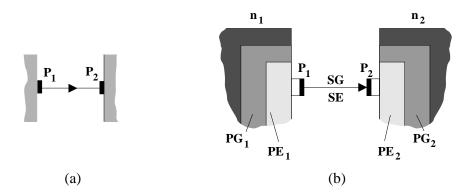

| $2.1 \\ 2.2$ | A Digital Cell                                                                                                             | 33  |

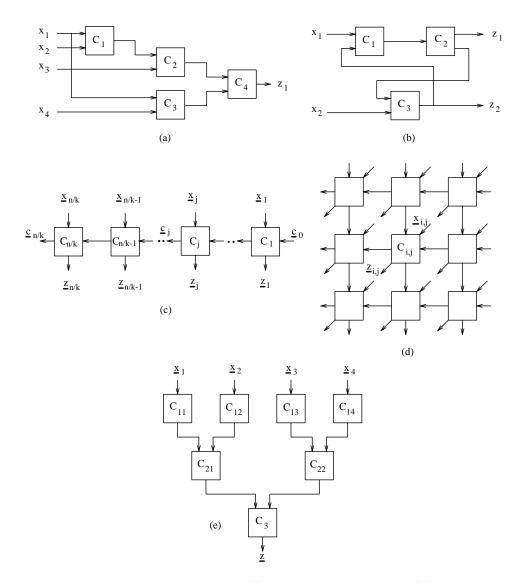

|              | k-iterative network, (d) array network, and (e) tree network                                                               | 35  |

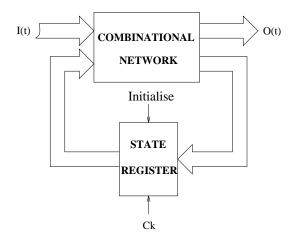

| 2.3          | Canonical Implementation of a Sequential Network                                                                           | 37  |

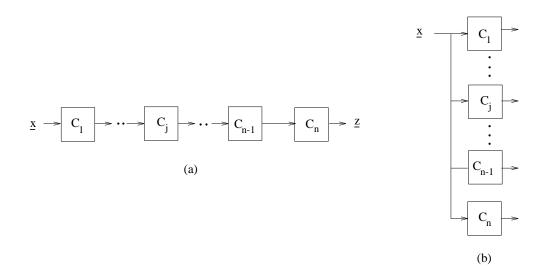

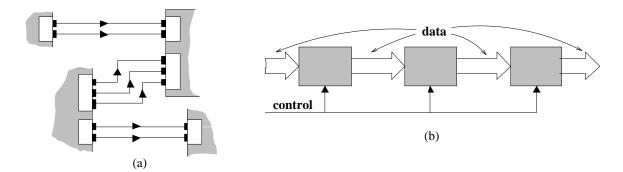

| 2.4          | Data Flow in Synchronous Sequential Networks: (a) cascade composition,<br>and (b) parallel composition                     | 39  |

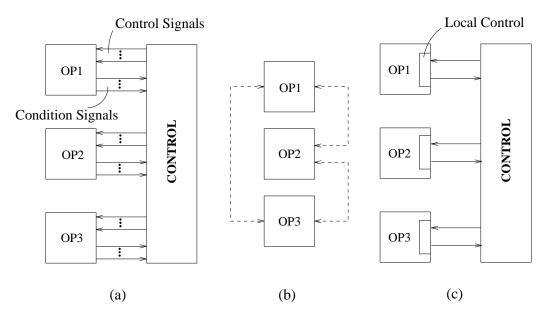

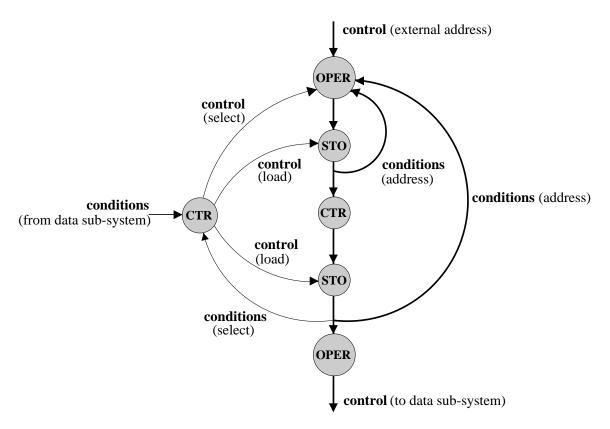

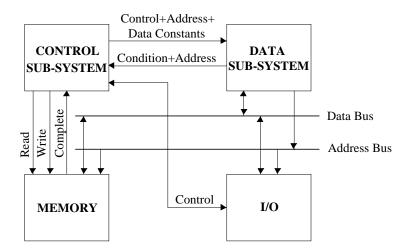

| 2.5          | Organisation of Algorithmic Systems: a) centralised control, b) decen-<br>tralised control, and c) semicentralised control | 41  |

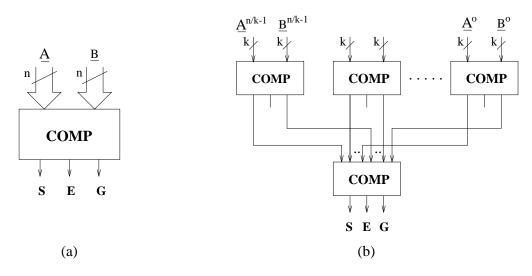

| 2.6          | Structure of a System with Centralised Control                                                                             | 42  |

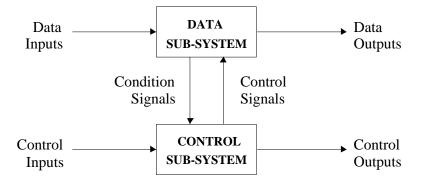

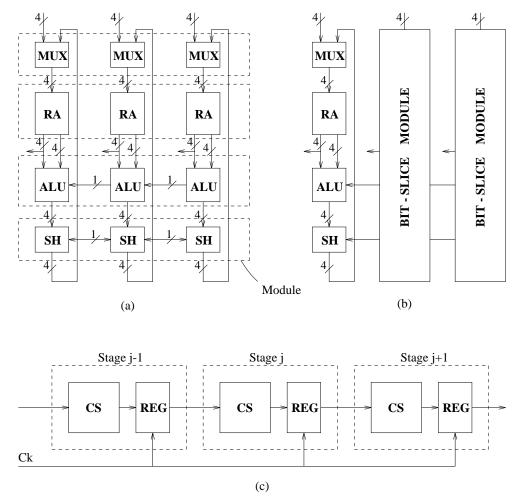

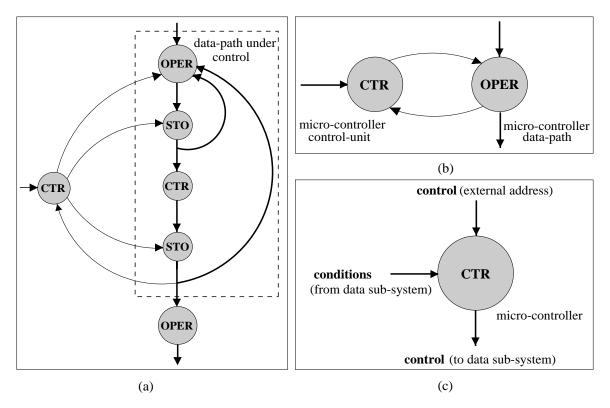

| 2.7          | Implementation of Data Sub-Systems: (a) modular implementation, (b)                                                        | 12  |

|              | bit-slice implementation, and (c) pipelining                                                                               | 43  |

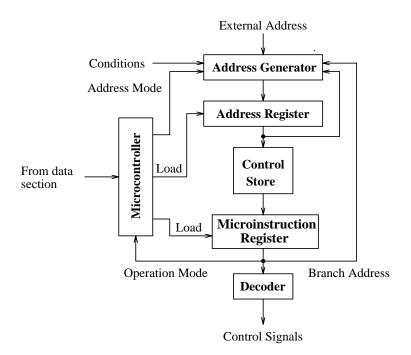

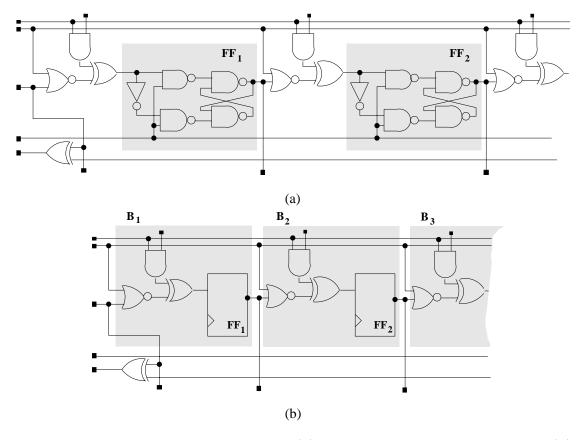

| 2.8          | Microprogrammed Control Unit                                                                                               | 44  |

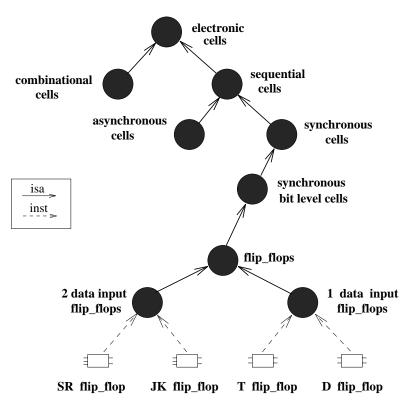

| 3.1          | Heuristic Classification of Electronic Cells                                                                               | 49  |

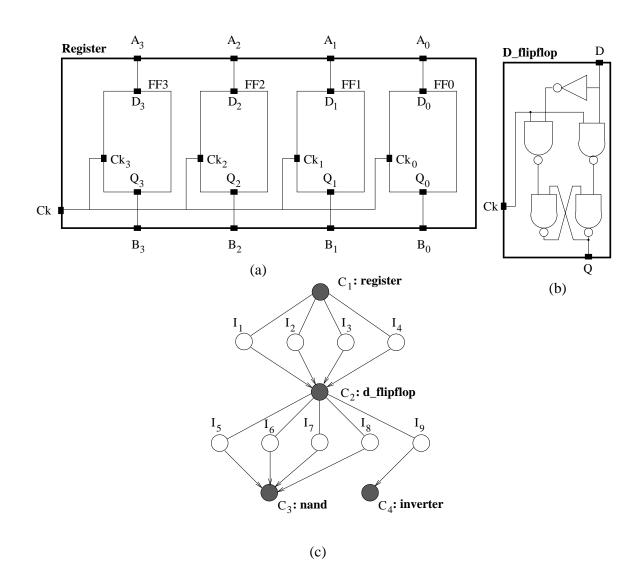

| 3.2          | Design Hierarchy: (a) 4-bit register, (b) D-type flip-flop, and c) design hierarchy for the 4-bit register                 | 51  |

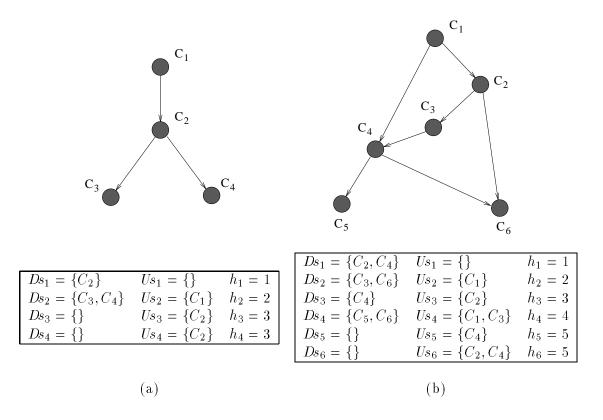

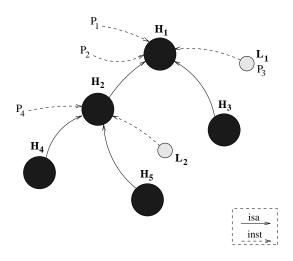

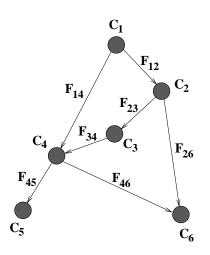

| 3.3          | Hierarchy Graphs: (a) 4-bit register hierarchy graph, and (b) hierarchy                                                    | JI  |

| 0.0          | graph with several paths leading to a cell.                                                                                | 52  |

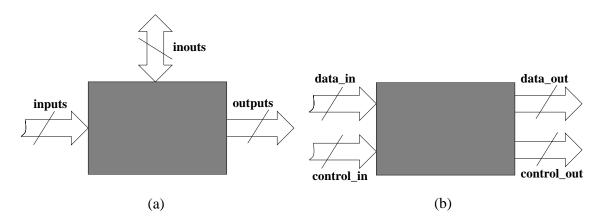

| 3.4          | Cell Interface: (a) cell interface description, and (b) meaningful cell interface.                                         | 58  |

| 3.5          | Port and Signal Electronic Functionalities                                                                                 | 61  |

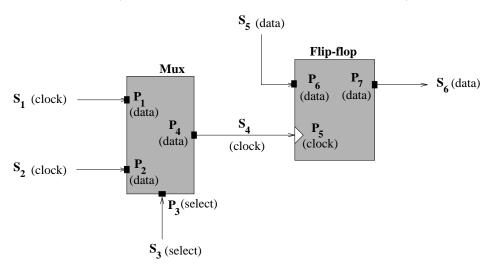

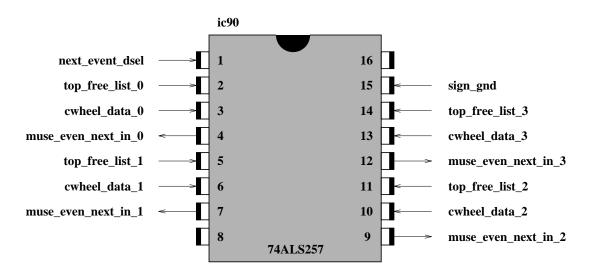

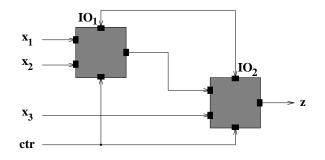

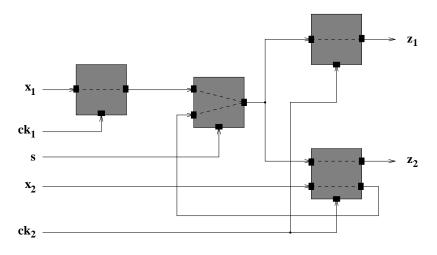

| 4.1          | Example Circuit                                                                                                            | 70  |

| 4.2          | Knowledge-derivation Functions                                                                                             | 74  |

| 4.3          | A Network with Bidirectional Ports                                                                                         | 82  |

| 4.4          | Computation of Data Transfer Paths                                                                                         | 83  |

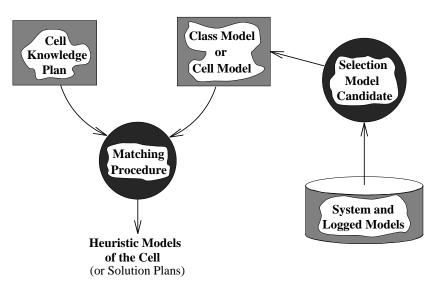

| 5.1          | Generation of Heuristic Cell Models                                                                                        | 87  |

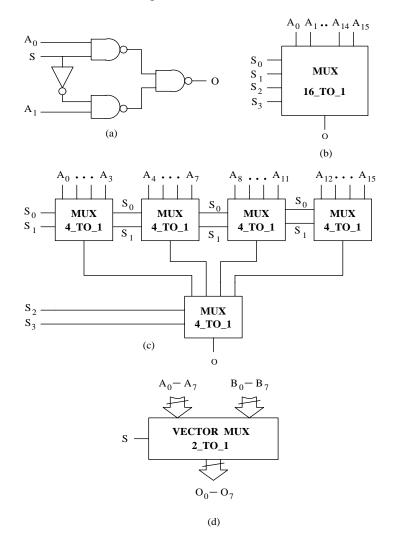

| 5.2          | Multiplexer Cells: (a) a construction of a 2_to_1 multiplexer, (b) a 16_to_1                                               |     |

|              | multiplexer, (c) a construction of a 16_to_1 multiplexer, and (d) a 2_to_1                                                 | 00  |

| 5.3          | vector-multiplexer                                                                                                         | 88  |

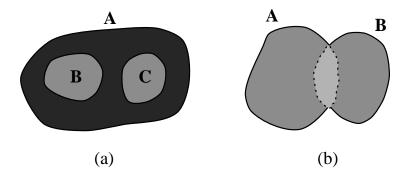

| J.J          | overlapped classes                                                                                                         | 93  |

| 5.4          | Partial Hierarchy of Electronic Cells                                                                                      | 94  |

| 5.5          |                                                                                                                            | 107 |

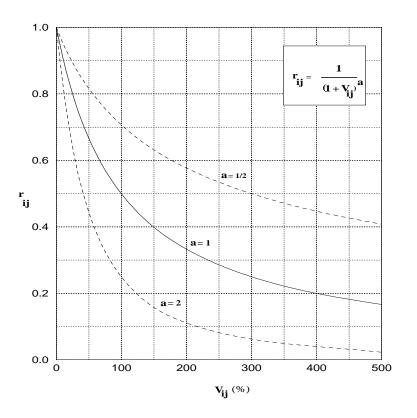

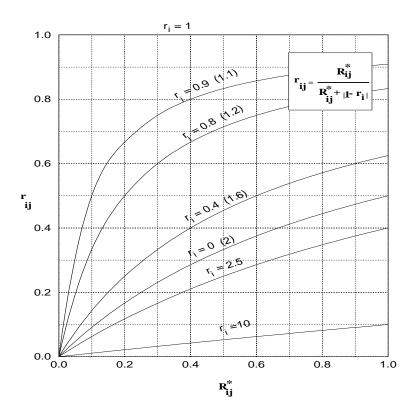

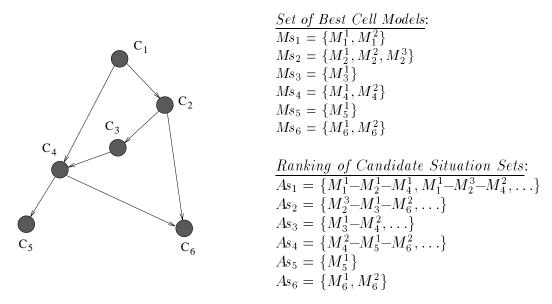

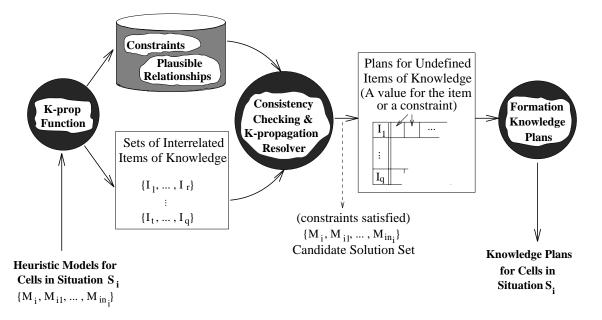

| $6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5$ | A SituationCombination of Evaluation-function ValuesWeighting FactorsEffect of the Relative ImportanceAn Example Design    | 109<br>113<br>119<br>120<br>125           |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

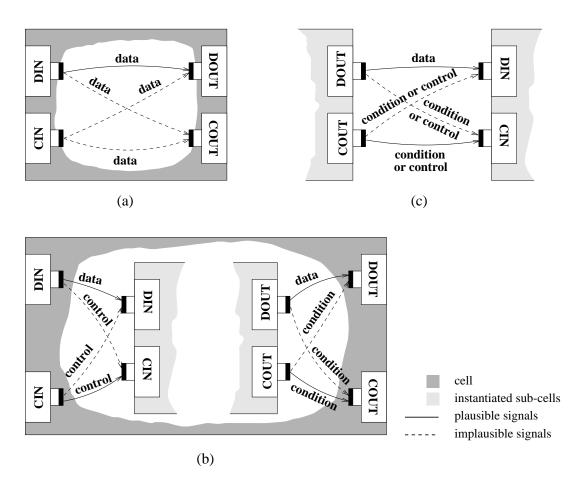

| $7.1 \\ 7.2$                      | Consistency and Knowledge-propagation                                                                                      | 130                                       |

| 7.3                               | primary set                                                                                                                | 132<br>134                                |

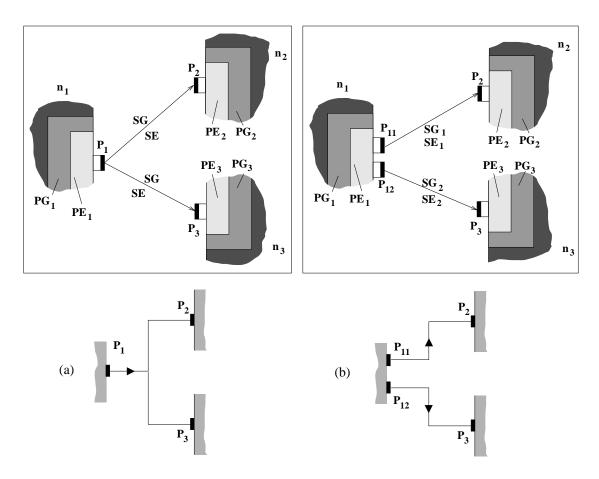

| 7.4                               | Interrelated Primary Sets: (a) a 1-to-2 connection, and (b) two 1-to-1 interrelated connections.                           | 134                                       |

| 7.5                               | Grouping of Connections: (a) groupings according to connectivity, and (b) typical arrangement of data and control signals. | 137                                       |

| $7.6 \\ 7.7$                      | Data/Control Signal Flow Example                                                                                           | 139                                       |

| 7.8                               | identification of a data unit, and (c) overall view                                                                        | 141                                       |

| 7.9                               | straction of the network                                                                                                   | 143<br>144                                |

| $7.10 \\ 7.11$                    |                                                                                                                            | 145<br>147                                |

| 8.1<br>8.2                        | Overall Structure                                                                                                          | $\begin{array}{c} 150 \\ 159 \end{array}$ |

| A.1                               | An Example Design                                                                                                          | 184                                       |

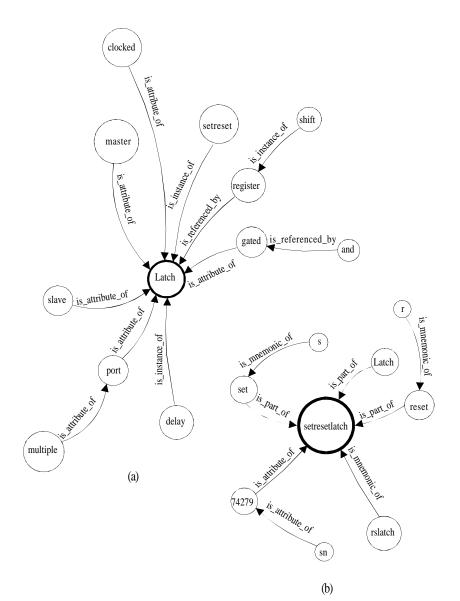

| <b>B</b> .1                       | Semantic Networks: a) class latch, and b) class set-reset latch                                                            | 192                                       |

| C.1                               | Combination of Two Evaluation-function Values                                                                              | 198                                       |

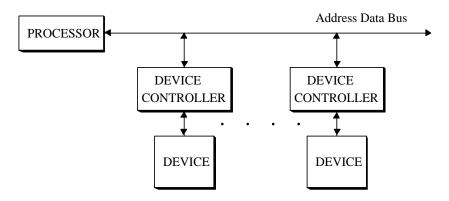

| D.1                               | Structure of a Uniprocessor System                                                                                         | 199                                       |

| D.2<br>D.3                        | Organisation of the I/O System                                                                                             | 200<br>201                                |

| D.4<br>D.5                        | Functional Structure of a Conventional Array Processor                                                                     | 202<br>203                                |

| E.1<br>E.2                        | Graph I                                                                                                                    | 206<br>208                                |

| L . 4                             | Отфинт                                                                                                                     | 200                                       |

Als meus pares

"La majoria dels homes són uns ingenus amb molta llana al clatell: s'imaginen que el món és tal i com ells el capten. Tingues sempre en compte però, que en realitat el món no té cap forma ni color, que cada ésser viu el percep d'una manera diversa, segons la naturalesa dels propis sentits". Pep Coll, La Mula Vella

> "Todo pasa y todo queda, pero lo nuestro es pasar, pasar haciendo caminos, caminos sobre la mar". Antonio Machado

"Orr would be crazy to fly more missions and sane if he didn't, but if he was sane he had to fly them. If he flew them he was crazy and didn't have to; but if he didn't want to he was sane and had to". Joseph Heller, Catch 22

"Pour un jour de synthèse il faut des années d'analyse". Fustel de Coulanges

# Expert Knowledge and Problem Formulation

### Chapter 1

## Introduction

The empirical observation that human experts can reason about electronic data in a way that automatic systems are unable to do triggered the research work presented in this thesis. The exploitation of heuristic design knowledge allows human experts a flexible way of understanding logic electronic design specifications which facilitates the analysis, design and management of electronic data. A procedure for the machine simulation of an heuristic way of understanding design specifications exhibited by human experts is introduced. The research work is within the area of applied Artificial Intelligence. Current research activities which can be related to this work include the re-engineering of software specifications and efforts directed to automatically reasoning about physical systems and man-made devices. The major contributions of this work are enumerated and an overview of the rest of the thesis is presented.

#### 1.1 Motivations of the Research Work

The research work presented in this thesis is aimed at providing the groundwork for an automatic *heuristic understanding* of digital electronic design specifications. The heuristic understanding of an electronic design is based on the analysis of design semantics implicit in the specification. The analysis bypasses the detailed logical and electrical data which can rigorously describe the behaviour of a system and its components (electronic cells). The term understanding is used in the sense that knowledge about the functionality or purpose of a design and its parts is abstracted away from its specification and this knowledge can be exploited later in order to plan and control automatic tasks. It is the exploitation of implicit design semantic knowledge, with the intention of improving the performance of computer-aided design (CAD) tools, which motivated this research work.

The need to exploit design semantics stems from the empirical observation that human experts can reason about electronic data in a way that automatic systems are unable to do. Human experts can often gain an overall understanding of the intention or purpose behind a design and its parts from the interpretation of data contained in its specification. This understanding allows the experts flexible ways of reasoning in order to efficiently plan and control design tasks. On the other hand, most automatic design tools process design data blindly according to the heuristics and algorithms they are programmed to use. The electronic data must meet the requirements of the CAD tools used and no intelligent machine interpretation of the data takes place. This is seen as one of the reasons why human experts can find solutions to problems that CAD tools are often unable to reach. The possibility of getting the machine to heuristically understand the circuit that is being designed (or that is being analysed) is seen in this thesis as one way of narrowing the gap between human experts and automatic systems with respect to the processing of electronic data.

The human understanding of an electronic specification is not only based on the study of the rigorous behaviour of the design but also on the examination of implicit design semantics. The study of electrical and logical data which precisely describes the behaviour of the design and its cells is very laborious and time consuming even for designs of a modest complexity. Without doubt, human experts are able to abstract higher level models of these behaviours which allow more flexible ways of reasoning than those based on the mathematical data. This flexibility comes, in most cases, from the fact that the knowledge which forms these models, and which is abstracted away from the specification, is generally quite vague and imprecise in nature. For example, some of this knowledge allows the experts to categorise the functionality of a device and its parts. But often, the principles behind these categorisations are quite ill-defined. As a result, the knowledge cannot be made more explicit in an electronic specification attending to the strict formalities of hardware description languages. As a consequence, in hardware descriptions, as in most types of specifications (e.g. computer programs), there are implicit semantics.

In the case of hardware descriptions, these implicit semantics often relate to the functionality or purpose of the design and its parts. When these implicit semantics are interpreted by an expert it is often possible to reach sensible conclusions which can be both explained and justified. Human experts make use of their experience and common sense in order to first analyse those semantic or heuristic aspects and data which appear most relevant for the understanding of a specification and which allow them to bypass the exploration of the most complex data. This leads to natural and pragmatic methods for the understanding of a specification. The usefulness of this kind of analysis is evident when an expert is able to understand the operation of a design in a short span of time.

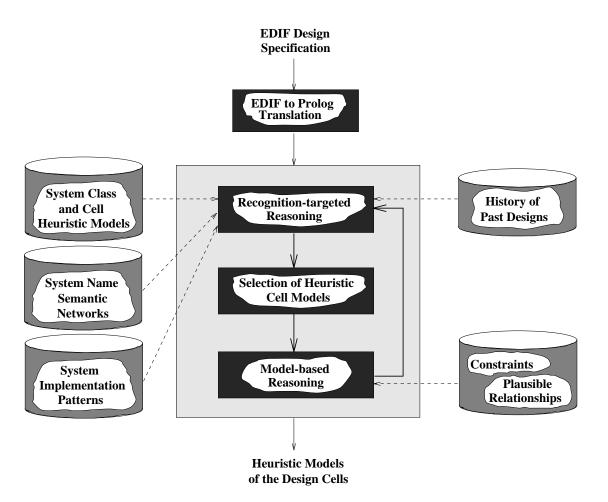

This work is concerned with the machine simulation of an heuristic way of understanding electronic design specifications exhibited by human experts. The thesis defines and classifies expert knowledge about digital electronic designs, explores ways to generate expert knowledge about a design from the heuristic analysis of its specification, and discusses examples of exploiting this knowledge to plan and control electronic CAD (ECAD) tasks. It is hoped that by capturing this kind of knowledge about a design the machine will be able to process the electronic data in a way that comes closer to the ways exhibited by human experts. The experimental result of this research is a knowledgebased system (KBS) aimed at the exploration of the architecture and functionality of a digital electronic design by means of an heuristic analysis of its specification. The system developed is called HERCULES (*HEuristic Reasoning for an automatic Commonsense Understanding of Logic Electronic design Specifications*).

#### 1.2 Exploiting Implicit Design Knowledge

A specification of an electronic design contains full or partial information about the structure and behaviour of the electronic circuits represented. The designers include in the description the data required by CAD systems for the processing of the design. In addition, the designers usually specify this data in such a way that other human designers can understand the design with a reasonable amount of effort. It is clear that a bare description of an electronic design in terms of the electrical or logical behaviours of its components and their interconnections is, in most cases, too extensive and elaborate for anybody to readily understand. For this reason, there are implicit semantics in the description of an electronic design. These implicit semantics improve the quality of the specification in the sense that they facilitate its understanding.

Some similarities exist with the specification of computer programs. In any programming language, the choice of meaningful names for variables and procedures, the use of comments, the organisation of data structures or the modularity of the program highly facilitate the task of understanding the goal of a program. This extra information is meaningful to the programmers, but it is not strictly required by the system that executes the program. The computer system will generate the same results with a well specified program as with a program with the same goal that is incomprehensible for program designers.

Similarly, the specification of an electronic design can be organised in such a way that facilitates its understanding. Some of the main techniques that are used to improve the quality of a description include the choice of meaningful names for the design objects (e.g. the names of cells and the ports of these cells), the use of comments, the arrangement of the design objects into arrayed structures (e.g. arrays of ports and arrays of signals) and the use of an adequate design hierarchy. All this information is meaningful to design engineers but most of it is unintelligible for automatic systems. Indeed, an automatic system must result in the same product from the processing of a well specified design as from the processing of a bare description, with the same goal, which is beyond human grasp.

The analysis of implicit semantics allows human experts to capture information of an heuristic nature that can be used, in many cases, to understand the functionality or intention of the cells and signals of a design. This process is initially based on the comparison of knowledge captured by interpreting electronic data contained in the specification with knowledge that the experts possess about electronic design. As a result, intuitive ideas or abstract models of the functionality or intention of the objects of a design are generated. The experts can next test and refine these ideas taking into account the context in which each object appears. This is because the objects of a design have relationships between them. For example, since an object is usually composed of other objects (e.g. a cell usually has a set of ports and a set of sub-cells), knowledge about an object must be consistent with knowledge about its parts. This provides a way of strengthening conclusions. These relationships can also be used in a more operational way. That is, they imply that knowledge about an object is useful for the inference of information about the parts of this object and vice versa. Other relationships between objects are imposed, for example, by the interconnections between cells and by the flow of signals in the circuit.

As an example, consider the identification of a device that represents an n-bit register. The analysis by means of the electrical or behavioural data (if available) is not straightforward since many variants of these devices exist. Alternatively, design semantics can be exploited. Examples of heuristics that can be used for the identification of a register include the name of the device, the device being constructed from an array of memory cells, the existence of clock ports, load ports and input and output data ports of the same width n, and the use or location of this device in a design (such as connected to the data output of an arithmetic-logic unit or ALU since a register is usually placed there). The identification of the clock port, for example, could be achieved by the analysis of the name of the port, by its connection to other external or internal clock ports, by the type of the signal carried, or by the dimension of the port (since other ports of the cell, such as the data ports, are generally larger).

The analysis of implicit design semantics provides, undoubtedly, an easy way to reach conclusions. Clearly, the nature of these design semantics is different from that of the electrical and logical data. The intuitive ideas which are formed about the objects of a design represent a higher level of abstraction than the level of abstraction of the mathematical data. As a result, more flexible ways of reasoning are possible which allow many unwise alternatives to be rapidly discarded. A penalty to pay with the analysis of this kind of data is a degree of uncertainty associated with the knowledge obtained (since the rigorous logical and electrical data is avoided). This is often compensated by the simplicity with which results can be attained.

In any case, the knowledge acquired can be adjusted or refined with the study of the more detailed electronic data. This study can be postponed until it is strictly necessary (e.g. when this type of knowledge is not sufficient to carry out a task or support an hypothesis) and it can be guided by the heuristic information already generated. As a matter of fact, human experts often subordinate the study of the elaborate mathematical information to the analysis of design semantics. Of course, a system that exploits only these semantics cannot understand most of the detail behind a hardware description. However, it is convenient for the capture of important design characteristics and for the presentation of the design with semantic information that can be useful for CAD tools (and for human experts too).

#### 1.3 Methodology

A procedure for the machine simulation of the heuristic way of reasoning outlined above is discussed in this section. The procedure must exploit design semantics which are implicit in the description of the design. As discussed in the above section, human experts initially obtain intuitive ideas about the possible purpose or operation of some of the objects of a design. This is mainly based on the resemblance of semantic information to knowledge about electronic design that the experts possess. Next, they repeatedly test and refine these ideas after studying the context in which each object appears.

In fact, this way of reasoning is typical of the manner in which humans analyse different situations of the real world. The initial extraction of ideas about parts of a situation is mostly an intuitive process based on the observation of some *characteristic* information. These ideas can be seen as models abstracted from the actual reality. Next, these ideas are reorganised or modified according to the relationships between different objects. A clear example is the observation of a picture. In its simplest form, a picture drawn by a child generally contains a poor representation of a real world situation, but it allows a viewer, in most cases, to form a mental idea of the situation that the picture attempts to represent. Some of the objects in the picture will be more or less obvious. Other objects may not be clear at all, but their contexts in the picture may throw light on their intentions. The picture may be indeed simple, but the little information available often characterises quite well the real situation. For a computer, it ought to be easier to realise the real world situation from the analysis of the naive picture than from the analysis of a more elaborated picture in which most of the characteristic information may well be hidden by the large amount of data. Because the process is only driven by characteristic information, this way of reasoning reflects expertise and common sense rather than a systematic way of approaching the solution.

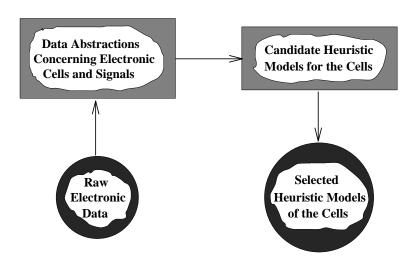

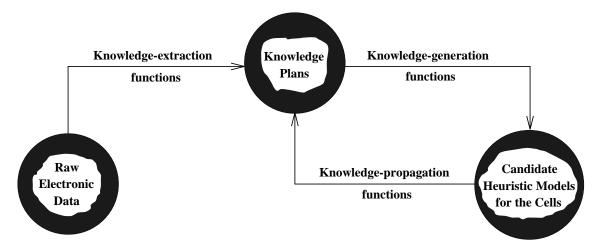

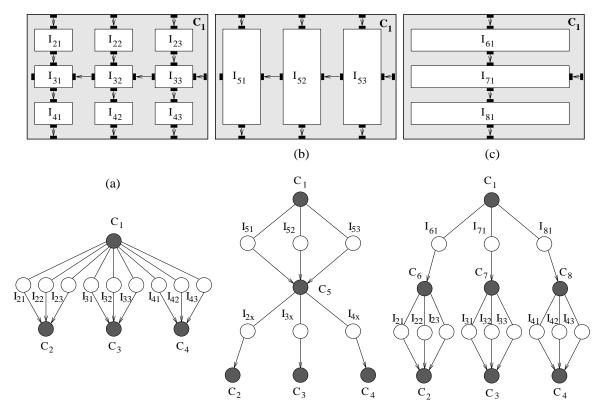

For the understanding of an electronic design, the system must initially capture a set of arrangements or plans for the heuristic knowledge about its cells (and its signals). These *knowledge plans* are derived from the interpretation of semantic information contained in the designer's specification. For a cell, knowledge plans can be extracted from the definition of the cell (cell object) or from each use of a cell in the design (instance objects). The functions used for the extraction of these plans are called *knowledge*-*extraction functions*. Examples of these functions are based on the analysis of the names of the objects, on the study of the size of the objects, on inferences drawn from the grouping of objects and on relationships derived from the hierarchy of the design.

Plans of the knowledge about a cell are compared with system information. Examples of system information include knowledge about classes of electronic cells typically used in electronic circuits and knowledge about electronic cells obtained from the processing of previous designs. The successful comparison of a plan for a cell with system information results in candidate *heuristic models* for the cell. The generation of a model for a cell implies that knowledge available in a plan is validated by the system. The model includes information about the functionality of the cell and its ports. The functions used for this comparison are called *knowledge-generation functions* since a model can contain additional knowledge provided by the system. This is supported by the fact that the items of knowledge existing in the initial plan are known to the system as 'usually' being associated with some other items of knowledge. In this sense, a model is an augmented plan (i.e. a plan with additional knowledge) with respect to the initial plan. A number of different model candidates may be possible for any cell since, for example, different plans can be initially formed.

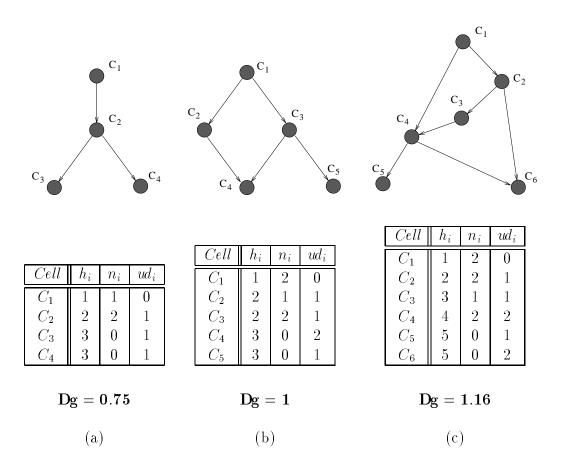

Consistency must be kept between the models of the cells. This is because the cells and signals of a design have relationships between them as discussed in the previous section. Since a number of models may be possible for each cell, the system must search for a set of consistent models (*solution set*) which 'best' represents the cells of a design (considering one model for each cell of the design). The consideration of all possible combinations of models for the cells of a design leads to a combinatorial explosion (the search space grows exponentially with the number of cells in the design). Even for designs with just a few cells and several candidate models for each cell it will not be feasible in general to consider an exhaustive search for the 'best' solution set. Because of this, more heuristic mechanisms must necessarily take over in order to select the 'best' candidate set which is to be considered first without having to generate all the possible sets. These heuristic mechanisms are based on a pseudo-probabilistic measure of the confidence in each model and in the knowledge represented. The evaluation measures of the models for each cell are combined to give a pseudo-probabilistic measure of the confidence in the overall solution set.

The need for consistency between the models selected for each cell may lead to the addition of further heuristic knowledge in the models of interrelated cells and signals or to the discarding of an alternative combination of models for the cells of the design. The functions used for this examination are called *knowledge-propagation functions* since knowledge about an object can essentially be propagated from interrelated objects. Examples of these functions are based on the analysis of the connectivity of the cells, on the examination of knowledge to a model of a cell results in a new plan for this cell. In the worst case, the study of each valid combination of alternative models could result in a new set of plans for each one of the cells of the design. A new set of plans can again be compared with system information to generate an additional number of new models. Broadly speaking, this starts a new *knowledge-generation/knowledge-propagation cycle* (reasoning cycle) and the process is repeated until no more new models can be obtained for any of the cells of the design from the best solution set hitherto generated.

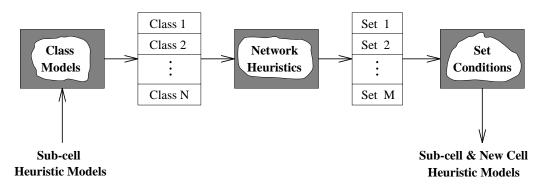

In short, the task of the system is the generation and selection of models for the cells (and signals) of a design in a way that avoids the combinatorial explosions which can arise. The functions for the derivation of knowledge can be classified in three groups. The first two, knowledge-extraction and knowledge-generation functions, are aimed at recognising the different cells of the design and they are said to perform *recognition-targeted reasoning*. They simulate the human ability of abstracting models for the design cells. The third group of functions, knowledge-propagation functions, are aimed at studying the consistency between the models of the different cells of the design. These functions simulate the human ability of analysing the relationships between the different cells and the signals which interconnect them and they are said to perform *model-based reasoning*. In addition, the system is controlled by functions which allow the selection of models and the evaluation of the confidence in the knowledge represented in a pseudo-probabilistic way.

#### 1.4 Artificial Intelligence

Most of the research presented in this thesis has been developed within the framework of knowledge engineering and applied Artificial Intelligence (AI). AI researchers bear in mind

the initial purpose of AI of creating a computer which thinks or, at least, can simulate human mental faculties by means of computational models. After several decades of research, the feasibility of creating such machines remains very controversial. Advocates and skeptics of AI still plunge into passionate discussions about the rationale or absurdity of the project [Pen89]. This is not surprising since the question touches upon deep issues of philosophy. For instance, what does it mean to say that a human thinks or understands something? With clear answers to questions like this, the end of the AI debate would perhaps not be a long way off. However, these answers have yet to come.

Whatever the outcome of the AI debate is, the conviction has grown that this technology provides worthwhile solutions in a diverse range of problem domains. AI has branched into a number of different areas — vision, natural language, robotics, planning, learning, expert systems — which correspond to diverse intelligent human activities. All these areas, though probably still in an embryonic state of development, already provide technological solutions for current industrial problems. From a quick look at these areas of research and the results obtained, one important point immediately arises: human beings can easily perform actions which, when simulated in a computer, involve a vast body of knowledge with complex interactions. Enthusiastic AI supporters are not impressed by this. For example, the fact that humans can see in the twinkle of an eye what requires millions of computations in a computer is being attributed to evolutionary fortuities which have specially prepared human brains to perform these types of tasks. Thus, the important point behind the impressive human faculties is not only the biological structure of human brains that supports the realisation of these actions but also the actual way in which humans achieve them. Here lies the central dogma of AI. If what the brain does can be thought of, at some level, as a kind of computation, the AI project should succeed.

Encouraged by this, AI researchers have been very concerned with making machines *understand*, specially in areas such as natural language. Of course, the grounds on which it would be possible to defend a claim that a machine understands anything are not yet clear (and, most likely, neither are the arguments required to impute human understanding!) [Jac90]. However, some of the grounds that seem necessary for this understanding to occur have been less questionable and they have formed an important part of AI research. These grounds are taken into account in this work to measure the ability to heuristically understand the specification of a design. They include:

- i the power to represent knowledge about the domain and the ability to use it effectively.

- ii the ability of the machine to perceive equivalences or analogies between different representations of the same or similar situations.

- iii an ability to learn in some non-trivial way. This usually involves the integration of new information with already existing knowledge, perhaps in a way that modifies both.

The early periods of AI research are characterised by the attempt to solve problems which require these kinds of computer understanding. A main topic of research of this period corresponds to the search for general purpose problem-solving methods for large classes of problems (such as those that can be characterised as search problems [CM85]). Day after day, researchers have gained more insight about the actual ways in which humans solve problems. They have realised that general methods of problem-solving underestimate the domain-specific knowledge and common sense that human experts possess. As a consequence, the period of AI research that stretches from the second half of the 1970s to the present day has been characterised by a greater orientation towards solving domain-specific problems [Jac90]. This period of research has put emphasis on the acquisition and representation of the relevant domain knowledge which a program accesses, rather than on the actual way in which the program is executed. The knowledge of the program or *knowledge base* is kept separate from the code that executes the program or *inference engine*. These knowledge-intensive programs are referred to as knowledge-based (KB) systems <sup>1</sup>. The process of constructing these systems is often called knowledge engineering and is considered to be *applied AI*.

Many knowledge-based CAD tools have appeared during the last decade for tasks as diverse as diagnosis and hardware synthesis. The use of KB techniques for CAD has been very much encouraged by the perceived success of the application of this technology to a diverse range of domains, including organic chemistry, mineral exploration and internal medicine. In these domains, KB systems show, in general, quite satisfactory levels of performance when large bodies of expert knowledge are encoded in rule-based knowledge bases [HR85]. This technology has not been so successful in the domain of CAD for very large scale of integration (VLSI) designs, despite the large wealth of knowledge required for the design of these circuits and the complexity of the design process [RKCM85]. A major reason for this is to be found in the different nature of the expert knowledge required in this domain. KB systems appear to work best in domains where there is a substantial body of empirical knowledge connecting situations to actions, but there is little information about the causal mechanisms underlying the case investigated. For example, the rules of knowledge would typically reflect empirical associations of facts derived from experience instead of a theory of the way in which a device or an organism under investigation actually works. A deeper representation of the domain, in terms of spatial, temporal or causal models, is often avoided, or considered unnecessary. Thus, the knowledge used in these KB systems is often called *shallow* as opposed to what is sometimes called *deep* knowledge.

Shallow KB systems reason about a problem with a very limited understanding of the domain. They are characterised by a sparse or bare representation of knowledge. For example, a rule such as "if a cell is a register then the cell has memory" states that any electronic cell which operates as a register has memory. With such a sparse representation there are in general few possibilities in reasoning. For example, the matching of a condition (such as the cell operating as a register) to pre-defined alternatives must be

<sup>&</sup>lt;sup>1</sup>KB systems are aimed at the representation and manipulation of domain knowledge, though no actual reasoning may take place. KB systems which have the ability to reason about the knowledge represented are called expert systems [Jac90]. For the sake of generality, the term KB system is used in this work to refer to all these systems.

exact. Most important of all, a problem with shallow systems is that they tend to represent only individual items of knowledge. For example, using this kind of representation it is not easy to represent the requirements for a generic electronic cell to have memory (specially if this is due to the way in which its sub-cells are interconnected). Instead, a specific-to-case approach is taken and the reality that a register cell has memory is simply stated for this particular case of electronic cells.

Deep knowledge-based (DKB) systems do not just have a single level of representation. A comparison of the most important features of these systems against their shallow counterparts is shown in table 1.1 [Mor90]. Layers of concepts are used in the representation of knowledge which provide a much richer structure and consequently a more sophisticated reasoning capability. The use of layers of concepts allows the consideration of general classes in deep systems as opposed to specific instances in shallow systems. In general, DKB systems provide more abstract ways of reasoning about a problem since the kinds of knowledge used are vague and imprecise in nature. On the other hand, shallow-based systems have a more precise representation of knowledge since they are aimed at individual items of information. However, this limits the reasoning capability of these systems. Finally, the control of deep systems is more complex because of the enhanced reasoning capability.

| Features                   | Shallow            | Deep                     |

|----------------------------|--------------------|--------------------------|

| Levels of Concepts         | single level       | multiple levels          |

| Structure                  | simple             | $\operatorname{complex}$ |

| Distinctness               | specific instances | general classes          |

| Precision, resolution      | high               | low                      |

| Reasoning, representations | sparse             | $\operatorname{rich}$    |

| Control                    | less               | more                     |

Table 1.1: Shallow and Deep Systems