# Une Méthodologie de Conception de Circuits Asynchrones à Faible Consommation d'Energie: Application au Microprocesseur MIPS

K. Slimani

# ▶ To cite this version:

K. Slimani. Une Méthodologie de Conception de Circuits Asynchrones à Faible Consommation d'Energie: Application au Microprocesseur MIPS. Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble - INPG, 2004. Français. NNT: . tel-00008328

# HAL Id: tel-00008328 https://theses.hal.science/tel-00008328

Submitted on 2 Feb 2005

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

| N° | attr | ibué | par | la bi | bli | othè | eque |

|----|------|------|-----|-------|-----|------|------|

| /  | /    | //   | /_  | _/_   | _/_ | _/_  | _/   |

## THESE

Pour obtenir le grade de

### **DOCTEUR DE l'INPG**

Spécialité : Micro et Nano Electronique

Préparée au laboratoire TIMA dans le cadre de L'Ecole Doctorale d'« Electronique, Electrotechnique, Automatique, Télécommunications, Signal »

Présentée et Soutenue publiquement

Par

### Kamel SLIMANI

Le 16 décembre 2004

Titre:

# UNE METHODOLOGIE DE CONCEPTION DE CIRCUITS ASYNCHRONES A FAIBLE CONSOMMATION D'ENERGIE: APPLICATION AU MICROPROCESSEUR MIPS

Directeur de Thèse : Marc Renaudin Codirecteur : Gilles Sicard

### **JURY**

Mme. Nathalie Julien , Présidente M. Christian Piguet , Rapporteur M. Jean-Didier Legat , Rapporteur M. Marc Renaudin , Directeur M. Gilles Sicard , Codirecteur

À la Mémoire d'Amé Youcef Et de Moez Ouni

# Remerciements

La thèse a été effectuée au laboratoire TIMA (Techniques de Informatique et de la Microélectronique pour l'Architecture des Ordinateurs) sur le site Viallet de l'Institut National Polytechnique de Grenoble. Je remercie le directeur du laboratoire Bernard Courtois pour m'y avoir accueilli.

Je remercie mon directeur de thèse Marc Renaudin professeur à l'ENSERG pour m'avoir accueilli au sein de son groupe de recherche Concurrent Integrated Circuit (CIS). Je le remercie pour m'avoir permis de côtoyer le monde passionnant de la conception asynchrone. Je voudrais aussi sincèrement le remercier pour son appui technique, pour sa gentillesse et son humour

Je tiens à remercier les membres du jury:

Nathalie Julien professeur à l'Université de Bretagne Sud pour m'avoir fait l'honneur de présider le jury de ma thèse.

Christian Piguet professeur au Swiss Center for Electronics and Microtechnology (CSEM) et Jean-Didier Legat Professeur à l'Université Catholique de Louvain pour avoir accepté d'être les rapporteurs de ma thèse. Je leur suis très reconnaissant de la qualité et de l'analyse intéressante de leurs rapports.

J'exprime ma gratitude à mon codirecteur Gilles Sicard maître de conférence à l'Université Joseph Fourier pour sa disponibilité, pour son retour très intéressant et pour son aide à la rédaction du manuscrit. Je voudrais aussi saluer sa gentillesse, sa simplicité et sa passion pour la Formule 1. Je n'oublierais jamais son agréable compagnie à Santorin.

Je tiens à remercier chaleureusement les membres du groupe CIS pour leur sympathie quotidienne, pour leur convivialité et pour les nombreuses activités qu'on a pu faire ensemble (ordre alphabétique) :

Alain (Mr opérateur arithmétique), Amine (mon fidèle compagnon de bureau), Anh Vu, Antoine, Arnaud, Aurélien, Bertrand, Cédric, David, Dhanistha, Estelle, Fabien (le roi des blagues), Fraidy (soirée au D'ombolo ça te dit), Gautier, Isabelle, JB (sa cheminée c'est la caverne d'Ali Baba), Jérôme, Joao & Marianna (alors ce bowling !!!), Julien, Laurent, Livier, Manu (toujours partant pour un verre, il est pas encore arrivé le train de Paris!!), Momo (alors marocain, tac tac tac), Philippe le montpelliérain, Salim (le kabyle), Sophie, Thibaut, Vivien, Yann (le photographe de choc), Yannick ('a' 'o' 'i' tout doux).

Je voudrais aussi sincèrement remercier toutes les personnes que j'ai connues à TIMA et qui ont fait que la vie au laboratoire était si sympathique. Je ne peux malheureusement pas toutes les nommer, je citerais quelques noms seulement :

Aimen, Amel, Amer (merci le gadgeot), Aziz, Damien (le néo canadien), Faiza, Férid, Greg, Iuliana (Ibiza c'est pour quand?) et Kati, Karim, Khirddine, Lobna, Marius, Menouer, Nacer, Nadir (fais le maximum!), Wassim, Yanick.

Je voudrais exprimer par la même occasion ma gratitude au personnel fort sympathique de TIMA, CMP et du CIME : les professeurs, les maîtres de conférence, les administrateurs réseaux et les très souriantes secrétaires.

J'adresse en particulier mes remerciements aux personnes qui m'ont très gentiment et très efficacement apporté leur aide lorsque je les sollicitais. Qu'Alexandre Chagoya et que Kholdoun reçoivent ma sincère gratitude.

Je remercie mes amis d'enfance et du football que je ne peux pas me risquer à nommer de peur d'en oublier. Je remercie également mes amis des virées nocturnes du week-end (Fabrice, Caro, Clarisse).

Enfin je terminerais par remercier de tout mon cœur mes parents et toute ma famille pour l'amour qu'ils me donnent chaque jour et pour la confiance qu'ils m'accordent.

# Résumé

L'évolution effrénée de la complexité des appareils portables s'accompagne d'une augmentation de la consommation d'énergie qui rend l'autonomie de ces appareils très limitée. Pour accroître l'autonomie des systèmes embarqués tels que les téléphones ou les ordinateurs portables, de nombreuses recherches sur la conception de circuits intégrés ont été réalisées en vue de réduire la consommation d'énergie.

Ces travaux de thèse ont pour but de proposer au concepteur des moyens de concevoir des circuits intégrés numériques à faible consommation d'énergie. Trois étapes importantes vers la réduction de la consommation d'énergie ont été proposées. L'utilisation de la logique asynchrone représente le premier pas vers la réduction de la consommation d'énergie. En effet, de nombreux travaux réalisés ces dernières années ont montré que les circuits asynchrones présentent la propriété intrinsèque de consommer moins d'énergie que les circuits implémentés en logique synchrone. Le second pas important est d'offrir au concepteur des outils lui permettant d'obtenir des informations sur l'activité et la consommation d'énergie du circuit lors de la conception de celui-ci. Nous avons spécifié un estimateur d'activité et un estimateur de la consommation d'énergie qui permettent au concepteur de collecter des informations pertinentes sur la répartition de l'activité et de la consommation d'énergie d'un circuit lors d'une simulation donnée. L'avantage de ces estimateurs est que les informations sont obtenues très tôt dans le flot de conception, au niveau de la spécification CHP d'un circuit. Enfin, des techniques d'optimisation sont proposées pour réduire la consommation d'énergie des circuits. Certaines techniques sont utiles à l'outil de synthèse (pour la synthèse automatique de circuits à faible consommation d'énergie) et d'autres sont utiles au concepteur pour le guider dans ses choix d'implémentation.

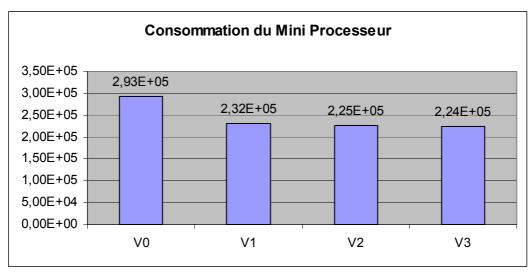

La méthodologie d'estimation et les techniques d'optimisation de la consommation d'énergie ont été appliquées à la réalisation d'un mini processeur, les résultats ont montré une réduction de la consommation d'énergie de 24%.

**Mots-clés**: Circuits asynchrones, faible consommation d'énergie, estimation d'activité, estimation de la consommation d'énergie, techniques d'optimisation, synthèse faible consommation d'énergie, implémentation faible consommation.

# Abstract

The steady evolution of mobile device complexity comes with an increase of the energy consumption which dramatically limits the autonomy of these devices. To increase the autonomy of embedded systems such as portable phones or computers, several researches on integrated circuit design have been performed in order to reduce the energy consumption.

This Phd work aims at proposing to the designer the means to design low energy digital integrated circuits. Three important steps have been proposed in this work to reduce the energy consumption of circuits. The first step is to use asynchronous logic to design circuit. Indeed, several works achieved these last years have shown that asynchronous logic can significantly reduce the energy consumption of circuits. It is an intrinsic property of asynchronous logic. The second step is to offer tools that allow the designer to get information on the activity and the energy consumption of a circuit during the design flow. An activity estimator and an energy estimator have been specified that allow the designer to get relevant information on the distribution of the activity and the energy within a circuit during a specific simulation. The inherent advantage of these estimators is to provide information on the activity and the energy very early in the design flow, at the CHP specification. Finally, optimisation techniques have been defined to reduce the energy consumption of circuits. Some techniques can be integrated in the synthesis tool (for automatic low energy-oriented synthesis) and other techniques can be useful to guide the designer in his implementation choices.

The estimation methodology and the energy consumption optimisation techniques have been applied to the implementation of a mini processor. The results have shown an energy consumption reduction of 24%.

**Keywords**: Asynchronous circuits, low energy consumption, activity estimation, energy consumption estimation, optimisation techniques, low energy consumption synthesis, low consumption design.

# Table des Matières

| Remerciemo | ents                                                          | VII    |

|------------|---------------------------------------------------------------|--------|

| Résumé     |                                                               | ix     |

| Abstract   |                                                               | X      |

|            | latières                                                      |        |

|            | gures                                                         |        |

|            | bleaux                                                        |        |

|            |                                                               |        |

|            | n                                                             |        |

| Chapitre 1 | Etat de l'art : Logique asynchrone, Consommation d'Energie et |        |

| Microproce | sseurs Asynchrones                                            | 5 -    |

| 1.1 Lo     | gique Asynchrone                                              | - 5 -  |

| 1.1.1      | Asynchrone versus Synchrone                                   |        |

| 1.1.2      | Les principes de base de l'asynchrone                         |        |

| 1.1.2      | 1 1                                                           |        |

| 1.1.2      |                                                               |        |

| 1.1.2      | <u> </u>                                                      |        |

| 1.1.3      | Les logiques asynchrones                                      |        |

| 1.1.3      |                                                               |        |

| 1.1.3      | · /                                                           |        |

| 1.1.3      |                                                               |        |

| 1.1.3      | 1 1                                                           |        |

| 1.1.4      | Les Bufferisations                                            | 15 -   |

| 1.1.4      |                                                               |        |

| 1.1.4      | • •                                                           |        |

| 1.1.4      | .3 La bufferisation PCHB                                      | 17 -   |

| 1.1.4      | .4 La bufferisation PCFB                                      | 18 -   |

| 1.2 La     | consommation d'énergie                                        | 18 -   |

| 1.2.1      | Les techniques d'estimation de la consommation d'énergie      | 19 -   |

| 1.2.2      | Les techniques d'optimisation de la consommation d'énergie    | 20 -   |

| 1.2.2      | .1 Pipeline asynchrone                                        | 20 -   |

| 1.2.2      | .2 Structure de contrôle                                      | 22 -   |

| 1.2.2      | 1                                                             |        |

| 1.2.2      |                                                               | 23 -   |

| 1.2.2      | ı J                                                           |        |

| 1.2.3      | Autres techniques                                             |        |

| 13 Le      | s Micronrocesseurs asynchrones                                | - 26 - |

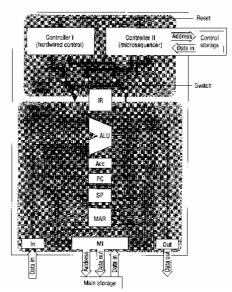

| 1.3.1      | Caltech Asynchronous Processeur (CAP)                                    |                 |

|------------|--------------------------------------------------------------------------|-----------------|

| 1.3.2      | Philips 80C51 asynchrone                                                 | 27 -            |

| 1.3.3      | AMULET                                                                   | 29 -            |

| 1.3.4      | ASPRO                                                                    | 33 -            |

| 1.3.5      | MICA                                                                     | 34 -            |

| 1.3.6      | TITAC                                                                    | 35 -            |

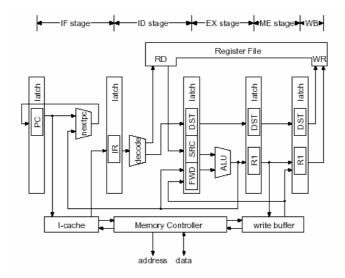

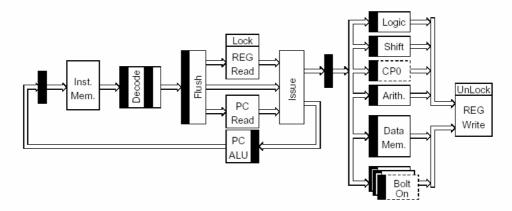

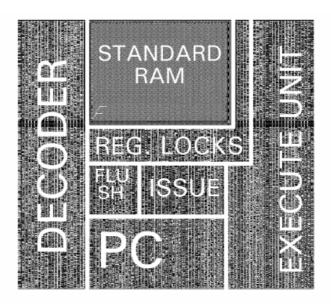

| 1.3.7      | MiniMips                                                                 | 38 -            |

| 1.3.8      | Asynchronous TinyRISC (ARISC)                                            | 39 -            |

| 1.3.9      | Lutonium                                                                 | 41 -            |

| 1.3.10     | Autres Microprocesseurs asynchrones                                      | 42 -            |

| 1.3.11     | Récapitulatif des microprocesseurs asynchrones                           | 45 -            |

| 1.4 Con-   | clusion                                                                  |                 |

| Chapitre 2 | Estimation de la Consommation d'Energie d'un Programme CHP               | 47 -            |

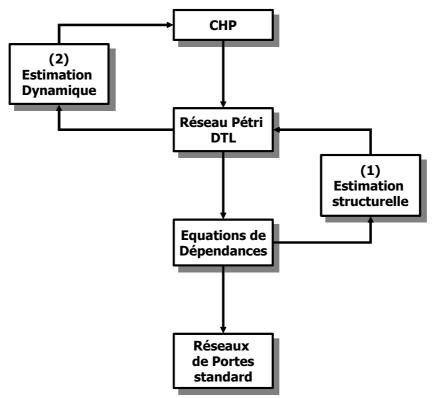

| 2.1 Métl   | hodologie d'estimation de la consommation d'énergie                      | _ 47 _          |

|            | mation de la consommation d'énergie structurelle                         |                 |

| 2.2.1      | Coût intrinsèque des commandes gardées                                   |                 |

| 2.2.1.1    | · · · · · · · · · · · · · · · · · · ·                                    |                 |

| 2.2.1.2    | <del>_</del>                                                             |                 |

| 2.2.1.3    |                                                                          |                 |

| 2.2.1.4    |                                                                          |                 |

| 2.2.1.5    |                                                                          |                 |

| 2.2.1.3    | Coût d'intersection des branches                                         |                 |

| 2.2.3      | Consommation des portes                                                  |                 |

| 2.2.4      | Consommation des architectures de base                                   |                 |

| 2.2.4.1    |                                                                          |                 |

| 2.2.4.2    |                                                                          |                 |

| 2.2.4.3    |                                                                          |                 |

| 2.2.4.4    |                                                                          |                 |

| 2.2.4.5    | e                                                                        |                 |

| 2.2.4.6    | 1                                                                        |                 |

|            | mation de la consommation d'énergie dynamique                            |                 |

| 2.3.1      | Labellisation du réseau de pétri                                         |                 |

| 2.3.2      | Calcul du coût dynamique                                                 |                 |

|            | lication à une architecture hétérogène                                   |                 |

|            | clusion                                                                  |                 |

| Chapitre 3 | Spécification des Outils d'Estimation                                    |                 |

| •          | -                                                                        |                 |

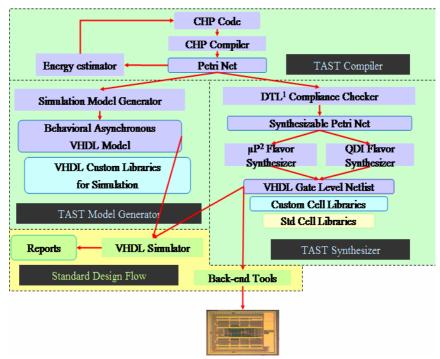

|            | entation du flot TAST                                                    |                 |

| 3.1.1      | Le compilateur CHP                                                       |                 |

| 3.1.2      | Le simulateur de Pétri Net<br>Le convertisseur CHP vers VHDL fonctionnel |                 |

| 3.1.3      |                                                                          |                 |

| 3.1.4      | L'outil de synthèse Quasi Insensible aux Délais                          |                 |

| 3.1.5      | L'outil de synthèse Micropipeline                                        |                 |

| 3.2 Estin  | mateur d'activité                                                        | . <b>-</b> 77 - |

| 3.2.1      | Format du fichier Trace                                       | 99 -    |

|------------|---------------------------------------------------------------|---------|

| 3.2.2      | Exemple                                                       |         |

| 3.2.3      | Caractéristiques de l'estimateur d'activité                   | 106 -   |

| 3.2.3      | 1 Couverture de code                                          | 106 -   |

| 3.2.3      | 2 Trace                                                       | 106 -   |

| 3.2.3      |                                                               |         |

| 3.3 Est    | timateur de la consommation d'énergie                         |         |

| 3.3.1      | Principe de l'estimateur de la consommation d'énergie         |         |

| 3.3.2      | Caractéristiques de l'estimateur de la consommation d'énergie |         |

|            | nclusion                                                      |         |

| Chapitre 4 | Exploration Architecturale et Optimisation de la Consommatio  |         |

| d'Energie  | - 115 -                                                       |         |

| 4.1 Sy     | nthèse orientée faible consommation d'énergie                 |         |

| 4.1.1      | Protocole de communication                                    |         |

| 4.1.2      | Bufferisation entrée/sortie                                   |         |

| 4.1.3      | Bufferisation mixte                                           | 125 -   |

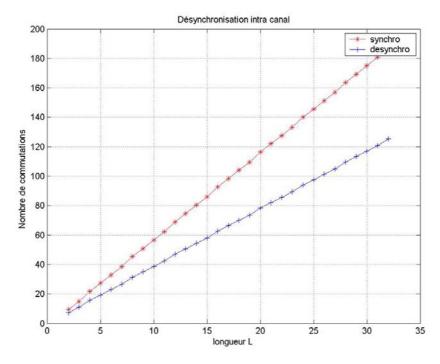

| 4.1.4      | Désynchronisation intra canal                                 | 126 -   |

| 4.1.5      | Ajout de synchronisation                                      | 127 -   |

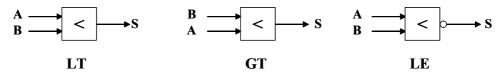

| 4.1.6      | Etude des opérateurs arithmétiques et logiques                | 129 -   |

| 4.2 Im     | plémentation CHP orientée faible consommation d'énergie       | 130 -   |

| 4.2.1      | Optimisation micro architecturale                             | 130 -   |

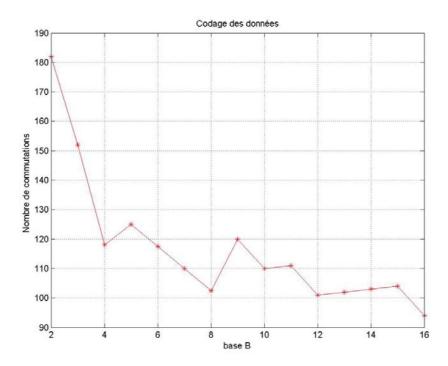

| 4.2.2      | Codage des données                                            | 131 -   |

| 4.2.3      | Adaptation de la taille des canaux de donnée                  | 132 -   |

| 4.2.4      | Désynchronisation inter canaux                                | 133 -   |

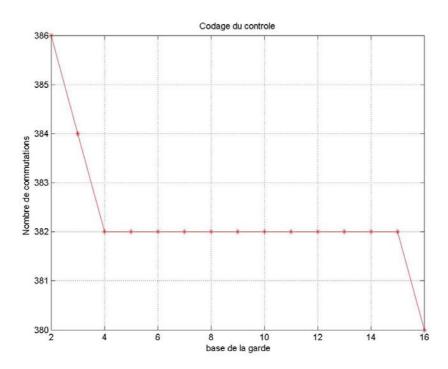

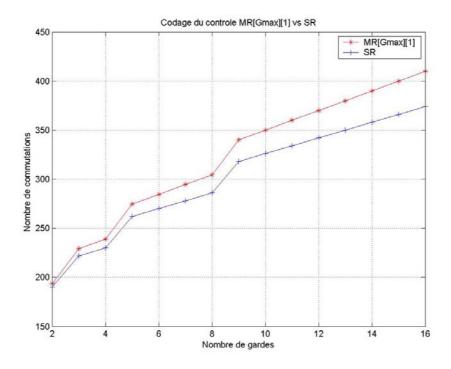

| 4.2.5      | Codage du contrôle                                            | 135 -   |

| 4.2.6      | Fusion des opérateurs                                         | 136 -   |

| 4.2.7      | Réduction de la synchronisation en cas d'exclusion mutuelle   | 139 -   |

| 4.2.8      | Structures de choix en fonction des probabilités              | 139 -   |

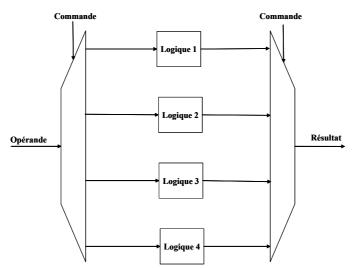

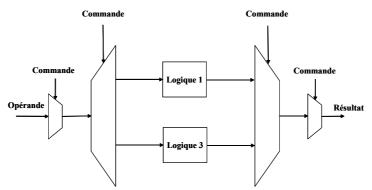

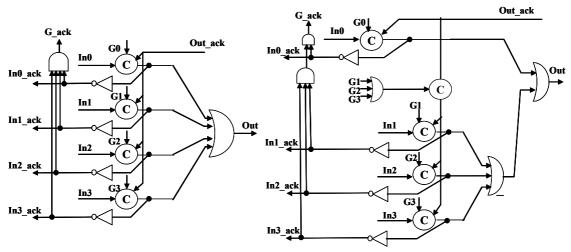

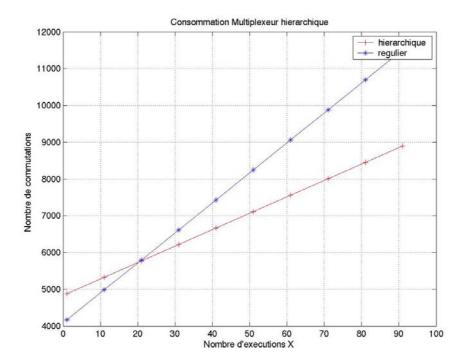

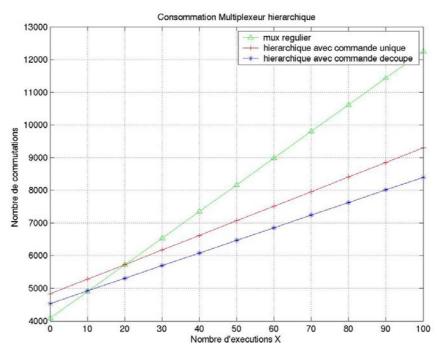

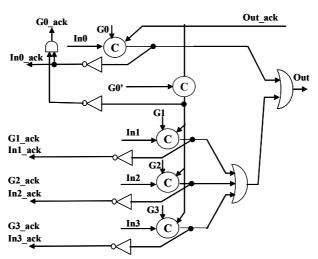

| 4.2.8      | 1 Structure de choix hiérarchique.                            | 139 -   |

| 4.2.8      | 2 Structure de choix hiérarchique avec commandes découpées    | 145 -   |

| 4.3 Co     | nclusion                                                      | 148 -   |

| _          | Application: Réalisation d'un Mini Processeur Asynchrone à F  |         |

| Consommat  | ion d'Energie                                                 | 149 -   |

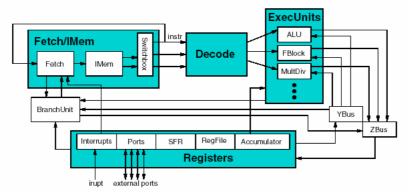

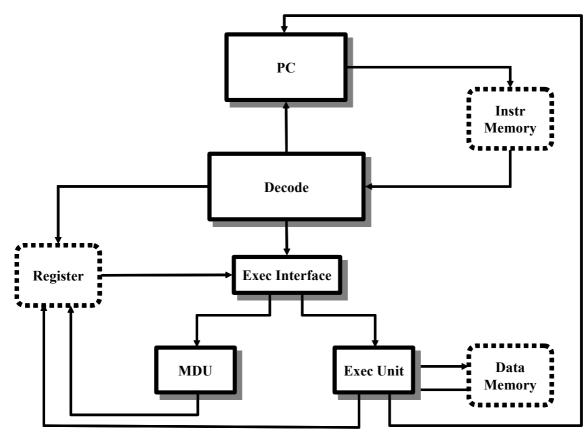

| 5.1 Ar     | chitecture du Mini Processeur                                 |         |

| 5.1.1      | Le compteur de programme (PC)                                 | 150 -   |

| 5.1.2      | Le décodeur (decode)                                          |         |

| 5.1.3      | L'interface d'exécution (Exec Interface).                     | 151 -   |

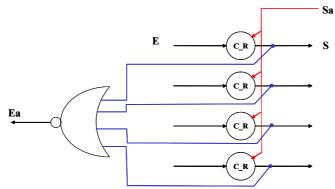

| 5.1.4      | L'unité d'exécution (Exec Unit)                               |         |

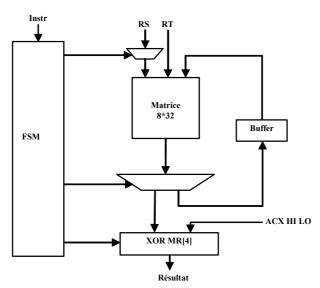

| 5.1.5      | L'unité de multiplication et division (MDU)                   |         |

| 5.1.6      | Le banc de registres                                          | 153 -   |

| 5.1.7      | Les mémoires                                                  |         |

| 5.1.7      | 1 Mémoire instruction (Instr Memory)                          | 154 -   |

| 5.1.7      |                                                               |         |

|            | ı d'instructions                                              |         |

| 5.3 Eta    | ones d'ontimisation du mini processeur                        | - 155 - |

| 5.3.1        | Version V0 : Forme primaire du mini processeur                     | 155 -   |

|--------------|--------------------------------------------------------------------|---------|

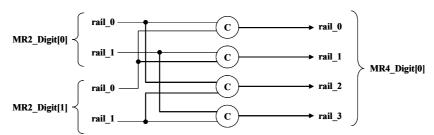

| 5.3.2        | Version V1: Mini processeur implémenté en codage 1 parmi 4         | 156 -   |

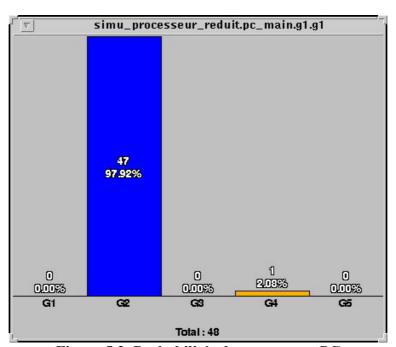

| 5.3.3        | Version V2 : Optimisation en fonction des probabilités d'exécution | 156 -   |

| 5.3.4        | Version V3 : Optimisation du contrôle                              | 163 -   |

| 5.4 Rés      | ultats                                                             | 163 -   |

| 5.4.1        | Consommation de l'ensemble du cœur du mini processeur              | 164 -   |

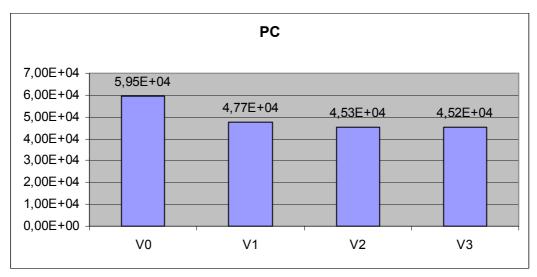

| 5.4.2        | PC                                                                 | 168 -   |

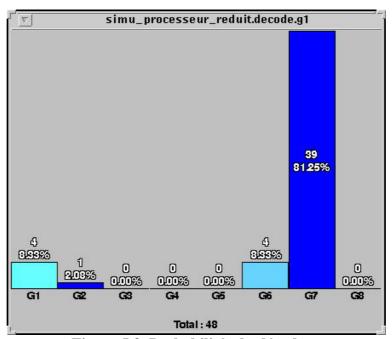

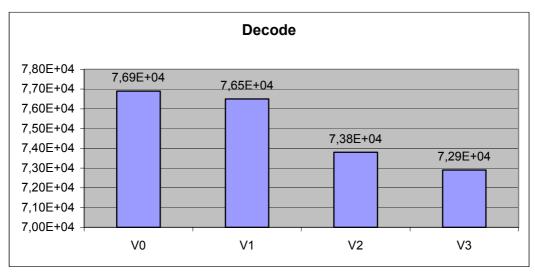

| 5.4.3        | Décodeur                                                           | 169 -   |

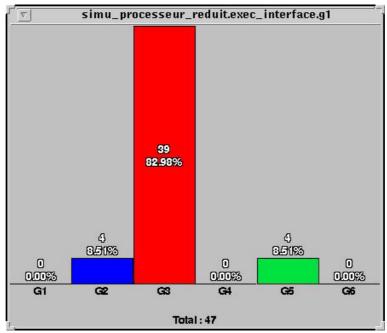

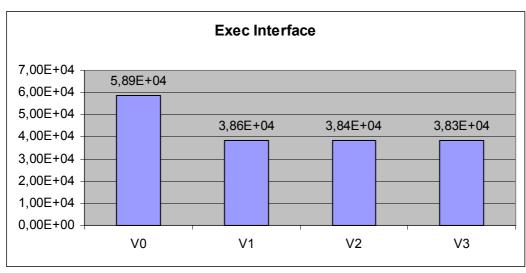

| 5.4.4        | Interface d'exécution                                              | 169 -   |

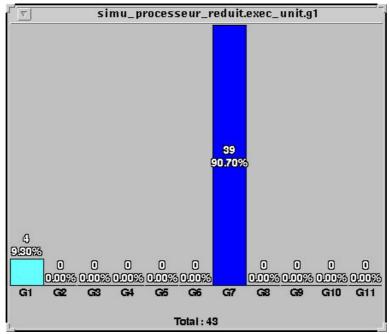

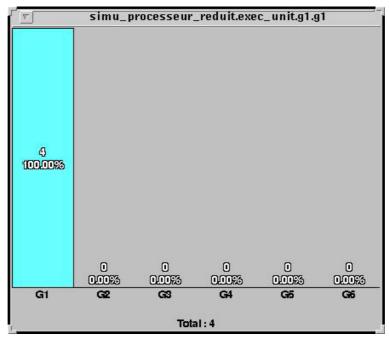

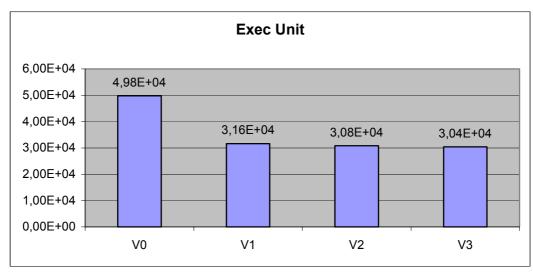

| 5.4.5        | Unité d'exécution                                                  | 170 -   |

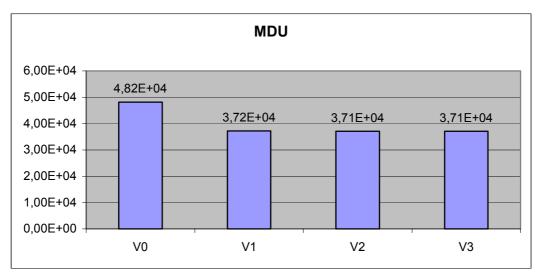

| 5.4.6        | La MDU                                                             | 171 -   |

| 5.5 Imp      | lémentation finale du mini processeur                              | 172 -   |

| 5.5.1        | Implémentation du cœur                                             | 172 -   |

| 5.5.2        | Implémentation du banc de registres                                | 173 -   |

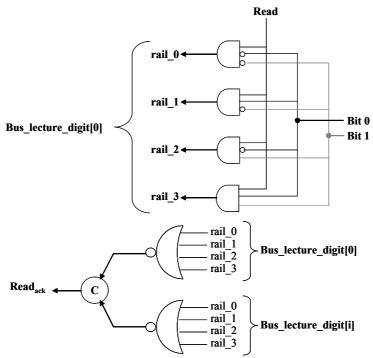

| 5.5.3        | Implémentation des mémoires                                        | 174 -   |

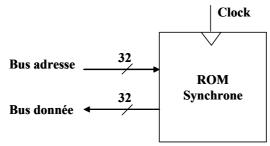

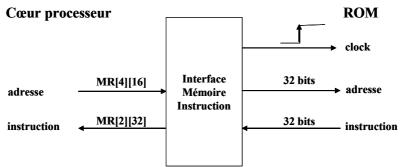

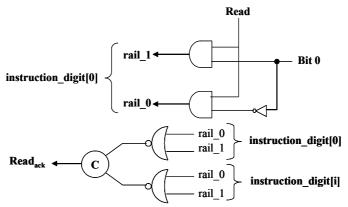

| 5.5.3.1      | Mémoire instruction                                                | 174 -   |

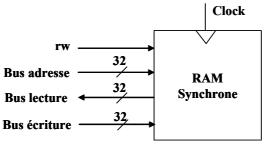

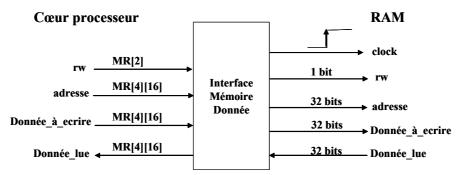

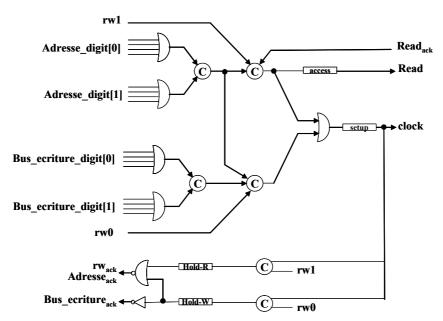

| 5.5.3.2      | 2 Mémoire donnée                                                   | 175 -   |

| 5.5.4        | Implémentation des interfaces                                      | 175 -   |

| 5.5.4.1      | Interface banc de registres                                        | 175 -   |

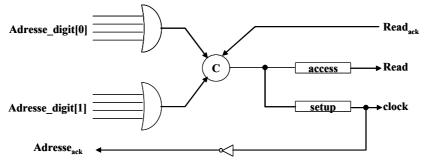

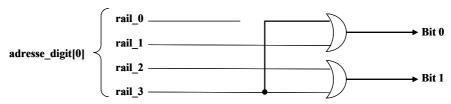

| 5.5.4.2      | 2 Interface mémoire instruction                                    | 176 -   |

| 5.5.4.3      | 3 Interface mémoire donnée                                         | 177 -   |

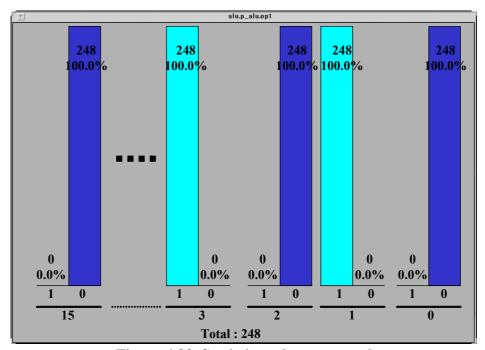

| 5.5.5        | Simulation du mini processeur                                      | 179 -   |

| 5.6 Con      | nclusion                                                           | 179 -   |

| Conclusion e | t Perspectives                                                     | 181 -   |

| Publications | et Réalisations Personnelles                                       | 185 -   |

| Bibliographi | e                                                                  | 187 -   |

| Anneve       |                                                                    | _ 195 _ |

# Liste des Figures

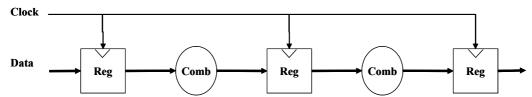

| Figure 1.1 Structure de base d'un circuit synchrone                                       | 5 -    |

|-------------------------------------------------------------------------------------------|--------|

| Figure 1.2 Structure de base d'un circuit asynchrone                                      | 6 -    |

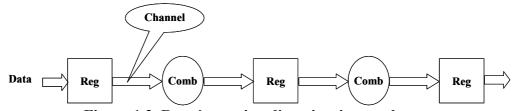

| Figure 1.3 Représentation d'un circuit asynchrone                                         | 8 -    |

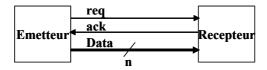

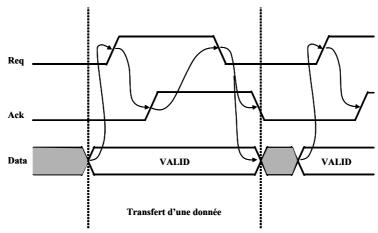

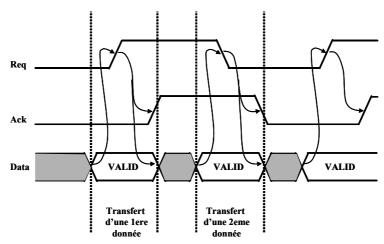

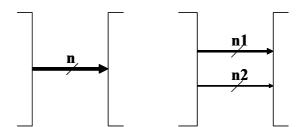

| Figure 1.4 Canal codé en donnée groupée                                                   | 9 -    |

| Figure 1.5 Codage donnée groupée associé au protocole 4 phases                            | 9 -    |

| Figure 1.6 Codage donnée groupée associé au protocole 2 phases                            |        |

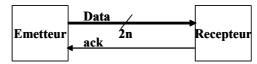

| Figure 1.7 Canal codé en double rail                                                      | - 11 - |

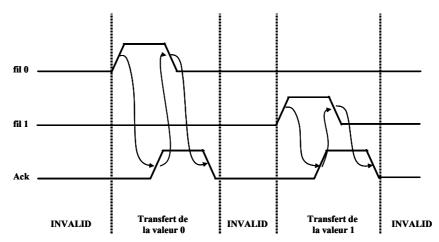

| Figure 1.8 Codage Double Rail associé au protocole 4 phases                               |        |

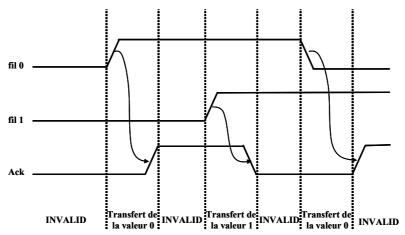

| Figure 1.9 Codage Double Rail associé à un protocole 2 phases                             |        |

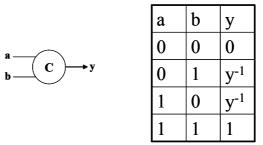

| Figure 1.10 Porte de Muller                                                               |        |

| Figure 1.11 Hypothèse circuit QDI (gauche) et SI (droite)                                 | - 14 - |

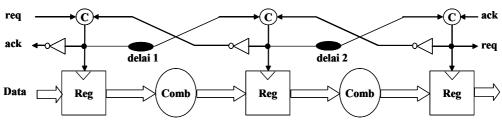

| Figure 1.12 Circuit micropipeline                                                         |        |

| Figure 1.13 Une table de flot (gauche) et la machine à état correspondante (droite)       | - 15 - |

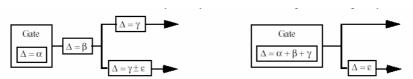

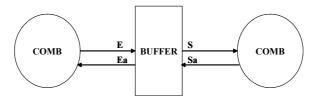

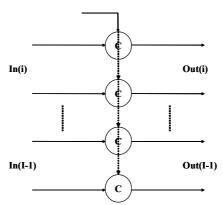

| Figure 1.14 Schéma général d'une bufferisation                                            |        |

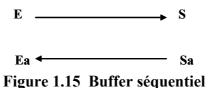

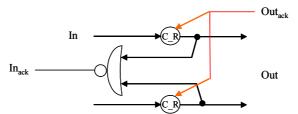

| Figure 1.15 Buffer séquentiel                                                             |        |

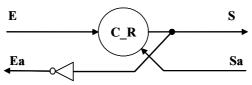

| Figure 1.16 Buffer WCHB                                                                   |        |

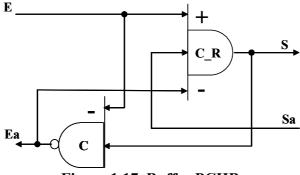

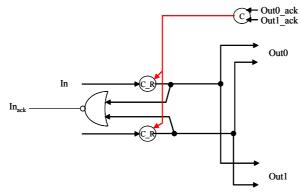

| Figure 1.17 Buffer PCHB.                                                                  | - 18 - |

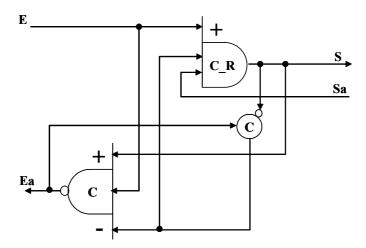

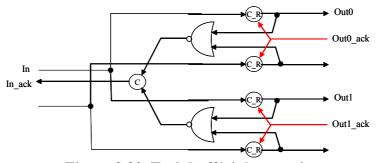

| Figure 1.18 Buffer PCFB                                                                   | - 18 - |

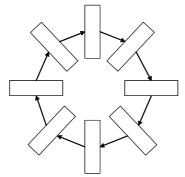

| Figure 1.19 Anneau de buffers                                                             |        |

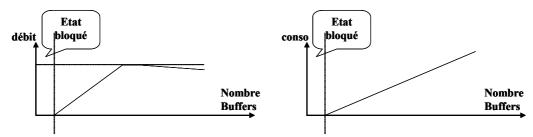

| Figure 1.20 Débit et Consommation en fonction du nombre de buffers                        |        |

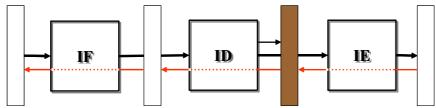

| Figure 1.21 Pipeline utilisant un lacth reconfigurable                                    |        |

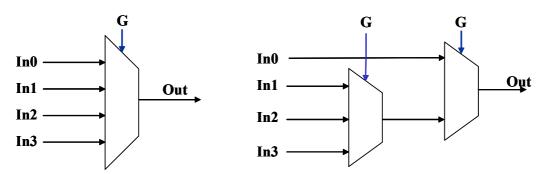

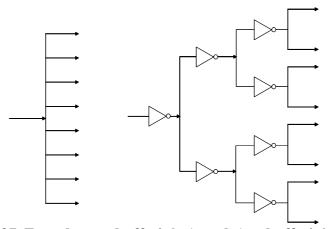

| Figure 1.22 Multiplexeur régulier et décomposé                                            |        |

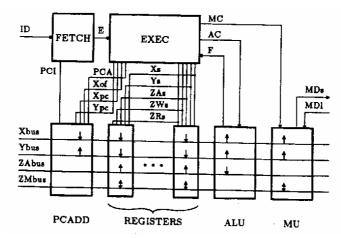

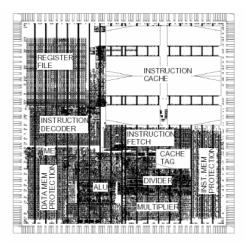

| Figure 1.23 Architecture du CAP.                                                          |        |

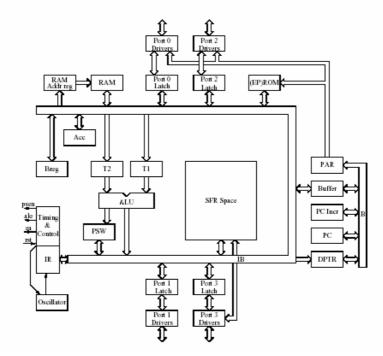

| Figure 1.24 Architecture du 80C51 asynchrone                                              |        |

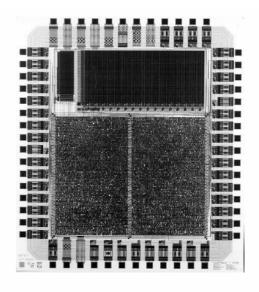

| Figure 1.25 Layout du 80C51 asynchrone                                                    |        |

| Figure 1.26 Architecture de AMULET1                                                       |        |

| Figure 1.27 Architecture de AMULET2e                                                      |        |

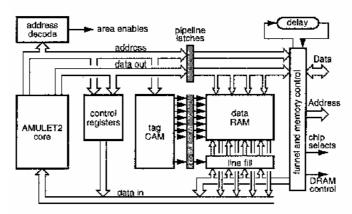

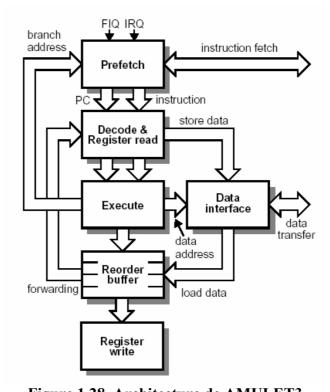

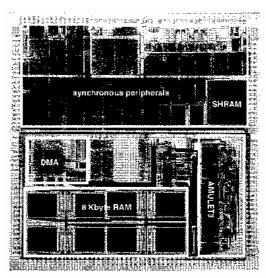

| Figure 1.28 Architecture de AMULET3                                                       | - 32 - |

| Figure 1.29 Système de contrôle DRACO                                                     |        |

| Figure 1.30 Architecture d'ASPRO                                                          |        |

| Figure 1.31 ASPRO.                                                                        |        |

| Figure 1.32 Architecture du processeur TITAC                                              |        |

| Figure 1.33 Architecture du processeur TITAC-2                                            |        |

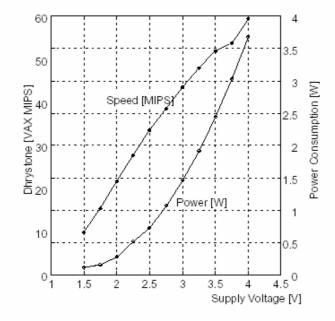

| Figure 1.34 Performances de TITAC-2 en fonction de la tension d'alimentation              | - 37 - |

| Figure 1.35 Layout de TITAC-2                                                             |        |

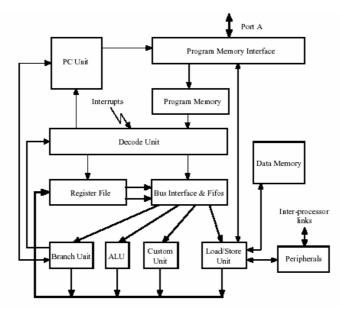

| Figure 1.36 Architecture du MiniMIPS                                                      | - 39 - |

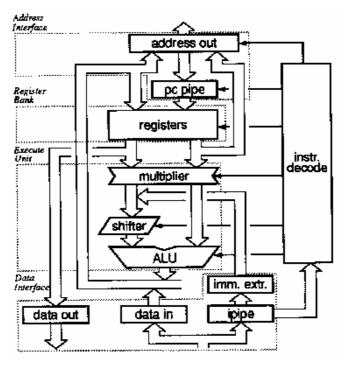

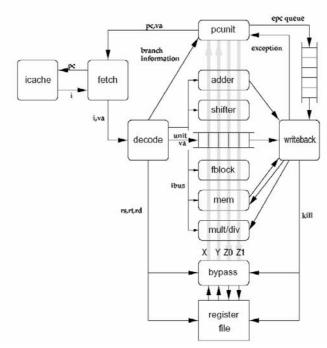

| Figure 1.37 Architecture du processeur Asynchronous TinyRISC                              | - 40 - |

| Figure 1.38 Layout du processeur Asynchronous TinyRISC                                    | - 40 - |

| Figure 1.39 Architecture de Lutonium                                                      |        |

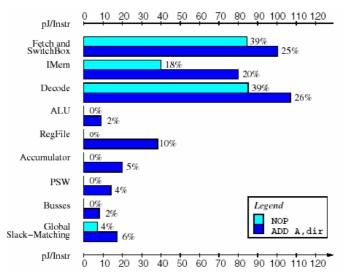

| Figure 1.40 Répartition de la consommation d'énergie dans Lutonium                        |        |

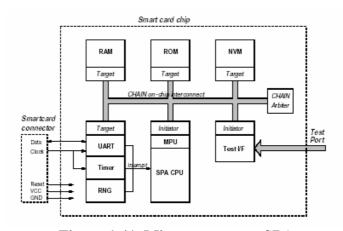

| Figure 1.41 Microprocesseur SPA                                                           |        |

| Figure 1.42 Layout du processeur MSL16A                                                   | - 44 - |

| Figure 2.1 Estimation de la consommation d'énergie dans le flot de synthèse TAST          | - 48 - |

| Figure 2.2 Réseau de pétri de la forme générale                                           |        |

| Figure 2.3 Evaluation de l'égalité (gauche) et de l'inégalité (droite) avec une constante |        |

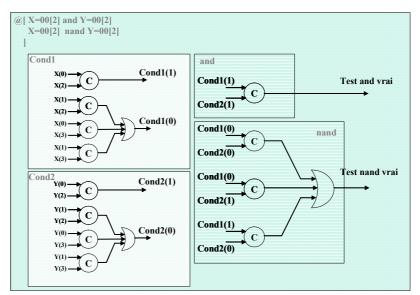

| Figure 2.4 Evaluation de l'égalité (gauche) et de l'inégalité (droite) avec une variable  |        |

| Figure 2.5 Exemple de test incluant les opérateurs and et nand                  |      |

|---------------------------------------------------------------------------------|------|

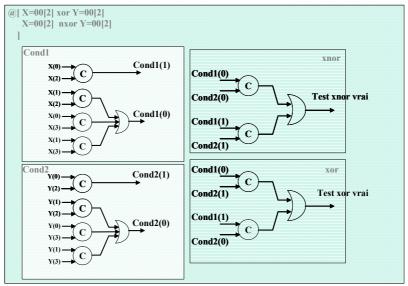

| Figure 2.6 Exemple de test incluant les opérateurs or et nor                    |      |

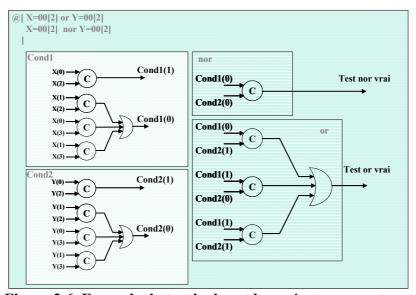

| Figure 2.7 Exemple de test incluant les opérateurs xor et xnor                  | 58 - |

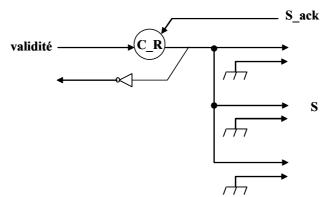

| Figure 2.8 Contrôle d'activation                                                | 59 - |

| Figure 2.9 Initialisation d'une sortie double rail                              | 62 - |

| Figure 2.10 Circuit d'émission d'une constante sur un canal                     | 64 - |

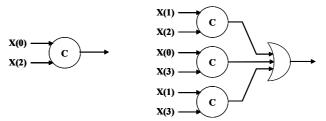

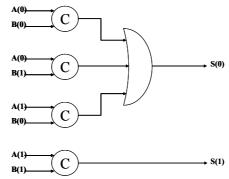

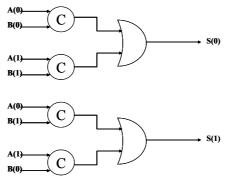

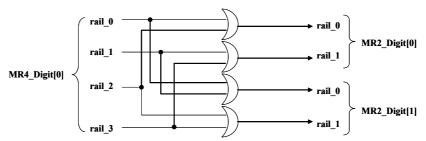

| Figure 2.11 Synthèse MR[2] de la porte AND                                      |      |

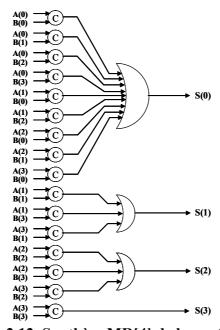

| Figure 2.12 Synthèse MR[4] de la porte AND                                      |      |

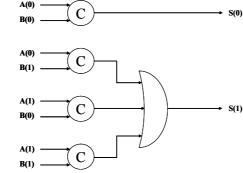

| Figure 2.13 Synthèse MR[2] de la porte OR                                       |      |

| Figure 2.14 Synthèse MR[2] de la porte XOR                                      |      |

| Figure 2.15 Synthèse MR[4] de la porte XOR                                      |      |

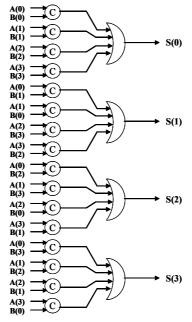

| Figure 2.16 Full Adder (FA) MR2                                                 |      |

| Figure 2.17 Full Adder (FA) MR4                                                 |      |

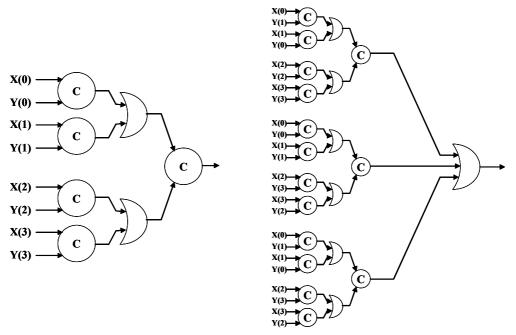

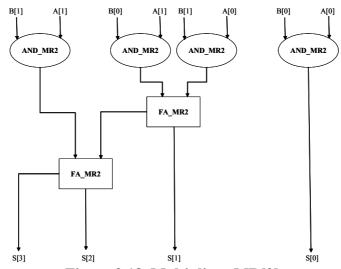

| Figure 2.18 Multiplieur MR[2]                                                   |      |

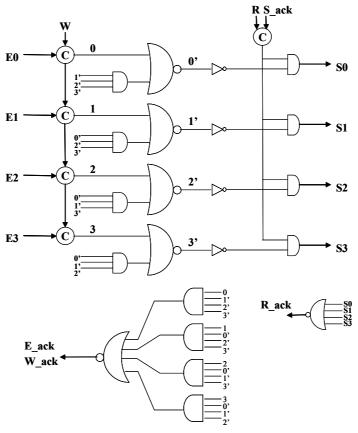

| Figure 2.19 Acquittement de la commande                                         |      |

| Figure 2.20 Fourche des données en entrée                                       |      |

| Figure 2.21 Acquittement des données entrantes                                  |      |

| Figure 2.22 Réunion des sorties                                                 |      |

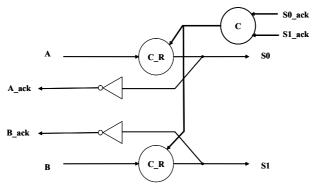

| Figure 2.23 Bufferisation en sortie d'une structure de choix à plusieurs gardes |      |

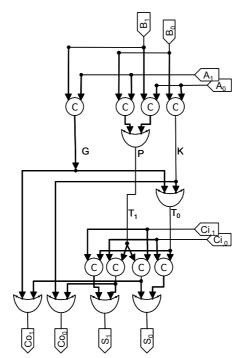

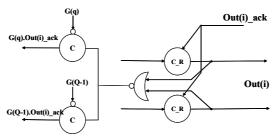

| Figure 2.24 Décomposition d'une porte OR à n entrées                            |      |

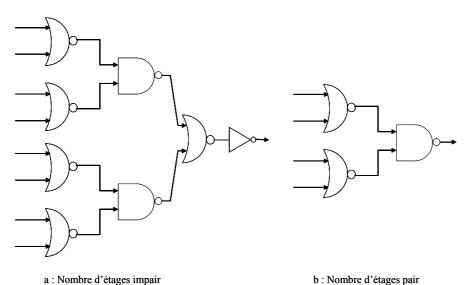

| Figure 2.25 Décomposition d'une porte AND à n entrées.                          |      |

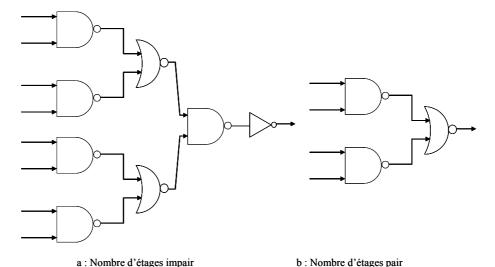

| Figure 2.26 Décomposition d'une porte de muller à 8 entrées                     |      |

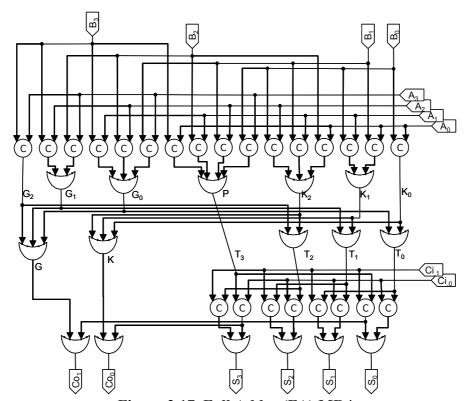

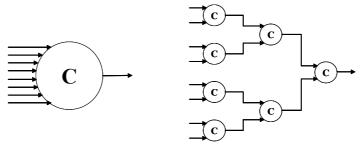

| Figure 2.27 Fourche non bufferisée (gauche) et bufferisée (droite)              |      |

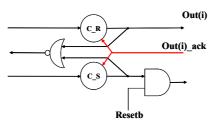

| Figure 2.28 Synthèse du Latch                                                   |      |

|                                                                                 |      |

| Figure 2.29 Fork bufferisé en entrée                                            |      |

| Figure 2.30 Fork bufférisé en sortie                                            |      |

| Figure 2.31 Synthèse du Join bufferisé en entrée.                               |      |

| Figure 2.32 Synthèse du Join bufferisé en sortie                                |      |

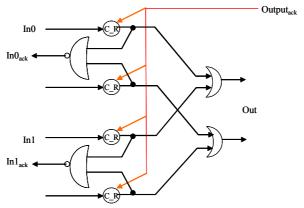

| Figure 2.33 Merge bufferisé en entrée                                           |      |

| Figure 2.34 Merge bufferisé en sortie                                           | 83 - |

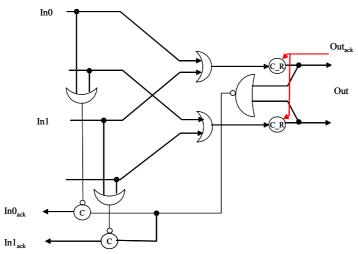

| Figure 2.35 Multiplexeur bufferisé en entrée                                    |      |

| Figure 2.36 Multiplexeur bufferisé en sortie finale                             |      |

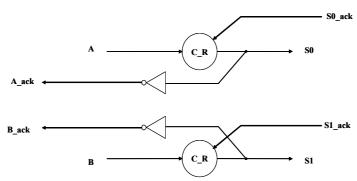

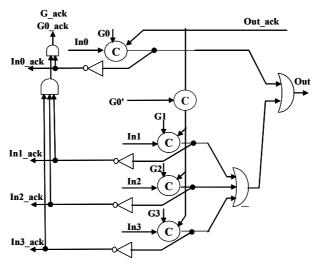

| Figure 2.37 Demultiplexeur bufferisé en entrée                                  |      |

| Figure 2.38 Démultiplexeur bufferisé en sortie                                  |      |

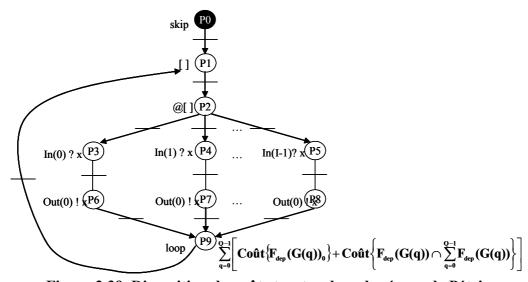

| Figure 2.39 Disposition du coût structurel sur le réseau de Pétri               |      |

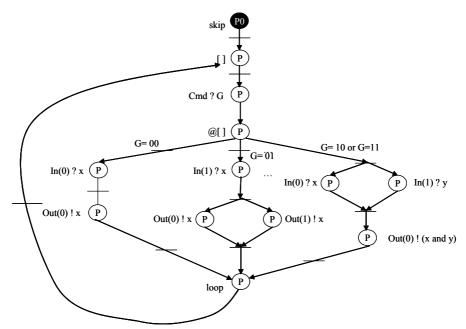

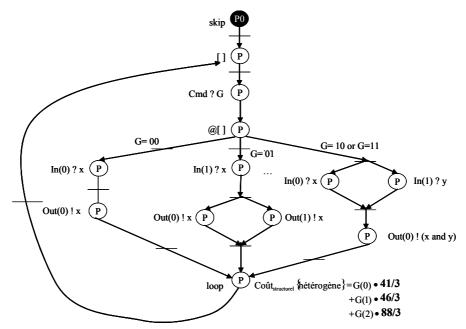

| Figure 2.40 Réseau de Pétri du composant hétérogène.                            |      |

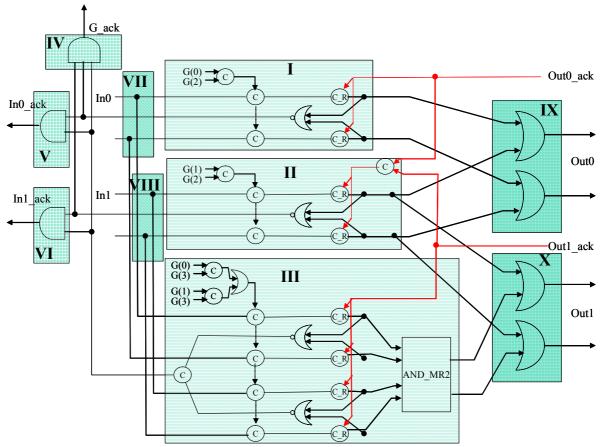

| Figure 2.41 Synthèse du composant hétérogène                                    |      |

| Figure 2.42 Labellisation du réseau de pétri avec le coût structurel            | 94 - |

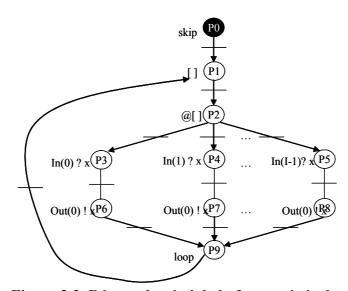

| Figure 3.1 Flot TAST                                                            |      |

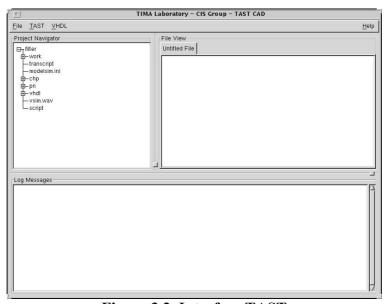

| Figure 3.2 Interface TAST                                                       |      |

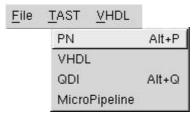

| Figure 3.3 Compilateur CHP                                                      | 97 - |

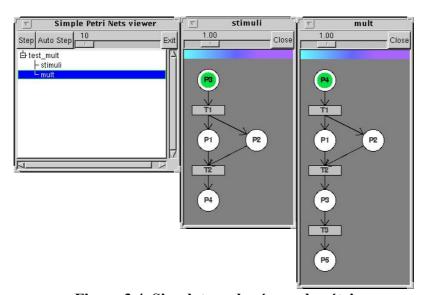

| Figure 3.4 Simulateur de réseau de pétri                                        | 97 - |

| Figure 3.5 Convertisseur Chp2vhdl                                               | 98 - |

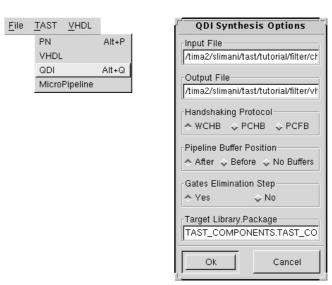

| Figure 3.6 Synthèse QDI                                                         | 98 - |

| Figure 3.7 Synthèse Micropipeline                                               | 99 - |

| Figure 3.8 Trace des canaux ("Trace –channels")                                 |      |

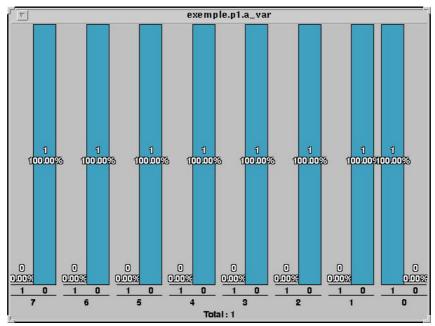

| Figure 3.9 Trace variables                                                      |      |

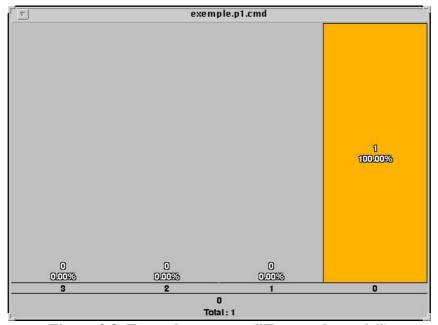

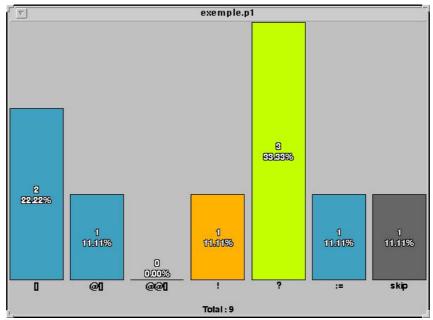

| Figure 3.10 Statistiques sur les instructions                                   |      |

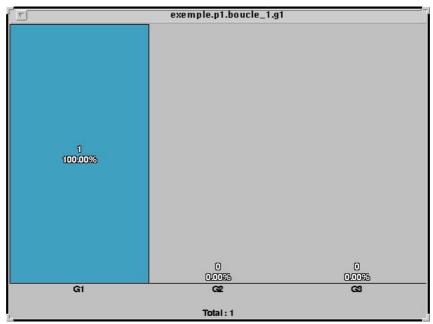

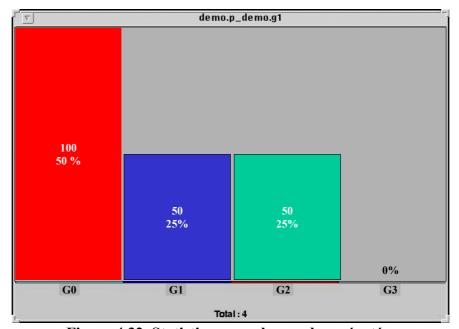

| Figure 3.11 Statistiques sur les structures de choix                            |      |

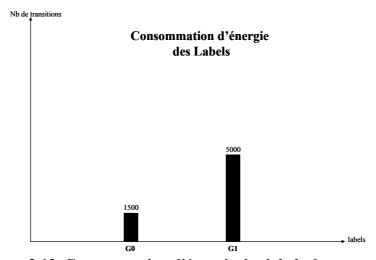

| Figure 3.12 Consommation d'énergie des labels du process. 1                     |      |

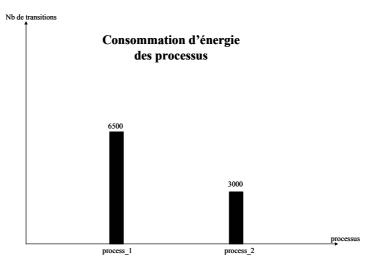

| Figure 3.13 Consommation d'énergie des processus du composant_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 113 -   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Figure 3.14 Consommation des composants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |

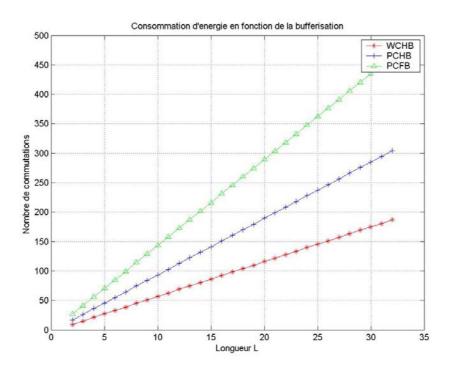

| Figure 4.1 Comparaison de bufferisation WCHB, PCHB, PCFB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 116 -   |

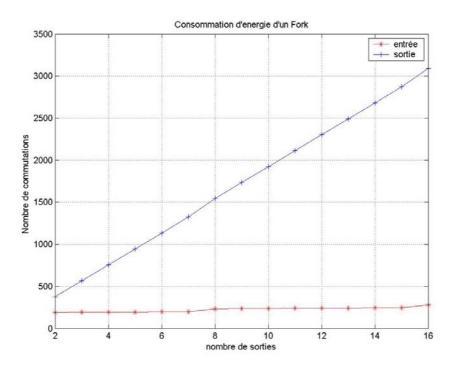

| Figure 4.2 Consommation d'un Fork bufferisé en entrée et en sortie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 118 -   |

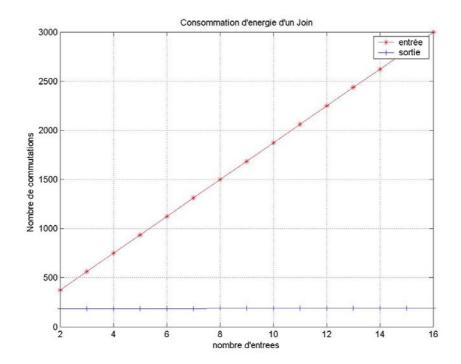

| Figure 4.3 Consommation d'un Join bufferisé en entrée et en sortie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 119 -   |

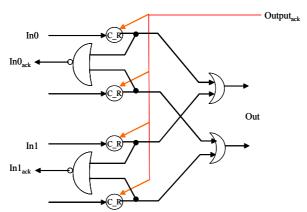

| Figure 4.4 Merge bufferisé en entrée                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 120 -   |

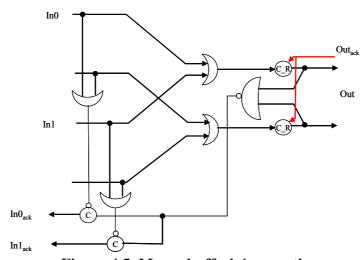

| Figure 4.5 Merge bufferisé en sortie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 120 -   |

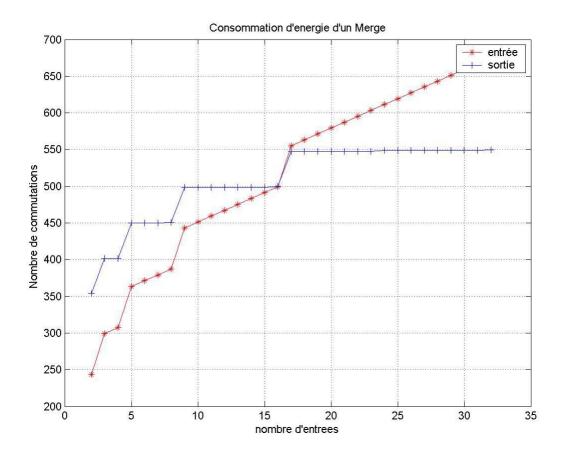

| Figure 4.6 Consommation d'un Merge bufferisé en entrée et en sortie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 121 -   |

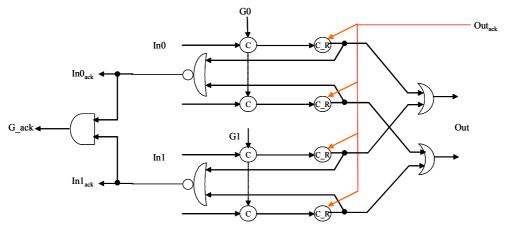

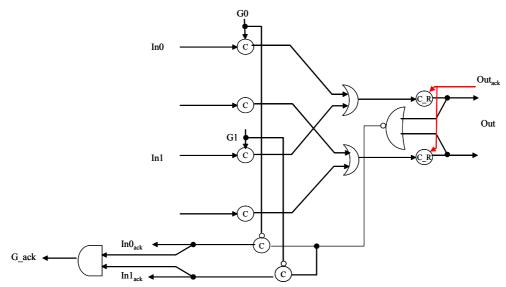

| Figure 4.7 Multiplexeur bufferisé en entrée                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

| Figure 4.8 Multiplexeur bufferisé en sortie finale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |

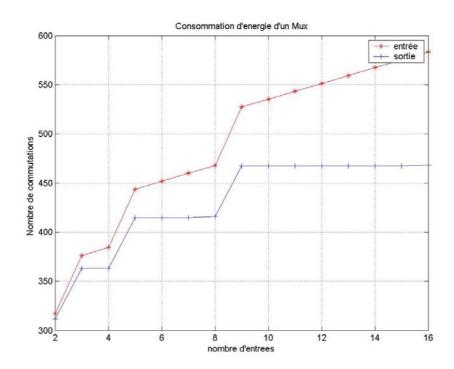

| Figure 4.9 Consommation d'un Multiplexeur bufferisé en entrée et en sortie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |

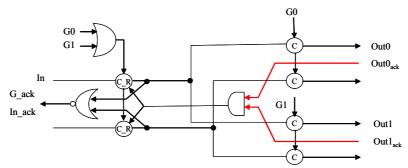

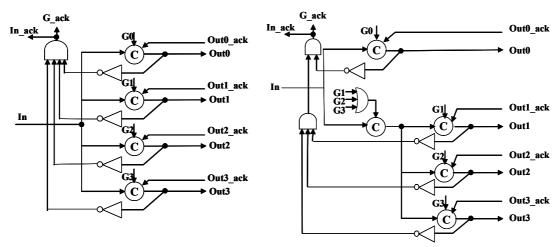

| Figure 4.10 Demultiplexeur bufferisé en entrée                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| Figure 4.11 Demultiplexeur bufferisé en sortie finale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

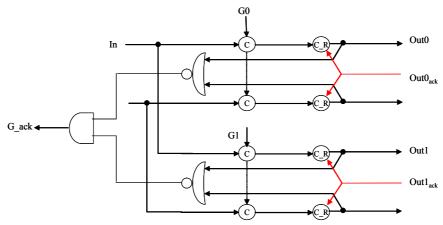

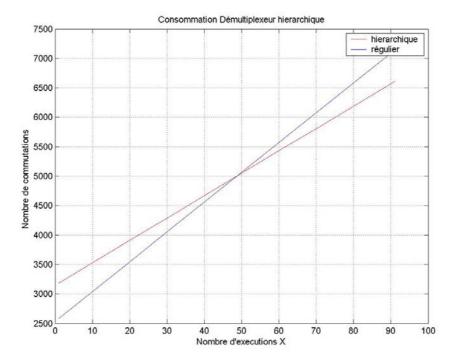

| Figure 4.12 Consommation d'un démultiplexeur bufferisé en entrée et en sortie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

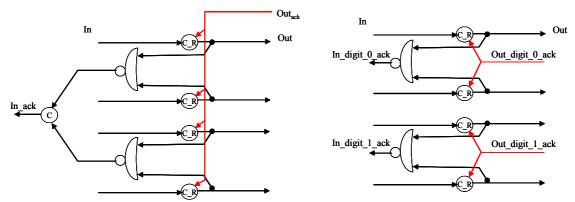

| Figure 4.13 Bufferisation normale (gauche) et désynchronisation intra canal (droite)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

| Figure 4.14 Consommation d'énergie d'un Latch acquitté digit à digit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

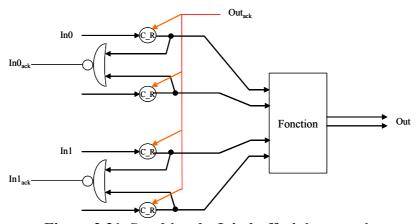

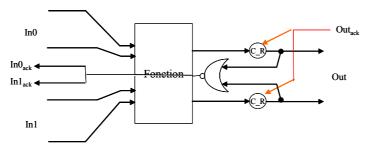

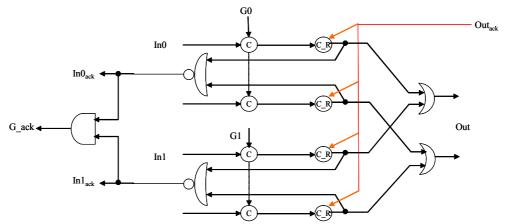

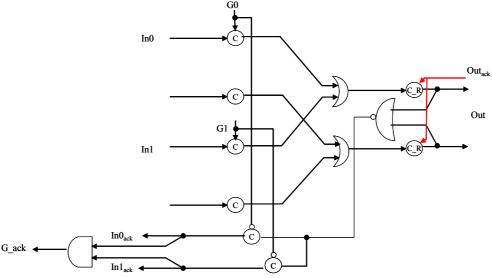

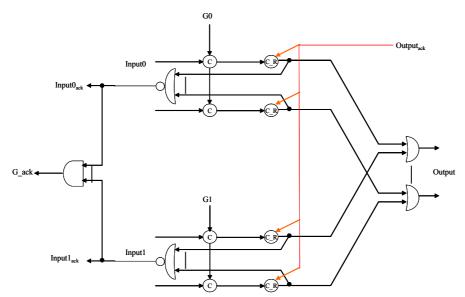

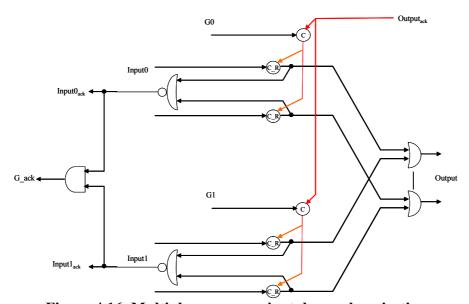

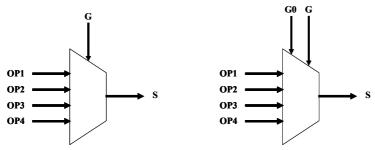

| Figure 4.15 Multiplexeur non optimisé                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

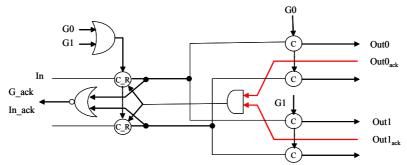

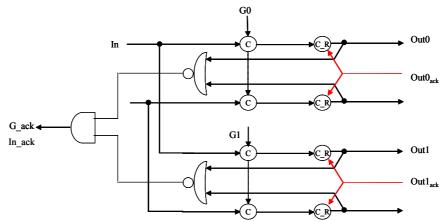

| Figure 4.16 Multiplexeur avec ajout de synchronisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

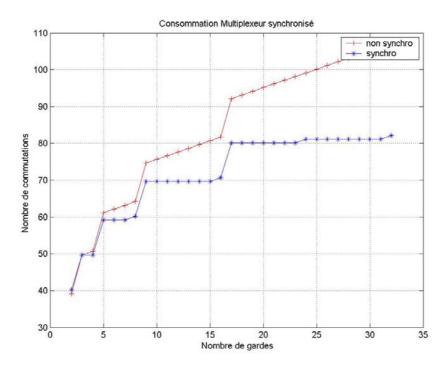

| Figure 4.17 Consommation du multiplexeur synchronisé                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

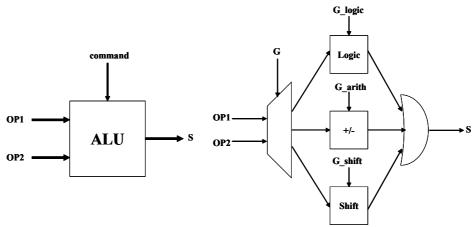

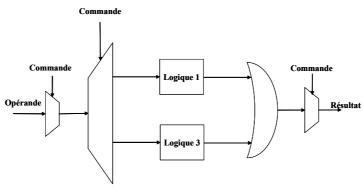

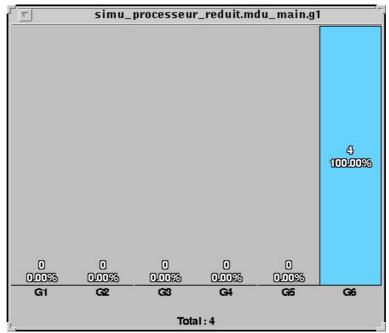

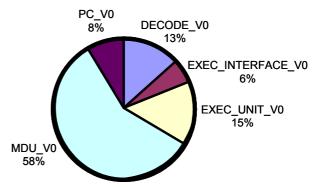

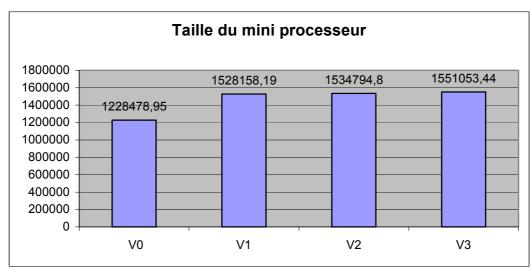

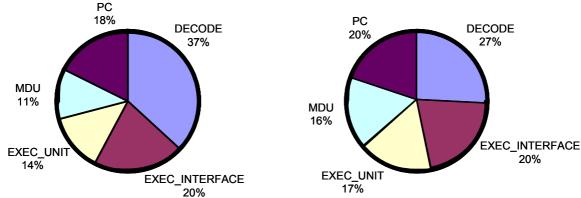

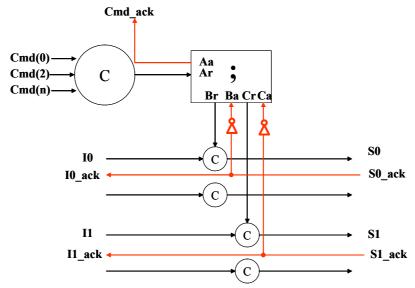

| Figure 4.18 Décomposition d'une ALU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |