## Contribution à la conception de systèmes temps-réel s'appuyant sur la technique de description formelle RT-Lotos

Christophe Lohr

#### ▶ To cite this version:

Christophe Lohr. Contribution à la conception de systèmes temps-réel s'appuyant sur la technique de description formelle RT-Lotos. Réseaux et télécommunications [cs.NI]. Institut National Polytechnique de Toulouse - INPT, 2002. Français. NNT: . tel-00005228

#### HAL Id: tel-00005228 https://theses.hal.science/tel-00005228

Submitted on 6 Mar 2004

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Préparée au

Laboratoire d'Analyse et d'Architecture des Systèmes du CNRS

En vue de l'obtention du

Doctorat de l'Institut National Polytechnique de Toulouse

Spécialité :

Programmation et Systèmes

par

## Christophe Lohr

# Contribution à la conception de systèmes temps-réel s'appuyant sur la technique de description formelle RT-Lotos

Soutenue le jeudi 19 décembre 2002, devant le jury :

| Président          | Patrick                      | SALLÉ                       |

|--------------------|------------------------------|-----------------------------|

| Directeur de thèse | Jean-Pierre                  | Courtiat                    |

| Rapporteurs        | Richard<br>Elie              | Castanet<br>Najm            |

| Examinateurs       | Michel<br>Hubert<br>François | DIAZ<br>GARAVEL<br>VERNADAT |

### Remerciements

Mes travaux de recherche ont été menés au Laboratoire d'Analyse et d'Architecture des Systèmes (LAAS) du Centre National de la Recherche Scientifique (CNRS) au sein du groupe Outils et Logiciels pour la Communication (OLC).

Je remercie donc Jean-Claude Laprie directeur du LAAS-CNRS pendant ces années de m'avoir accueillí au sein du laboratoire ainsi que Michel Diax responsable du groupe OLC pour m'avoir accepté dans son groupe.

J'aimerais remercier Richard Castanet, Elie Najm, Michel Diax, Hubert Garavel, Patrick Salle, et François Vernadat de m'avoir fait l'honneur de participer à mon jury.

Un grand merci à Aurore Collomb , Hubert Garavel , et Pierre de Sagui-Sannes pour la relecture attentive de mon manuscrit , et à François Vernadat qui m'a aussi aidé à préparer ma soutenance.

Je tiens à remercier tout particulièrement mon directeur de recherche Jean-Pierre Courtiat, pour son dévouement et son aide constante au cours de toutes ces années, grâce auxquels il m'a été possible de mener cette thèse à bien. Je n'oublierai jamais ses maximes pleines de sagesse, et notamment les plus célèbres: « Si c'était facile, ce ne serait pas une thèse!» et « Le temps passe vite!».

Je suis très reconnaissant envers tous ceux qui ont contribué à mes travaux de recherche: tout d'abord Roberto Crux de Oliviera, génial auteur de l'outil xt1 et des nombreux aspects théoriques qui l'entourent; et je regrette qu'il n'ait pu mener à terme ses projets de recherche. Je remercie Celso Saibel Santos, collèque chaleureux dont les discussions sur son algorithme d'agrégation ont fait germer dans ma tête ce qu'est devenu le TLSA. Je remercie Paulo Sampaio qui a eu le courage de bien vouloir exploiter et mettre à l'épreuve mon TLSA pour ses propres travaux. Je remercie Benaceur Outtaj pour son aide concernant le calcul des invariants Kronos. Je tiens à remercier Pierre de Sagui-Sannes et Ludovic Apvrille sans qui TURTLE ne serait pas.

Merci aussi à tous mes compagnons de route depuis mes débuts dans la recherche: Laurent Andriantsiferana, Rachid Benabbou, Emmanuel Castel, Hugues Buisson, Guillermo Hoyos, Roberta Gomes, et tous les autres.

Je veux exprimer également toute ma reconnaissance au personnel du LAAS. ingénieurs, techniciens et administratifs, pour leur concours et leur efficacité essentiels à la conclusion de ce travail.

Je voudrais remercier aussi mes parents, ma famille, pour leur présence et leur soutien malgré les kilomètres.

Je tiens à remercier spécialement tous mes amis (je ne me risquerai pas à faire la liste, c'est trop long et je m'en voudrai d'oublier guelgu'un), pour les nombreuses fêtes, discussions de comptoir, plongées sous-marines, et autres moments de détente indispensables à une thèse épanouissante et réussie.

Enfin . mes pensées vont vers toi . Sidonie . qui partage ma vie depuis quelques années maintenant . pour toute ton affection . ta tendresse . mais aussi ta compréhension et ton soutien de tous les instants. Je t'embrasse.

## Table des matières

| In | trod | uction              |                                                                            | 1  |

|----|------|---------------------|----------------------------------------------------------------------------|----|

| 1  | For  | malisa <sup>.</sup> | tion des systèmes temps-réel et RT-Lotos                                   | 7  |

|    | 1.1  | Différe             | ents formalismes pour exprimer des contraintes temporelles                 | 7  |

|    |      | 1.1.1               | Extensions temporisées des réseaux de Petri                                | 8  |

|    |      | 1.1.2               | Automates temporisés                                                       | 6  |

|    |      | 1.1.3               | Algèbres de processus                                                      | 11 |

|    |      | 1.1.4               | Principales extensions temporelles à Lotos                                 | 12 |

|    | 1.2  | Le lan              | gage RT-Lotos                                                              | 19 |

|    |      | 1.2.1               | Lotos                                                                      | 19 |

|    |      | 1.2.2               | L'extension RT-Lotos                                                       | 26 |

|    |      | 1.2.3               | Traitement du non-déterminisme temporel                                    | 38 |

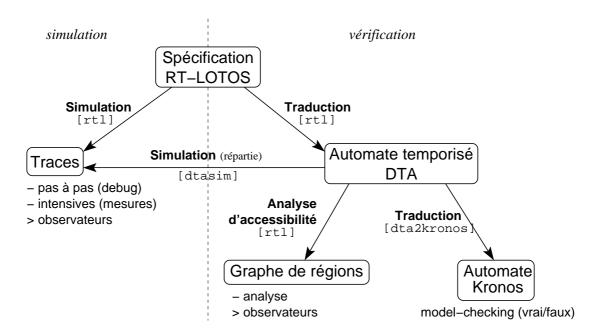

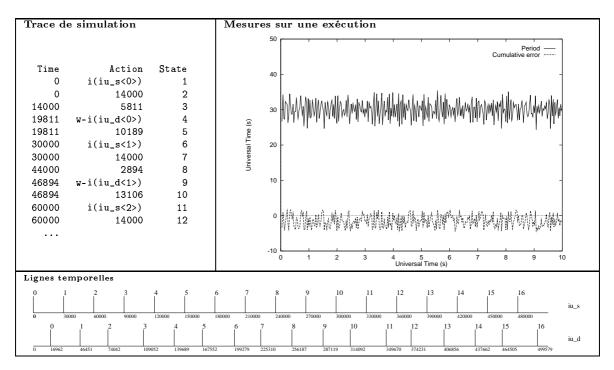

|    | 1.3  | Valida              | tion avec RT-Lotos                                                         | 40 |

|    |      | 1.3.1               | Simulation                                                                 | 40 |

|    |      | 1.3.2               | Vérification formelle                                                      | 44 |

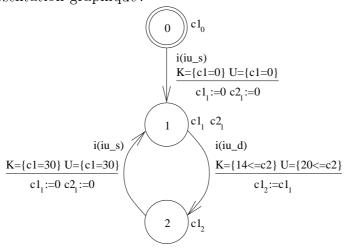

|    |      | 1.3.3               | Analyse d'accessibilité                                                    | 49 |

|    |      | 1.3.4               | Model-checking                                                             | 55 |

|    | 1.4  | Expér               | iences avec RT-Lotos                                                       | 61 |

|    | 1.5  | Concl               | usion                                                                      | 62 |

| 2  | Ord  | lonnan              | cement temporel de systèmes cohérents                                      | 65 |

|    | 2.1  | Synthe              | èse d'automates d'ordonnancement                                           | 65 |

|    |      | 2.1.1               | Motivation pour un automate d'ordonnancement                               | 66 |

|    |      | 2.1.2               | Adéquation des automates temporels existants                               | 67 |

|    |      | 2.1.3               | Problématique de la synthèse d'automates                                   | 68 |

|    | 2.2  | Une p               | roposition d'automate d'ordonnancement : le TLSA                           | 69 |

|    |      | 2.2.1               | Définition formelle d'un TLSA                                              | 70 |

|    |      | 2.2.2               | Propriétés du formalisme TLSA                                              | 72 |

|    | 2.3  | Un alg              | gorithme pour synthétiser un TLSA                                          | 76 |

|    |      | 2.3.1               | Initialisation de l'algorithme                                             | 79 |

|    |      | 2.3.2               | Identification de la configuration accessible au plus tôt de chaque classe | 79 |

|    |      | 2.3.3               | Sélection et regroupement des transitions Lotos                            | 89 |

|    |      | 2.3.4               | Découpage des états                                                        | 95 |

|    |      | 2.3.5               | Pré-traitement du graphe minimal d'accessibilité                           | 97 |

|    | 2.4  | Élimir              | nation des comportements non cohérents                                     | 97 |

|    |      | 2.4.1               | Démarche du filtrage des comportements non cohérents                       | 97 |

|    |      | 2 1 2               | Suppression des configurations indésirables                                | 07 |

|                  |       | 2.4.3    | Insertion de transitions particulières _t                                                                   | 98  |

|------------------|-------|----------|-------------------------------------------------------------------------------------------------------------|-----|

|                  | 2.5   | Utilisa  | ation du TLSA                                                                                               | 99  |

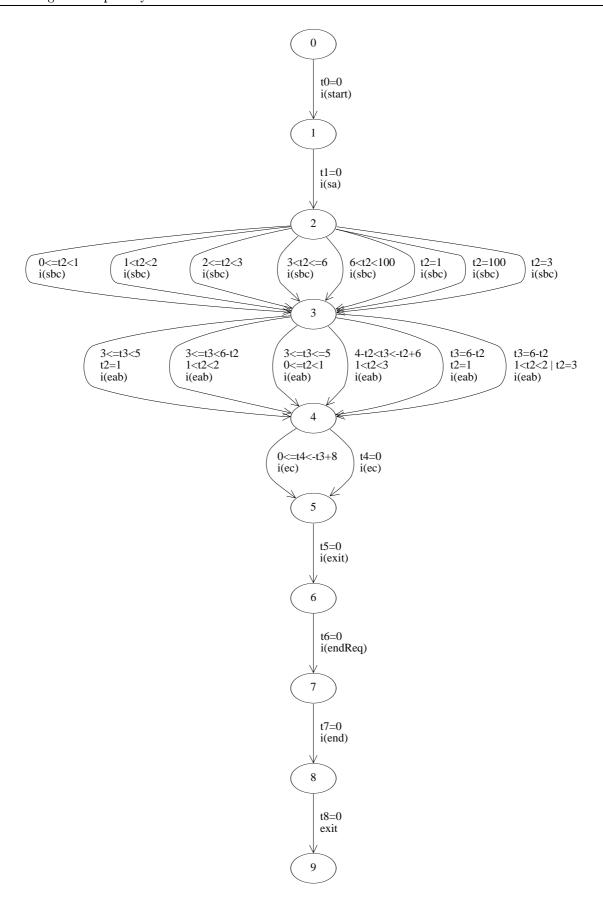

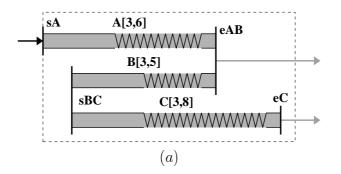

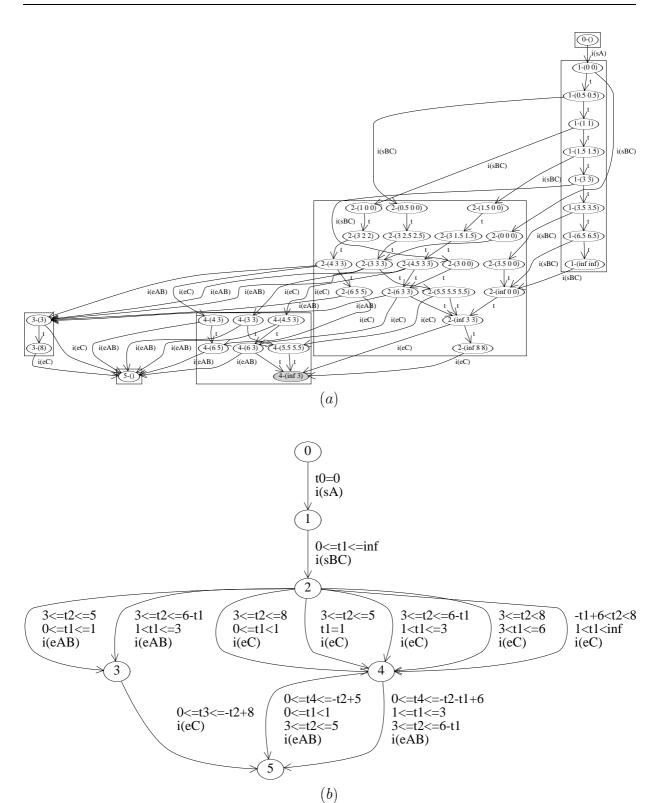

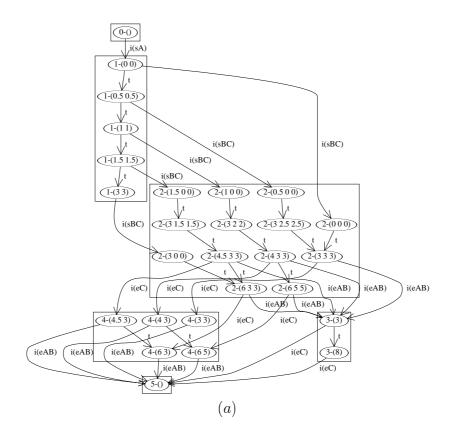

|                  |       | 2.5.1    | Présentation d'un cas d'étude                                                                               | 99  |

|                  |       | 2.5.2    | Mise en oeuvre de la méthodologie                                                                           | 100 |

|                  |       | 2.5.3    | Bilan de la méthodologie                                                                                    | 102 |

|                  | 2.6   | Conclu   | ısion                                                                                                       | 104 |

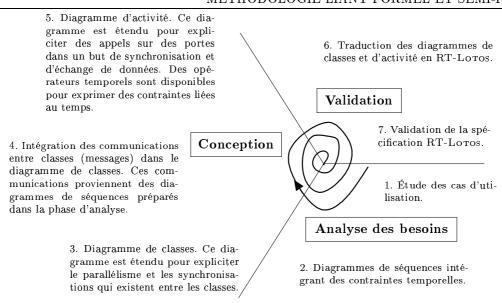

| 3                | Méi   | thodol   | ogie liant formel et semi-formel                                                                            | 105 |

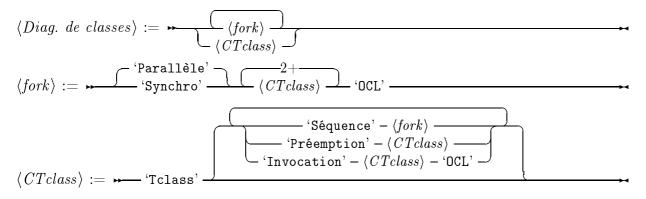

| _                | 3.1   |          | ofil temps-réel formel pour UML                                                                             |     |

|                  |       | 3.1.1    | Les projets UML temps-réel                                                                                  |     |

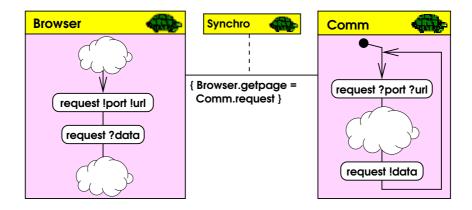

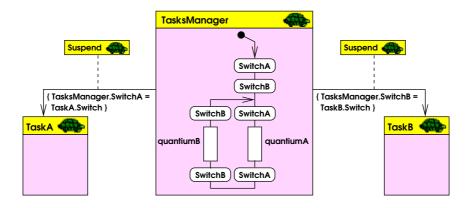

|                  |       | 3.1.2    | L'approche TURTLE                                                                                           |     |

|                  |       | 3.1.3    | Mise en œuvre de TURTLE                                                                                     | 114 |

|                  |       | 3.1.4    | Étude de cas                                                                                                | 118 |

|                  |       | 3.1.5    | Les limites de la méthodologie                                                                              | 121 |

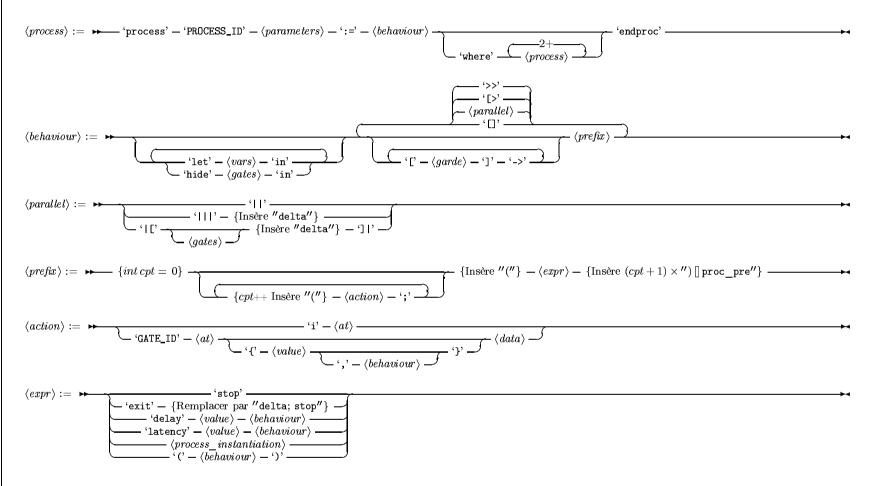

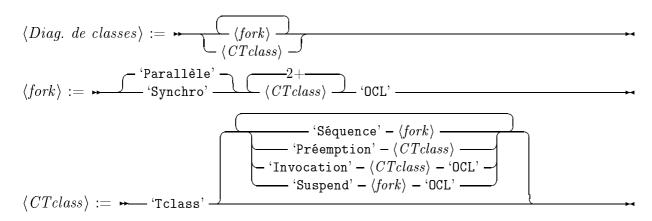

|                  | 3.2   | Algori   | thmes pour traduire les diagrammes de classes TURTLE                                                        | 124 |

|                  |       | 3.2.1    | Définitions préliminaires                                                                                   | 124 |

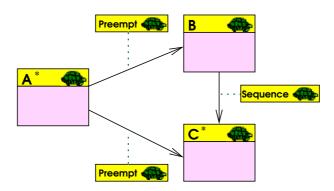

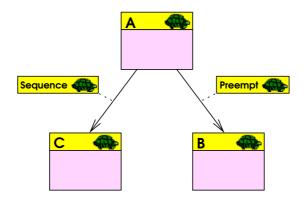

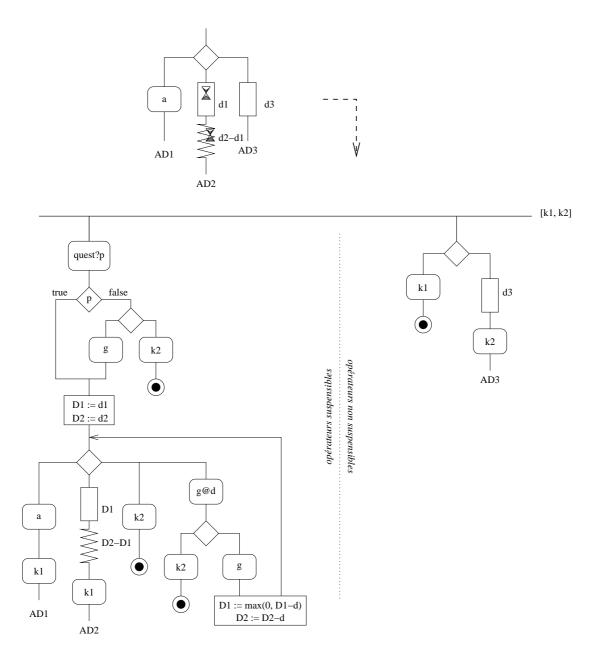

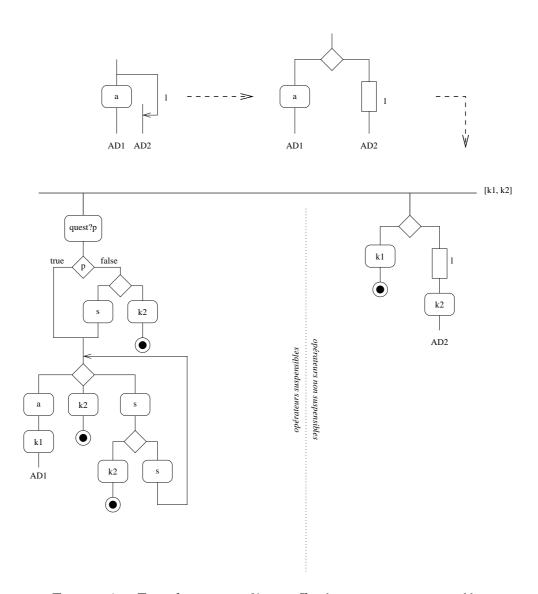

|                  |       | 3.2.2    | Traduction des $Tclasses$ à l'origine de relations de $Preemption$                                          | 126 |

|                  |       | 3.2.3    | Traduction des <i>Tclasses</i> à l'origine de relations de <i>Sequence</i>                                  | 126 |

|                  |       | 3.2.4    | Traduction des <i>Tclasses</i> qui ne sont à pas l'origine de relations de                                  | 100 |

|                  |       | 205      | Preemption ou de Sequence                                                                                   | 129 |

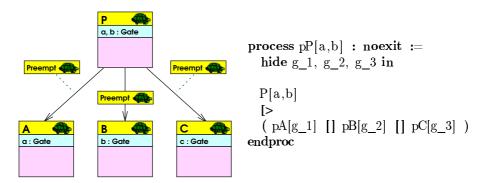

|                  |       | 3.2.5    | Réduction des <i>Tclasses</i> à l'origine à la fois de relations de <i>Sequence</i> et de <i>Preemption</i> | 129 |

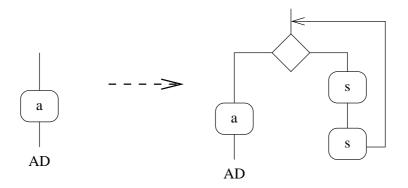

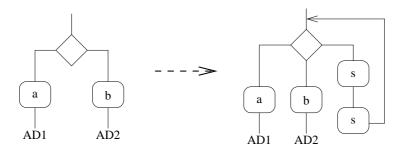

|                  |       | 3.2.6    | Traduction des ensembles de <i>Tclass</i> en relation de <i>Parallel</i> et <i>Synch</i> :                  |     |

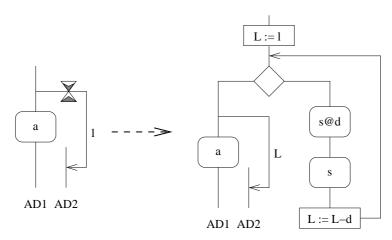

|                  |       | 3.2.7    | Traduction des <i>Tclasses</i> actives                                                                      |     |

|                  | 3.3   | Extens   | sions par domaine d'application                                                                             | 140 |

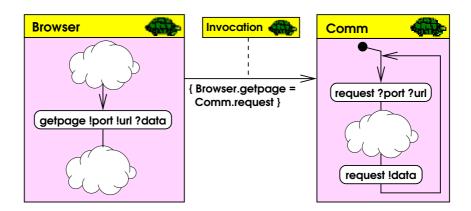

|                  |       | 3.3.1    | Invocation de classes                                                                                       | 140 |

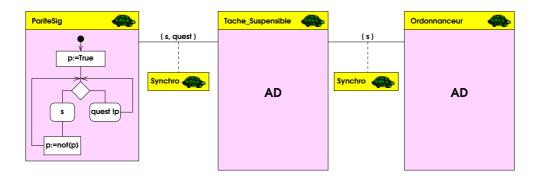

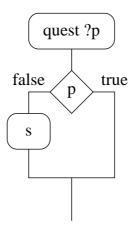

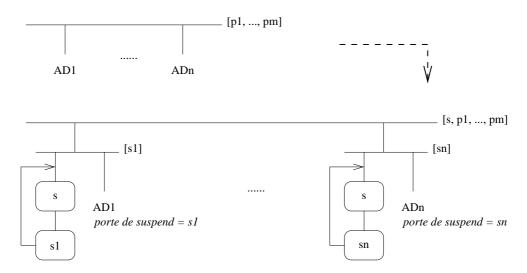

|                  |       | 3.3.2    | Suspension/reprise d'activité                                                                               | 142 |

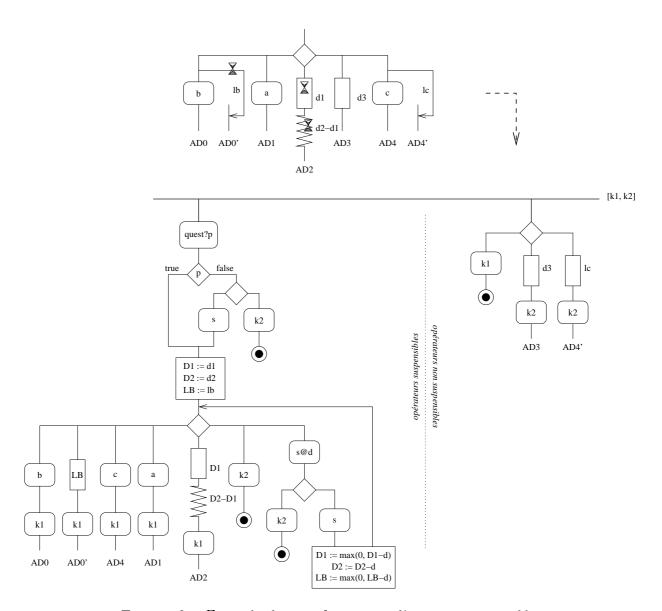

|                  |       | 3.3.3    | Traduction du profil temps-réel système en TURTLE                                                           | 144 |

|                  | 3.4   | Conclu   | asion                                                                                                       | 151 |

| C                | onclu | sion     |                                                                                                             | 155 |

| Pι               | ıblic | ations   | de l'auteur                                                                                                 | 161 |

| $\mathbf{R}_{0}$ | éfére | nces     |                                                                                                             | 163 |

|                  |       |          |                                                                                                             |     |

| A                | nnex  | e        |                                                                                                             | 175 |

| A                | Jus   | tificati | on de la traduction des domaines d'urgence en invariants                                                    | 177 |

| В                | Pré   |          | ment du graphe minimal d'accessibilité                                                                      | 181 |

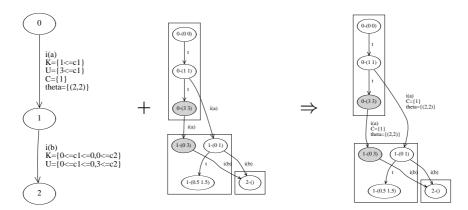

|                  | B.1   |          | ter les fonctions $C$ et $theta$                                                                            | 181 |

|                  | B.2   |          | ter les régions-point                                                                                       |     |

|                  | В3    | Projec   | tion et minimisation                                                                                        | 182 |

LISTE DES FIGURES

|              | B.3.3 Traitement des informations temporelles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 184<br>184<br>184<br>185                                                                                                                                       |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\mathbf{C}$ | Spécification RT-Lotos engendrée depuis TURTLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 187                                                                                                                                                            |

|              | Liste des figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ?5                                                                                                                                                             |

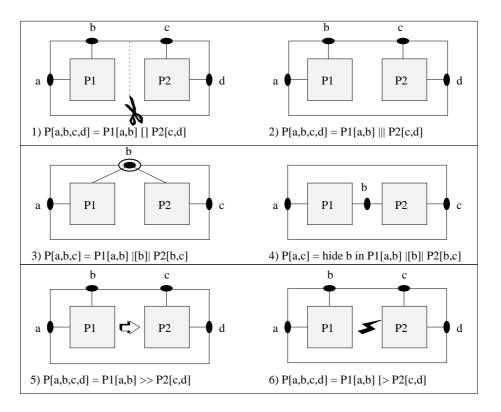

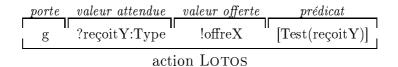

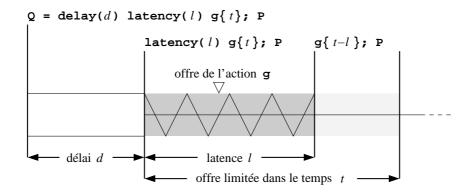

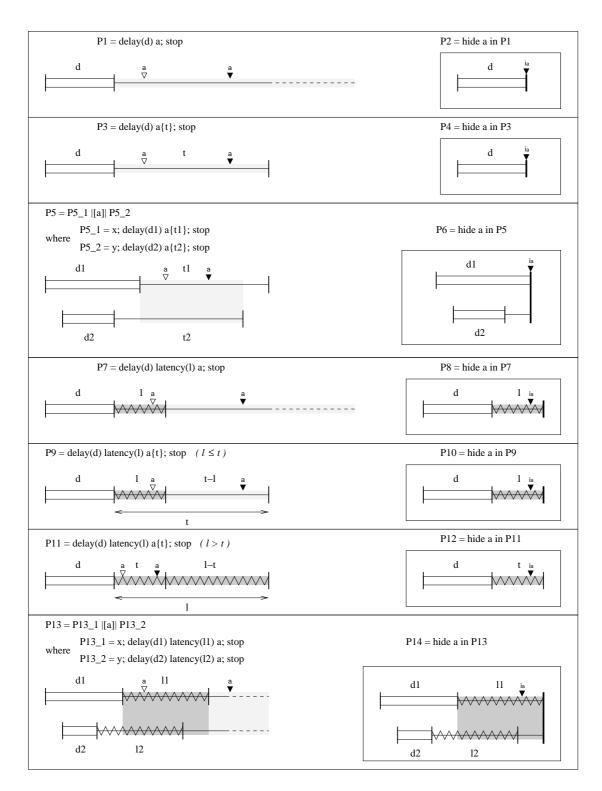

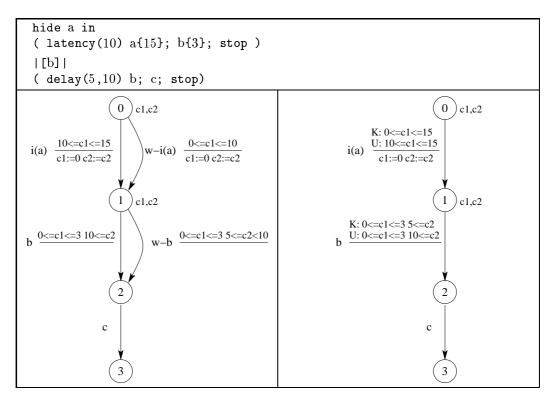

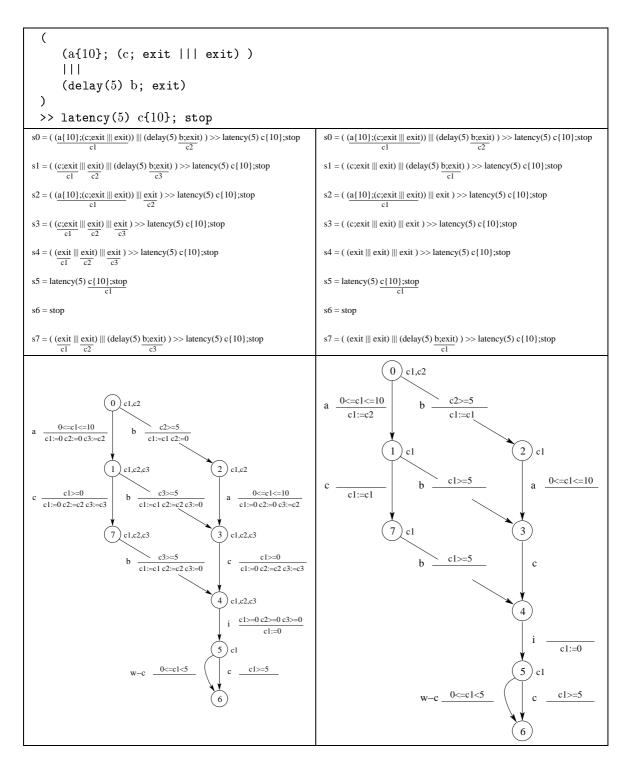

|              | 1.1 Comparaison des extensions temporelles à Lotos 1.2 Principaux opérateurs de Basic-Lotos 1.3 Illustration des opérateurs de Basic-Lotos 1.4 Syntaxe de Basic-Lotos 1.5 Sémantique opérationnelle de Basic-Lotos 1.6 Représentation d'une action en Lotos 1.7 Règles de synchronisation en Lotos avec données 1.8 Principaux opérateurs Lotos avec utilisation de données 1.9 Sémantique opérationnelle de (Full) Lotos 1.10 Exemple de contraintes temporelles spécifiées avec RT-Lotos 1.11 Illustration des opérateurs RT-Lotos 1.12 Syntaxe de Basic RT-Lotos 1.13 Le modèle Basic RT-Lotos 1.14 Exemple de déclaration d'un type naturel en RT-Lotos 1.15 Exemple d'utilisation de l'opérateur © 1.16 Syntaxe de (Full) RT-Lotos 1.17 Le modèle (Full) RT-Lotos 1.18 Comparaison entre latency(t) et i{t} 1.19 Validation avec RT-Lotos 1.20 Exemple : médium de communication 1.21 Simulation du médium de communication 1.22 Exemple de DTA 1.23 L'urgence dans le DTA avec actions weak ou avec domaine temporel U 1.24 Optimisation des horloges du DTA 1.25 Exemple de graphe minimal d'accessibilité 1.26 Spécification vérifiable uniquement à la volée | 14<br>20<br>21<br>22<br>23<br>24<br>25<br>25<br>26<br>27<br>29<br>32<br>33<br>35<br>36<br>37<br>38<br>39<br>41<br>42<br>43<br>45<br>50<br>51<br>51<br>53<br>54 |

|              | <ul> <li>1.27 Architecture générale de l'outil Kronos</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 56<br>59                                                                                                                                                       |

iv LISTE DES FIGURES

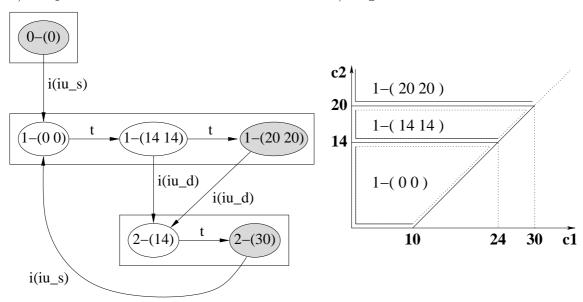

|      | Spécification RT-Lotos du croisement ferroviaire                               |

|------|--------------------------------------------------------------------------------|

| 2.1  | Illustration des règles de tir                                                 |

| 2.2  | Spécification RT-Lotos du problème de Dechter                                  |

| 2.3  | Exemples d'observateur                                                         |

| 2.4  | Mise en place d'un observateur                                                 |

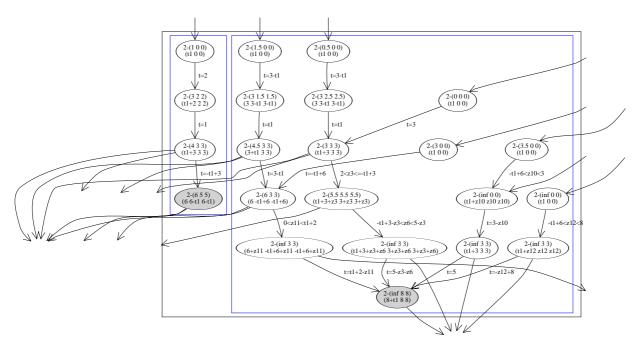

| 2.5  | TLSA partiel issu du problème de Dechter                                       |

| 2.6  | Vue d'ensemble de l'algorithme                                                 |

| 2.7  | Principe de l'algorithme de synthèse d'un TLSA                                 |

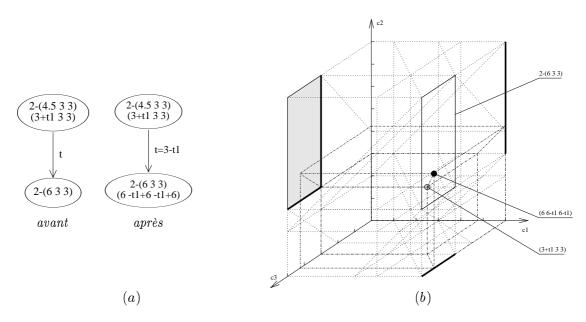

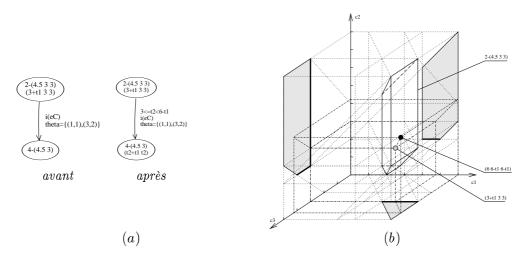

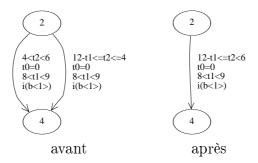

| 2.8  | Traitement d'une transition t                                                  |

| 2.9  | Transition t : valuation strictement supérieure à                              |

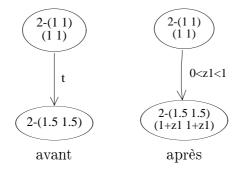

| 2.10 | Traitement d'une transition LOTOS                                              |

|      | Recopie d'un nœud                                                              |

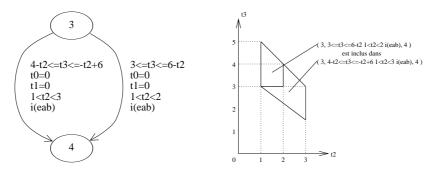

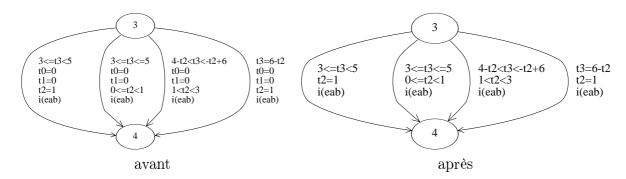

|      | Graphe des configurations accessibles au plus tôt : TLSA avant regroupement    |

|      | des transitions                                                                |

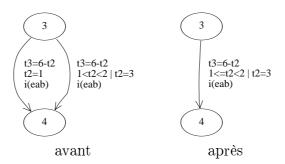

| 2.13 | Fenêtres de tir contiguës                                                      |

| 2.14 | Fenêtres de tir ayant la même expression                                       |

| 2.15 | Fenêtre de tir ayant des expressions différentes mais dont une seule a des     |

|      | variables                                                                      |

| 2.16 | Fenêtre de tir ayant des expressions différentes et dont chacune a des va-     |

|      | riables                                                                        |

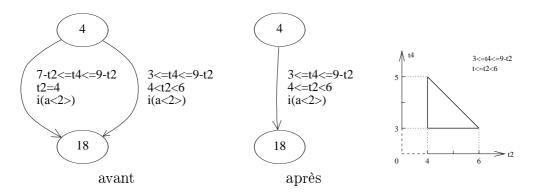

| 2.17 | Transitions incluses                                                           |

| 2.18 | Simplifier l'historique des tirs                                               |

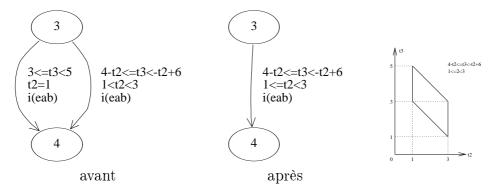

| 2.19 | Découpage des états de contrôle                                                |

|      | (a) Scénario multimédia (b) Spécification RT-Lotos                             |

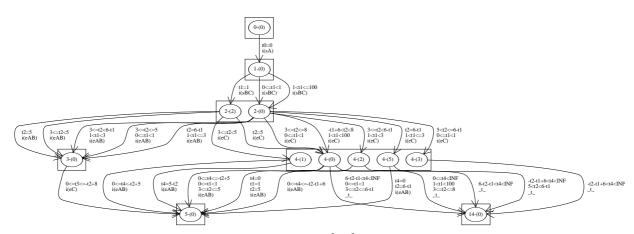

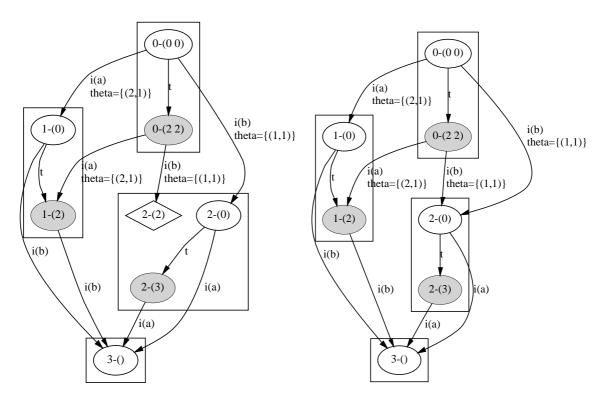

| 2.21 | (a) Graphe minimal d'accessibilité (b) TLSA associé                            |

| 2.22 | (a) Graphe minimal d'accessibilité consistant (b) TLSA associé                 |

| 0.1  | II (d. 1.1. trut ' d. 1.1.t. DELT                                              |

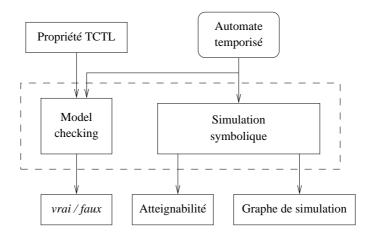

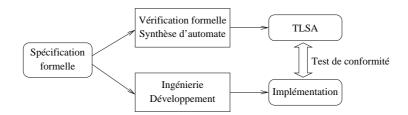

| 3.1  | Une méthodologie UML intégrant la validation RT-Lotos                          |

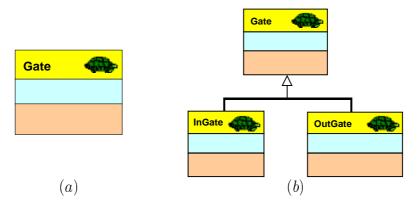

| 3.2  | Le type abstrait $Gate$                                                        |

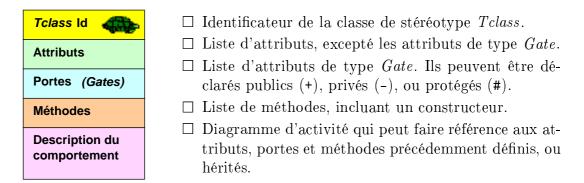

| 3.3  | Structure d'une classe stéréotypée $Tclass$                                    |

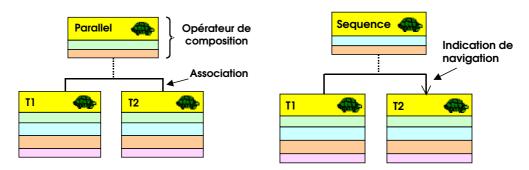

| 3.4  | Opérateurs de composition héritant de Composer                                 |

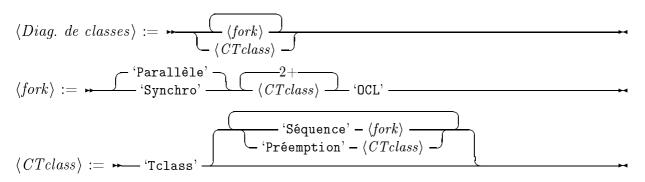

| 3.5  | Règles de composition des diagrammes de classes TURTLE                         |

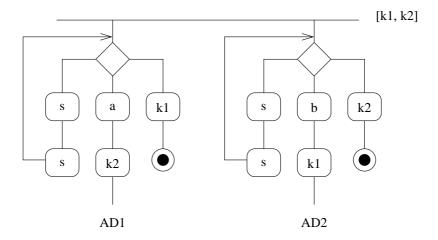

| 3.6  | Opérateurs non temporels des diagrammes d'activité TURTLE                      |

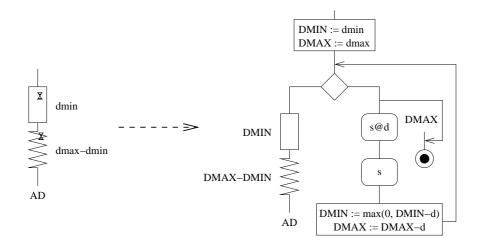

| 3.7  | Opérateurs temporels des diagrammes d'activité TURTLE                          |

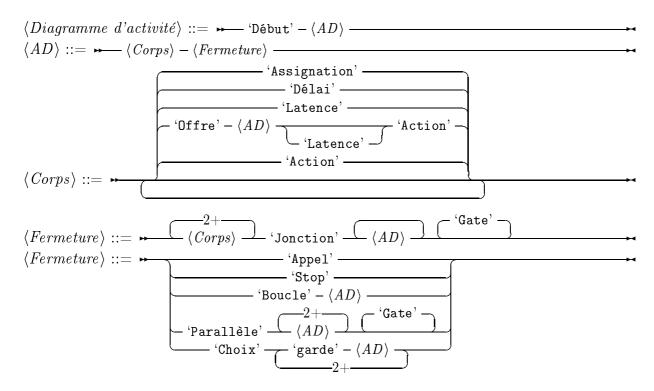

| 3.8  | Règles de composition des symboles d'activité TURTLE                           |

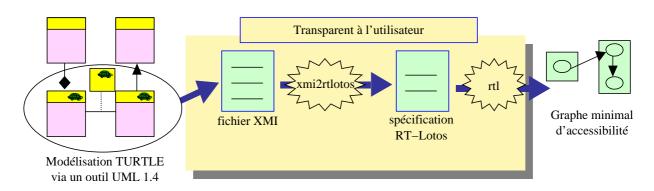

| 3.9  | De la modélisation TURTLE à la vérification                                    |

| 3.10 | Traduction RT-Lotos des activités TURTLE                                       |

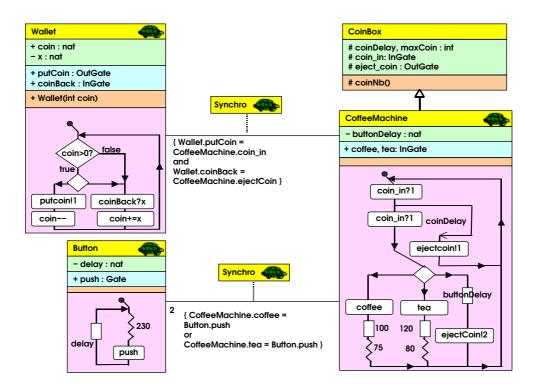

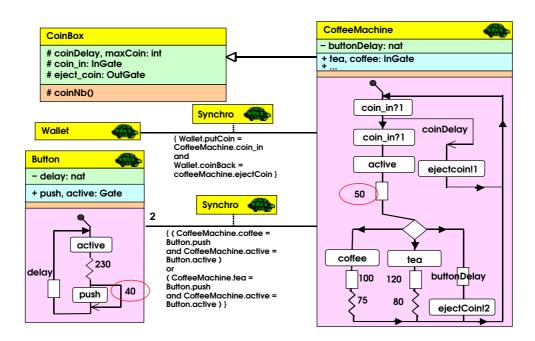

|      | Diagramme de classes n° 1 de la machine à café                                 |

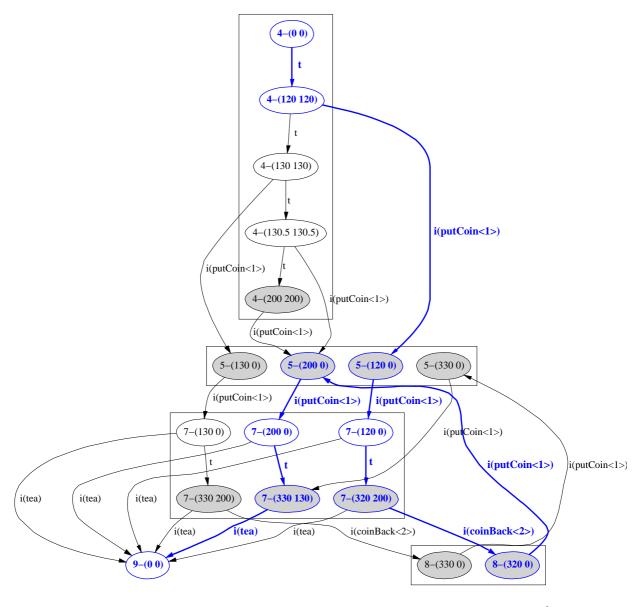

| 3.12 | Extrait du graphe minimal d'accessibilité de la machine à café n° $1 \ldots 1$ |

| 3.13 | Diagramme de classes n° 2 de la machine à café                                 |

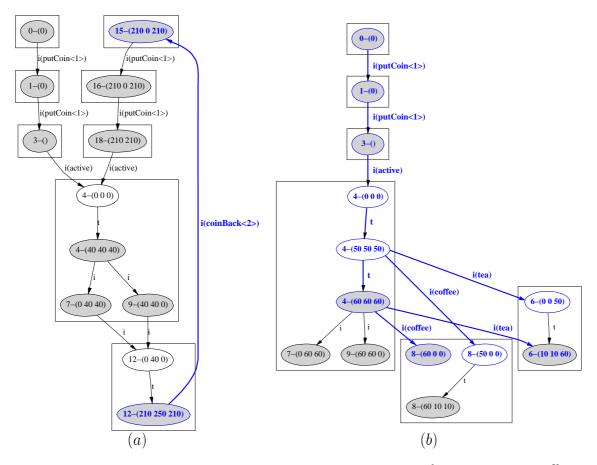

| 3.14              | Graphe minimal d'accessibilité de la machine à café n° 2 avec une offre sur les boutons limitée à $40$ (graphe $(a)$ ) puis à $60$ (graphe $(b)$ ) | 22              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 3.15              |                                                                                                                                                    | 25              |

|                   |                                                                                                                                                    | - °<br>26       |

|                   |                                                                                                                                                    | $\frac{28}{28}$ |

|                   | -                                                                                                                                                  | <b>-</b> 0      |

|                   | Fonction $String\ Rewrite(process:\ String,\ delta:\ String,\ proc\_pre:$                                                                          | 34              |

| 3 20              | 3)                                                                                                                                                 | 41              |

|                   | <u>-</u>                                                                                                                                           | 41              |

|                   | -                                                                                                                                                  | $41 \\ 42$      |

|                   |                                                                                                                                                    |                 |

|                   | 1                                                                                                                                                  | 42              |

|                   |                                                                                                                                                    | $\frac{43}{44}$ |

|                   | 1 1                                                                                                                                                | 44              |

|                   | 0                                                                                                                                                  | 45              |

|                   |                                                                                                                                                    | 45              |

|                   | 11 1                                                                                                                                               | 46              |

|                   | 1                                                                                                                                                  | 46              |

|                   |                                                                                                                                                    | 47              |

|                   | 1                                                                                                                                                  | 47              |

|                   |                                                                                                                                                    | 48              |

|                   | •                                                                                                                                                  | 49              |

|                   | <u>.</u>                                                                                                                                           | 50              |

|                   |                                                                                                                                                    | 51              |

| 3.36              | 1                                                                                                                                                  | 52              |

| 3.37              | Conformité entre implémentation et TLSA                                                                                                            | 58              |

| B.1               | Reporter les fonctions C et theta                                                                                                                  | 82              |

| B.2               | Rerouter le graphe minimal d'accessibilité                                                                                                         | 83              |

|                   | Liste des algorithme.                                                                                                                              | <b>S</b>        |

|                   | Liste des digoritimes                                                                                                                              | J               |

|                   |                                                                                                                                                    |                 |

| 2.1               | Recherche des configurations accessibles au plus tôt                                                                                               | 80              |

| 2.2               | <u>-</u>                                                                                                                                           | 82              |

| 2.3               |                                                                                                                                                    | 86              |

| $\frac{2.5}{2.4}$ |                                                                                                                                                    | 87              |

| 3.1               | -                                                                                                                                                  | $\frac{37}{27}$ |

| J.1               | Transferred and I office and relations and I compression                                                                                           |                 |

| 3.2  | Traduction des <i>Tclasses</i> à l'origine de relations de <i>Sequence</i>                   | 128 |

|------|----------------------------------------------------------------------------------------------|-----|

| 3.3  | Traduction des <i>Tclasses</i> qui ne sont à pas l'origine de relations de <i>Preemp</i> -   |     |

|      | tion ou de $Sequence$                                                                        | 129 |

| 3.4  | Fonction $String\ Make\_Pre(T, \mathcal{T}, \mathcal{R})$                                    | 131 |

| 3.5  | Fonction $String\ Make\_Seq(T,\ \mathcal{T},\ \mathcal{R})$                                  | 132 |

| 3.6  | Réduction des Tclasses à l'origine de relations de Sequence et de Preemption                 | 133 |

| 3.7  | Amélioration de la fonction $String\ Make\_Seq(T,\mathcal{T},\mathcal{R})$                   | 135 |

| 3.8  | Amélioration de la réduction des <i>Tclasses</i> à l'origine de relations de <i>Sequence</i> |     |

|      | et de <i>Preemption</i>                                                                      | 136 |

| 3.9  | Construire l'ensemble de renommage des portes                                                | 137 |

| 3.10 | Traduction des relations Parallel et Synchro                                                 | 138 |

## Introduction

Au cours des décennies passées, les informaticiens ont eu pour défi d'élaborer des théories et des techniques qui puissent garantir que les systèmes informatiques fonctionnent correctement, c'est-à-dire, selon des caractéristiques prescrites exprimant leur comportement désiré. Les manières traditionnelles d'obtenir de telles «garanties» ont été la simulation et le test. Ces techniques permettent d'obtenir un certain degré de confiance dans la conformité du fonctionnement du système. Cependant, dans beaucoup de cas cette approche prend excessivement de temps et fournit souvent seulement une évaluation probabiliste de la conformité.

Dans la littérature, il a été proposé un grand nombre de techniques dotées d'un support mathématique pour raisonner sur la conformité des systèmes informatiques [Hoa69, Dij75, Pnu77, Lam77, Hoa78, Mil89, Hol91]. L'idée générale est de décrire dans un cadre formel les systèmes informatiques à étudier, puis d'appliquer des méthodes rigoureuses pour démontrer que la description des systèmes est correcte, qu'elle répond bien à certaines exigences formellement définies. L'avantage de cette approche est qu'elle peut être employée tôt dans le cycle de conception pour détecter des erreurs de conception logique avant même que les systèmes n'aient encore été mis en œuvre.

L'étude exposée dans ce document s'intéresse à la conception de systèmes temps-réel en s'appuyant sur la méthode formelle RT-Lotos, extension temporelle à l'algèbre de processus Lotos. Nous abordons plusieurs points relatifs à la spécification, la validation et l'ordonnancement de systèmes concurrents sujets à des contraintes logiques et temporelles.

#### Systèmes temps-réel

Un système temps-réel est un système informatique doté d'un comportement qui est contraint par le temps. À la différence de systèmes non temporisés, un système temps-réel doit interagir correctement avec son environnement non seulement au regard des informations échangées, mais également au regard des instants auxquels ces interactions se réalisent.

Les systèmes temps-réel sont fréquemment soit des systèmes embarqués, soit des systèmes critiques, qui apparaissent comme des composants de systèmes complexes plus importants et dont la sûreté de fonctionnement est critique [Sto96]. On distingue les systèmes temps-réel durs, qui doivent toujours réagir en temps opportun, et les systèmes temps-réel mous, qui peuvent occasionnellement ne pas satisfaire leurs contraintes temporelles sans compromettre leur fonctionnement normal [TH97]. Certains systèmes peuvent combiner des tâches temps-réel dures et des tâches temps-réel molles. Les systèmes temps-réel ont pour caractéristique commune qu'ils peuvent être constitués de nombreux composants fonctionnant en parallèle; ce sont donc des systèmes concurrents. Lorsqu'un système temps-réel doit réagir à chaque stimulus de l'environnement, il est appelé système réactif [Pnu86].

Le qualificatif «temps-réel» est parfois employé pour désigner des systèmes qui doivent réagir aux stimuli de leur environnement «aussi vite que possible». Implicitement, de tels systèmes ont pour contrainte de devoir terminer la réaction à un premier stimulus avant que le suivant ne se produise. Pour répondre à ce besoin, de tels systèmes doivent être «rapides». En fait, un système temps-réel, n'est pas nécessairement rapide, seulement il doit effectuer ses travaux au bon moment. Les systèmes temps-réel sont souvent sujets à des contraintes complexes de synchronisation et doivent accomplir plusieurs tâches en parallèle. De telles caractéristiques rendent complexes leur conception et leur exécution. Par ailleurs, s'il s'agit souvent de systèmes critiques, et l'on doit s'assurer de la correction de leur comportement. Des méthodes formelles peuvent alors être employées pour aider le développement de tels systèmes en fournissant un cadre formel dans lequel la vérification de leur fonctionnement correct peut être menée.

#### Méthodes formelles

Les méthodes formelles ou techniques de description formelle jouent un rôle fondamental dans les différentes étapes du processus de l'ingénierie des systèmes informatiques. Les techniques de description formelle peuvent être définies comme un ensemble de notations pourvues d'une sémantique formelle et d'outils utilisés pour spécifier sans ambiguïté un système complexe dans les différentes phases de son cycle de vie (expression des besoins, architecture fonctionnelle, architecture détaillée), et pour valider (simuler et vérifier formellement) un certain nombre de ses propriétés [Win90, Hal90]. Les méthodes formelles sont généralement caractérisées par quatre concepts de base: l'abstraction, l'indépendance vis-à-vis de l'implémentation, la sémantique formelle, et les méthodes de vérification utilisables.

À la fin des années 80, plusieurs techniques ont été développées pour décrire des systèmes de plus en plus complexes, d'une manière complète, non ambiguë, et à un niveau d'abstraction élevé. Ces techniques reposent en général sur des modèles mathématiques puissants qui leur permettent d'assurer une vérification a priori de ces systèmes.

#### Langage de description formelle

Les langages de description formelle sont issus du besoin de décrire complètement et sans ambiguïté les systèmes informatiques. La définition de la sémantique du langage est essentielle pour peu que l'on désire établir dans un cadre formel que tel système résout bien tel problème [Liv78, Gue81, AG92]. C'est en effet la sémantique qui donne le sens à un système, permettant ainsi de vérifier que le système fait effectivement ce que l'on attend de lui. L'utilisation de techniques de description formelles, complétées par des outils informatiques adaptés, offrant des fonctionnalités de simulation, de prototypage rapide, de validation et de vérification formelle, permet la conception de systèmes sûrs.

Les travaux présentés dans ce mémoire s'articulent autour de la méthode formelle RT-LOTOS, un langage qui permet de spécifier des systèmes temps-réel et de les valider par analyse d'accessibilité. RT-LOTOS appartient à la famille des algèbres de processus, un processus se définissant comme une machine à états finis fonctionnant de manière concurrente et autonome avec les autres processus et se synchronisant éventuellement avec eux lors de rendez-vous multiple.

#### Analyse d'accessibilité

La vérification est une approche s'appuyant sur un raisonnement mathématique qui permet de prouver que la description formelle d'un système satisfait certaines propriétés souhaitées. En d'autres termes, il s'agit de vérifier le bon fonctionnement d'un système de processus qui interagissent (réseau de communication, programmes qui s'exécutent en parallèle, etc.), c'est-à-dire l'absence de comportements indésirables (états bloquants, boucles infinies d'actions sans progression du temps, etc.) et la conformité des comportements possibles à des spécifications préétablies [Arn92]. L'analyse automatique suppose une modélisation du comportement des processus considérés, et une formalisation des propriétés à vérifier.

Nous distinguons deux approches pour vérifier le bon fonctionnement d'un système. L'approche énumérative consiste à construire de manière exhaustive tous les états du système d'après sa description formelle. Cette approche, relativement simple à mettre en place, n'est possible que si la modélisation du système est finie; son inconvénient majeur est la taille du modèle engendré qui croit exponentiellement avec le nombre de composantes parallèles du système. L'approche symbolique consiste à représenter les ensembles caractéristiques d'états par des prédicats. Cette approche, qui peut s'appliquer à des systèmes dont la modélisation est infinie, a l'avantage principal d'éviter l'explosion combinatoire; par contre, il est crucial de disposer d'une procédure de décision efficace pour comparer les prédicats avec les propriétés à vérifier.

Une modélisation discrète du temps permet de vérifier les systèmes temps-réel en utilisant directement l'approche énumérative. Si l'on souhaite une modélisation dense du temps l'approche énumérative n'est pas utilisable directement, le système ayant alors une modélisation infinie. Pour ce faire, le modèle utilisé doit pouvoir représenter des ensembles infinis

d'états le long d'une progression temporelle.

Le langage RT-LOTOS est pourvu d'une méthode de vérification par analyse d'accessibilité, qui est basée sur l'approche énumérative avec un traitement du temps dense. L'analyse d'accessibilité consiste à rechercher dans l'ensemble des états possibles du système modélisé, depuis l'état initial, une suite d'actions atteignant un état particulier [AD91]. Cette technique passe par la construction exhaustive de tous les états (appelés également configurations) du modèle. Ce résultat est obtenu, lorsque c'est possible, par la construction d'un système à états finis appelé graphe de régions. Dans un graphe de régions, chaque région est constituée essentiellement d'un ensemble de configurations qui sont équivalentes dans le sens où elles peuvent évoluer vers la même région dans le futur.

L'approche symbolique pour la vérification systèmes temps-réel a également été définie dans le cadre de vérification par model-checking d'automates temporisés [Yov93].

Les travaux exposés dans ce mémoire reposent sur l'analyse d'accessibilité de RT-LOTOS [CRdO95].

#### Contributions de la thèse

Les principales contributions de notre étude portent sur trois aspects.

- o Dans un premier temps, nous proposons un ensemble de travaux concernant les techniques de validation liées au langage RT-LOTOS. Plus précisément, nous nous intéressons à l'automate temporisé (appelé un DTA) dérivé d'une spécification RT-LOTOS, d'une part en terme de simulation (nous avons développé une technique de simulation rapide basée sur une exécution du DTA et non pas sur une exécution des actions sémantiques de la spécification RT-LOTOS), et d'autre part en termes de validation formelle (nous proposons un interfaçage entre des outils de vérification du type model-checker et RT-LOTOS au moyen d'une traduction entre les différents types d'automates temporisés employés).

- o Dans un deuxième temps, nous proposons une technique ainsi qu'un modèle formel pour extraire les comportements cohérents d'un système et réaliser l'ordonnancement dans le temps de ses actions, c'est-à-dire que nous cherchons à exploiter sous un angle nouveau les informations présentes dans les graphes de régions obtenus par analyse d'accessibilité. Ainsi, nous proposons un moyen de raffiner les graphes d'accessibilité, d'en élaguer certaines branches jugées non souhaitables, d'extraire les dates de tir possible des actions, et de les présenter sous la forme d'un nouveau type automate temporisé (appelé un TLSA) ayant pour vocation l'ordonnancement dans le temps des actions d'un système.

- o Dans un troisième temps, nous proposons un lien possible entre méthodes formelles et méthodes semi-formelles. Dans ce cadre, nous proposons une sémantique formelle pour les diagrammes UML s'appuyant sur RT-LOTOS, après avoir défini une extension temps-réel à UML (appelée TURTLE). Nous définissons ainsi une méthodologie qui s'inscrit dans les techniques de développement industriel classiques et qui permet une vérification formelle des systèmes temps-réel.

#### Plan du mémoire

Ce document est organisé en trois chapitres:

Chapitre 1: Ce chapitre introduit la problématique de la description formelle des systèmes temps-réel. Il expose plus particulièrement le formalisme RT-Lotos, et présente les diverses techniques de validation développées pour RT-Lotos.

- Chapitre 2: Ce chapitre traite de la problématique de l'ordonnancement de systèmes temps-réel. Il présente la solution que nous avons élaborée, en donne la formalisation, les techniques et algorithmes à mettre en œuvre, et propose une étude de cas.

- Chapitre 3: Ce chapitre propose une méthodologie permettant de lier une approche formelle et approche semi-formelle. Il présente notre solution s'appuyant sur UML et RT-Lotos et expose les techniques sous-jacentes que nous avons élaborées.

Certains algorithmes et détails d'implémentation sont décrits en annexe pour faciliter la lecture du mémoire.

# Formalisation des systèmes temps-réel et RT-Loτos

Ce chapitre introduit différentes techniques de description formelle pour la spécification des systèmes temps-réel. La première section expose différentes techniques pour la formalisation de systèmes temporels, tels que les réseaux de PETRI temporisés, les automates temporisés, et les algèbres de processus. La seconde section expose le formalisme RT-LOTOS, extension temporelle du formalisme LOTOS. Finalement, la troisième section présente différentes techniques de validation développées et mises en œuvre pour RT-LOTOS.

## 1.1 Différents formalismes pour exprimer des contraintes temporelles

Un système temps-réel est un système dont le comportement doit satisfaire des contraintes temporelles strictes. Les systèmes temps-réel sont en général caractérisés par des interactions complexes avec leur environnement et par des contraintes temporelles dont la violation peut être critique. Dans un tel contexte, une approche formelle permet de définir les différents types de contraintes en les étayant d'une sémantique précise, de poser également les hypothèses de travail nécessaires comme par exemple la manière dont le temps progresse par rapport à l'exécution du système et les actions qu'il réalise, puis finalement, de vérifier a priori la conformité de l'ensemble des comportements possibles du système vis-à-vis de propriétés fixées a priori.

De nombreuses méthodes formelles existent pour modéliser les systèmes temps-réel [HD96]. Nous nous attacherons ici aux systèmes avec un domaine temporel dense. Dans ce contexte, nous retiendrons les extensions temporisées des réseaux de PETRI, les automates

temporisés, et les algèbres de processus.

#### 1.1.1 Extensions temporisées des réseaux de Petri

Les réseaux de Petri (notés RdP), du fait de leur sémantique du parallélisme et de leur représentation graphique, apparaissent comme particulièrement attractifs pour la modélisation d'architectures. Le modèle initial des réseaux de Petri est atemporel. Plusieurs extensions ont été proposées pour prendre en compte le temps. Une comparaison détaillée est présentée dans [Boy01]. On y distingue principalement quatre grandes «familles» de réseaux :

Les réseaux de Petri temporisés qui associent une durée aux transitions ou aux places.

- RdP t-temporisés (C. RAMCHANDANI): le tir d'une transition n'est plus instantané (de durée nulle) mais nécessite un certain temps [Ram74].

- RdP p-temporisés (J. SIFAKIS): un jeton déposé dans une place reste indisponible pendant un certain temps [Sif77].

- RdP temporisés (R.R. RAZOUK et C.V. PHELPS): une transition doit rester sensibilisée pendant un certain temps avant de pouvoir être tirée, puis le tir commence et se poursuit durant un certain temps [RP84].

Les réseaux de Petri temporels qui préfèrent la notion de délai (entre événements) à celle de durée (d'un état ou d'une action).

- RdP temporels (P. MERLIN): un intervalle de temps [a,b] est associé à chaque transition; si la transition est sensibilisée de façon continue, elle va être tirée entre a et b unités de temps [Mer74, MF76].

- RdP à arcs temporels (B. Walter): le temps porte sur les arcs incidents aux transitions; une transition ne peut être tirée que s'il existe, pour chaque place en entrée de la transition, un jeton dont l'âge est bien dans l'intervalle de l'arc reliant la place à la transition, mais rien ne force le tir de la transition lorsque la borne maximale de son intervalle temporel est atteinte [Wal83].

- RdP p-temporels (W. KHANSAS): un intervalle temporel est associé aux places; un jeton dans une place annotée d'un intervalle [a,b] ne peut pas quitter cette place avant d'y avoir passé au moins a unités de temps, et doit la quitter avant b unités de temps; si un jeton n'arrive pas à quitter une place avant b unités de temps, il devient un jeton mort [Kha97].

- RdP statiquement temporisés (A. CERONE et A. MAGGIOLO-SCHETTINI): un modèle très général qui associe un intervalle temporel sur les places, les transitions et les arcs incidents aux transitions, et pourvu de deux sémantiques de tir forte (une transition est forcée lorsqu'elle atteint la borne maximum de son intervalle de tir) ou faible (un jeton peut rester indéfiniment dans une place) [CMS99].

Les systèmes à gardes algébriques qui utilisent des contraintes temporelles de la forme  $(3 \le x) \lor (x \le 7)$  (où x représente une valeur d'horloge) plutôt que de simples

durées ou délais. Ce type de contraintes est proche des gardes que l'on trouve sur les automates temporisés (voir section 1.1.2). Les réseaux RT (H. BOUCHENEB), définis dans [Bou99], se présentent comme un modèle unificateur qui ajoute des conditions temporelles aux réseaux de Petri prédicat/transition de H.J. Genrich ([Gen89]).

Les systèmes à synchronisation, c'est-à-dire des modèles conçus pour modéliser un système comme la composition de sous-éléments en les «synchronisant». Les réseaux de PETRI à flux temporels (RdPFT) (M. DIAZ et P. SÉNAC), introduits pour la modélisation de scénarios multimédia [DS93], associent des durées aux places, des règles de synchronisation entre éléments, une condition temporelle sur les arcs, et différents modes possible de synchronisation entre flux. Une extension hiérarchique des RdPFT a été introduite [SDLdSS96, Sén96] pour permettre de modéliser des scénarios complexes de façon modulaire.

#### 1.1.2 Automates temporisés

Les automates temporisés ont étés introduits par Rajeev Alur et David L. Dill [ACD90, AD91, AD94]. Un automate temporisé est un automate à états finis classique étendu par un ensemble de variables à valeur réelles appelées horloges. Ces horloges représentent les horloges des entités concurrentes d'un système. Elles sont supposées croître toutes à la même vitesse, et mesurer le temps passé depuis leur dernière remise à zéro. Les horloges peuvent êtres testées (comparées à des entiers naturels) et remises à zéro. Un état (ou configuration) du système est composé d'un état de contrôle de l'automate et d'un jeu de valeurs des horloges. Les transitions entre les états de contrôle de l'automate sont composées (i) d'un label appelé action, (ii) d'une condition temporelle de sensibilisation appelée garde définie sur les horloges du système qui doit être satisfaite pour autoriser le système à réaliser la transition, et (iii) d'un ensemble d'horloges qui doivent être remises à zéro. Les transitions sont atomiques, c'est-à-dire qu'elles se réalisent en un temps nul. Par contre, le temps peut s'écouler au sein des états de contrôle de l'automate.

De nombreux travaux ont proposé des extensions à ce modèle.

La notion d'urgence a été introduite :

- soit en distinguant des actions urgentes des actions non urgentes, comme dans l'algèbre de processus CCS [Mil89];

- soit en ajoutant à chaque état de contrôle de l'automate une condition temporelle appelée invariant définie sur les horloges du système qui doit rester satisfaite lors d'une progression du temps à l'intérieur de l'état de contrôle [HNSY94];

- soit en ajoutant à chaque transition une condition temporelle qui indique, lorsqu'elle est satisfaite, que le temps ne peut plus progresser (*Timed Automata with Deadlines* [BST97], *Dynamic Timed Automata* (DTA) section 1.3.2).

Dans un but d'optimisation, des travaux ont proposé de réduire le nombre d'horloges. Une première approche consiste à essayer de repérer les horloges non utilisées et les horloges qui sont toujours égales [DY96]. Une autre approche consiste à définir un ensemble

d'horloges non plus globales à tout le système mais locales à chacun des états de contrôle de l'automate. Des fonctions de recopie d'horloges sont alors ajoutées aux transitions. Le nombre d'horloges par état de contrôle est a priori inférieur ou égal au nombre d'horloges globales du système (voir également la définition du DTA dans la section 1.3.2).

Des travaux ont proposé une extension radicale du modèle en introduisant des horloges ne progressant plus nécessairement toutes au même rythme. Ces automates sont appelés automates hybrides [NSY93].

On trouvera dans [Pet99] un historique très clair des différents modèles, depuis les premiers travaux de Alur et Dill jusqu'au modèle de l'outil UPPAAL [UPP].

#### i) Composition d'automates

Un système est divisé habituellement en parties, ou sous-systèmes. Dès lors, il peut être pratique de décrire la *composition* de sous-systèmes qui s'exécutent en parallèle et qui communiquent et se synchronisent entre eux.

Le modèle traditionnel des automates temporisés est basé sur un passage synchrone du temps pour tous les sous-systèmes et un entrelacement des actions atomiques de chaque sous-système. On parle alors de temps universel par opposition à une perception locale de l'écoulement du temps que pourrait avoir chacun des sous-systèmes (cette perception pouvant être soumise à des dérives, de la gigue, etc.)

Dans le cas de la synchronisation d'automates, il est plus courant de définir un opérateur qui définit la synchronisation. Du fait de l'absence de parallélisme intrinsèque au modèle, la composition de deux automates crée un automate avec un nombre d'états de contrôle important (de l'ordre du produit du nombre des états de contrôle des automates composés), qui dissuade de les construire à la main. Ainsi, l'opérateur de synchronisation doit générer automatiquement le nouvel automate, fruit de la synchronisation des deux autres: ses états de contrôle, ses transitions, mais aussi ses contraintes temporelles. En pratique, la synchronisation est généralement faite à la volée (on ne construit pas le résultat explicitement). Par contre, la sémantique de la composition doit être effectivement définie.

Dans [ACD90], la composition parallèle d'automates temporisés est interprétée comme une conjonction logique similaire à l'opérateur de (multi-)synchronisation forte des algèbres de processus. Intuitivement cela signifie que pour être composés, deux systèmes doivent réaliser les mêmes actions aux mêmes dates. Cette restriction est trop forte pour être utilisée en pratique. Par conséquent, des travaux ont proposé d'autres sémantiques de composition d'automates temporisés. Certains auteurs, toujours en suivant le modèle d'algèbre de processus, proposent d'une part une fonction de relation de complémentarité entre action qui dit qu'une action a peut se synchroniser avec son action complémentaire  $\bar{a}$  en donnant une action invisible  $\tau$ , et d'autre part une restriction '\' telle que  $A_1 \parallel A_2 \setminus_{\{a,b\}}$  oblige les automates  $A_1$  et  $A_2$  à se synchroniser sur les actions  $a,\bar{a}$  et  $b,\bar{b}$ . Ce modèle de synchronisation deux à deux a obligé l'introduction de la notion de nœuds committed, c'est-à-dire (en simplifiant) des états de contrôle où on ne peut pas rester, pour garantir une atomicité lors de synchronisations entre plusieurs automates. Toutes ces variations sont présentées

de façon claire dans [Bur98]. Pour traiter la synchronisation entre automates, [LL98a] propose un cadre plus général que la synchronisation deux à deux: une fonction qui permet de synchroniser n automates et d'associer n'importe quel nom à cette synchronisation (au lieu de nécessairement la cacher en la transformant en une action invisible  $\tau$ ).

#### ii) Vrai parallélisme et entrelacement

La composition d'automates temporisés est basée sur une notion de parallélisme par entrelacement des actions. La sémantique de parallélisme par entrelacement s'oppose traditionnellement à la sémantique dite de vrai parallélisme.

Dans le cas d'un parallélisme par entrelacement, les actions sont nécessairement atomiques; typiquement, une activité qui consomme du temps est spécifiée par une action de début et une action de fin. L'occurrence de «deux actions parallèles a et b au même instant» sera représentée par un losange que l'on ne pourrait différencier de «a suivi de b ou b suivi de a», qui donnerait le même losange:

Cependant, cette interprétation de la concurrence souffre de plusieurs inconvénients majeurs dès que l'on veut en particulier s'abstraire des hypothèses d'atomicité (temporelle et/ou spatiale) des actions. Pour résoudre ces problèmes, différentes sémantiques alternatives (connues globalement sous le nom de sémantiques de vrai parallélisme) ont été étudiées, comme, par exemple, les sémantiques de causalité [CdC93] et de maximalité [Saï96]. Ces sémantiques imposent un traitement mathématique plus complexe et n'ont à ce jour pas réellement percé pratiquement.

#### 1.1.3 Algèbres de processus

Les algèbres de processus sont des langages abstraits conçus pour la spécification, la conception, et l'analyse fonctionnelle de systèmes concurrents. De nombreux modèles ont été proposés. Les modèles émergents sont LOTOS (Language of Temporal Ordering Specification [BB87]), CCS (Calculus of Communicating Systems de R. MILNER [Mil89]), CSP (Communicating Sequential Process de C.A.R. HOARE [Hoa89]), ACP (Algebra of Communicating Processes de J.A. BERGSTRA [BK85]), auxquels peuvent être ajoutés des modèles qui introduisent le temps, comme TCCS (Temporal CCS [MT90]), ainsi que les langages du type SPA (Stochastic Process Algebras de U. HERZOG [HR98]).

Dans les algèbres de processus, les systèmes sont modélisés par un ensemble de processus, des entités appelées agents, qui exécutent des actions atomiques. Ces actions sont les briques de base du langage, et des opérateurs sont utilisés pour décrire des comportements séquentiels qui peuvent s'exécuter de manière concurrente et se synchroniser (et communiquer) entre eux.

Avec CCS, deux agents communiquent lorsque l'un réalise une action, par exemple a, et que l'autre réalise l'action complémentaire  $\bar{a}$ . L'action résultant de la communication est distinguée par le label  $\tau$ , qui représente une action interne invisible à l'environnement. Les agents peuvent réaliser leurs actions internes indépendamment les uns des autres, en

parallèle, avec une sémantique d'entrelacement. Les opérateurs du langage permettent de construire un agent pour lequel on spécifie une première action (préfixe); un choix entre plusieurs alternatives (choix); ou des activités concurrentes (composition).

Le mécanisme de communication de CSP diffère car il n'y a pas de notion de complémentarité des actions: deux agents communiquent en réalisant simultanément la même action (avec le même label). Lors de la communication, l'action conjointe reste visible à l'environnement, et peut être utilisée par d'autres processus; ainsi, plus de deux processus peuvent participer à une communication.

L'approche ACP se caractérise par une approche purement algébrique. Elle partage avec CSP la même notion d'équivalence (équivalence par bisimulation).

Les approches CCS, CSP et ACP ont pour objectif une analyse qualitative et non quantitative, et font ainsi abstraction du temps. Plusieurs travaux ont proposé d'incorporer le temps dans les algèbres de processus. Une vue d'ensemble de la problématique est proposée dans [NS91]; le lecteur trouvera également dans [Ver97] un exposé détaillé, précis et très complet des algèbres de processus, notamment celles intégrant le temps. Par exemple, TCCS étend CCS avec un délai fixe et une attente pour réaliser les synchronisations, en considérant que les actions consomment un temps nul (actions atomiques). Par opposition, les SPAs associent généralement une variable aléatoire représentant la durée de chaque action. Par contre, les SPAs adoptent le mécanisme de communication (multiple) de CSP.

Lotos appartient également à la famille des algèbres de processus. Il s'agit d'un langage basé sur les concepts de CCS et CSP pour la description des aspects contrôle, et les types abstraits algébriques pour la description des données. Lotos sera présenté plus en détail dans le paragraphe 1.2.1.

Les algèbres de processus apparaissent comme des modèles de description formelle et de spécification «orientés contraintes» [VSvSB91, Led94] qui semblent bien adaptés à l'intuition et à la compréhension humaine. Ajoutée à cela la faculté d'automatiser le processus de vérification, ces modèles connaissent un certain succès.

#### 1.1.4 Principales extensions temporelles à Lotos

LOTOS [Lot88] est une algèbre de processus permettant d'exprimer la structure logique et temporelle de comportements. Ce modèle formel sera détaillé dans la sous-section 1.2.1.

Lotos appartient à la famille des *algèbres de processus*; il s'appuie sur le langage CCS de MILNER (étendu par un mécanisme de synchronisation multipoint hérité de CSP de Hoare) pour la spécification de la partie comportementale; la partie description des structures de données est inspirée de Act-One, un formalisme de description de types de données abstraits algébrique. Lotos est un langage asynchrone, avec synchronisation par rendez-vous multiples. Les processus offrent des synchronisations à leur environnement au travers de *portes* de communication (ou *actions*).

La problématique de l'expression explicite du temps dans Lotos a engendré une série

d'approches différentes. Nous listons les principaux modèles ci-dessous:

- TIC-Lotos (Quemada 1987, UPM Espagne)

- Lotos-T (Miguel 1992, UPM Espagne)

- T-Lotos et U-Lotos (Bolognesi 1991, CNUCE Italie)

- TLOTOS (LEDUC 1992, ULG Belgique)

- Time Lotos et ET-Lotos (Leduc, Léonard 1993-94, ULG Belgique)

- TE-Lotos (Leduc, Léonard, Quemada, Miguel et all., 1995)

- Lotos/T (Nakata 1993, ES-Osaka Japon)

- RT-Lotos (Courtiat 1993, LAAS France)

- E-Lotos (ISO/IEC 15437:2001)

Certaines de ces approches ont servi de prémices et de base de réflexion aux approches qui ont suivi. Certains concepts émergents semblent poindre à travers l'ensemble de ces travaux. Pour différencier ces approches, nous considérerons les aspects suivants:

- Choix du domaine temporel:

- 1. Soit discret: les grandeurs temporelles sont définies sur les entiers naturels (Z), une progression de une unité de temps peut alors être transcrite par l'occurrence d'une action spécifique (fréquemment notée tic). Ceci facilite la définition formelle, car le modèle se rapproche du modèle non temporisé, mais occasionne un fort risque d'explosion combinatoire.

- 2. Soit dense et dénombrable: les grandeurs temporelles sont définies sur les rationnels positifs  $(\mathbb{Q}^{0,\infty}_+)$ . Cela semble parfaitement convenir à la grande majorité des cas pratiques d'utilisation d'un langage de spécification formelle de systèmes temps-réel. Le modèle mathématique sous-jacent est, par contre, plus complexe à définir et à mettre en œuvre dans le cadre de la vérification.

- 3. Soit  $r\acute{e}el$ : quelques rares modèles évoquent la possibilité de définir les grandeurs temporelles dans  $\mathbb{R}^{0,\infty}_+$ . Notons qu'alors, à notre connaissance, aucune technique de validation n'a été proposée.

- Temporisation des actions: elle se fait soit par l'ajout d'un opérateur temporel dédié  $(*opérateur\langle \cdots \rangle P)$ , soit par une extension de l'opérateur de préfixe (préfixe d'un processus par une action:  $(*g\langle \cdots \rangle ; P)$ , soit les deux.

- Hypothèses d'urgence des actions: une action est dite urgente lorsqu'elle doit se réaliser immédiatement, sans progression possible du temps, dès qu'elle est sensibilisée. Certains modèles présupposent implicitement que toutes les actions sont urgentes. La plupart associent l'urgence aux actions internes (l'action i ou une action intériorisée par hide). Certains modèles introduisent un mot clef spécifique pour déclarer urgentes des actions internes ou observables. D'autres, enfin, proposent des mécanismes pour relâcher l'urgence des actions internes sous certaines conditions.

- Opérateurs additionnels: certains langages proposent des facilités d'écriture pour spécifier des comportements réputés classiques par le biais d'opérateurs de haut niveau, qui toutefois n'introduisent pas véritablement de fonctionnalités nouvelles dans

le modèle (en d'autre terme, les comportements spécifiés pas ces opérateurs de haut niveau peuvent également être spécifiés au moyen d'opérateurs du modèle de base, mais de manière plus lourde).

|            | Domaine temporel         | Temporisation       | Urgence             |

|------------|--------------------------|---------------------|---------------------|

| TIC-Lotos  | discret                  | préfix et opérateur | toute action        |

| Lotos-T    | discret ou dense         | prefix              | actions cachées     |

| T-Lotos    | $\operatorname{discret}$ | opérateur           | mot clef spécifique |

| U-Lotos    | $\operatorname{discret}$ | opérateur           | mot clef spécifique |

| TLotos     | discret                  | opérateur           | relâchée            |

| Time Lotos | $\operatorname{dense}$   | opérateur           | actions cachées     |

| ET-Lotos   | $\operatorname{dense}$   | préfix et opérateur | actions cachées     |

| TE-Lotos   | $\operatorname{dense}$   | préfix et opérateur | toute action        |

| Lotos/T    | discret                  | préfix              | mot clef spécifique |

| RT-Lotos   | $\operatorname{dense}$   | préfix et opérateur | actions cachées     |

| E-Lotos    | $\operatorname{dense}$   | préfix et opérateur | actions cachées     |

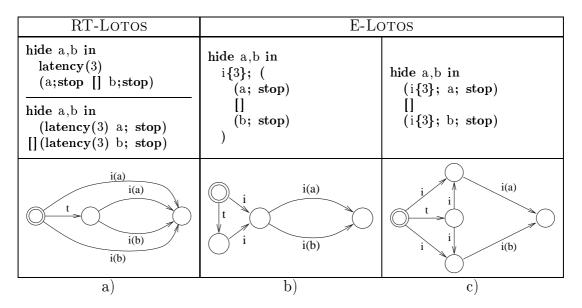

Fig. 1.1 – Comparaison des extensions temporelles à Lotos

La figure 1.1 reprend dans les grandes lignes quelques points de comparaison entre les différentes extensions temporelles à LOTOS listées ici.

#### i) TImed Calculus (QUEMADA)

Dans [QF87, QAdF89, QdFA93] les auteurs proposent une algèbre de processus appelée TImed Calculus (TIC), basée sur un domaine temporel discret. Le temps est introduit sur l'opérateur de préfixe: «at; P», où  $t \in \mathbb{Z}$  et P est un processus TIC, désigne un processus qui réalise l'action a (implicitement urgente) après t unités de temps depuis la précédente action, puis se comporte comme P. Une extension appelée «opérateur de choix temporel» est disponible: «aT; P», où T désigne un intervalle de  $\mathbb{Z}$ , désigne un processus qui réalise l'action a après un délai choisi dans T. Le modèle propose également d'un opérateur «Age (t,P)» qui permet de consommer t unités de temps sur la première action de P.

Notons que cette approche associe les contraintes temporelles entre événements successifs dans une expression de préfixage. C'est pourquoi, il est impossible de faire une spécification de conditions temporelles pour des événements non successifs sans utiliser d'événements intermédiaires ou processus avec contraintes additionnelles [vHTZ89]. Cette approche ne permet pas non plus d'exprimer des contraintes temporelles globales et pour cela, lors d'un événement de synchronisation, le délai associé à une porte est défini par les contraintes temporelles locales des processus qui y participent [MBC+94].

#### ii) Lotos-T (Miguel)

Dans [MFV92] les auteurs proposent une algèbre de processus appelée Lotos-T, basée sur un domaine temporel qui doit être spécifié au moyen d'un type abstrait (comprenant au moins >, 0, et +), et qui donc, peut être discret ou dense. Ce modèle s'appuie sur le modèle TIC. Le temps est introduit par l'opérateur de préfixe: « $a\{t\}$ ; P», où t est du temps et P est un processus Lotos-T, qui désigne un processus réalisant l'action a après t unités de temps depuis la précédente action, puis se comporte comme P. L'urgence n'est plus implicitement systématique, mais devient attachée aux actions internes uniquement. Notons qu'il n'est plus possible de spécifier un intervalle temporel : le non-déterminisme temporel étant obtenu comme un cas particulier du non-déterminisme de l'opérateur de choix sur une variable libre de type temps:

ce qui, en pratique, réduit le domaine temporel à un domaine énumérable par l'opérateur de choix, donc vraisemblablement, non dense.

Notons par ailleurs que les auteurs proposent un modèle étendu, appelé LOTOS-TP, qui permet de spécifier également des comportements probabilisés.

#### iii) U-Lotos/ T-Lotos (Bolognesi)

Les auteurs [BL91a, BL91b] proposent deux algèbres de processus appelées U-LOTOS et T-LOTOS, basées sur un domaine temporel discret. Ces approches sont inspirées des réseaux de PETRI temporels de type MERLIN [Mer74, MF76] et de TCCS [MT90]

U-Lotos introduit le temps par un nouvel opérateur de préfixe : (t). P» est le processus qui laisse s'écouler t unités de temps puis se transforme en P. L'urgence est spécifiée par l'opérateur asap (as soon as possible) : «asap G in P» rend urgente les portes de l'ensemble G dans P.

T-LOTOS propose également la construction (t).P, et généralise l'opérateur d'urgence des actions: «timer a(t1, t2) in P» est le processus qui se comporte comme P excepté que l'action a doit être exécutée dans l'intervalle temporel [t1,t2] dès qu'elle est sensibilisée. Le processus U-LOTOS «asap a in P» est équivalent au processus T-LOTOS «timer a(0,0) in P».

Le problème principal de la proposition T-LOTOS est relatif à l'occurrence d'une action observable. L'exécution d'une action interne peut être contrôlée par le processus lui-même, mais l'occurrence d'un événement observable (non interne) correspond à une proposition d'interaction faite à l'environnement, dont la participation à la synchronisation est requise pour l'occurrence de l'action. Pourtant, les opérateurs d'urgence forcent l'occurrence des actions observables à la fin de l'intervalle temporel, ce qui nous parait contre-intuitif.

#### iv) TLOTOS (LEDUC)

L'auteur [Led91] propose une algèbre de processus appelée TLOTOS, définie sur un domaine temporel discret, inspirée de ATP (Algebra of Timed Processes [NS94]).

Soit P et Q deux processus TLOTOS, et  $d \in \mathbb{Z}$ ; le temps est introduit par trois opérateurs. L'opérateur start delay (ou opérateur de time-out), noté  $\lfloor P \rfloor^d(Q)$ , désigne le processus qui se comporte comme P à condition que P débute avant d unités de temps, ou autrement qui se comporte comme Q. L'opérateur execution delay (ou opérateur de watchdog), noté  $\lceil P \rceil^d(Q)$ , désigne le processus qui se comporte comme le processus P avant la  $d^{\grave{e}me}$  unités de temps, et comme Q ensuite. L'urgence implicite des actions est relâchée, localement à un processus, par l'opérateur unbounded start delay, noté  $\lfloor P \rfloor^\omega$ , et qui désigne le processus qui se comporte comme P excepté qu'il peut attendre un temps arbitrairement long avant de débuter. Lors de compositions, l'urgence ou non des actions est attachée à la notion d'actions cachées ou observables. La sémantique de ces trois opérateurs est identique à leurs correspondants du modèle ATP.

#### v) Timed Lotos/ET-Lotos (LEDUC, LÉONARD)

Les auteurs de [LL92, LL93, LL97] proposent deux algèbres de processus appelées Timed LOTOS et ET-LOTOS, définies sur un domaine temporel dense.

Timed Lotos [LL92] introduit le temps au moyen d'un opérateur de délai, noté  $\Delta^{[d^-,d^+]}P$ , qui désigne le processus qui laisse passer un temps choisi dans l'intervalle  $[d^-,d^+]$ , puis se comporte comme P (avec éventuellement  $d^+=\omega$  pour spécifier un intervalle non borné). Le modèle apporte également deux opérateurs qui s'appliquent aux portes d'un processus. L'opérateur delay on interactions, noté  $\Delta_g^I P$  (où I est un intervalle temporel, g une porte (d'interactions), et P un processus), introduit un délai non-déterministe choisi dans I sur toutes les actions g de P. L'opérateur de time-out, noté  $\lfloor P \rfloor_g^d(Q)$ , spécifie que si le processus P propose une interaction sur la porte g sans succès pendant une période g, alors g est interrompu et remplacé par g.

ET-LOTOS (pour Enhanced Timed LOTOS) [LL93, LL97] étend le modèle Timed LO-TOS au niveau de l'opérateur de préfixe d'action par une offre limitée dans le temps et un mécanisme de capture de date: « $g \ Qt \ \{d\}$ ; P» spécifie le processus qui offre une interaction sur la porte q pendant au plus d unités de temps, enregistre le temps écoulé entre l'offre et l'occurrence de q dans la variable t, puis se comporte comme le processus P. Si, à l'instant d, l'action proposée ne s'est pas produite, alors ce processus devient le processus stop. L'urgence est attachée à la notion d'action cachée: une action interne est potentiellement urgente. Notons que l'offre limitée dans le temps peut s'appliquer à l'action interne i, mais que sa signification est tout autre: i{d} introduit un délai non-déterministe choisi dans [0,d] avant de réaliser l'action interne i. L'opérateur de délai de Timed Lotos  $\Delta^{[d^-,d^+]}$ permettait de spécifier un délai non-déterministe choisi dans l'intervalle. L'opérateur de délai de ET-Lotos  $\Delta^d$  propose uniquement un délai déterministe, le non-déterminisme temporel étant introduit par ailleurs, au moyen de i{d}. Cela introduit une restriction du pouvoir d'expression du modèle qui sera expliqué dans un paragraphe suivant, lors d'une comparaison avec RT-Lotos. Les opérateurs  $\Delta_q^I P$  et  $\lfloor P \rfloor_q^d(Q)$  sont également présents, mais apparaissent désormais comme des opérateurs de haut niveau pouvant être ré-écrits avec les opérateurs de bas niveau de ET-Lotos.

Le formalisme ET-Lotos a suscité de nombreux autres travaux. Dans [BDS95] on

peut trouver une sémantique dénotationnelle pour ET-LOTOS et dans [BD97, BK97] une proposition de sémantique de vrai parallélisme causal.

#### vi) TE-LOTOS (LEDUC, LÉONARD, QUEMADA, MIGUEL et al.)

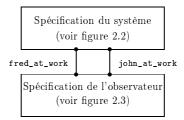

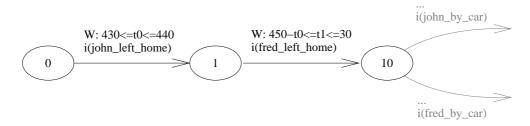

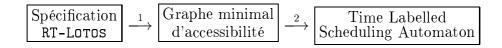

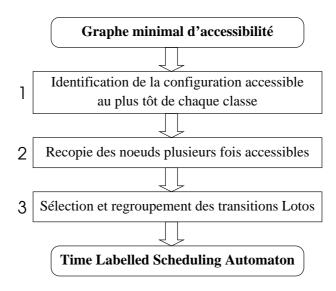

Dans [LLdF<sup>+</sup>95], les auteurs proposent une unification de plusieurs travaux autour de Lotos et du temps, appelée TE-Lotos (pour *Time Extended* Lotos), dans le cadre des activités de normalisation d'une version étendue de Lotos.