### Techniques de conception pour le durcissement des circuits intégrés face aux rayonnements

F. Vinci dos Santos

#### ▶ To cite this version:

F. Vinci dos Santos. Techniques de conception pour le durcissement des circuits intégrés face aux rayonnements. Micro et nanotechnologies/Microélectronique. Université Joseph-Fourier - Grenoble I, 1998. Français. NNT: . tel-00003047

### HAL Id: tel-00003047 https://theses.hal.science/tel-00003047

Submitted on 25 Jun 2003

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE

présentée par

## Filipe VINCI DOS SANTOS

pour obtenir le titre de DOCTEUR

### de l'UNIVERSITÉ JOSEPH FOURIER — GRENOBLE 1

(arrêtés ministériels du 5 juillet 1984 et du 30 mars 1992)

Spécialité : Physique-Microélectronique

# Techniques de conception pour le durcissement des circuits intégrés face aux rayonnements

Date de Soutenance : 15 Octobre 1998

Composition du Jury:

Bernard Courtois Directeur de Thèse

Pierre Gentil Président

Andreas Kaiser Rapporteur

Jean-Michel Karam Examinateur

Volker Kempe Examinateur

Thèse préparée au sein du Laboratoire TIMA 46, Avenue Félix Viallet, F-38031 Grenoble

#### Résumé

Les microsystèmes sont le dernier développement de la microélectronique. Leur apparition ouvre des possibilités révolutionnaires dans plusieurs domaines d'application, dont l'exploitation de l'espace. L'utilisation des microsystèmes dans l'espace se heurte au problème de l'expostion à la radiation, notamment pour la partie électronique. Cet obstacle a été surmonté dans le passé par la mise en place de filières de fabrication résistantes («durcies») aux effets de la radiation. Le rétrécissment des budgets militaires a provoqué la disparition de la plupart des technologies de fabrication durcies, ce qui est en train de pousser les constructeurs vers l'emploi de technologies commerciales standard (COTS). L'objectif de cette thèse a été d'investiguer des techniques de conception pour le durcissement d'un microsystème fabriqué par une technologie COTS. Le microsystème en question est un capteur de rayonnements infrarouges basé sur des thermopiles en silicium, suspendues par une étape de micro-usinage en volume par la face avant. Les éléments pertinents des différents domaines de connaissance impliqués sont passés en revue, avec une analyse des techniques de durcissement applicables à la construction de l'életronique de lecture en technologie CMOS. Un programme de caractérisation expérimentale a été réalisé, et il a permit d'établir le niveau de sensibilité de la technologie aux rayonnements et l'efficacité des techniques de durcissement développées. Les très bons résultats obtenus ont permis de passer à la réalisation de la chaîne de lecture du capteur, qui a été fabriquée, caractérisée et qualifiée pour l'espace.

Mots-clé: technologie CMOS, contrôle d'attitude et d'orbite, systèmes spatiales, microsystèmes, circuits intégrés, durcissement face aux rayonnements, thermopiles intégrés, thermocouples en silicium, capteurs d'infrarouge, micro-usinage en volume, composants COTS, VLSI, microélectronique.

#### Abstract

Integrated microsystems are the latest development of microelectronics. Their appearance allows a host of revolutionary new applications in several fields, including space exploration. The use of microsystems in space is hampered by the problem of exposure to radiation, particularly for the electronics section. This problem has been overcome in the past through the development of special fabrication technologies ("hardened"), able to resist the effects of radiation. The cutback in the military budgets has been responsible for the extinction of most radiation-hardened technologies. This fact is pushing the space industry towards the use of commercial off-the-shelf (COTS) technologies. The purpose of this thesis is to explore design techniques for the radiation-hardening of an integrated microsystem fabricated on a COTS technology. This microsystem is an infra-red sensor based on silicon thermopiles, suspended by front-side bulk micromachining. The pertinent elements of the different domains of knowledge needed for this task are reviewed, with an analysis of the hardening techniques applicable to the realization of the read-out electronics in CMOS technology. An experimental characterization program was carried out, and it has allowed to establish precisely the level of radiation tolerance of the technology, as well as to evaluate the usefulness of the design techniques developed. The excellent results obtained gave impulse to the endeavor of fabricating the whole sensor read-out chain. This chain was designed, manufactured, tested and qualified for space use.

Keywords: CMOS technology, attitude and orbit control, space systems, microsystems, integrated circuits, radiation hardening, integrated thermopiles, silicon thermocouples, infrared sensors, bulk micromachining, COTS components, VLSI, microelectronics.

# Table des matières

| 1 | Inti | roducti | ion                                            |     | 1  |

|---|------|---------|------------------------------------------------|-----|----|

|   | 1.1  | Des b   | ombes-A au téléphone portable                  |     | 1  |

|   |      | 1.1.1   | Le marché civil des télécommunication          |     | 4  |

|   |      | 1.1.2   | Les microsystèmes intégrés                     |     | 6  |

|   | 1.2  | Objec   | tif et organisation de l'étude                 | . , | 8  |

| I | Pri  | incipe  | s                                              |     | 13 |

| 2 | Les  | dispos  | sitifs semiconducteurs                         |     | 15 |

|   | 2.1  | Introd  | luction                                        |     | 15 |

|   | 2.2  | La con  | nductivité                                     |     | 16 |

|   |      | 2.2.1   | Les bandes d'énergie                           |     | 16 |

|   |      | 2.2.2   | Le dopage                                      |     | 18 |

|   | 2.3  | La jon  | nction p-n                                     |     | 21 |

|   |      | 2.3.1   | La diode                                       |     | 23 |

|   | 2.4  | Le tra  | msistor MOS                                    | . , | 24 |

|   |      | 2.4.1   | La structure Conducteur-Isolant-Semiconducteur |     | 26 |

|   |      | 2.4.2   | Tension de Bandes Plates                       |     | 28 |

|   |      | 2.4.3   | Modélisation du transistor MOS                 |     | 32 |

|   |      | 2.4.4   | Modèle de Schichman-Hodges                     |     | 35 |

|   |      | 2.4.5   | Modèle de Meyer                                |     | 36 |

|   |      | 2.4.6   | Modèle en petits signaux                       |     | 38 |

|   |      | 2.4.7   | Modélisation du bruit                          |     | 39 |

| 3 | Les  | techne  | ologies de fabrication                         |     | 45 |

|   | 3.1  | Introd  | luction                                        |     | 45 |

|   | 3.2  | Le pro  | océdé planar                                   |     | 46 |

|   | 3.3  | Les or  | pérations élémentaires                         | + + | 48 |

|   |      | 3.3.1   | Le masquage et la photo-lithographie           |     | 48 |

|   |      | 3.3.2   | La gravure                                     |     | 48 |

|   |      | 3.3.3   | L'oxydation                                    |     | 49 |

|   |      | 3.3.4   | Le dépôt                                       | , , | 49 |

|   |      | 3.3.5   | Le dopage                                      |     | 49 |

|   | 3.4  | Les m   | odules                                         | . , | 50 |

|   |      | 3 4 1   | Le module d'isolation                          |     | 51 |

|    |       | 3.4.2                                     | Le module de dispositif                               |    |     | +   |    |   |     |      |     |   | 53  |

|----|-------|-------------------------------------------|-------------------------------------------------------|----|-----|-----|----|---|-----|------|-----|---|-----|

|    |       | 3.4.3                                     | Le module de connexion                                |    |     |     |    |   |     |      |     |   | 55  |

|    | 3.5   | Les tec                                   | nnologies                                             |    |     |     |    |   |     |      |     |   | 56  |

|    | 3.6   | Les tech                                  | hnologies CMOS bulk                                   |    |     | 4.5 |    |   |     | 11.2 |     | 4 | 57  |

|    |       | 3.6.1                                     | Le thyristor parasite                                 |    |     |     |    |   |     |      |     |   | 57  |

|    | 3.7   | Les teci                                  | nnologies CMOS épitaxiées                             |    |     |     |    |   |     |      |     |   | 60  |

|    | 3.8   |                                           | hnologies CMOS SOI                                    |    |     |     |    |   |     |      |     |   | 61  |

|    | 3.9   |                                           | rosystèmes intégrés                                   |    |     |     |    |   |     |      |     |   | 62  |

|    | 25.70 |                                           | Microsystèmes compatibles avec des filières standards |    |     |     |    |   |     |      |     |   | 62  |

|    |       |                                           | Microsystèmes spatiaux                                |    |     |     |    |   |     |      |     |   | 65  |

| 4  | Ray   | onnem                                     | ent et matière                                        |    |     |     |    |   |     |      |     |   | 67  |

|    | 4.1   | Introdu                                   | ction                                                 |    |     |     |    |   |     |      |     | 4 | 67  |

|    | 4.2   | Mécani                                    | smes fondamentaux                                     |    |     |     |    |   |     |      |     |   | 68  |

|    |       |                                           | Interaction de photons                                |    |     |     |    |   |     |      |     |   | 68  |

|    |       |                                           | Interaction de particules chargées                    |    |     |     |    |   |     |      |     |   | 69  |

|    |       | 200000000000000000000000000000000000000   | Interaction de neutrons                               |    |     |     |    |   |     |      |     |   | 71  |

|    |       |                                           | Terminologie et unités                                |    |     |     |    |   |     |      |     |   | 72  |

|    |       |                                           | Mécanismes de transfert d'énergie                     |    |     |     |    |   |     |      |     |   | 72  |

|    | 4.3   |                                           | ur le silicium                                        |    |     |     |    |   |     |      |     |   | 76  |

|    | 1.0   |                                           | Dislocation                                           |    |     |     |    |   |     |      |     |   | 76  |

|    |       |                                           | Ionisation                                            |    |     |     |    |   |     |      |     |   | 77  |

|    | 4.4   |                                           | mements radiatifs                                     |    |     |     |    |   |     |      |     |   | 86  |

|    | 4.4   |                                           |                                                       |    |     |     |    |   |     |      |     |   | 86  |

|    |       |                                           | L'espace                                              |    |     |     |    |   |     |      |     |   | 90  |

|    |       | 4.4.2                                     | Autres environnements radiatifs                       |    |     | *   | *) | • |     |      |     | * | 90  |

| 11 | D     | urcisse                                   | ment                                                  |    |     |     |    |   |     |      |     |   | 93  |

| -  |       |                                           |                                                       |    |     |     |    |   |     |      |     |   | 95  |

| 5  |       |                                           | ent des circuits intégrés                             |    |     |     |    |   |     |      |     |   |     |

|    | 5.1   | > 1 - 1 - 0 - 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | ction                                                 |    |     |     |    |   |     |      |     |   |     |

|    | 5.2   |                                           | le la dose cumulée                                    |    |     |     |    |   |     |      |     |   |     |

|    |       |                                           | L'isolation LOCOS                                     |    |     |     |    |   |     |      |     |   |     |

|    |       |                                           | Transistors MOS                                       |    |     |     |    |   |     |      |     |   |     |

|    |       |                                           | Éléments passifs                                      |    |     |     |    |   |     |      |     |   |     |

|    |       |                                           | Jonctions p-n planaires                               |    |     |     |    |   |     |      |     |   |     |

|    | 5.3   |                                           | ransitoires                                           |    |     |     |    |   |     |      |     |   |     |

|    |       |                                           | Verrouillages de courant                              |    |     |     |    |   |     |      |     |   |     |

|    |       |                                           | Aléas                                                 |    |     |     |    |   |     |      |     |   |     |

|    |       | 5.3.3                                     | Autres effets transitoires                            |    |     | ٠   | ٠  |   |     |      |     | * | 107 |

|    | 5.4   | L'évalu                                   | ation de la sensibilité                               |    |     |     |    |   |     |      |     |   | 109 |

|    |       |                                           | Dose totale                                           |    |     |     |    |   |     |      |     |   |     |

|    |       | 5.4.2                                     | Événements singuliers                                 |    | . , | +   |    |   |     |      | . + | 7 | 112 |

|    | 5.5   | Durciss                                   | ement des circuits et des systèmes                    |    |     |     |    |   |     |      |     |   | 113 |

|    |       | 5.5.1                                     | Le durcissement par rapport à la dose cumulée         |    |     |     |    |   |     |      |     |   | 116 |

|    |       | 5.5.2                                     | Le durcissement par rapport aux verrouillages de cour | an | t   |     |    |   | . , |      | ,   | , | 124 |

|    |       | 5.5.3                                     | Durcissement des microsystèmes                        |    |     |     |    |   |     |      |     |   | 125 |

| 6 | Car            | actéris                                 | ation de la technologie 131                  |  |  |  |  |  |  |  |

|---|----------------|-----------------------------------------|----------------------------------------------|--|--|--|--|--|--|--|

|   | 6.1            | Introd                                  | uction                                       |  |  |  |  |  |  |  |

|   | 6.2            | Descri                                  | ption générale de la technologie             |  |  |  |  |  |  |  |

|   | 6.3            | Évalua                                  | ation théorique de la réponse à la radiation |  |  |  |  |  |  |  |

|   |                | 6.3.1                                   | L'isolation LOCOS                            |  |  |  |  |  |  |  |

|   |                | 6.3.2                                   | Les transistors                              |  |  |  |  |  |  |  |

|   |                | 6.3.3                                   | Les diodes planaires                         |  |  |  |  |  |  |  |

|   | 6.4            |                                         | érisation expérimentale                      |  |  |  |  |  |  |  |

|   | 200            | 6.4.1                                   | Moyens                                       |  |  |  |  |  |  |  |

|   |                | 6.4.2                                   | Méthodologie                                 |  |  |  |  |  |  |  |

|   |                | 6.4.3                                   | Mesures                                      |  |  |  |  |  |  |  |

|   |                | 6.4.4                                   | Résultats                                    |  |  |  |  |  |  |  |

|   | 6.5            | 170000000000000000000000000000000000000 | vse des données                              |  |  |  |  |  |  |  |

|   | 0.0            | 6.5.1                                   | Transistors                                  |  |  |  |  |  |  |  |

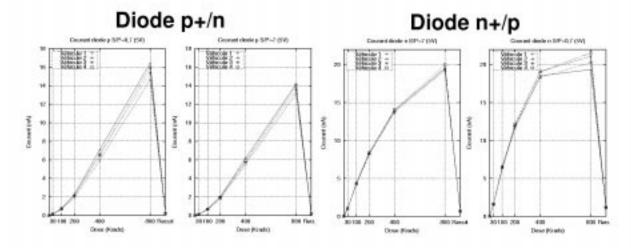

|   |                | 6.5.2                                   | Diodes                                       |  |  |  |  |  |  |  |

|   |                | 6.5.3                                   | FOXFETs                                      |  |  |  |  |  |  |  |

|   | 6.6            |                                         | ision                                        |  |  |  |  |  |  |  |

|   | 0.0            | Conci                                   | ision                                        |  |  |  |  |  |  |  |

| 7 | Mise en oeuvre |                                         |                                              |  |  |  |  |  |  |  |

|   | 7.1            | Introd                                  | uction                                       |  |  |  |  |  |  |  |

|   | 7.2            | La lec                                  | ture du signal de thermopiles                |  |  |  |  |  |  |  |

|   |                | 7.2.1                                   | Commutation                                  |  |  |  |  |  |  |  |

|   |                | 7.2.2                                   | Amplification                                |  |  |  |  |  |  |  |

|   |                | 7.2.3                                   | L'architecture retenue                       |  |  |  |  |  |  |  |

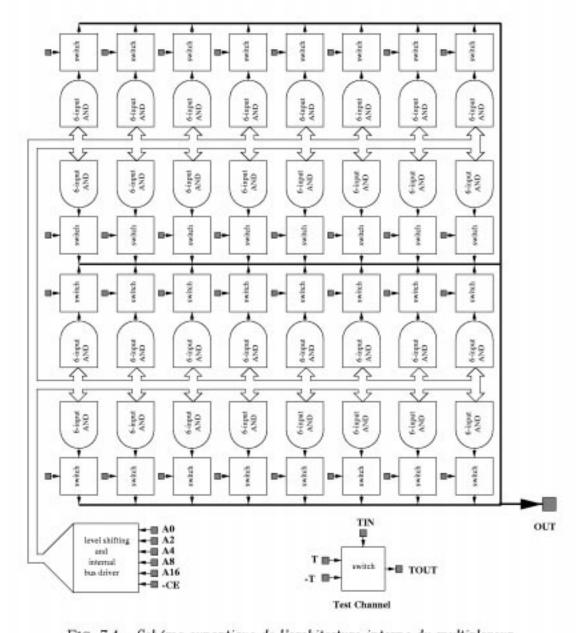

|   | 7.3            |                                         | ltiplexeur analogique                        |  |  |  |  |  |  |  |

|   |                | 7.3.1                                   | Circuit                                      |  |  |  |  |  |  |  |

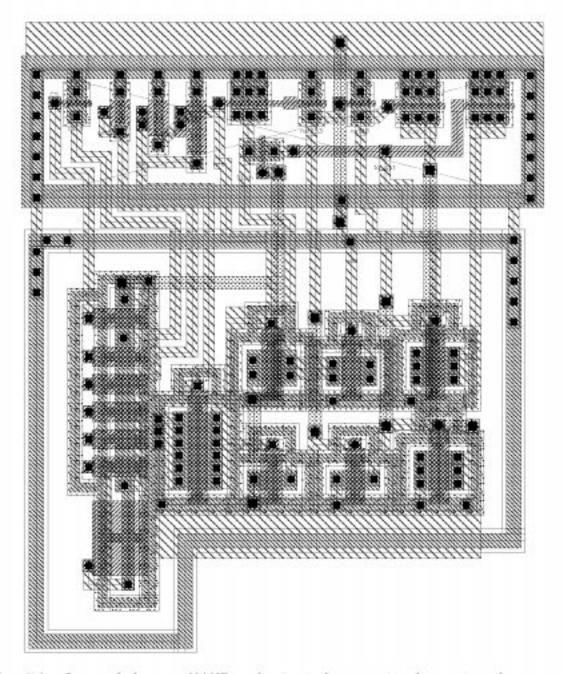

|   |                | 7.3.2                                   | Layout                                       |  |  |  |  |  |  |  |

|   |                | 7.3.3                                   | Mesures                                      |  |  |  |  |  |  |  |

|   |                | 7.3.4                                   | Essais sous le rayonnement                   |  |  |  |  |  |  |  |

|   | 7.4            | 10.333330                               | isions                                       |  |  |  |  |  |  |  |

|   |                | Concil                                  |                                              |  |  |  |  |  |  |  |

| C | onclu          | ision G                                 | énérale 185                                  |  |  |  |  |  |  |  |

# Table des figures

| 2.1  | La résistivité $\rho$                                                                                     |

|------|-----------------------------------------------------------------------------------------------------------|

| 2.2  | Diagramme bi-dimensionel des bandes d'énergie                                                             |

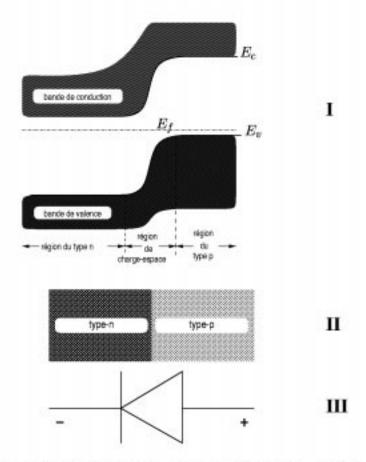

| 2.3  | Diagramme des bandes d'énergie d'une jonction p-n                                                         |

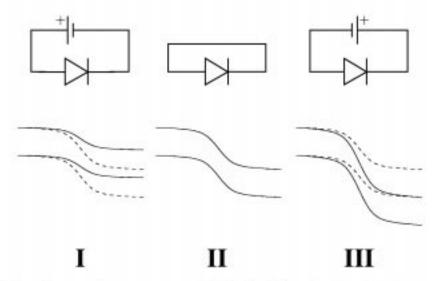

| 2.4  | Déplacement des bandes d'une jonction p-n                                                                 |

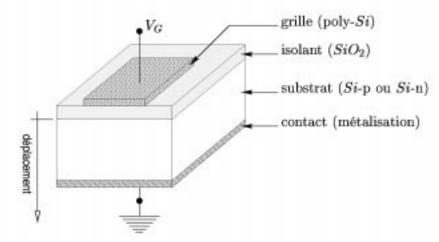

| 2.5  | Vue en coupe d'une structure MOS                                                                          |

| 2.6  | Diagramme de bandes d'énergie d'une structure MOS                                                         |

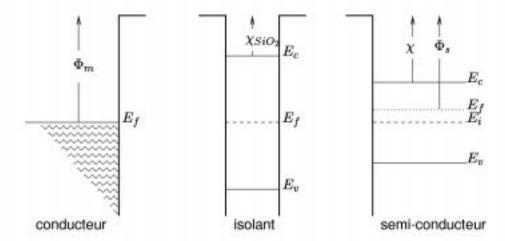

| 2.7  | Bandes plates, accumulation et déplétion                                                                  |

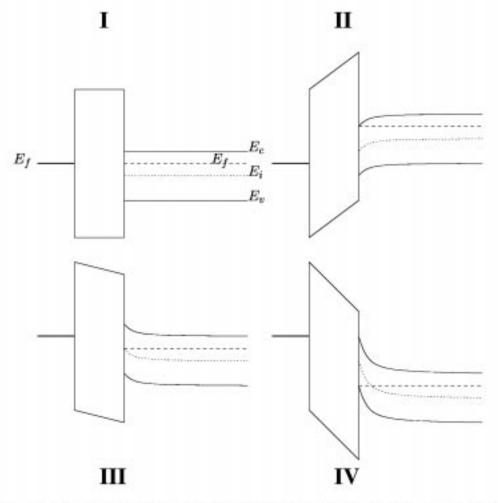

| 2.8  | Distribution des charges à l'intérieur d'une structure MOS                                                |

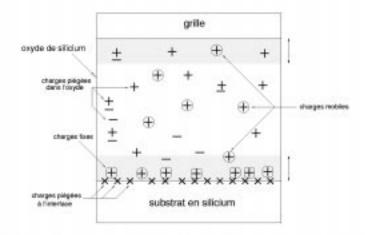

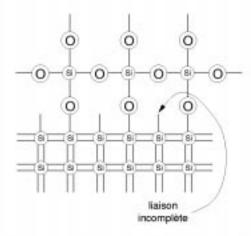

| 2.9  | Liaisons atomiques incomplètes à l'interface $Si-SiO_2$                                                   |

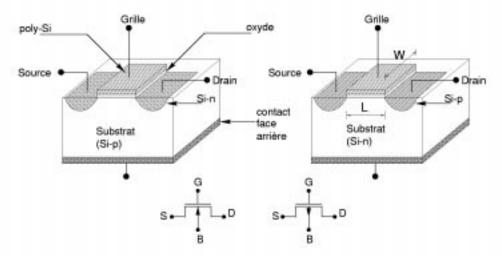

| 2.10 | Transistors MOS à enrichissement du type n et p                                                           |

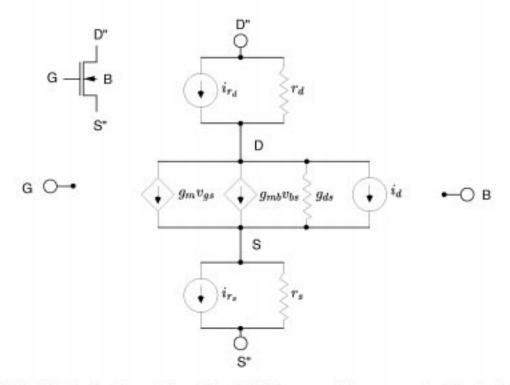

| 2.11 | Modèle électrique du MOS en petits signaux                                                                |

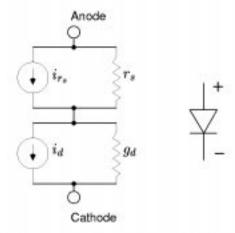

| 2.12 | Modèle électrique du bruit de la diode                                                                    |

| 2.13 | Modèle électrique du bruit du MOS                                                                         |

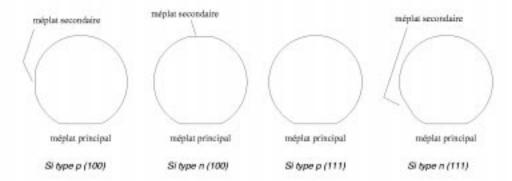

| 3.1  | Types de plaquette et ses méplats                                                                         |

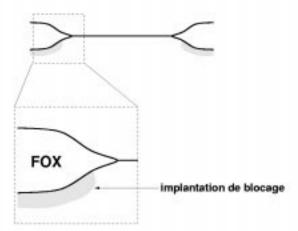

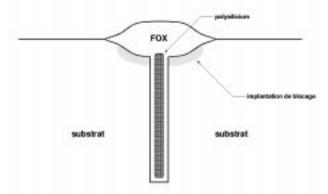

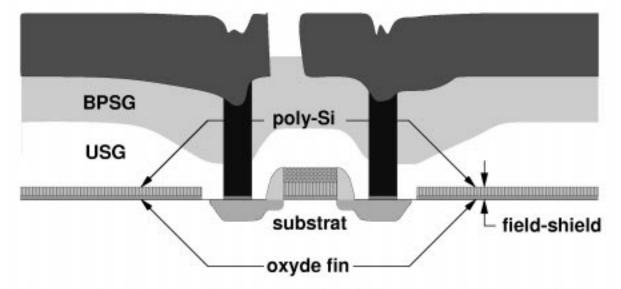

| 3.2  | Structure en bec d'oiseau aux bords de l'isolation LOCOS                                                  |

| 3.3  | Isolation par tranchée                                                                                    |

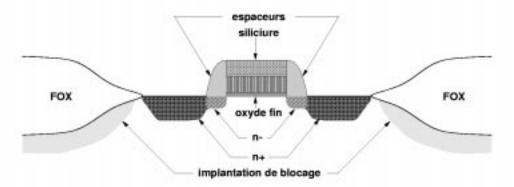

| 3.4  | Profil d'un transistor NMOS avec un drain graduel (LDD) 54                                                |

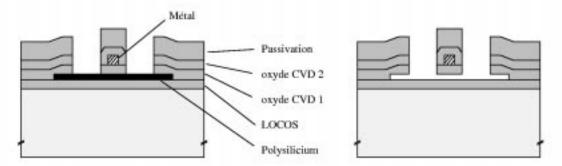

| 3.5  | Vue en coupe schématique de la tranche après la formation des premières in-                               |

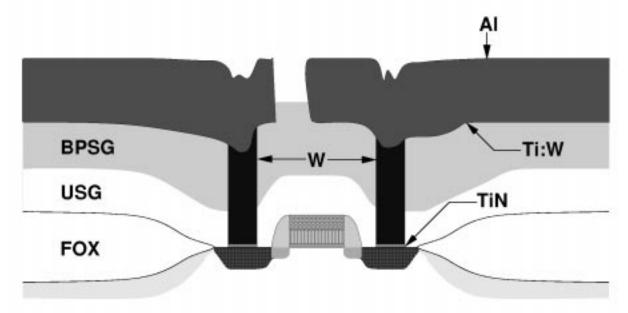

|      | terconnexions en métal                                                                                    |

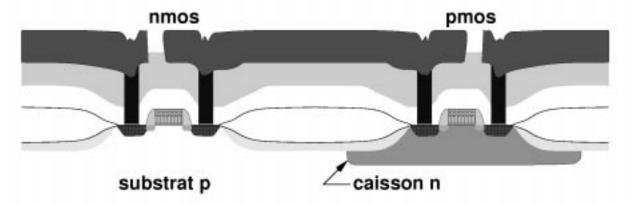

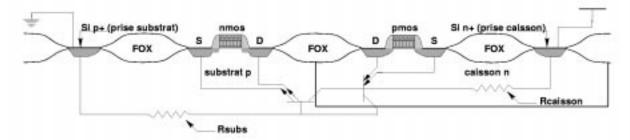

| 3.6  | Vue en coupe schématique d'un inverseur dans un procédé CMOS en substrat<br>massif avec un caisson simple |

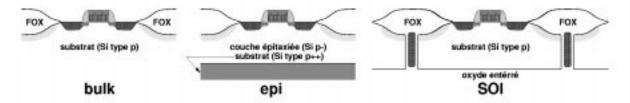

| 3.7  | Vue en coupe schématique des technologies bulk, épitaxiée et SOI (SIMOX) 57                               |

| 3.8  | Vue en coupe schématique du thyristor parasite                                                            |

| 3.9  | Circuit équivalent du thyristor                                                                           |

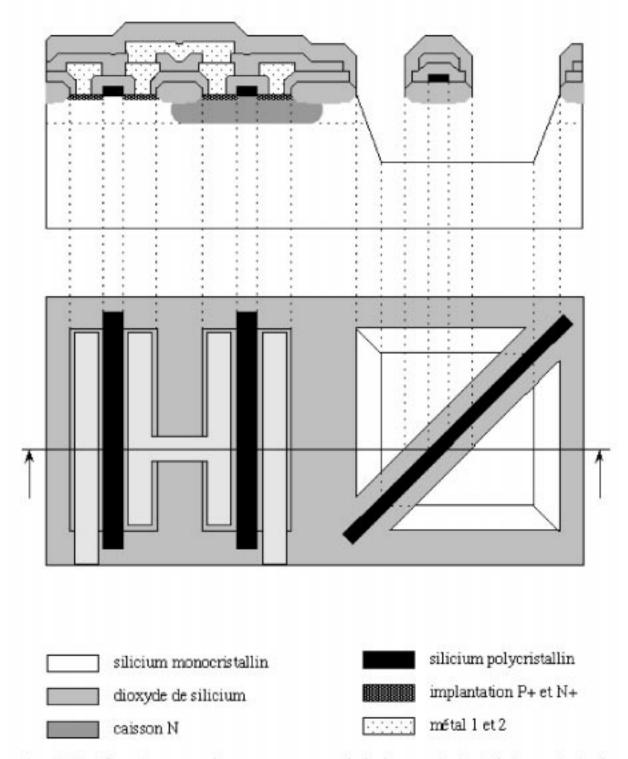

| 3.10 | - 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1.                                                                  |

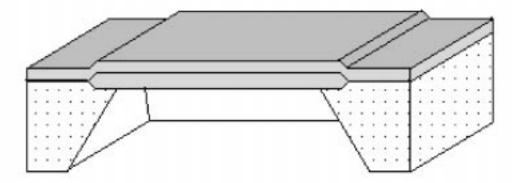

| 3.11 | Type de structure obtenue par la gravure de la face arrière                                               |

|      | Exemple de micro-usinage en surface                                                                       |

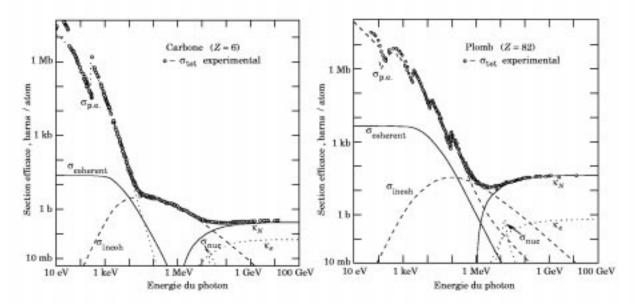

| 4.1  | Section efficace de photons                                                                               |

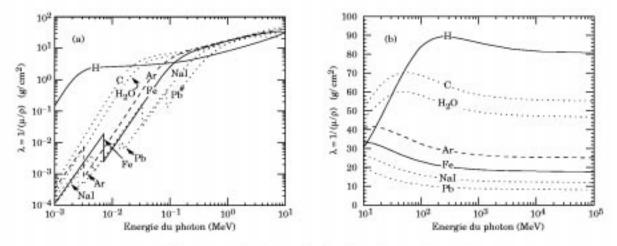

| 4.2  | Le parcours libre moyen des photons                                                                       |

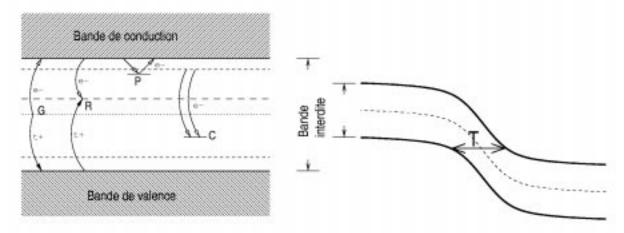

| 4.3  | Processus provoqués par les états énergétiques                                                            |

| 4.4  | Quatre jonctions p-n implantées, polarisées en inverse                                                    |

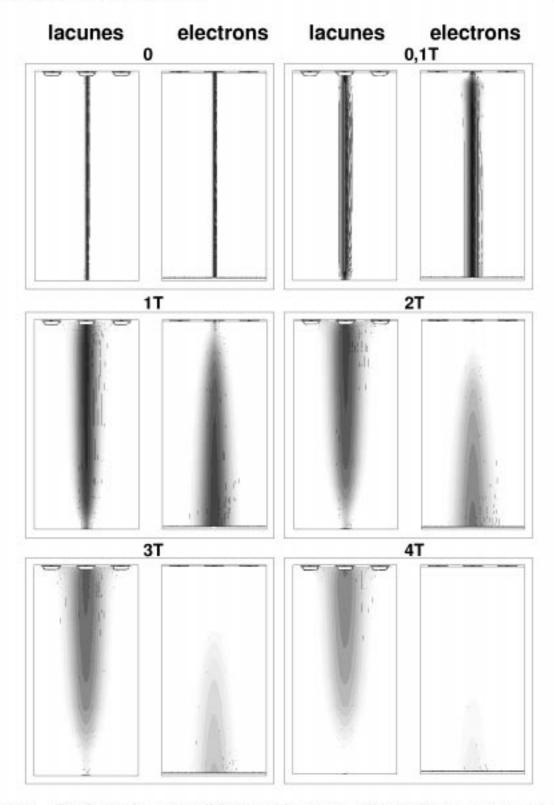

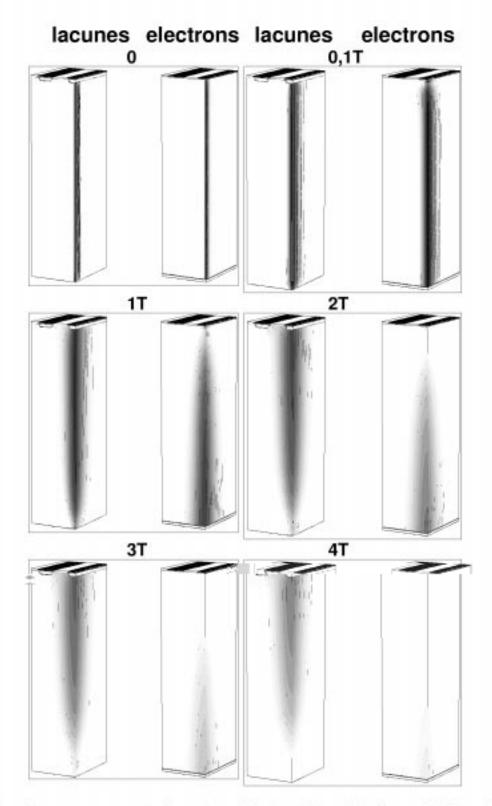

| 4.5  | Simulation du passage d'une particule                                                                     |

| 4.6  | Vue en coupe à trois dimensions de la simulation                                                          |

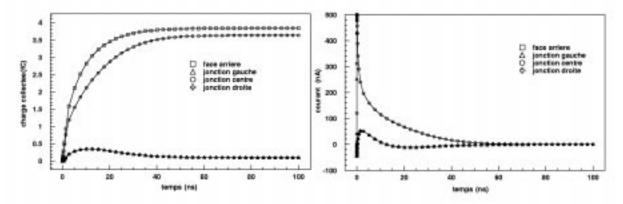

| 4.7  | L'évolution du courant et de la collecte de charge                                                        |

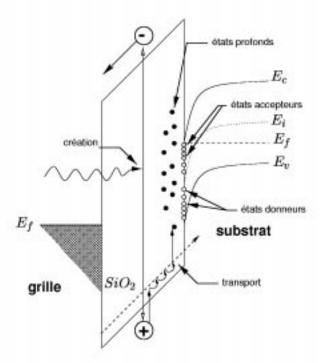

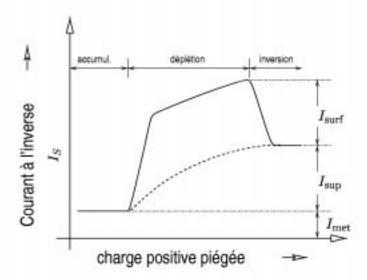

| 5.1  | Création, localisation et comportement d'états piégeurs                                          |

|------|--------------------------------------------------------------------------------------------------|

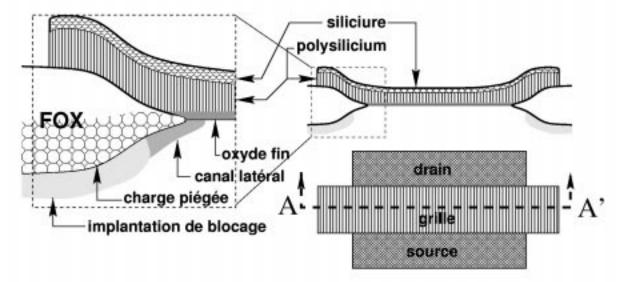

| 5.2  | Canaux latéraux sous le bec d'oiseau                                                             |

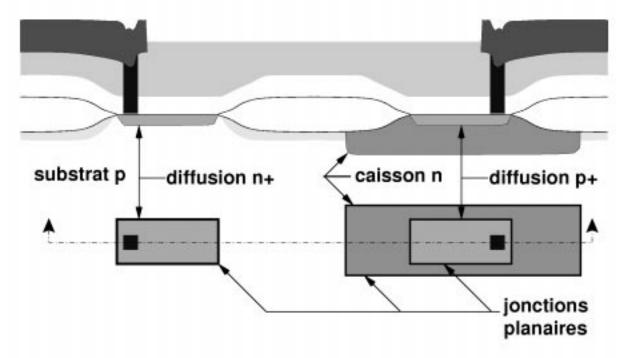

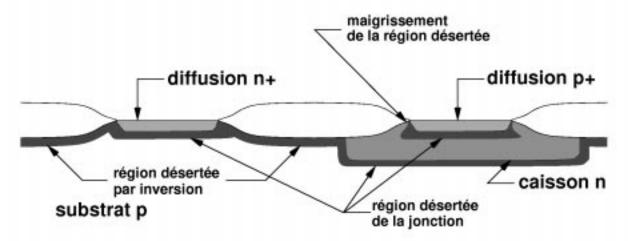

| 5.3  | Jonctions p-n dans une technologie CMOS bulk                                                     |

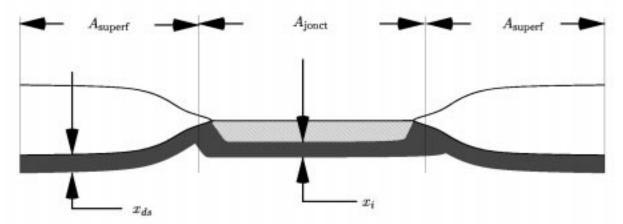

| 5.4  | Jonctions p-n planaires élargies                                                                 |

| 5.5  | Coupe schématique d'une jonction p-n planaire                                                    |

| 5.6  | Courant de génération-recombinaison en inverse                                                   |

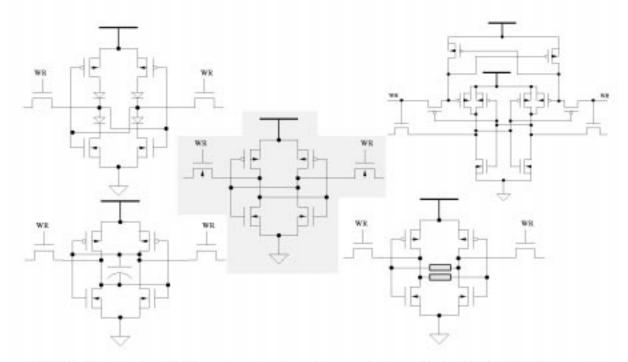

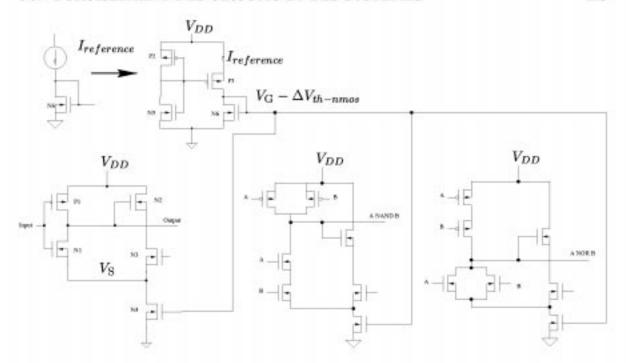

| 5.7  | Mémoires estatiques durcies                                                                      |

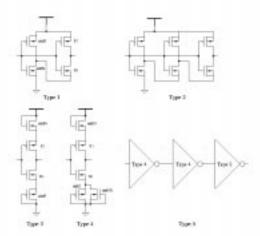

| 5.8  | Isolation par blindage                                                                           |

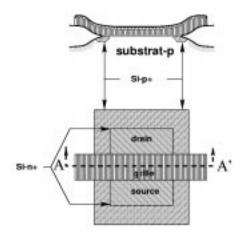

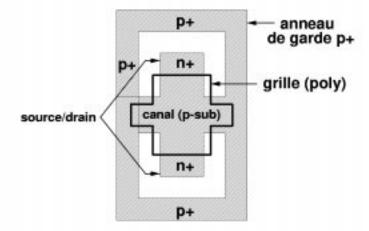

| 5.9  | Anneau de garde pour NMOS durci                                                                  |

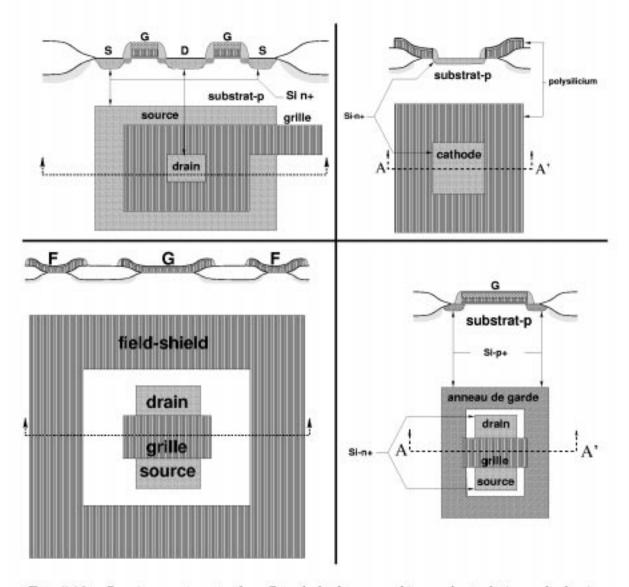

| 5.10 | Layouts durcis                                                                                   |

| 5.11 | Polarisation du substrat                                                                         |

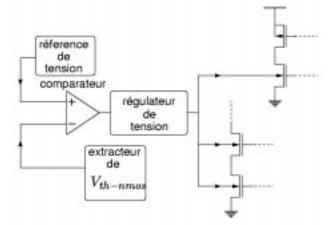

| 5.12 | Durcissement de la marge de bruit d'entrée                                                       |

| 5.13 | Durcissement de la courbe de transfert                                                           |

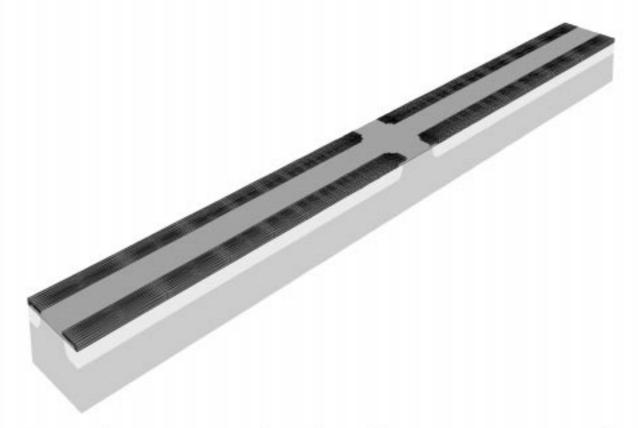

| 5.14 | Vue en coupe droite d'un thermocouple sur une poutre                                             |

|      |                                                                                                  |

| 6.1  | Durcissement du transistor NMOS de la technologie AMS CAE par l'utilisation                      |

|      | d'un anneau de garde                                                                             |

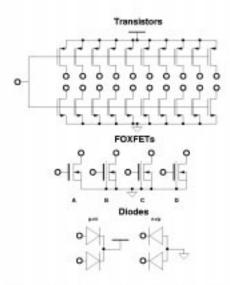

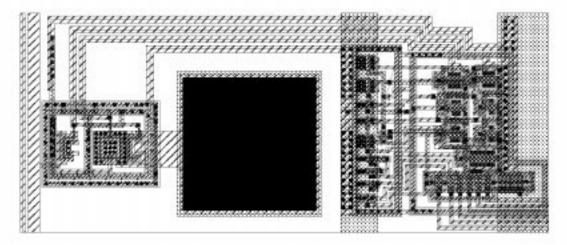

| 6.2  | Dispositifs disponibles dans le véhicule de test                                                 |

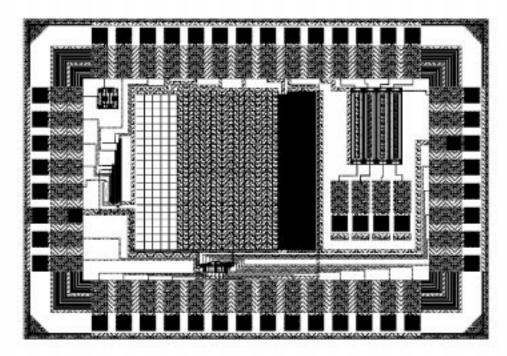

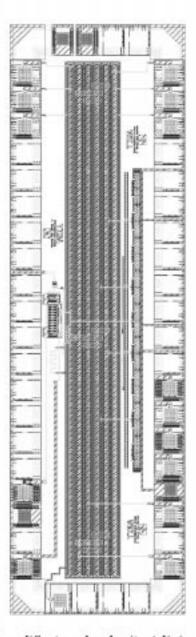

| 6.3  | Layout du véhicule de test                                                                       |

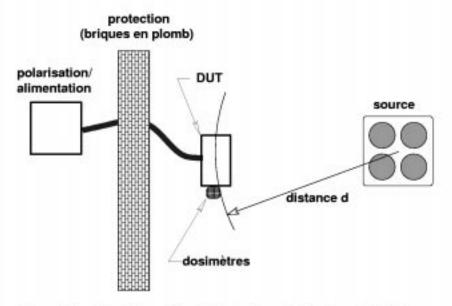

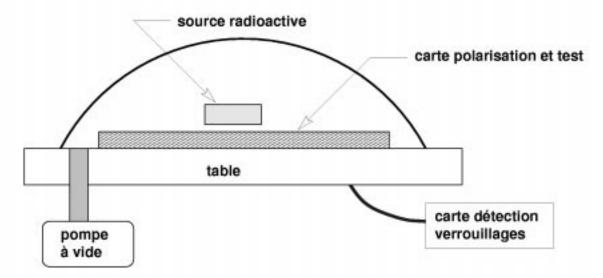

| 6.4  | Conditions d'irradiation du véhicule de test à Saclay                                            |

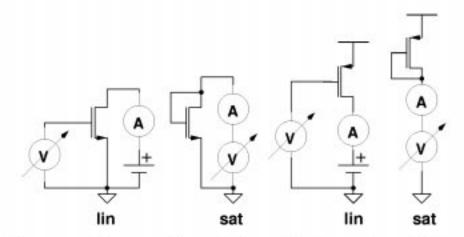

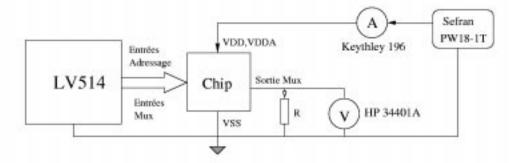

| 6.5  | Montage pour la mesure des transistors MOS                                                       |

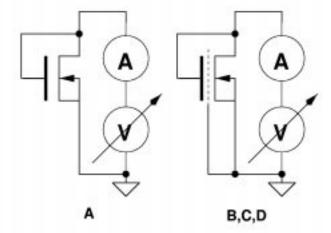

| 6.6  | Montage pour la mesure des FOXFETs                                                               |

| 6.7  | Montage pour la mesure des diodes                                                                |

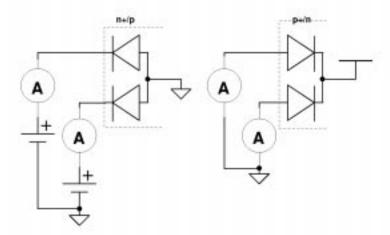

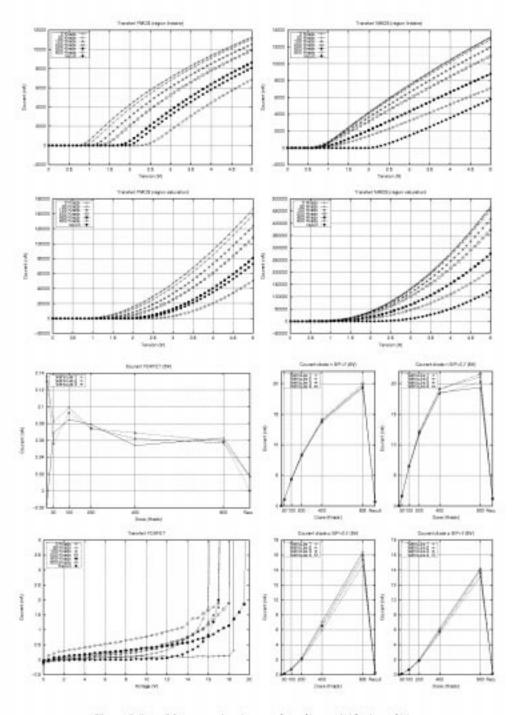

| 6.8  | Mesures typiques des dispositifs irradiés                                                        |

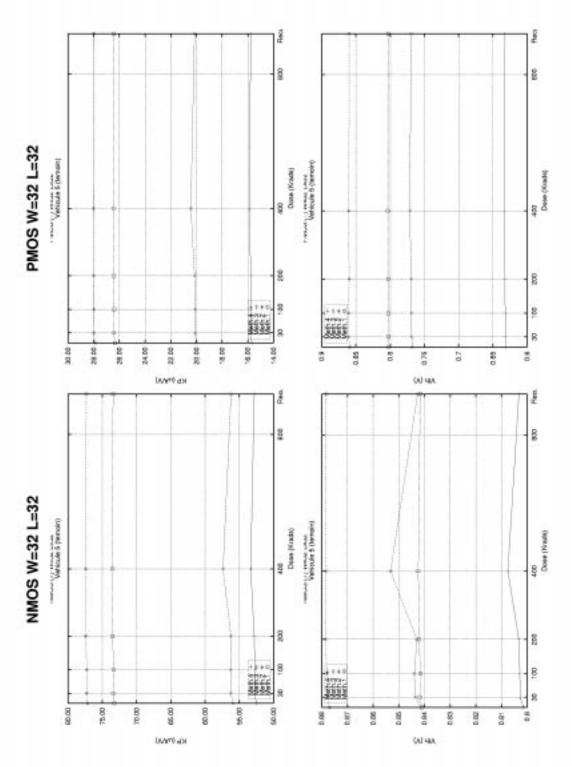

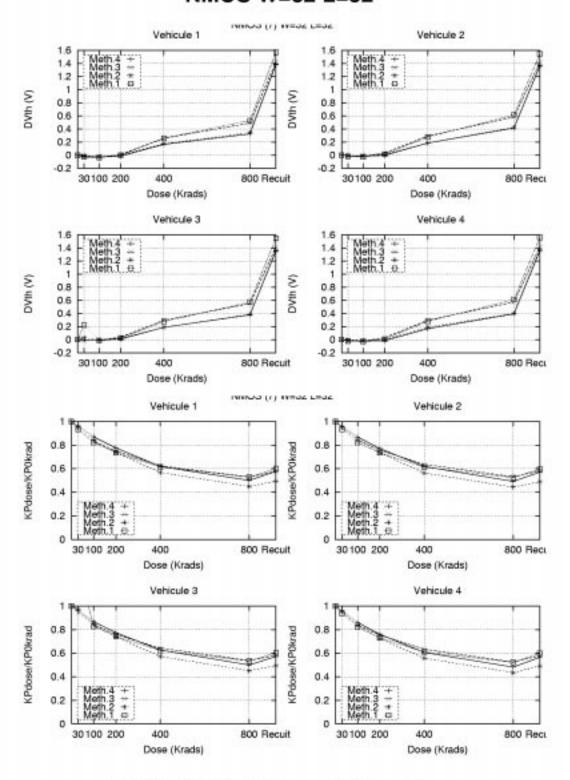

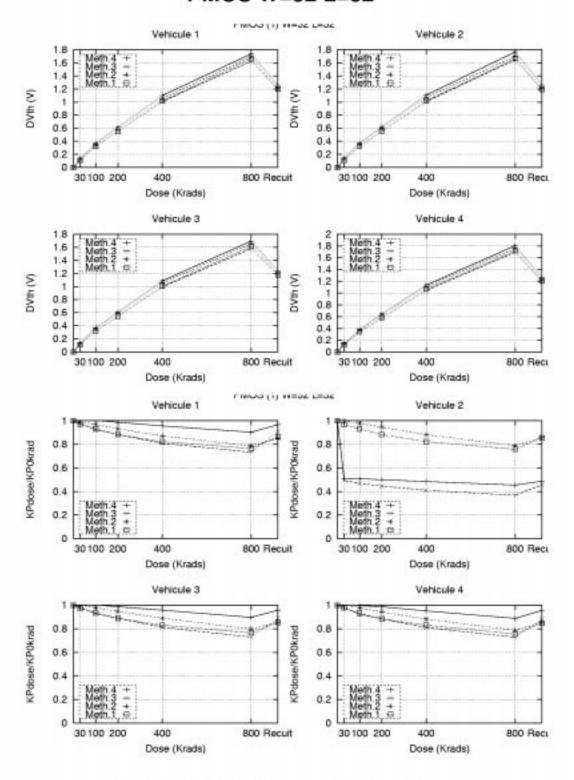

| 6.9  | Transconductance KP et tension de seuil $V_{th}$ des transistors                                 |

|      | Evolution de $V_{th-nmos}$ et $KP_{II}$ avec la dose                                             |

|      | Évolution de $V_{th-pmos}$ et KPp avec la dose                                                   |

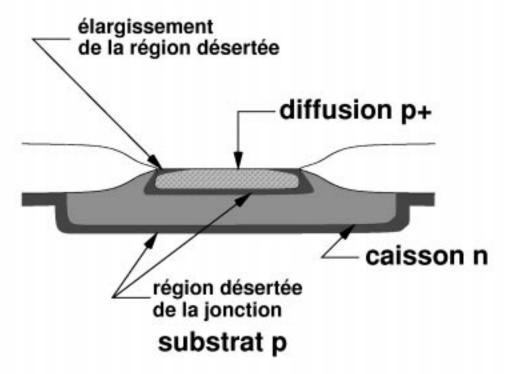

|      | Mécanisme d'élargissement de la région désertée                                                  |

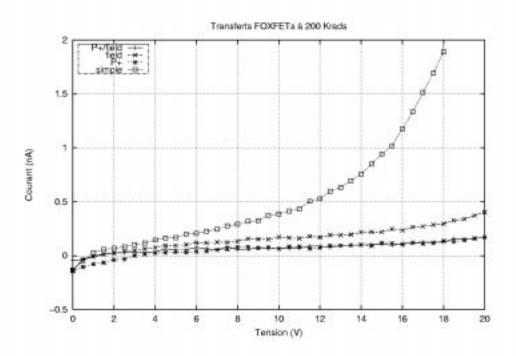

|      | Transfert des FOXFETs à 200 Krads                                                                |

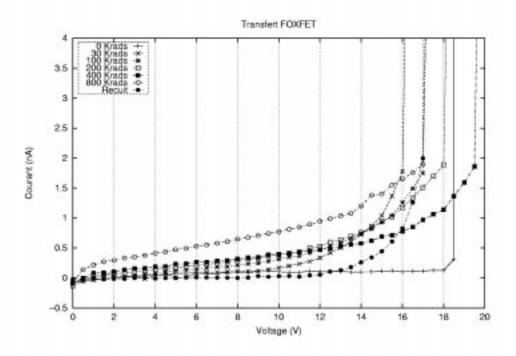

|      | Évolution du courant du FOXFET simple avec l'irradiation                                         |

| 0.10 | Evolution du courant du FOAFET simple avec l'irradiation                                         |

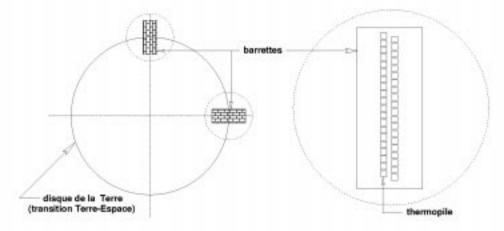

| 7.1  | Disposition des barrettes de thermopiles dans un capteur                                         |

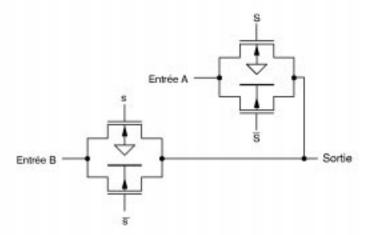

| 7.2  | Bloc de commutation du signal dans un multiplexeur                                               |

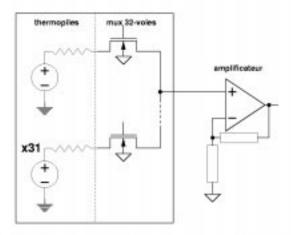

| 7.3  | Architecture de traitement du signal des thermopiles                                             |

| 7.4  | Schéma synoptique de l'architecture interne du multiplexeur                                      |

| 7.5  | Layout du bloc de commutation                                                                    |

| 7.6  | Layout du circuit de commande                                                                    |

| 7.7  | Layout du bloc de commutation du signal                                                          |

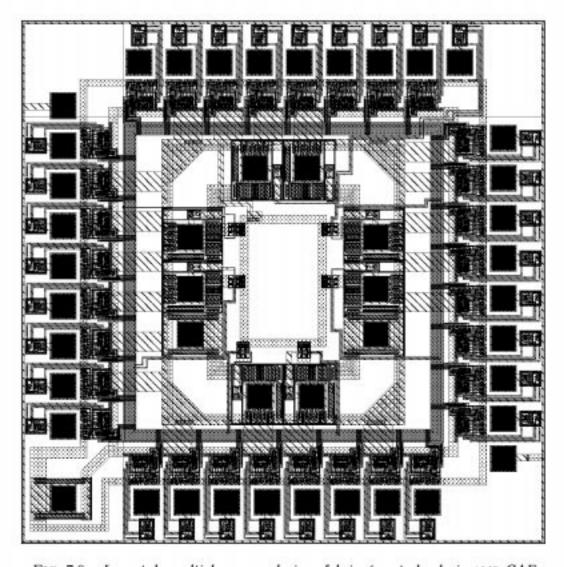

| 7.8  | Layout du multiplexeur analogique fabriqué en technologie AMS CAE 175                            |

| 7.9  | Montage pour le test de la fonctionnalité du multiplexeur                                        |

|      | Installations et montage pour l'irradiation des multiplexeurs dans l'irradiateur                 |

|      | PAGURE                                                                                           |

| 7.11 | Évolution des seuils logiques de commutation $V_{\rm IL}$ et $V_{\rm IH}$ avec l'irradiation 178 |

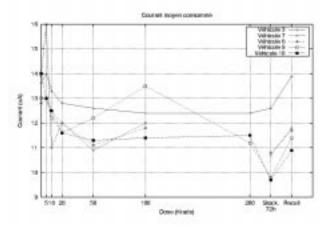

|      | Évolution de la consommation du multiplexeur avec l'irradiation 179                              |

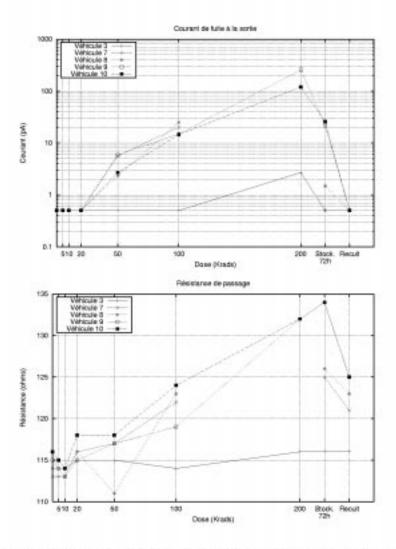

|      | Évolution du courant de fuite et de la résistance                                                |

|      | Montage pour l'exposition du multiplexeur au $^{252}Cf$                                          |

|      |                                                                                                  |

| TTA | DI | 1.7 | DEC   | DI      | 177 | JRES   |

|-----|----|-----|-------|---------|-----|--------|

| 1.4 | BI | 100 | LIE 3 | $r_{I}$ | Lri | 111 PM |

7.15 Layout de l'amplificateur bas bruit réalisé en technologie AMS CAE. . . . . . . . 183

# Liste des tableaux

| 2.1 | Relation entre le potentiel à la surface et la concentration de porteurs libres 29 |

|-----|------------------------------------------------------------------------------------|

| 2.2 | Paramètres du modèle LEVEL1 du simulateur SPICE                                    |

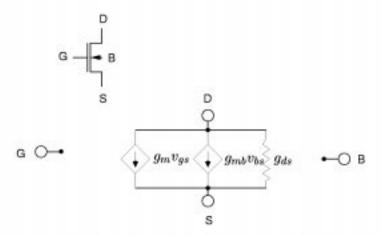

| 2.3 | Modèle électrique du MOS en petits signaux                                         |

| 4.1 | Constantes d'interaction                                                           |

| 4.2 | Fluences équivalentes                                                              |

| 4.3 | Flux des particules dans l'espace et ses modèles                                   |

| 5.1 | Les ions disponibles dans l'accélérateur tandem de L'Institut de Physique Nu-      |

|     | cléaire d'Orsay                                                                    |

| 5.2 | Marges de sécurité prises dans le passé pour des véhicules spatiaux                |

| 5.3 | Sources de rayonnement pour l'analyse du risque de SEE                             |

| 5.4 | Quelques filières de fabrication CMOS durcies disponibles aujourd'hui 118          |

| 6.1 | Les principales caractéristiques de la technologie AMS CAE                         |

| 6.2 | Les principales caractéristiques des dispositifs du véhicule de test               |

| 6.3 | Conditions d'irradiation des véhicules de test                                     |

| 6.4 | Conditions de polarisation des dispositifs durant l'irradiation                    |

| 6.5 | Courants de fuite typiques des différents diodes                                   |

| 6.6 | Tolérances aux rayonnements pour plusieurs technologies                            |

| 7.1 | Conditions d'irradiation des multiplexeurs dans l'irradiateur Pagure 177           |

| 7.2 | Conditions d'exposition du multiplexeur au $^{252}Cf$                              |

## Chapitre 1

## Introduction

CETTE THÈSE a été entreprise avec le dé-sir d'apporter un gain de compétitivité significatif dans un domaine historiquement stratégique, l'exploration de l'espace. Ce domaine est à cet instant en pleine effervescence, du fait de la déréglementation des télécommunications au niveau mondial et à l'explosion de l'INTERNET. Le fait que l'objectif du travail exposé soit technique-scientifique n'enlève pas l'intérêt d'une revue rapide des courants historiques dans le marché de systèmes électroniques spatiaux. Cette revue du passé et du présent exposera le contexte et les prémisses de la décision d'investir des resources considérables dans la voie des microsystèmes pour l'espace basés sur des technologies de produits «grand public».

T HIS THESIS has been undertaken with the objective of contributing to a competitive advantage in a historically strategic domain, the exploration of space. This domain experiences now a great deal of excitement, because of the global deregulation of telecomunications and the explosion of the Internet. The fact that the work exposed here is technical-scientific does not withdraw the interest of a short review of the historical currents in the market of space electronics. This review of the past and present situation will expose the context and premises behind the decision to invest considerable resources in the development of space microsystems using consumer products technologies.

### 1.1 Des bombes-A au téléphone portable From A-bombs to portable phones

L'explosion nucléaire américaine Starfish, à haute altitude, et la panne ultérieure du satellite de communications civil Telstar ont montré, en 1962, la vulnérabilité à la radiation de l'électronique spatiale de l'époque. Cet événement a inauguré la recherche et le développement des techniques de durcissement des composants électroniques intégrés modernes[1, p.47]. La plus grande partie de cet effort a été menée pour des applications de défense.

À la fin des années 60, la France fût l'un des premiers pays a entamer des reThe high altitude Starfish U.S. nuclear explosion, and the subsequent failure of the Telstar civilian telecommunications satellite starkly demonstrated in 1962 the vulnerability to radiation of the space electronics of the time. This event inaugurated the research and development of radiation hardening techniques for modern electronic components[1, p.47]. This activity has been carried out mostly for the defense sector.

At the end of the 60s, France was one of the first countries to conduct research activcherches dans ce sens, avec les travaux du CEA-DAM/Grenoble[2, p.4]. Les travaux de recherche, en France et à l'étranger, ont débouché sur des filières technologiques spécifiques pour fabriquer des composants durcis. Ainsi des familles de composants ont été développées et commercialisées selon les besoins des programmes militaires.

Depuis ce début et jusqu'à un passé récent le marché d'électronique spatiale civil était subordonné au marché militaire. Cette relation a largement façonnée l'architecture des engins spatiaux commerciaux, sans pour autant représenter un inconvénient majeur. Ces satellites ont ainsi pu être construits à des prix convenables au marché des télécommunications. L'évolution de ce marché, l'explosion de l'industrie des semiconducteurs et le déclin de l'industrie de l'armement ont brisé cet équilibre, qui a néanmoins duré plusieurs décennies.

La disparition et l'obsolescence des filières spécifiques ont créé une situation nouvelle pour le secteur de l'espace. L'adaptation à les nouvelles conditions a d'ailleurs déjà commencé, tant pour le marché militaire que pour le marché civil. Cependant, les stratégies diffèrent selon les besoins et les spécificités de chaque marché. Il est utile d'identifier les points de convergence des deux domaines.

#### Les besoins militaires et civils The military and civilian requirements

Durant plus de 30 ans, le marché militaire a eu un poids suffisant pour que les fabricants des semiconducteurs conçoivent, développent, produisent et commercialisent des composants qui prenaient en compte leurs besoins de tenue aux rayonnements. Pendant cette période, le marché civil était relativement peu important, et s'approvisionnait surtout des produits militaires «bas de gamme» pour ses composants durcis. Ces produits étaient (et le sont encore) conçus pour répondre aux contraintes spécifiques des applications militaires, outre ities in this area, with the endeavors of the CEA-DAM at Grenoble[2, p.4]. This continued effort has yielded fabrication technologies specially suited to the manufacturing of hardened components, both within France and abroad. In this manner, whole families of components have been developed and commercialized in order to serve the needs of the military programs.

From this early beginning and until the recent past, the civilian space electronics market was a fringe area of the much larger military market. This relationship has shaped the architecture of most commercial spacecrafts, without any apparent ill effects. In this way the satellites could be built at a cost within reach of the telecom market. The evolution of this market, the explosive growth of the semiconductor industry, and the decline of the arms industry have shattered this balance, which had nonetheless lasted for several decades.

The disappearance and the obsolescence of the custom-developed technologies have created a new environnement in the space sector. The adaptation to the new situation has already started, both in the military and the civilian side. At the same time, each sector follows a somewhat different strategy, to address their specific needs. It's an useful exercise to identify the common ground of the two fields.

For more than 30 years the military market size was such that the semiconductor companies researched, developed, manufactured and commercialized a wide range of components that were intended to resist radiation. During this period the civilian market was relatively unimportant, and its needs for radiation resistant components were met by the "low-end" range of the military products. These products were (and still are) built to meet some very specific requirements, in addition to radiation hardness. l'immunité aux rayonnements.

La spécificité du marché militaire se traduit principalement par les points suivants[2, p.30]:

- un besoin de fiabilité, y compris en environnement sévère;

- un besoin d'achat en très faibles quantités (parfois moins d'un millier de pièces);

- un besoin de pérennité (10 ans au moins);

- une absence de préoccupations par rapport à un coût élevé.

Ces spécificités étaient respectées par les fabricants de composants de manière habituelle. En général, les fabricants proposaient des produits aux deux marchés. La réduction des budgets de défense, l'explosion du marché civil de l'électronique, et l'augmentation vertigineuse des investissements nécessaires pour industrialiser les nouvelles technologies ont radicalement changé le scénario. Désormais, la totalité de grands fabricants de semiconducteurs n'investit plus seulement pour satisfaire le marché militaire, estimé à représenter moins de 0,5 % du marché mondiale de semiconducteurs à la fin de la décennie.

Par contre, la nécessité de composants capables d'opérer sous la contrainte du rayonnement ne cesse de s'accroître, à cause du poids grandissant du marché civil des télécommunications. Les caractéristiques des composants dont les équipementiers civils ont besoin sont aussi en train de changer profondément. Cette évolution est menée par une concurrence sans relâche qui oblige une maîtrise des coûts de production couplée à une innovation continue. On assiste alors à une divergence entre les besoins militaires et civils. Ce qui pilote le progrès technologique aujourd'hui est le secteur civil, notamment le marché des télécommunications. The specific requirements of the military market can be summarized as follows[2, p.30].

- High level of reliability, even in aggressive environments.

- Purchasing in very small quantities (maybe less than 1,000).

- Product longevity (10 years at least).

- Lack of concerns with regard to a high unit cost.

These specific requirements were routinely met by the component manufacturers, which generally served both markets. The reduction of the defense budgets, the explosive growth of the electronics civilian market and the vertiginous increase in the capital investment for the industrialization of new semiconductor technologies have radically changed the situation. Nowadays, no large semiconductor companies commits resources to the military business, which is estimated to total less than 0.5% of the world semiconductor market by the end of this decade.

On the other hand, the need for components able to operate under the stress of radiation is even more acute, due to the increasing importance of the civilian telecomunications sector. The type of components that the civilian contractors require are also changing profoundly. This evolution is driven by the relentless competition, that imposes a capping of the production costs, together with a continuous push to provide more advanced products. There appears thus a major split between the needs of the military and the civilian sectors. The technology driver today is the civilian sector, particularly the telecom market.

#### 1.1.1 Le marché civil des télécommunications The civilian telecomunications market

Le secteur spatiale civil a connu une évolution technique et commerciale importante ces dernières décennies. Depuis le lancement du premier satellite de communications INTELSAT 1, en 1965, la capacité de transmission a été multipliée par 500 (soit 120 000 circuits téléphoniques par satellite pour la dernière génération), la masse de l'engin au lancement a été portée de moins de 100 kg à plus de 4 tonnes, alors que la durée de vie en orbite passait de 1,5 à 17 ans 3. Cependant, l'architecture générale des charges utiles de télécommunications n'a guère changé (reception, translation de fréquence, transmission). En revanche, de nouvelles générations mettront en oeuvre des techniques de traitement beaucoup plus évoluées (commutation de paquets, etc.). Ce changement d'architecture est rendu nécessaire par l'évolution des besoins en mission, qui ont été profondément modifiés par la diversification accélérée des services mobiles de télécommunications, notamment le déploiement des services mobiles personnels avec une couverture globale. Ces nouveaux services s'appuyeront pour la plupart sur des constellations de satellites.

#### Les nouveaux réseaux satellitaires The new satellite networks

Les services de liaisons mobiles sont plus efficacement mis en oeuvre par des constellations de satellites en orbite basse ou intermédiaire. Ce genre de système satellitaire présente l'avantage d'une moindre distance entre le satellite et le terminal mobile, permettant à ce dernier une transmission à puissance réduite. Pour le transport de la voix, un autre avantage est la réduction du retard de propagation. Le satellite peut aussi profiter d'une réduction de taille et de coût (du fait que sa couverture sera moins importante), mais en contrepartie sa durée de vie est limitée du fait du frottement accru avec l'atmosphère. En plus, la mise en oeuvre est très com-

The civilian space sector has undergone a great evolution, both technical and commercial, during the past decades. Since the launch of the first telecomunications satellite, INTELSAT 1, in 1965, the communication capacity has been multiplied by 500 (that is, 120,000 telephone circuits per satellite for the last generation), the mass of the craft at launch has gone from less than 100 kg to more than 4 tons, while the service life in orbit has been lengthened from 1.5 to 17 years. Yet, the general architecture of the telecom payload has remained mostly unchanged (reception, frequency translation, transmission). On the other hand, the newer generations will have a much more sophisticated on-board processing (packet switching, etc.). This technology shift is a consequence of the new mission requirements, which have been profoundly changed by the diversification of the mobile telecomunications market, particularly with the introduction of global personal mobile telecomunication services. These new services will for the most part rely on satellite constellations.

The mobile communication services are more efficiently implemented through low or intermediate orbit satellite constellations. This kind of satellite system has the advantage of a shorter distance between the mobile terminal and the satellite, allowing the former to transmit a lower power signal. Another advantage for voice carrier systems is the diminished propagation delay. The satellite itself can also profit from a reduced size and cost (because of the smaller coverage), but in exchange its service life is reduced by the increased atmospheric drag. Moreover, the overall implementation is very complicated, once that the satellites must relay each other plexe, puisque les satellites doivent se relayer afin d'assurer la continuité de communication avec le terminal au sol. Chaque satellite aura une visibilité limitée, allant des alentours de 1 heure pour les orbites intermédiaires à seulement 5 minutes pour les orbites basses.

Toutefois, l'avantage d'un terminal mobile moins coûteux et avec une durée d'utilisation sur batterie plus longue peut s'avérer décisif pour la conquête d'une tranche d'un marché fortement concurrencée. La plupart des nouveaux systèmes satellitaires planifiés sont donc des constellations. Ces constellations seront composées de 10 (système INMARSAT-P) jusqu'à 288 (système Teledesic, de Microsoft Corporation) satellites. Il faudra changer radicalement la manière dont les satellites sont fabriqués, pour passer de la construction actuelle presque artisanale à une production de masse en série, puisque le coût par engin doit chuter énormément. Ce changement est déjà amorcé en quelque sort, et on peut donner comme exemple l'usine qui Alenia Spazio a construit spécifiquement pour le montage des satellites du système GLOBALSTAR (48 satellites sur une orbite à 1 400 km, plus 8 satellites en réserve). Le consortium responsable de la construction de ce système a d'ailleurs basculé totalement dans un mode de production en série, afin de pouvoir fournir des satellites à un coût réduit. C'est-à-dire, de l'ordre de 90 millions de francs par satellite, livré sur la plateforme de tir[4].

Les futures générations de satellites auront les avantages suivants :

- une capacité de transmission élevée;

- une flexibilité d'allocation de ressources (voix, données);

- une couverture reconfigurable:

- une masse au lancement réduite;

- une autonomie de gestion à bord.

Pour atteindre ces buts, leur architecture

in order to ensure a continuous link to the ground terminal. Each satellite will have a limited visibility, going from around 1 hour for the intermediate orbits to only 5 minutes for the low orbits.

However, the advantage of a lower cost mobile terminal, with a longer battery life, may prove itself decisive in the battle for a share of a highly competitive market. Therefore, most of the planned satellite systems are constellations. These constellations will have from 10 (INMARSAT-P) up to 288 satellites (Teledesic, of Microsoft Corp.). It'll be necessary to change radically the way the satellites are made, to go from the nearly handmade work done nowadays to a mass produced product, since the unit cost must fall precipitously. This change is coming about already, and one can give as example the factory that Alenia Spazio has put together specifically for the assembly of the GLOBALSTAR satellites (48 satellites on a 1,400 km orbit, plus 8 reserve satellites). The consortium in charge of the system has in fact switched completely to a series production line, in order to be able to supply satellites at lower cost. That is, on the order of 90 million francs per satellite, delivered at the launch pad[4].

The future generations of satellites will have the following advantages:

- high transmission capacity,

- flexible resource alocation (data, voice),

- reconfigurable coverage,

- small mass at launch,

- autonomous on-board processing.

To achieve these objectives, their architec-

diffère de façon importante de l'architecture courante en trois points principaux:

- le traitement numérique du signal;

- la commutation à bord;

- les plateformes à faible masse et faible dissipation, capables de gérer de façon autonome le contrôle d'attitude et d'orbite.

À l'heure actuelle, les algorithmes de calcul associés au traitement numérique et à la commutation à bord sont bien maîtrisés. La difficulté pour la mise en oeuvre se trouve dans le manque d'ASICs ayant une grande densité d'intégration et capables de résister à des doses importantes de radiation. Ce problème fait l'objet d'un grand nombre de travaux, portant notamment sur le portage de dessins d'ASICs commerciaux à des filières technologiques durcies, ou sur la qualification d'ASICs standard disponibles sur le marché pour l'utilisation dans l'espace[5]. Cette dernière approche est connue, dans sa forme la plus générale, comme l'utilisation de produits COTS (produits disponibles commercialement dans les rayons). L'approche COTS semble être l'unique solution pour la fabrication de nouvelles générations de satellites.

Pour les plateformes, il s'agit d'employer de nouveaux processeurs de bord plus performants, et de réduire l'encombrement (taille et masse) des instruments. Pour aboutir à cette réduction, il faut faire appel à de nouvelles technologies. La technologie émergente la plus prometteuse est celle des microsystèmes intégrés.

#### 1.1.2 Les microsystèmes intégrés Integrated microsystems

Le domaine des microsystèmes intégrés a connu un grand essor depuis le début des années 90. La miniaturisation des capteurs et des actionneurs a toujours été l'objet des recherches, mais c'est à la fin des années 80 que le concept des microsystèmes a pris sa forme ture differs profoundly from the current one, in three major points:

- digital signal processing,

- · on-board routing,

- low-mass, low-power platforms (bus), capables of autonomous control of attitude and orbit.

At this moment, the computer algorithms for the digital signal processing and the onboard routing are well developed. The stumbling block for the actual use is the lack of high integration ASICs able to resist to a significant dose of radiation. This difficulty has been the subject of much work, mostly geared to the porting of commercial ASIC designs to hardened processes, or to the qualification of standard ASICs available in the market for space use[5]. This last approach is known generally as the use of COTS (commercial off-theshelf) products. The COTS approach appears to be the only solution for the deployment of the new generations of satellites.

For the platforms, it's a question of using new, more advanced processors, and of reducing the volume (size and mass) of the instruments. To succeed in this endeavor, one must take advantage of new technologies. The most promising emerging technology are the integrated microsystems.

The integrated microsystems domain has known a great deal of development since the beginning of the 90's. The miniaturization of sensors and actuators has always been a subject of research, but it was at the end of the 80's that the concept of microsystems took its actuelle.

Ceci est dû à plusieurs facteurs, dont on peut citer:

- l'intérêt scientifique de nouvelles possibilités;

- la maturité des technologies de fabrication micro-électronique;

- l'engagement immédiat de l'industrie, attirée par la perspective de réduction de coûts.

De nos jours, une vaste gamme de microsystèmes a été développée, et plusieurs millions de pièces ont déjà été commercialisées.

Un microsystème peut être défini au sens large comme un système fabriqué collectivement, intégrant les fonctions; capteur, traitement du signal, actionneur, alimentation.

L'ensemble des fonctions ou bien juste une partie peut être implanté. Les microsystèmes sont capables d'accompagner l'évolution de leur environnement et de réagir par rapport à cela. Les microsystèmes les plus répandus aujourd'hui sont ceux basés sur les microtechnologies du silicium. Cela est dû à la maîtrise de la fabrication à très large échelle des composants semiconducteurs en silicium, où les dispositifs sont de plus en plus complexes et d'une taille individuelle de plus en plus réduite. L'emploi de ces technologies industrielles est un puissant levier à l'introduction des microsystèmes en silicium sur le marché.

#### Application de microsystèmes pour l'espace Microsystems applications in space

Parmi les nombreux microsystèmes déjà disponibles sur le marché, plusieurs pourraient trouver des applications dans l'espace. Cette possibilité fait l'objet d'études approfondies depuis le début des années 90. Plus récemment la NASA, à travers du JPL (Jet Propulsion Laboratory, en Californie), s'est lancée sur un ambitieux programme de développement de missions interplanétaires, axé sur les microsystèmes. Les responsables de ce programme. present form.

There are several reasons for this, some of which are:

- The scientific interest of the new possible approaches,

- the maturity of microelectronics manufacturing technologies,

- the early industry involvement, attracted by the possible cost reductions.

To this day, a wide range of microsystems has been developed, and several millions of units have been already sold.

A microsystem can be defined, in a general way, as a collectively fabricated system, comprising the functions; sensor, signal conditioning, actuator and power supply.

Every function, or just a subset, is present on a given implementation. The microsystems are capable of sensing their environment, and to react to changes. The most common variety of microsystem is the silicon technology one. This is a consequence of the mastering of the manufacturing technology for the production in very large scale of silicon semiconductor components, where the devices are ever more complex with an ever smaller individual size. The use of these industrial processes is a powerful leverage for the marketing of silicon microsystems.

Among the many microsystems already available on the market, several could find use in space. This possibility has been vigorously researched since the beginning of the 90's. More recently, NASA, through the Jet Propulsion Lab (JPL, in California), has started an ambitious interplanetary missions development program, based around microsystems. The managers of this program, called Millenium Project, forecast a range of commercial nommé Millenium Project, prévoient d'importantes retombées commerciales. À l'instar de la NASA, l'Agence Spatiale Européenne (ESA) a défini les microsystèmes comme un des 13 axes technologiques majeurs de son programme de recherche et développement pour la période 1997–1999[6].

Des études ont constaté que dans un satellite, tel qu'il est conçu aujourd'hui, l'endroit où les microsystèmes pourraient contribuer à un gain décisif par rapport aux solutions actuelles est dans le sous-système de contrôle d'attitude et d'orientation (SCAO).

L'utilisation des microsystèmes peut apporter des gains substantiels par rapport à la masse et à la dissipation. Ceci sera cruciale pour les satellites qui en sont sévèrement contraints, à cause principalement des coûts de lancement. C'est le cas des satellites faisant partie des constellations. La fabrication de ces microsystèmes dans une production en série n'est envisageable dans le futur proche que sur des filières en silicium. On ne peut pas espérer que ces filières soient développés tenant en compte les besoins spécifiques de l'environnement spatial, dont la radiation. Il faut alors déterminer le degré de compatibilité des circuits et des microsystèmes avec ces contraintes, et étudier des techniques d'amélioration. C'est dans ce scénario que s'inscrit le travail de recherche ci-décrit.

spin-offs. In the footsteps of NASA, the European Space Agency (ESA) has defined microsystems as one of the 13 major technology axes of its research and development program for the period 1997–1999[6].

It's generally accepted that, in a satellite, as it's conceived today, the place where microsystems could contribute a decisive advantage with respect to current solutions is the Attitude and Orientation Control System (AOCS).

The use of microsystems can yield substantial gains in terms of mass and power consumption. This will be a crucial point for the satellites that are severely constrained in this regard, particularly because of launch costs. The industrial manufacturing of microsystems cannot be done in the near future using other than silicon processes. One can't expect that the development of these processes will take in consideration the specific requirements of the space environnement, such as radiation. One must then determine the degree of compatibility of circuits and microsystems with these constraints, and to find ways to improve it. This is the research framework of this thesis.

### 1.2 Objectif et organisation de l'étude Purpose and organization of the thesis

L'objectif de cette étude est de démontrer la faisabilité d'utilisation d'une filière technologique 1,2 µm CMOS bulk standard, compatible avec des microsystèmes usinés, pour des applications spatiales. Plusieurs techniques de projet pouvant augmenter la tolérance des structures aux rayonnements sont passées en revue. Leur efficacité est examinée de façon expérimentale, dans le cadre du développement d'un imageur intégré sensible dans la bande infra-rouge, pour un nouveau type de viseur de Terre statique conçu spécifiquement The purpose of this thesis is to demonstrate the feasibility of the use of a standard 1,2  $\mu$ m CMOS bulk technology, compatible with micromachined microsystems, for space applications. Several design techniques capable of increasing the tolerance of the structures to radiation are reviewed. Their effectiveness are assessed experimentally, within the framework of the development of an integrated infra-red imaging device, for a new type of static Earth sensor customized for small satellites. The accomplishment of this

pour de petits satellites. L'accomplissement de cette tâche nécessite le développement d'une compétence multi-disciplinaire, englobant; la physique des semiconducteurs, la physique des particules, la modélisation et la simulation de dispositifs intégrés, la fabrication des circuits intégrés, la fabrication des microsystèmes micro-usinés et la conception de circuits analogiques de hautes performances. Les diverses connaissances requises sont décrites de manière condensée dans ce rapport.

L'étude commence par une description des principes de fonctionnement des dispositifs électroniques intégrés (chapitre 2), suivie par une revue des procédés industrielles pour la fabrication de circuits intégrés (chapitre 3). Cette étude est étendue au dernier développement de la micro-électronique; les microsystèmes intégrés, notamment les microsystèmes qui sont compatibles avec les procédés de fabrication de circuits intégrés «grand public».

L'exposition de circuits intégrés à la radiation entraîne des altérations de fonctionnement. Ces altérations sont fonction du type de radiation et des matériaux qui composent les circuits intégrés. La première démarche dans la recherche de moyens d'assurer le fonctionnement des circuits est donc de comprendre les fondements des mécanismes d'interaction de la radiation avec la matière. Les différents types d'interaction qui peuvent avoir lieu dans les circuits intégrés en silicium sont décrits dans le chapitre 4. Cette description est ciblée sur les phénomènes ayant lieu sur les circuits en technologie CMOS transitant dans l'espace proche de la Terre. Les caractéristiques majeures du rayonnement auquel sont exposés la plupart des satellites civils sont répertoriées.

Les effets de cette exposition sur les circuits intégrés embarqués dépendent de leur construction et de leur mode d'opération (analogiques, numériques, etc.). Les dégradations induites dans les dispositifs électriques disponibles dans une technologie CMOS sont décrites dans le chapitre 5. L'évaluation du niveau de détérioration du comportement électrique est impérative. Cette évaluation peut task requires a multi-disciplinary study, encompassing; semiconductor physics, particle physics, modeling and simulation of integrated devices, integrated circuits fabrication, micromachined microsystems fabrication, and design of high-performance analog circuits. In this thesis, the wide know-how needed is discussed in a compact fashion.

The study starts with a description of the working principles of integrated electronic devices (chapter 2), followed by a review of the industrial processes for the manufacturing of integrated circuits (chapter 3). The study is extended to the latest development in microelectronics: the integrated microsystems, in particular the microsystems which are compatible with the manufacturing technology of "consumer electronics" integrated circuits.

The exposure of integrated circuits to radiation causes functional degradations. These degradations are a function of the type of the radiation and the materials that constitute the integrated circuit. The first step in the search for ways to ensure continued circuit functionality is then to understand the fundamentals of the interactions between radiation and matter. The different kinds of interactions that can take place in silicon integrated circuits are detailed in chapter 4. This description is focused on the phenomena that take place in CMOS technology integrated circuits transiting in near-Earth space. The major features of the radiation to which most civilian satellites are exposed are listed.

The effects of this exposure in the onboard integrated circuits depend on their construction and type (analog, digital, etc.). The damages induced in the electronic devices available in a CMOS technology are discussed in chapter 5. The investigation of the worsening of the electrical behavior is paramount. This investigation can be carried out through theoretical studies, as well as experimentally. être menée au niveau théorique, ainsi que par une caractérisation expérimentale. Les méthodes expérimentales d'évaluation sont étudiées, ainsi que les divers moyens d'assurer la fonctionnalité du système (son durcissement aux rayonnements). Ces techniques de durcissement imposent des sur-coûts divers, et pénalisent la capacité de traitement du système électronique. Les compromis sont relevés au cas par cas. La toute nouvelle question du durcissement des microsystèmes est soulévée, avec une discussion approfondie du cas des thermopiles en silicium.

Les éléments étudiés sont rassemblés dans le chapitre 6. Tout d'abord, la faisabilité d'utilisation de la technologie AMS CAE (1,2 μm CMOS bulk ) dans l'espace fait l'objet d'une analyse théorique. Pour déterminer avec précision la sensibilité de la technologie choisie un programme de caractérisation a été mis en place, avec la réalisation de structures de test spécifiques. La méthodologie suivie lors des essais a été proche des recommandations de l'Agence Spatiale Européenne[7]. La mise en oeuvre et les résultats obtenus sont rapportés, et les conclusions pour la réalisation de l'électronique de lecture sont données à la fin du chapitre 6.

Les connaissances amassées et les renseignements tirés des essais sont appliqués dans le développement d'un microsystème pour une application spatiale (systèmes de contrôle d'orbite et d'attitude). Ce microsystème est un capteur de rayonnements infrarouges basé sur des barrettes de thermopiles en silicium, avec de l'électronique de traitement intégrée. Les enjeux de la conception et de la fabrication du premier élément de la chaîne de traitement du signal sont décrits dans le chapitre 7. Les résultats des essais effectués pour la qualification du composant pour l'espace sont également rapportés. Le chapitre est terminé avec une courte description de l'élément suivant de la chaîne, l'amplificateur bas bruit.

Ce rapport de thèse est clos par une synthèse générale, où les thèmes abordés dans chaque chapitre sont revisités. Enfin, les persThe experimental methods are studied, and also the various means to ensure the continued functioning of the system (radiation hardening techniques). These hardening techniques have a significant cost, and reduce the processing power of the electronic system. The tradeoffs in each case are noted. The brand new question of microsystems hardening is brought up, with a detailed analysis of the case of silicon thermopiles.

All elements fall in place together in chapter 6. First, the feasibility of using the AMS CAE technology in space is analyzed from a theoretical point of view. To find out precisely the susceptibility of the technology chosen, a characterization program was conducted, with the fabrication of custom test structures. The methodology employed during the tests followed closely the guidelines issued by the European Space Agency[7]. The test set-up, and the results obtained are reported, and the guidelines for the implementation of the read-out electronics are given at the end of chapter 6.

The know-how garnered and the information extracted from the experiments are then applied in the development of a microsystem for space applications (attitude and orbit control systems). This microsystem is an infrared sensor, based on a linear array of silicon thermopiles, with integrated electronics. The issues involved in the design and fabrication of the first element of the signal read-out chain are discussed in chapter 7. The results of the tests carried out to qualify the component for space are also reported. The chapter is finished with a short description of the next element in the chain, the low-noise amplifier.

This thesis is wrapped up by a global synthesis, where the themes discussed in each chapter are revisited. Finally, the outlook for pectives pour la suite des travaux dans le sens du durcissement de technologies COTS sont discutées.

the continuation of the research in the field of radiation hardening of COTS technologies is discussed. Première partie

$\begin{array}{c} \text{Principes} \\ \textbf{\textit{Fundamentals}} \end{array}$

## Chapitre 2

## Les dispositifs semiconducteurs Semiconductor devices

#### 2.1 Introduction

Les systèmes électroniques modernes sont basés presque exclusivement sur des circuits intégrés semiconducteurs, fabriqués dans la plupart des cas en silicium. Cette préférence s'explique par l'ensemble d'avantages qu'il possède pour la réalisation de dispositifs électroniques à l'échelle industrielle. Cependant, leurs propriétés de fonctionnement sont altérées par la radiation. Il est donc nécessaire d'étudier les principes physiques de ces dispositifs pour comprendre la nature des dégâts engendrés et rechercher des moyens pour les atténuer.

Les fondements abrégés physiques des dispositifs semiconducteurs sont décrits dans ce chapitre. L'accent est mis sur les dispositifs spécifiques aux technologies planaires, notamment ceux qui présentent une sensibilité importante aux rayonnements ionisants. La revue des concepts de base de la physique des semiconducteurs est suivie d'une description qualitative du comportement électrique (macroscopique) de chaque dispositif. Les caractéristiques électriques sont expliquées par rapport aux phénomènes à l'échelle atomique. Un traitement exhaustif du sujet peut être trouvé dans plusieurs ouvrages [8, 9].

La description des phénomènes physiques est relayée par une introduction à la modélisation électrique du transistor MOS. Bien que cette modélisation soit appuyée sur des considérations physiques, les besoins spécifiques à la résolution des équations de circuit donnent aux modèles une autre nature. La compréhension des hypothèses intégrées dans ces modèles électriques est fondamentale pour l'introduction des effets du rayonnement. Deux modèles électriques sont étudiés, les modèles de Schichman-Hodges et le modèle de Meyer. Les paramètres utilisés par ces modèles sont suffisants pour la modélisation des effets de la radiation ionisante.

Finalement, une introduction à la modélisation électrique du bruit des dispositifs semiconducteurs est faite. Cette introduction est motivée par l'importance du bruit pour les microsystèmes, notamment les circuits de lecture. Le bruit est un facteur qui impose souvent la limite d'opération des circuits électroniques analogiques. Les modèles de bruit mis en oeuvre par des simulateurs électriques ne sont pas toujours correctes. En outre, quelques formes de bruit s'accroîssent de façon significative avec l'exposition au rayonnement.

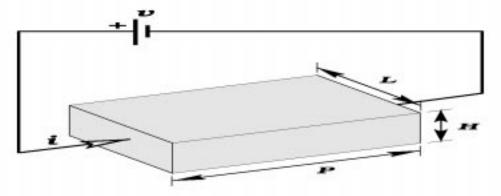

Fig. 2.1 – La résistivité  $\rho$  est égale à  $\frac{v}{i}\frac{L\times H}{P}$

#### 2.2 La conductivité

Les caractéristiques électriques des matériaux sont très variées. Il est convenable de les classer par rapport à leur résistance électrique. Pour exprimer la résistance de façon générale, il est utile de définir la résistivité  $\rho$  d'un corps, comme montré dans la figure 2.1. La résistivité des solides varie énormément selon le matériau, et en général ne dépends que de la composition du matériau et de la température. La résistivité d'un matériau trouve son origine dans sa structure atomique. Les matériaux ayant une faible résistivité (comme les métaux) sont classés comme des conducteurs, et ceux qui ont une forte résistivité (comme le caoutchouc) sont classés comme des isolants. Néanmoins, ils existent des matériaux dont la résistivité est intermédiaire, et elle peut être amenée à changer de forme drastique entre celle des conducteurs et celle des isolants. Ces matériaux sont appelés les semiconducteurs. Le semiconducteur qui a le plus grand intérêt économique aujourd'hui est le silicium monocristallin. Le comportement électrique du silicium est habituellement exprimé en termes des phénomènes dans les bandes d'énergie.

#### 2.2.1 Les bandes d'énergie

Un atome seul dans l'espace retient ses électrons par le champ électrique coulombien qui est exercé par son noyau. L'électron possède une énergie cinétique et une énergie potentielle, et leur combinaison constitue le niveau d'énergie de l'électron. Un électron soumis au champ du noyau ne peut posséder que des niveaux discrets d'énergie, au-dessous d'un niveau de référence. Ces niveaux discrets (appelés d'états quantiques stationnaires, dans le modèle de l'atome proposé par Bohr) sont les seuls niveaux d'énergie admis pour l'électron sur orbite. L'ensemble des niveaux d'énergie non-admis forment les bandes d'énergies interdites.

Les niveaux d'énergie sont considérés comme négatifs, à partir du niveau d'énergie de l'électron sur l'orbite la plus proche du noyau. L'énergie augmente vers zéro, selon l'éloignement de l'orbite. C'est-à-dire que les électrons possèdent de plus en plus d'énergie, et la différence entre leur niveau d'énergie et zéro représente l'énergie qu'il faut apporter pour libérer l'électron de l'emprise de l'atome.

À très basses températures les électrons remplissent les niveaux d'énergie permis, commençant par les niveaux de plus basses énergies. Le principe d'exclusion de Pauli impose une limite de deux électrons (ayant des moments cinétiques intrinsèques 1 opposés) par niveau.

<sup>1.</sup> spin

Dans un cristal pur, les atomes sont tous identiques et se trouvent assemblés dans une structure régulière. L'interaction entre les champs des noyaux et la contrainte du principe d'exclusion de Pauli entraînent une distorsion des niveaux d'énergie de chaque atome, et le cristal développe des bandes d'énergie admises, s'étendant sur tout le matériau. Chaque bande est bornée par des limites inférieures et supérieures d'énergie, et peut être séparée d'autres bandes par des bandes d'énergie interdites. Il peut avoir aussi des superpositions de bandes d'énergie admises, à l'interface des matériaux. La structure exacte de ces bandes, l'existence et la magnitude des bandes interdites déterminent les propriétés électriques macroscopiques du solide.

Chaque bande d'énergie est composée d'un certain nombre de niveaux discrets d'énergie. Si tous les niveaux sont occupés par deux électrons (de spins distincts) la bande est complète. La bande complète la plus éloignée du noyau, au zéro absolu, est la bande de valence. La bande immédiatement après est la bande de conduction.

Dans un semiconducteur la bande de valence est séparée de la bande de conduction par un écart d'énergie peu important, et un certain nombre d'électrons peuvent acquérir suffisamment d'énergie pour passer dans la bande de conduction, où ils sont libres de se déplacer dans le solide sous l'influence d'un champ électrique externe. Chaque électron qui quitte ainsi la bande de valence laisse derrière lui un état (niveau) d'énergie vacant. L'ensemble de ces états peut être occupé par d'autres électrons de la bande de valence, se déplaçant sous l'influence du champ électrique externe. Il est plus simple de concevoir alors qu'il existe un déplacement de trous d'énergie dans la bande. Conceptuellement, pour chaque électron qui franchit la bande interdite et arrive dans la bande de conduction, il y a un trou qui «chute» dans la bande de valence. Ces électrons et trous sont libres de se déplacer dans le solide, constituant ainsi un courant.

Parfois il est plus utile de visualiser la production d'électrons et trous libres en termes de brisures de liaisons covalentes entre les atomes. Dans un semiconducteur cristallin pur, les atomes sont disposés de façon périodique, et forment un motif de base qui est répliqué à travers le solide, dans toutes les directions. Les atomes sont reliés entre eux par des liaisons électriques homopolaires (covalentes), chacune composée d'une paire d'électrons de la couche orbitale de valence (un de chaque atome). Au zéro absolu tous les électrons sont fermement tenus par ces liaisons, et aucun peut se déplacer sous l'influence d'un champ électrique externe. À des températures plus élevées la vibration des atomes est capable de rompre quelques liaisons, et les électrons deviennent libres pour se déplacer, engendrant un courant d'électrons. L'électron libre laisse une liaison incomplète, et un autre électron voisin peut y être rattrapé. Le déplacement de la liaison incomplète peut être interprété comme un courant de trous.

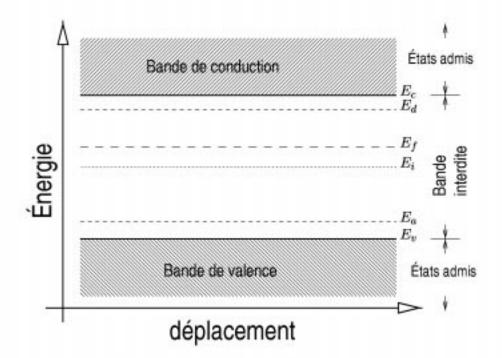

Les bandes de valence et conduction sont montrés schématiquement dans la figure 2.2. L'écart entre les bandes détermine la conductivité du matériau. Les isolants on généralement un écart supérieur à  $5 \ eV \ (\approx 9 \ eV \ pour \ le \ SiO_2)$ . Les semiconducteurs ont des formes de bandes d'énergie semblables, mais la largeur de leur bande interdite est moins importante ( $\approx 1,1 \ eV$  pour le Si). À température ambiante, un nombre non-négligeable d'électrons du semiconducteur absorbent assez d'énergie de la maille cristalline pour franchir la bande interdite (dans le cas du silicium la transition est indirecte, et passe par un centre de génération-recombinaison). La distribution des niveaux d'énergie occupés par des électrons obéit à la fonction de Fermi-Dirac :

$$f(E)dE = \frac{dE}{1 + e^{\frac{E-E_f}{kT}}}$$

(2.1)

Fig. 2.2 — Diagramme bi-dimensionel des bandes d'énergie, montrant le niveau énergique de Fermi  $(E_f)$ , le niveau de Fermi intrinsèque  $(E_i)$  la limite supérieure de la bande de valence  $(E_v)$  et la limite inférieure de la bande de conduction  $(E_c)$ . Le diagramme montre aussi l'emplacement des niveaux énergétiques accepteurs  $(E_a)$  et donneurs  $(E_d)$ .

La fonction f(E)dE donne la probabilité d'occupation de la bande d'énergie de largeur infinitésimale dE par un électron, à la température T (en Kelvins). Le terme k représente la constante de Boltzmann ( $\approx 1.380 \times 10^{-23}$  J/K). Le terme  $E_f$  est le niveau (ou potentiel) de Fermi. Au zéro absolu, tous les électrons se trouvent à des niveaux inférieurs au niveau de Fermi. Au-dessus du zéro absolu, la moitié des électrons occupent des niveaux d'énergie inférieurs à  $E_f$ . Ce niveau se déplace, en fonction de la distribution des états d'énergie disponibles. Sur le Si pur (intrinsèque),  $E_f$  se trouve presque exactement au centre de la bande interdite:

$$E_f \simeq \frac{E_c + E_v}{2}$$

#### 2.2.2 Le dopage

La structure et l'occupation des bandes d'énergie du cristal semiconducteur peuvent être modifiées de façon contrôlée par l'introduction d'atomes d'autres éléments (impuretés). Cette possibilité est fort importante, vue que dans le semiconducteur intrinsèque la population d'électrons dans la bande de conduction est insuffisante pour établir un courant conséquent. Ces électrons ont acquis assez d'énergie pour s'affranchir de la bande interdite, laissant derrière eux des trous. Leur nombre augmente avec la température, et la densité  $n_0$  d'électrons est égale à celle de trous  $p_0$ . Leur produit est une constante, qui dépend seulement de la température:

$$n_i^2 = n_0.p_0$$

(2.2)

Le terme  $n_i$  est nommé la densité intrinsèque de porteurs. La relation 2.2 est toujours applicable, même pour les semiconducteurs dopés, pourvu qu'ils soient en équilibre thermique. La densité de porteurs  $n_i$  dans le silicium pur est donnée par la formule[10, p.104]:

$$n_i = 2,23 \times 10^{19} \left(\frac{T}{300}\right)^{\frac{3}{2}} e^{\frac{-0.55}{kT}}$$

(2.3)