# Outils pour l'exploration d'architectures programmables embarquées dans le cadre d'applications industrielles (Tools for exploration of embedded programmable architectures in industrial applications)

F. Nacabal

#### ▶ To cite this version:

F. Nacabal. Outils pour l'exploration d'architectures programmables embarquées dans le cadre d'applications industrielles (Tools for exploration of embedded programmable architectures in industrial applications). Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble - INPG, 1998. Français. NNT: . tel-00002973

## HAL Id: tel-00002973 https://theses.hal.science/tel-00002973

Submitted on 11 Jun 2003

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THÈSE DE DOCTORAT

présentée par

#### François NAÇABAL

pour obtenir le grade de **DOCTEUR**

#### de l'INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

(arrêté ministériel du 30 mars 1992)

Spécialité : Microélectronique

# OUTILS POUR L'EXPLORATION D'ARCHITECTURES PROGRAMMABLES EMBARQUÉES DANS LE CADRE D'APPLICATIONS INDUSTRIELLES

Date de Soutenance : 27 Février 1998

#### Composition du jury :

Messieurs : Pierre GENTIL Président

Yvon SAVARIA Rapporteur

Sanjay RAJOPADHYE Rapporteur

Joseph BOREL Examinateur

Pierre PAULIN Examinateur

Ahmed JERRAYA Examinateur

Thèse préparée au sein du Laboratoire TIMA-INPG à Grenoble et du département Central R&D de SGS-THOMSON Microelectronics à Crolles

# Remerciements

Ce travail a été effectué au sein du laboratoire des Techniques de l'Informatique et de la Microélectronique pour l'Architecture d'ordinateurs (TIMA) de l'Institut National Polytechnique de Grenoble (INPG), ainsi qu'au département de Recherche et Développement Central de SGS-THOMSON Microelectronics à Crolles. Je tiens à remercier tout particulièrement Messieurs Ahmed Jerraya et Pierre Paulin pour leur aide dans l'orientation de mon travail, et leur précieux support.

Je remercie Monsieur Pierre Gentil, de l'INPG, qui m'a fait l'honneur de présider mon jury de thèse.

Que Messieurs Yvon Savaria, de l'Ecole Polytechnique de Montréal, et Sanjay Rajopadhye, de l'IRISA, trouvent ici l'expression de ma reconnaissance pour avoir accepté d'être rapporteurs de mon travail.

Je remercie de plus Monsieur Joseph Borel, de SGS-THOMSON, qui a accepté de faire partie de mon jury de thèse.

Je remercie l'équipe de conception du circuit IVT de SGS-THOMSON, en particulier Michel Harrand, Olivier Deygas et José Sanches.

Je tiens à témoigner ma reconnaissance à tous ceux qui m'ont aidé durant ces trois années, aussi bien dans l'équipe Embedded Systems Technology de SGS-THOMSON que dans le groupe System-Level Synthesis du TIMA, et plus spécialement à Marco Cornero, Clifford Liem et Miguel Santana.

Je remercie très particulièrement Chantal Brunel et Philippe Guillaume pour leur support constant et leur profonde amitié.

Je remercie enfin toute ma famille, pour m'avoir toujours soutenu au cours de mes études, et à qui je souhaite dédier cette thèse.

# Table des matières

| 1        | Intr | roduction                                                             | 15 |

|----------|------|-----------------------------------------------------------------------|----|

|          | 1.1  | Objectifs                                                             | 16 |

|          | 1.2  | Contributions                                                         | 18 |

|          | 1.3  | Plan de la thèse                                                      | 18 |

| <b>2</b> | Con  | atexte industriel                                                     | 19 |

|          | 2.1  | Le système Integrated Videotelephone Terminal (IVT)                   | 19 |

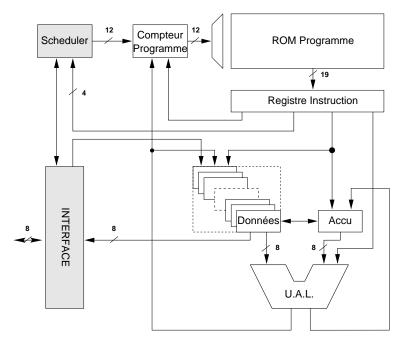

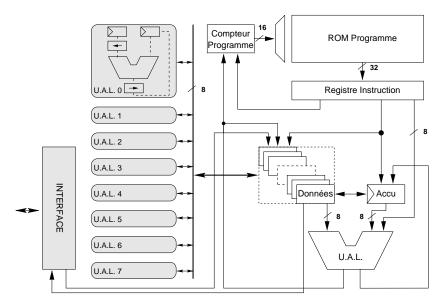

|          |      | 2.1.1 Le Micro-Sequencer (MSQ)                                        | 19 |

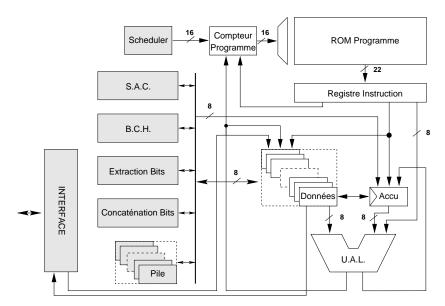

|          |      | 2.1.2 Le Bit Stream Processor (BSP)                                   | 20 |

|          |      | 2.1.3 Le Vliw Image Processor (VIP)                                   | 22 |

|          | 2.2  | Les processeurs DSP                                                   | 23 |

|          |      | 2.2.1 Le Digital Audio Processor (DAP)                                | 23 |

|          |      | 2.2.2 Le D950                                                         | 23 |

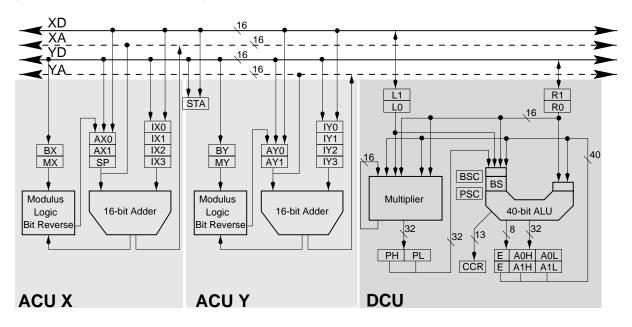

|          |      | 2.2.3 Le D960                                                         | 25 |

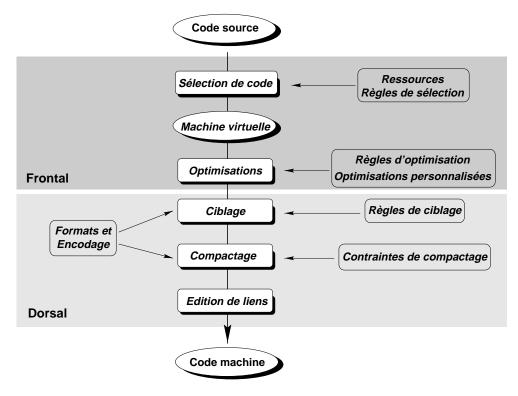

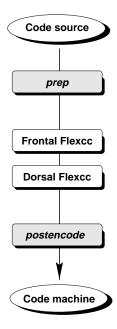

|          | 2.3  | Chaîne de compilation Flexcc                                          | 26 |

|          |      | 2.3.1 Sélection de code virtuel                                       | 27 |

|          |      | 2.3.2 Traduction vers l'assembleur cible                              | 27 |

|          |      | 2.3.3 Compactage de code                                              | 27 |

|          |      | 2.3.4 Résumé de l'approche                                            | 28 |

|          | 2.4  | Compilation pour processeurs embarqués dédiés                         | 28 |

|          |      | 2.4.1 Utilisation du langage C et de ses différents niveaux de codage | 29 |

|          |      | 2.4.2 Configuration mémoire                                           | 30 |

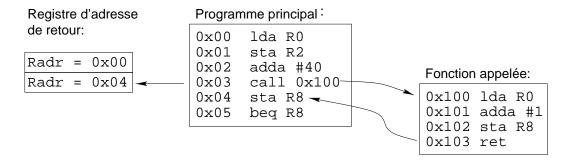

|          |      | 2.4.3 Appel de fonctions                                              | 33 |

|          |      | 2.4.4 Expansion en ligne                                              | 34 |

|          |      | 2.4.5 Insertion d'instructions assembleur                             | 35 |

|          |      | 2.4.6 Fonctions pré-définies                                          | 35 |

|          |      | 2.4.7 Encodage réduisant la consommation                              | 37 |

|          | 2.5  | Conclusion                                                            | 38 |

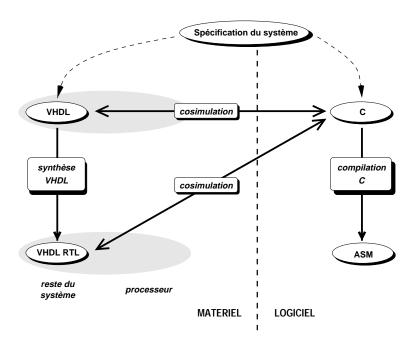

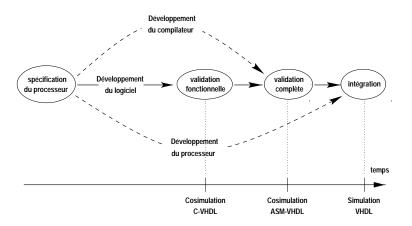

| 3        | La d | co-simulation C-VHDL                                                  | 41 |

| U        | 3.1  | Motivations                                                           | 41 |

|          | 0.1  | 3.1.1 Validation du logiciel embarqué                                 | 42 |

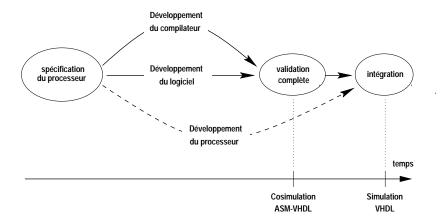

|          |      | 3.1.2 Validation tardive avec le flot de conception classique         | 42 |

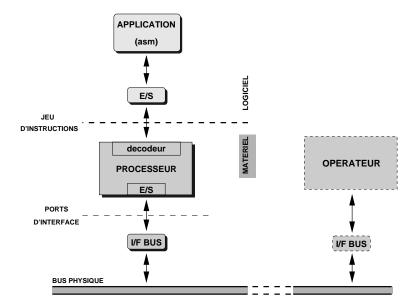

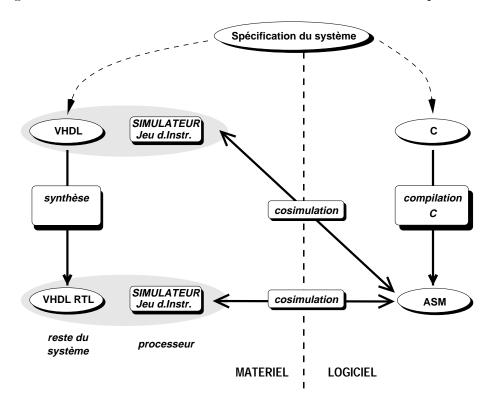

|          |      | 3.1.3 La co-simulation assembleur-VHDL au niveau instructions         | 45 |

|          |      | 3.1.4 Apport de la co-simulation C-VHDL au niveau fonctionnel         | 49 |

|          |      | 3.1.5 Principe de la co-simulation C-VHDL                             | 52 |

|          | 3.2  | État de l'art                                                         | 58 |

|          | ა.∠  | 3.2.1 Seamless                                                        | 58 |

|          |      | 9.4.1 DEGIHESS                                                        | 50 |

| 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                | 3.2.3   | Cossap et SPW                                             | . 60  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|---------|-----------------------------------------------------------|-------|

| 3.3 Spécification de l'outil CoSim 3.3.1 Fonctionnalités 3.3.2 Configuration du modèle VHDL du système 3.4 Mise en œuvre de la co-simulation C-VHDL sous Unix 3.4.1 Communication inter-processus 3.4.2 Laisson avec le simulateur VHDL 3.4.3 Synchronisation 3.5 Intégration au système applicatif 3.5.1 Génération de code d'interface 3.5.2 Bloc matériel de connexion C/interface-bus 3.5.3 Intégration aux flots de conception existants 3.6 Expérimentations industrielles 3.6.1 Circuit de test Calc 3.6.2 Circuit IVT 3.7 Travaux futurs 3.7.2 Conclusion  4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions roissant 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion  4.4 Benchmarks et applications 4.4.1 Benchmarks et applications 4.4.2 Châne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                             |   |                | 3.2.4   | Coware                                                    | . 61  |

| 3.3.1 Fonctionnalités 3.3.2 Configuration du modèle VHDL du système 3.4 Mise en œuvre de la co-simulation C-VHDL sous Unix 3.4.1 Communication inter-processus 3.4.2 Liaison avec le simulateur VHDL 3.4.3 Synchronisation 3.5 Intégration au système applicatif 3.5.1 Génération de code d'interface 3.5.2 Bloc matériel de connexion C/interface-bus 3.5.3 Intégration aux flots de conception existants 3.6 Expérimentations industrielles 3.6.1 Circuit de test Calc 3.6.2 Circuit IVT 3.7 Travaux futurs - Conclusion 3.7.1 Travaux futurs 3.7.2 Conclusion  4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaine de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience |   |                | 3.2.5   | Synthesia                                                 | . 62  |

| 3.3.2 Configuration du modèle VHDL du système 3.4 Mise en œuvre de la co-simulation C-VHDL sous Unix 3.4.1 Communication inter-processus 3.4.2 Liaison avec le simulateur VHDL 3.4.3 Synchronisation 3.5 Intégration au système applicatif 3.5.1 Génération de code d'interface 3.5.2 Bloc matériel de connexion C/interface-bus 3.5.3 Intégration aux flots de conception existants 3.6 Expérimentations industrielles 3.6.1 Circuit de test Calc 3.6.2 Circuit IVT 3.7 Travaux futurs - Conclusion 3.7.1 Travaux futurs 3.7.2 Conclusion 4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions croissant 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                   |   | 3.3            | Spécifi | cation de l'outil CoSim                                   | . 64  |

| 3.4 Mise en œuvre de la co-simulation C-VHDL sous Unix  3.4.1 Communication inter-processus  3.4.2 Liaison avec le simulateur VHDL  3.4.3 Synchronisation  3.5 Intégration au système applicatif  3.5.1 Génération de code d'interface  3.5.2 Bloc matériel de connexion C/interface-bus  3.5.3 Intégration aux flots de conception existants  3.6 Expérimentations industrielles  3.6.1 Circuit de test Calc  3.6.2 Circuit IVT  3.7 Travaux futurs - Conclusion  3.7.1 Travaux futurs  3.7.2 Conclusion  4 Exploration d'architectures  4.1 Motivations et objectifs  4.1.1 Motivations  4.1.2 Objectifs  4.2 Techniques de minimisation de code  4.2.1 Définitions  4.2.2 Réduction de la largeur à nombre d'instructions constant  4.2.3 Réduction de la largeur à nombre d'instructions croissant  4.2.4 Réduction du nombre d'instructions à largeur croissante  4.2.5 Tableau comparatif  4.3 Cas concrets de minimisation de code  4.3.1 Le Thumb de ARM  4.3.2 Le Hobbit de AT&T  4.3.3 CRISCO  4.3.4 Conclusion  4.4 Description de l'exploration du D960  4.4.1 Benchmarks et applications  4.4.2 Chaîne de compilation  4.4.3 Environnement d'exploration FlexPlore  4.5 Exploration autour du D960  4.5.1 Configuration des bancs registres  4.5.2 Encodage des champs immédiats dans le jeu d'instructions  4.5.3 Nombre de registres scratchs  4.5.4 Exemple de compromis à l'encodage  4.5.5 Leçons tirées de l'expérience                                |   |                | 3.3.1   | Fonctionnalités                                           | . 65  |

| 3.4.1 Communication inter-processus 3.4.2 Liaison avec le simulateur VHDL 3.4.3 Synchronisation 3.5 Intégration au système applicatif 3.5.1 Génération de code d'interface 3.5.2 Bloc matériel de connexion C/interface-bus 3.5.3 Intégration aux flots de conception existants 3.6 Expérimentations industrielles 3.6.1 Circuit de test Calc 3.6.2 Circuit IVT 3.7 Travaux futurs - Conclusion 3.7.1 Travaux futurs 3.7.2 Conclusion 4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                             |   |                | 3.3.2   | Configuration du modèle VHDL du système                   | . 66  |

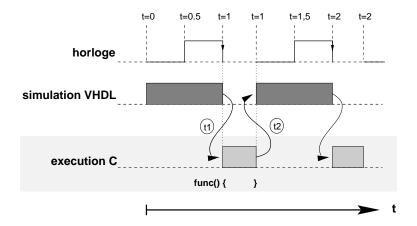

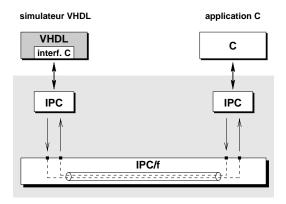

| 3.4.2 Liaison avec le simulateur VHDL 3.4.3 Synchronisation 3.5 Intégration au système applicatif 3.5.1 Génération de code d'interface 3.5.2 Bloc matériel de connexion C/interface-bus 3.5.3 Intégration aux flots de conception existants 3.6 Expérimentations industrielles 3.6.1 Circuit de test Calc 3.6.2 Circuit IVT 3.7 Travaux futurs - Conclusion 3.7.1 Travaux futurs 3.7.2 Conclusion  4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                |   | 3.4            | Mise e  | n œuvre de la co-simulation C-VHDL sous Unix              | . 67  |

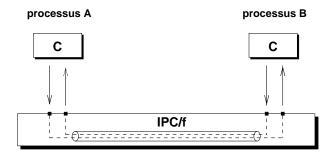

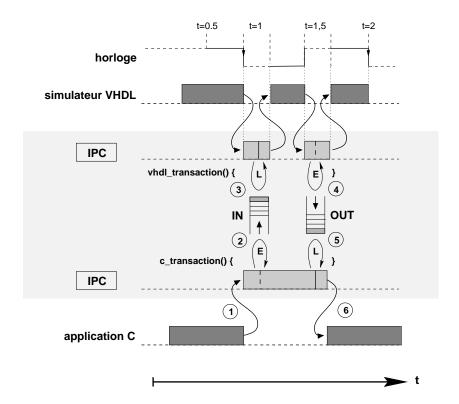

| 3.4.3 Synchronisation 3.5 Intégration au système applicatif 3.5.1 Génération de code d'interface 3.5.2 Bloc matériel de connexion C/interface-bus 3.5.3 Intégration aux flots de conception existants 3.6 Expérimentations industrielles 3.6.1 Circuit de test Calc 3.6.2 Circuit IVT 3.7 Travaux futurs - Conclusion 3.7.1 Travaux futurs 3.7.2 Conclusion  4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction de la largeur à nombre d'instructions croissant 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                    |   |                | 3.4.1   | Communication inter-processus                             | . 67  |

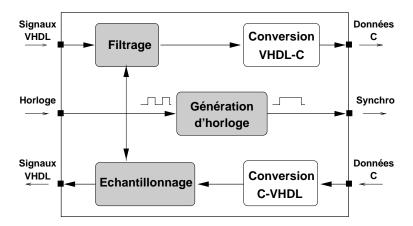

| 3.5. Intégration au système applicatif 3.5.1 Génération de code d'interface 3.5.2 Bloc matériel de connexion C/interface-bus 3.5.3 Intégration aux flots de conception existants 3.6 Expérimentations industrielles 3.6.1 Circuit de test Calc 3.6.2 Circuit IVT 3.7 Travaux futurs - Conclusion 3.7.1 Travaux futurs 3.7.2 Conclusion  4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                           |   |                | 3.4.2   | Liaison avec le simulateur VHDL                           | . 68  |

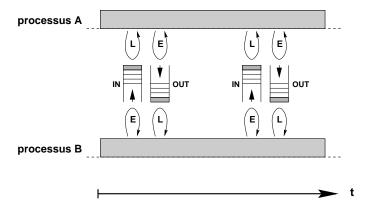

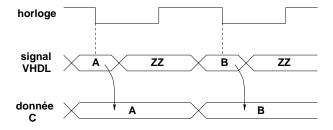

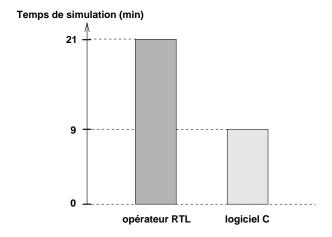

| 3.5.1 Génération de code d'interface 3.5.2 Bloc matériel de connexion C/interface-bus 3.5.3 Intégration aux flots de conception existants 3.6 Expérimentations industrielles 3.6.1 Circuit de test Calc 3.6.2 Circuit IVT 3.7 Travaux futurs - Conclusion 3.7.1 Travaux futurs 3.7.2 Conclusion  4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.1.2 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                         |   |                | 3.4.3   | Synchronisation                                           | . 69  |

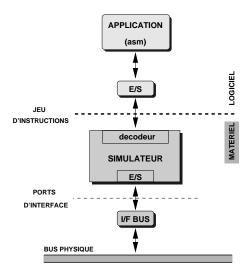

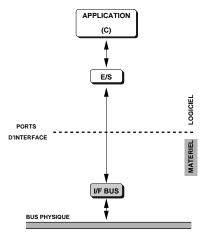

| 3.5.2 Bloc matériel de connexion C/interface-bus 3.5.3 Intégration aux flots de conception existants 3.6 Expérimentations industrielles 3.6.1 Circuit de test Calc 3.6.2 Circuit IVT 3.7 Travaux futurs - Conclusion 3.7.1 Travaux futurs 3.7.2 Conclusion  4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissant 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                        |   | 3.5            | Intégra | ation au système applicatif                               | . 73  |

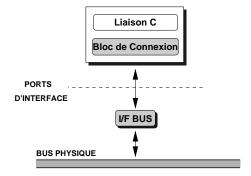

| 3.5.3 Intégration aux flots de conception existants 3.6 Expérimentations industrielles 3.6.1 Circuit de test Calc 3.6.2 Circuit IVT 3.7 Travaux futurs - Conclusion 3.7.1 Travaux futurs 3.7.2 Conclusion  4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                        |   |                | 3.5.1   | Génération de code d'interface                            | . 73  |

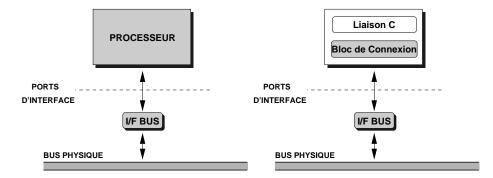

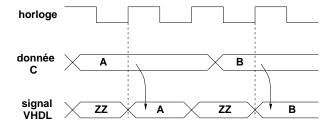

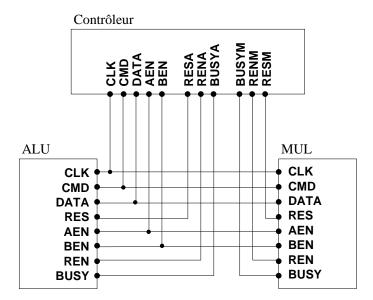

| 3.6.1 Circuit de test Calc 3.6.2 Circuit IVT 3.7 Travaux futurs - Conclusion 3.7.1 Travaux futurs 3.7.2 Conclusion 4.1.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.1.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions croissant 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                | 3.5.2   | Bloc matériel de connexion C/interface-bus                | . 74  |

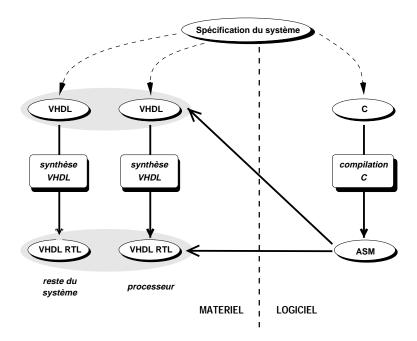

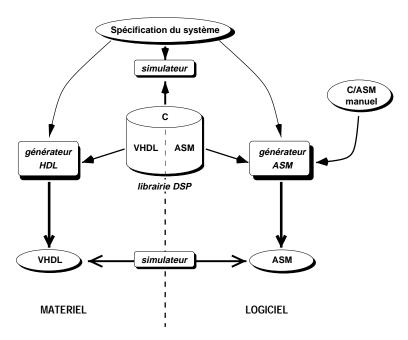

| 3.6.1 Circuit de test Calc 3.6.2 Circuit IVT 3.7 Travaux futurs - Conclusion 3.7.1 Travaux futurs 3.7.2 Conclusion 4.1.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.1.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions croissant 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                | 3.5.3   | Intégration aux flots de conception existants             | . 79  |

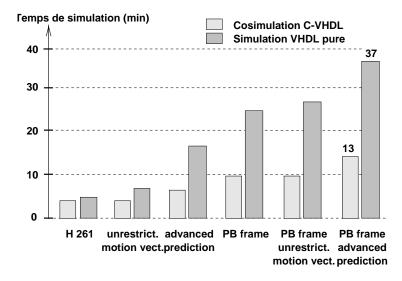

| 3.6.2 Circuit IVT 3.7 Travaux futurs - Conclusion 3.7.1 Travaux futurs 3.7.2 Conclusion  4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissant 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 3.6            | Expéri  |                                                           |       |

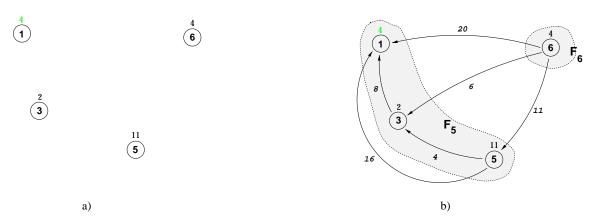

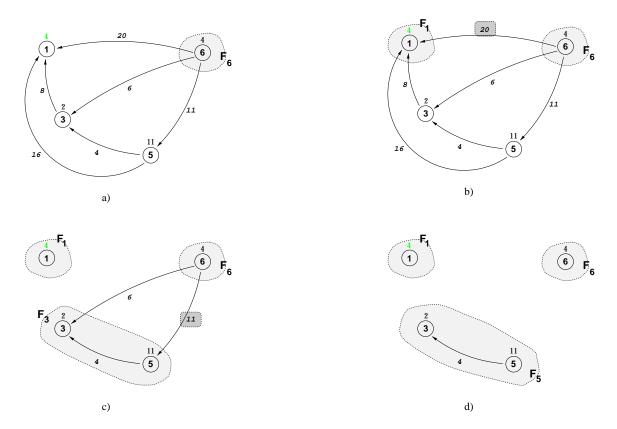

| 3.6.2 Circuit IVT 3.7 Travaux futurs - Conclusion 3.7.1 Travaux futurs 3.7.2 Conclusion  4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissant 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                | 3.6.1   | Circuit de test Calc                                      | . 83  |

| 3.71 Travaux futurs 3.7.2 Conclusion  4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissant 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                | 3.6.2   |                                                           |       |

| 3.7.1 Travaux futurs 3.7.2 Conclusion  4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissant 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 3.7            | Travau  |                                                           |       |

| 4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions d'instructions croissant 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                |         |                                                           |       |

| 4 Exploration d'architectures 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissant 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                |         |                                                           |       |

| 4.1 Motivations et objectifs 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |                |         |                                                           |       |

| 4.1.1 Motivations 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4 | $\mathbf{Exp}$ | loratio | on d'architectures                                        | 91    |

| 4.1.2 Objectifs 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 4.1            | Motiva  | ations et objectifs                                       | . 91  |

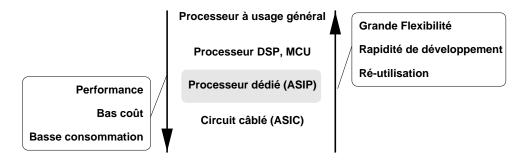

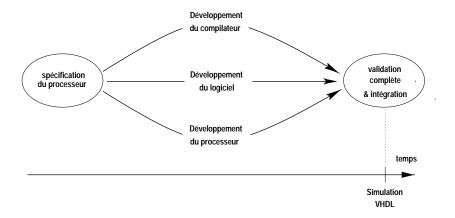

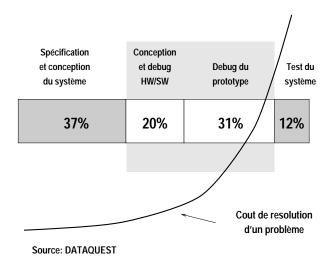

| 4.2 Techniques de minimisation de code 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction du nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                | 4.1.1   | Motivations                                               | . 91  |

| 4.2.1 Définitions 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                | 4.1.2   | Objectifs                                                 | . 93  |

| 4.2.2 Réduction de la largeur à nombre d'instructions constant 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 4.2            | Techni  | iques de minimisation de code                             | . 94  |

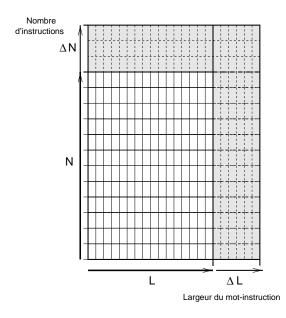

| 4.2.3 Réduction de la largeur à nombre d'instructions croissant 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                | 4.2.1   | Définitions                                               | . 95  |

| 4.2.4 Réduction du nombre d'instructions à largeur croissante 4.2.5 Tableau comparatif 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                | 4.2.2   | Réduction de la largeur à nombre d'instructions constant  | . 98  |

| 4.2.5 Tableau comparatif  4.3 Cas concrets de minimisation de code  4.3.1 Le Thumb de ARM  4.3.2 Le Hobbit de AT&T  4.3.3 CRISCO  4.3.4 Conclusion  4.4 Description de l'exploration du D960  4.4.1 Benchmarks et applications  4.4.2 Chaîne de compilation  4.4.3 Environnement d'exploration FlexPlore  4.5 Exploration autour du D960  4.5.1 Configuration des bancs registres  4.5.2 Encodage des champs immédiats dans le jeu d'instructions  4.5.3 Nombre de registres scratchs  4.5.4 Exemple de compromis à l'encodage  4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                | 4.2.3   | Réduction de la largeur à nombre d'instructions croissant | . 100 |

| 4.3 Cas concrets de minimisation de code 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion  4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore  4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                | 4.2.4   | Réduction du nombre d'instructions à largeur croissante   | . 102 |

| 4.3.1 Le Thumb de ARM 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion  4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore  4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |                | 4.2.5   | Tableau comparatif                                        | . 103 |

| 4.3.2 Le Hobbit de AT&T 4.3.3 CRISCO 4.3.4 Conclusion  4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore  4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 4.3            | Cas co  | oncrets de minimisation de code                           | . 104 |

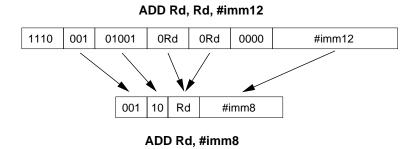

| 4.3.3 CRISCO 4.3.4 Conclusion  4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore  4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                | 4.3.1   | Le Thumb de ARM                                           | . 104 |

| 4.3.4 Conclusion  4.4 Description de l'exploration du D960  4.4.1 Benchmarks et applications  4.4.2 Chaîne de compilation  4.4.3 Environnement d'exploration FlexPlore  4.5 Exploration autour du D960  4.5.1 Configuration des bancs registres  4.5.2 Encodage des champs immédiats dans le jeu d'instructions  4.5.3 Nombre de registres scratchs  4.5.4 Exemple de compromis à l'encodage  4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |                | 4.3.2   | Le Hobbit de AT&T                                         | . 106 |

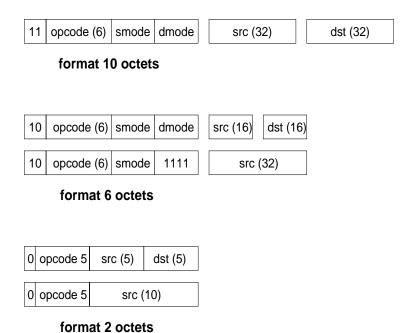

| 4.4 Description de l'exploration du D960 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                | 4.3.3   | CRISCO                                                    | . 107 |

| 4.4.1 Benchmarks et applications 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                | 4.3.4   | Conclusion                                                | . 108 |

| 4.4.2 Chaîne de compilation 4.4.3 Environnement d'exploration FlexPlore 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 4.4            | Descri  | ption de l'exploration du D960                            | . 108 |

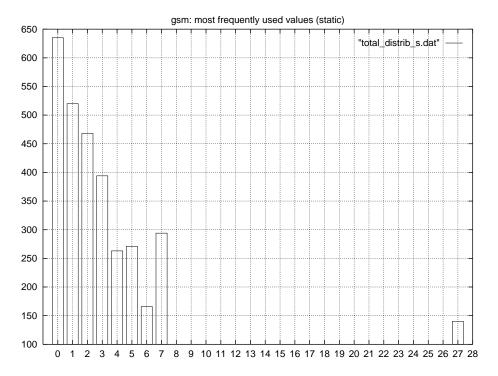

| 4.4.3 Environnement d'exploration FlexPlore  4.5 Exploration autour du D960  4.5.1 Configuration des bancs registres  4.5.2 Encodage des champs immédiats dans le jeu d'instructions  4.5.3 Nombre de registres scratchs  4.5.4 Exemple de compromis à l'encodage  4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                | 4.4.1   | Benchmarks et applications                                | . 109 |

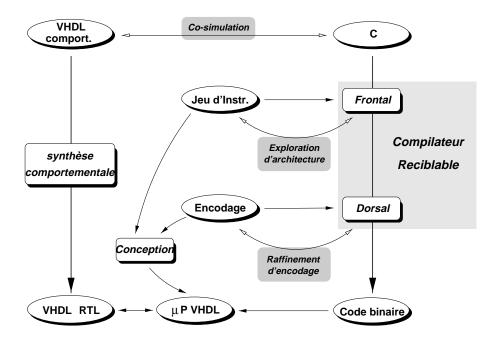

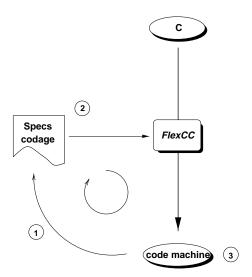

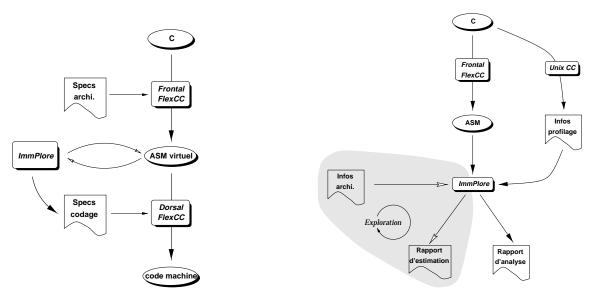

| 4.5 Exploration autour du D960 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |                | 4.4.2   | Chaîne de compilation                                     | . 109 |

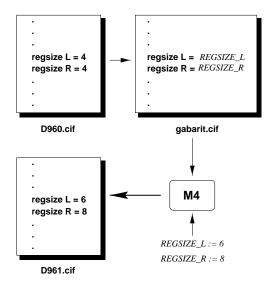

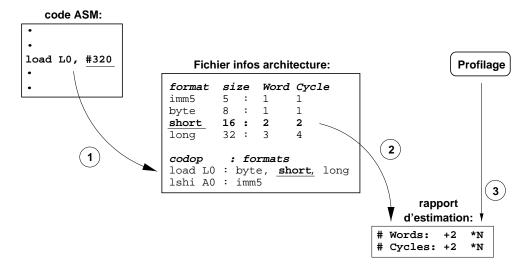

| 4.5.1 Configuration des bancs registres 4.5.2 Encodage des champs immédiats dans le jeu d'instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                | 4.4.3   | Environnement d'exploration FlexPlore                     | . 111 |

| 4.5.2 Encodage des champs immédiats dans le jeu d'instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 4.5            | Explor  | ration autour du D960                                     | . 111 |

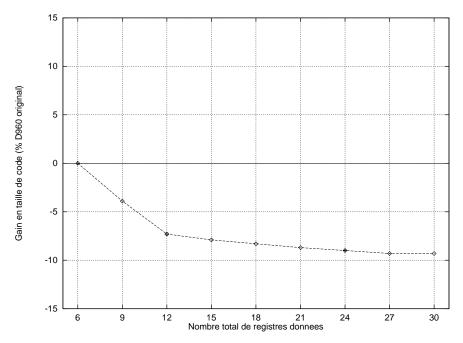

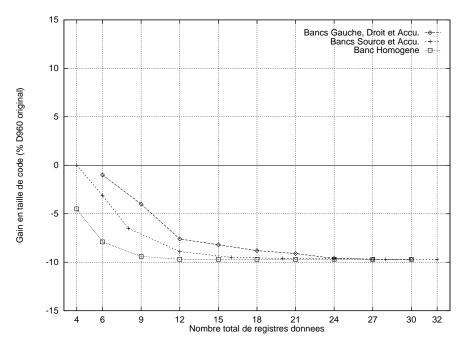

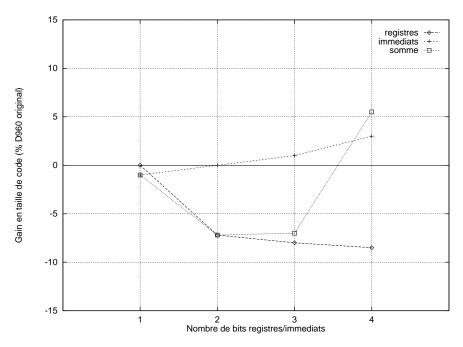

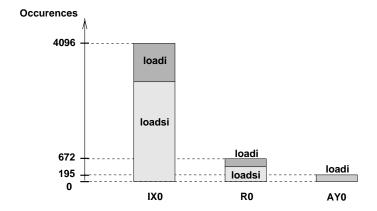

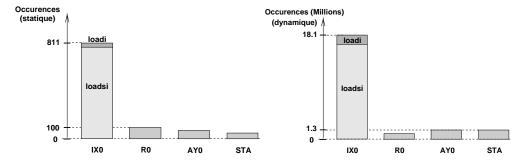

| 4.5.3 Nombre de registres scratchs 4.5.4 Exemple de compromis à l'encodage 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |                | 4.5.1   | Configuration des bancs registres                         | . 112 |

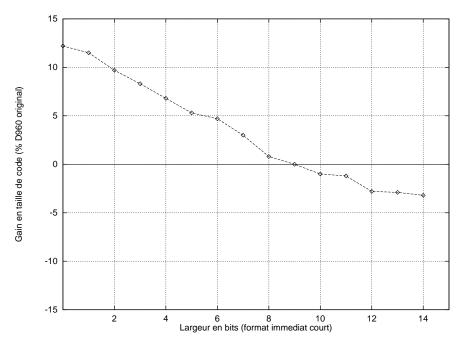

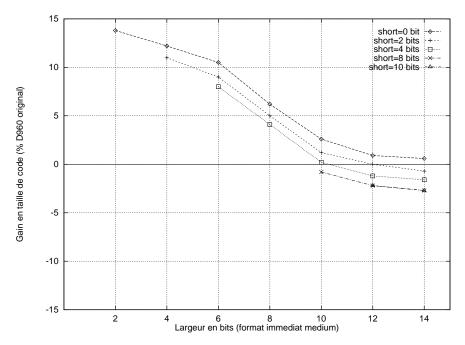

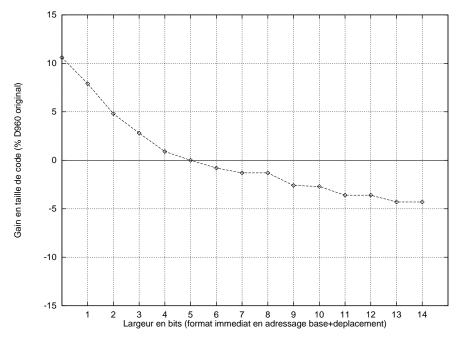

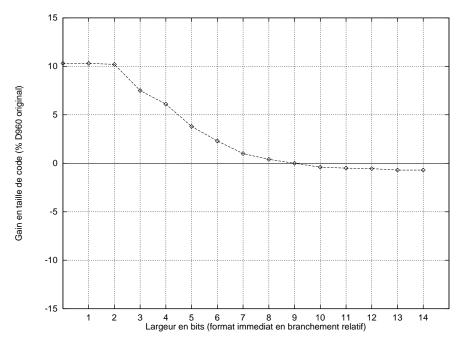

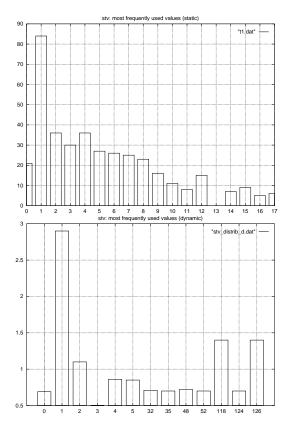

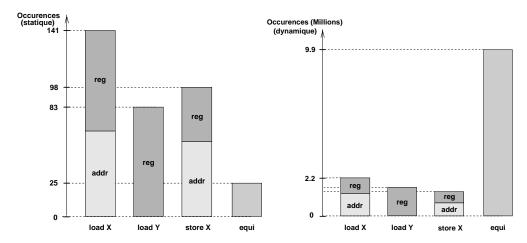

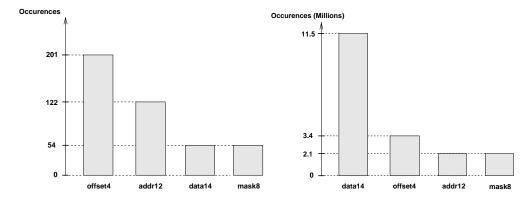

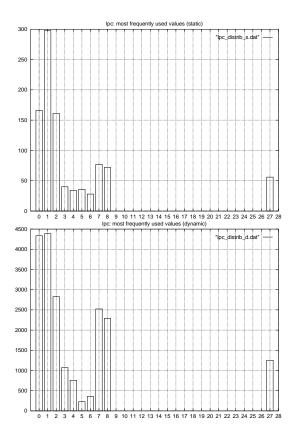

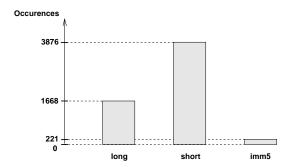

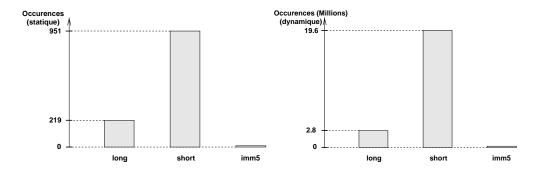

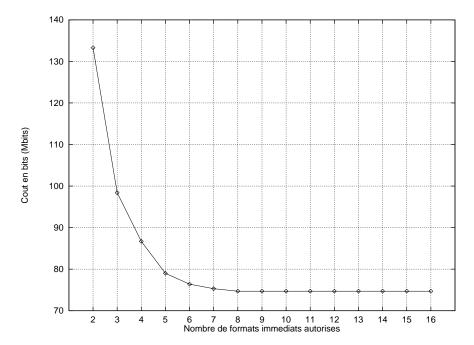

| 4.5.4 Exemple de compromis à l'encodage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                | 4.5.2   | Encodage des champs immédiats dans le jeu d'instructions  | . 114 |

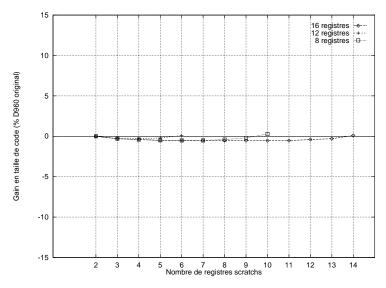

| 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                | 4.5.3   | Nombre de registres scratchs                              | . 118 |

| 4.5.5 Leçons tirées de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                | 4.5.4   | Exemple de compromis à l'encodage                         | . 119 |

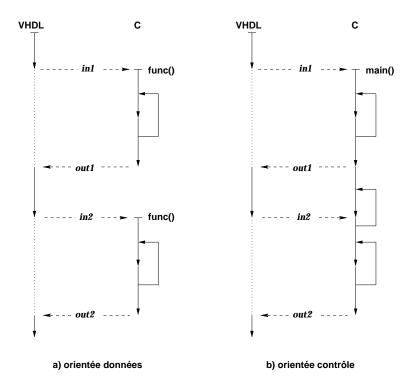

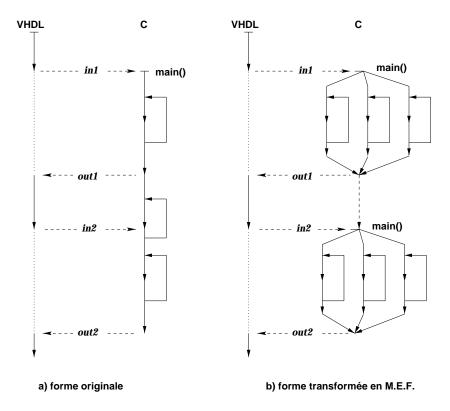

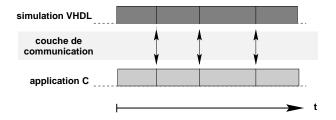

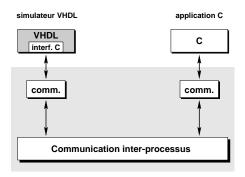

| 4.6 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |                | 4.5.5   |                                                           |       |